Results and perspectives from RD53 on the Next Generation Readout Chips for HL-LHC silicon pixel detector phase 2 upgrades

> L. Demaria (INFN / Torino) On behalf of RD53 Collaboration

> > TREDI 2019 - Trento 25 Feb 2019

### This talk will cover:

- Introduction

- RD53 evolution towards final chip

- Analog Front End : results / performance

### This talk will not cover:

- Test beam results (more talk during the conference)

- Detailed radiation hardness results

- Details of Serial Powering testing of RD53A &/or system aspects

Many results shown here rely on the work done by several people in RD53 but a **special thanks** goes to young students, that are working with lot of enthusiasm and energy: you will find their names along the presentation when referring to their work !

### **Requirements from HL\_LHC experiments**

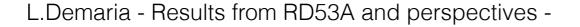

Small pixels:50x50um2Large chips :2cm x 2cm(~0.5 billion transistors)Pixel Hit rates:up to 3 GHz/cm2(200 P.U.)Radiation :1Grad, 1016 n/cm2(unprecedented)

Trigger: up to 1MHz with 12.8us latency (~100x buffering and readout) Low power - Low mass systems

Data readout : up to 4-8 Gbs/s

TRIGGER Latency up to 12.8us (x3) ==> deeper storage buffer

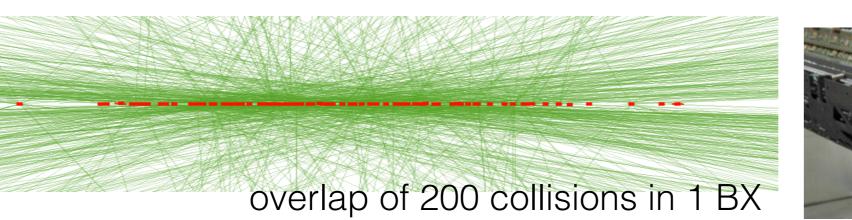

Pixel Detector at HL\_LHC

Sensor

Charged particle

2014

2015

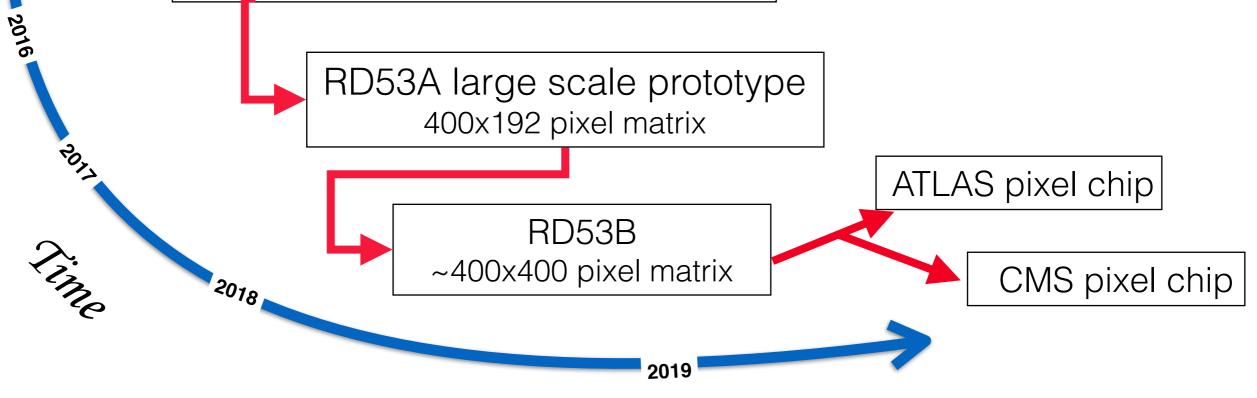

# RD53 timeline

- A. Development of Building blocks: IP-Block; Analog Very Front Ends

- B. Development of Digital Architecture

- **S** C. Verification environment

- D. Complex Chip Integration : modern tools to secure a successful ASIC submission

- E. Radiation characterization: try mitigation strategy

Small DEMONSTRATORs : 64x64 pixel matrix

### RD53A core design team

Flavio Loddo (Bari) Tomasz Hemperek (Bonn) Roberto Beccherle (INFN PI) Elia Conti (CERN) Francesco Crescioli (Paris) Francesco De Canio (INFN BG-PV) Leyre Flores (Glasgow) Luigi Gaioni (INFN BG-PV) Dario Gnani (LBNL) Hans Krueger (Bonn) Sara Marconi (CERN / INFN PG) Mohsine Menouni (CPPM) Sandeep Miryala (FNAL) Ennio Monteil (INFN TO) Luca Pacher (INFN TO) Andrea Paternò (INFN TO)

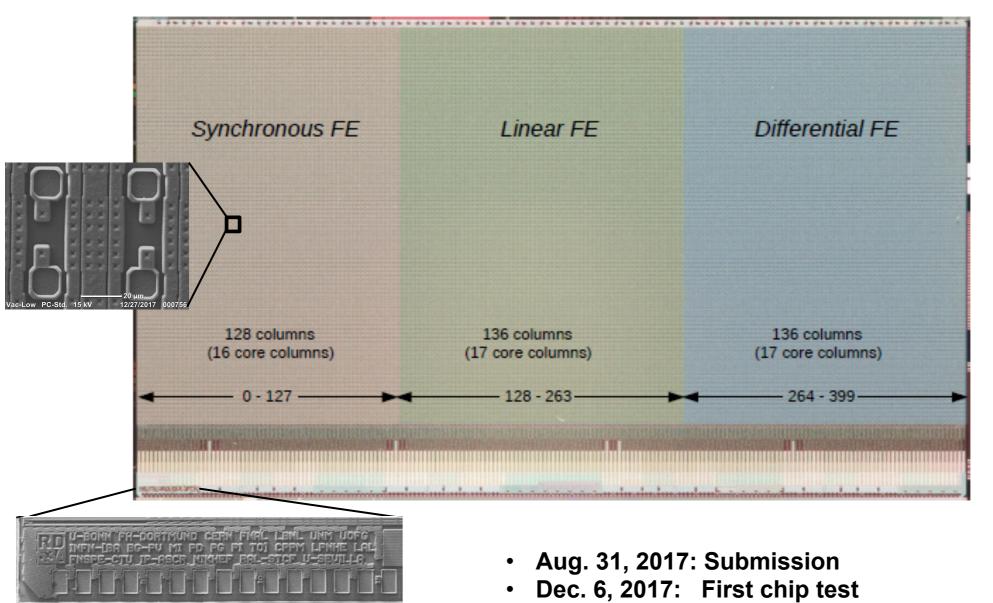

### 2 x 1,15 cm<sup>2</sup>

### ~200M transistors

- Mar. 15, 2018: 25 wafers ordered

- Apr. 13, 2018: First bump-bonded chip test

- Aug. 1, 2018: Other 25 wafers ordered

#### Chip doc on CDS: http://cds.cern.ch/record/2287593

L.Demaria - Results from RD53A and perspectives -

TREDI 2019 - Trento 25 Feb 2019

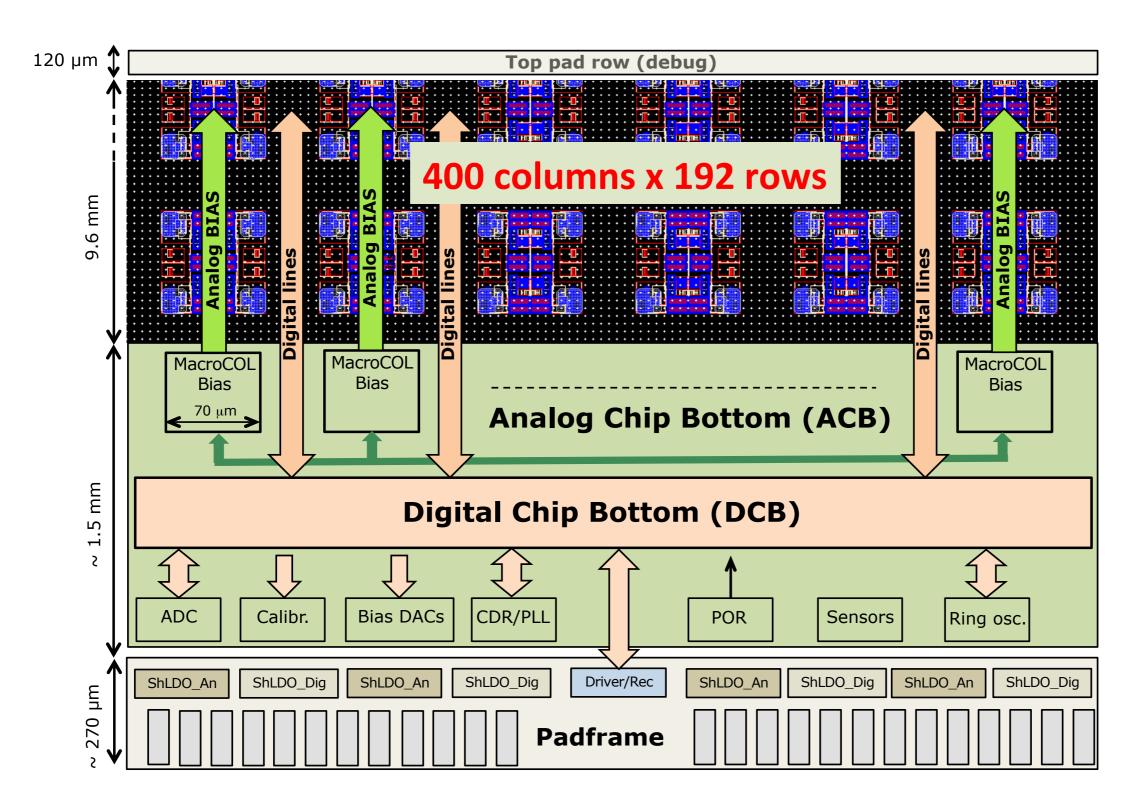

### RD53A Functional floorplan

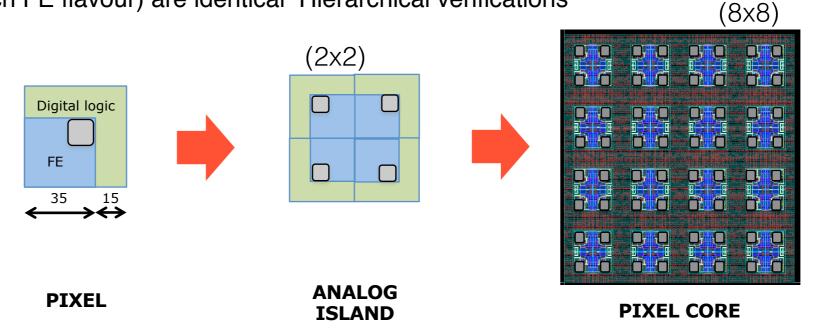

# Pixel Matrix

- The pixel matrix is built up of 8 x 8 Pixel Cores

- 16 analog islands (2x2 quads) embedded in a flat digital synthesized sea

- 50% of area to Analog, 50% to digital

- A Pixel Core can be simulated at transistor level with analog simulator

- $\cdot$  All Cores (for each FE flavour) are identical Hierarchical verifications

All the digital logic for signal digitisation, storage, trigger-matching and readout is shared among several pixel, called Pixel Regions. Two different Pixel region architectures have been implemented

### Distributed Buffering architecture (DBA)

- with (1x4) regions and distributed ToT storage

- implemented for two Analog FE (Lin, Diff)

### Centralized Buffering architecture (CBA)

- with (4x8) regions and centralised ToT storage

- implemented for one Analog FE (Sync)

both allow to run at high rate (3 GHz/cm2), high trigger rate (1MHz) long latencies (12.8 us) with <1% inefficiency

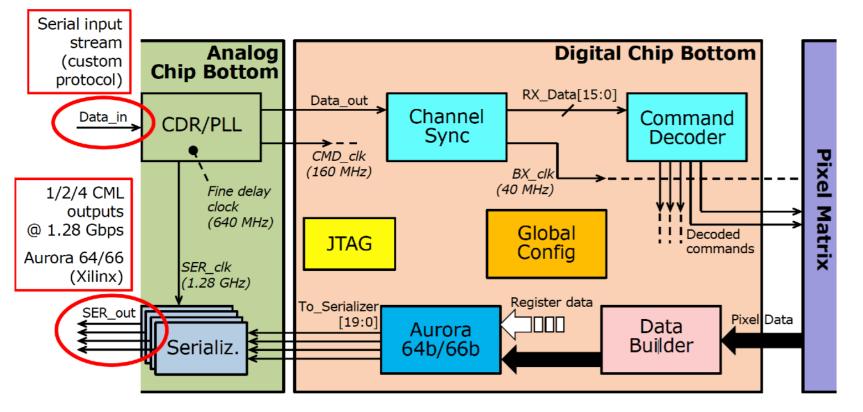

## Digital Bottom and I/O

- CDR/PLL: single input: commands, clock, trigger@160 MHz

- serial output with 4-lines, each@1,28 Gbs, using Aurora 64b/66b protocol

ALL works fine, chip works also after irradiation (500 Mrad) results

### Issue / Improvements discovered:

- CDR/PLL full reliability is fundamental. Lock stability needs further improvement for larger range of input voltage, temperature and after irradiation.

- For Output the PLL clock is influenced by chip activity. Problem understood and proved

- new prototype submitted in August

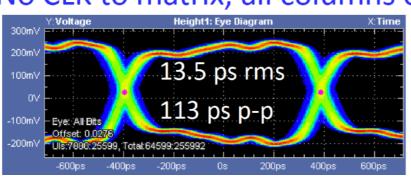

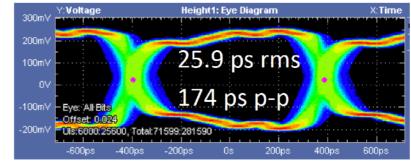

### No CLK to matrix, all columns off CLK send to matrix, all columns on

# Testing and use of RD53A

- Two test systems : BDAQ53 and YARR

- More than 300 chips distributed among >30 institutes for chip characterisation

- 150 of them are bump bonded to sensors

- In April first test beam, mainly to understand RD53A

- Test beams for Sensor RD started with RD53A

- May-August with un-irradiated detectors

- In autumn first test of irradiated detectors

- 2019 : further. test-beams (Desy/FNAL...)

- Wafer level testing at Bonn soon other 2-3 centres

- Experiments started intense system-tests with serial powering chains of (1x2) or (2x2) modules

| Current Wafer: 12 |                  |                  |                 |                     |                  |                   |                    |                  |                 |                   |

|-------------------|------------------|------------------|-----------------|---------------------|------------------|-------------------|--------------------|------------------|-----------------|-------------------|

|                   |                  |                  |                 |                     | 05-01<br>CPPM    | 06-01<br>DORTMUND |                    |                  |                 |                   |

|                   |                  |                  |                 | 04-02<br>BN         | 05-02<br>CERN    | 06-02<br>LBNL     | 07-02<br>CPPM      | 08-02<br>BN      |                 | _                 |

|                   |                  | 02-03<br>BN      | 03-03<br>ETH    | 04-03<br>BN         | 05-03<br>UIC     | 06-03<br>BN       | 07-03<br>WUPPERTAL | 08-03<br>CPPM    | 09-03<br>BN     |                   |

|                   |                  | 02-04<br>GLASGOW | 03-04<br>CERN   | 04-04<br>MI-BICOCCA | 05-04<br>FIRENZE | 06-04<br>BN       | 07-04<br>CPPM      | 08-04<br>CPPM    | 09-04<br>LBNL   |                   |

|                   |                  | 02-05<br>BN      | 03-05<br>TORINO | 04-05<br>BN         | 05-05<br>CERN    | 06-05<br>BN       | 07-05<br>CPPM      | 08-05<br>BN      | 09-05<br>LBNL   | 10-05<br>DORTMUND |

|                   | 01-06<br>GLASGOW | 02-06<br>CERN    | 03-06<br>BN     | 04-06<br>CERN       | 05-06<br>FIRENZE | 06-06<br>BN       | 07-06<br>BN        | 08-06<br>BN      | 09-06<br>LBNL   | 10-06<br>CPPM     |

|                   | 01-07<br>ETH     | 02-07<br>CERN    | 03-07<br>BN     | 04-07<br>HAMBURG    | 05-07<br>BN      | 06-07<br>BN       | 07-07<br>BN        | 08-07<br>BN      | 09-07<br>KEK    | 10-07<br>CPPM     |

|                   | 01-08<br>ETH     | 02-08<br>CERN    | 03-08<br>CERN   | 04-08<br>CPPM       | 05-08<br>CERN    | 06-08<br>BN       | 07-08<br>CPPM      | 08-08<br>BN      | 09-08<br>TORINO | 10-08<br>LPNHE    |

|                   |                  | 02-09<br>BN      | 03-09<br>CERN   | 04-09<br>BN         | 05-09<br>CPPM    | 06-09<br>BN       | 07-09<br>WUPPERTAL | 08-09<br>BN      | 09-09<br>CERN   | 10-09<br>LPNHE    |

|                   |                  | 02-10<br>BN      | 03-10<br>BARI   | 04-10<br>CPPM       | 05-10<br>BN      | 06-10<br>BN       | 07-10<br>BN        | 08-10<br>BERGAMO | 09-10<br>LPNHE  |                   |

|                   |                  |                  | 03-11<br>CERN   | 04-11<br>CPPM       | 05-11<br>BN      | 06-11<br>ETH      | 07-11<br>BN        | 08-11<br>BN      |                 | -                 |

|                   |                  |                  |                 | 04-12<br>BN         | 05-12<br>BN      | 06-12<br>BN       | 07-12<br>BN        |                  | -               |                   |

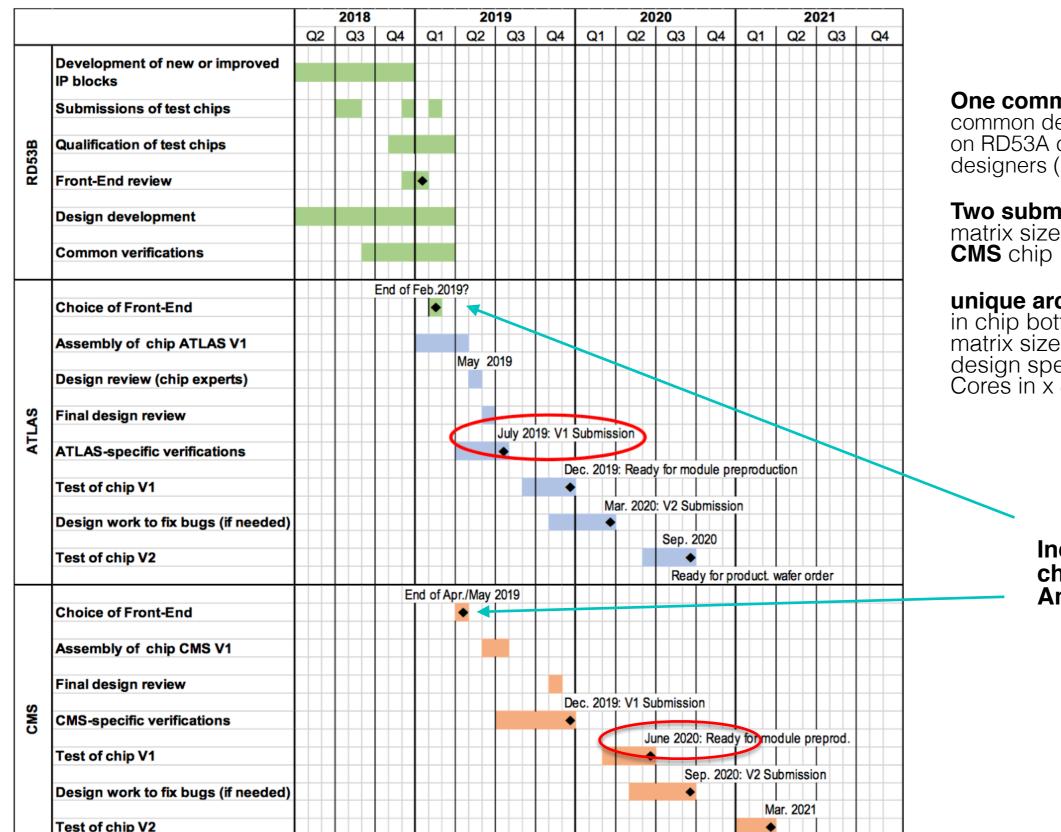

# Strategy and timeline

Ready for product, wafer order

**One common design**: RD53B with common design team - mainly based on RD53A design team: ~ 30 designers (13 FTE)

**Two submissions** with different matrix size: **ATLAS** chip first, then **CMS** chip

**unique architecture** - no difference in chip bottom or Core designmatrix size is a parameter in the design specifying the number of Cores in x & y.

> Independent choice of Analog FE

### RD53A to RD53B

- All RD53A elements with bug fixes and, where needed, technical improvements

- Improved versions of some IPs

- Additional feature to be implemented:

- Bias of edge and top "long" pixels

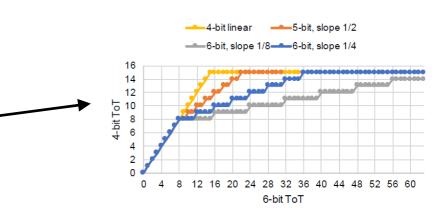

- 6-to-4 bit dual slope ToT mapping

- 80 MHz ToT counting

- ATLAS 2-level trigger scheme

- TMR for SEU hardening

- Power saving ~20%

- Design for test scan chains

- Optimal data formatting and compression

- Date aggregation between pixel chips (CMS requirement now also ATLAS interested)

• ..

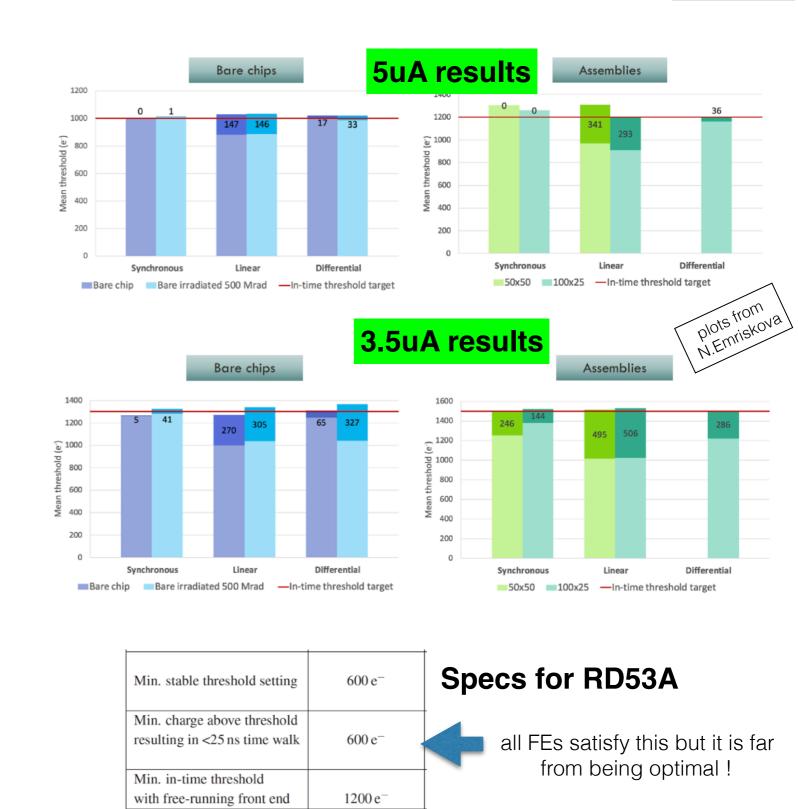

### Analog FE

- small Analog FE : ~ 50% of the 50x50 um2 area

- high efficiency : <1% dead-time, low threshold

- **low power** : reference is 5uA per pixel

- charge measurement (~1ke- /count ) 4-bit

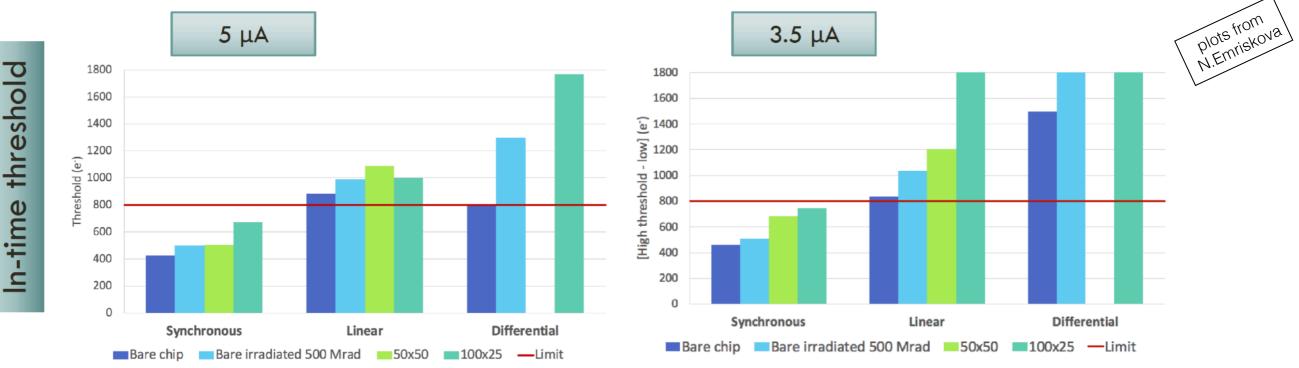

- low level of fake rate : <1E-6 per chip

- applied to sensor choice and radiation conditions : reference 50fF detector, 10nA; 500 Mrad

- Specification on analog FE have been evolving with time

- Initial RD53A requirements

- Important feedback from Analog FE Review

- Now moving to ATLAS requirements and CMS requirements

Take in mind that

- Essential to understand the impact of AFE performances to the CMS/ATLAS pixel detectors : simulation work essential

- The sensor R&D is heavily dependent on RD53A : no sensor choice done yet

# Analog FE review

### General Comments

- The present document and the recommendation presented here is strictly based on the measurement results that have been presented during the reviewer meetings (4<sup>th</sup>-5<sup>th</sup> December 2018 and 24<sup>th</sup> January 2019).

- The reviewers believe that, although many measurements have been done on the front-end designs, still more measurements (and interaction between the measurement teams and the design teams) would be required to better understand the effects that are observed on the three front-ends discussed. In particular, the review committee would like to encourage the measurement teams to increase the statistics of analysed chips and assemblies in order to validate the conclusions presented in this document.

- It is also the belief of the reviewers that the circuit simulation tools in their present state are able to simulate any effect that is observed in fabricated circuits (except radiation effects in the electronics and process-fabrication stress effects). For this reason, the reviewers would like to encourage the measurement teams to work closely with the designers to understand and reproduce on simulations the different effects that are or might be observed.

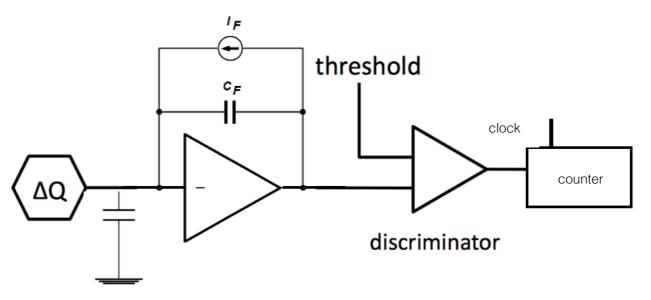

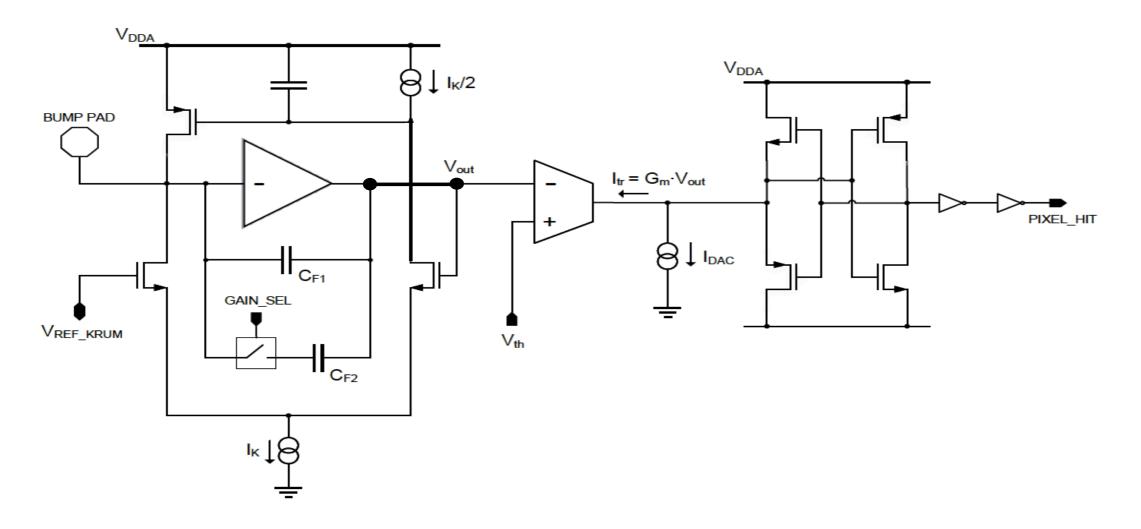

# Analog FE : basics

- 1. Signal charges fast Feedback Capacitance (Cf);

- 2. A stable current discharges Cf, making the signal duration linearly dependent wrt charge;

- 3. Discriminator determines when the signal is above threshold : **Time over Threshold**

- 4. a clocked counter counts the ToT

|           | Input        | lleak to<br>sensor | Feedback-<br>current | Discriminator          | Threshold pixel<br>tuning         | ToT-count<br>clock        |

|-----------|--------------|--------------------|----------------------|------------------------|-----------------------------------|---------------------------|

| Linear FE | single ended | Krummenacher       |                      | Asynchronous           | 4-bit trimming<br>DAC             | 40 MHz chip<br>clock      |

| Diff FE   | differential | LCC circuit        | IFF                  | Asynchronous           | 5-bit trimming<br>DAQ             | 40 MHz chip<br>clock      |

| Synch FE  | single ended | Krummenacher       |                      | Synchronous<br>with BX | Autozero Pulse<br>200ns@abort gap | 20-400 MHz<br>local clock |

L.Demaria - Results from RD53A and perspectives -

TREDI 2019 - Trento 25 Feb 2019

value status

20.0 m

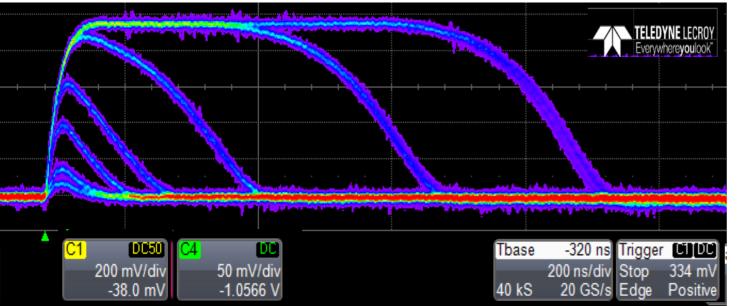

P1:sdev(C4) 97.0 mV P2:pkpk(C4) 97.0 mV P3:msiC4) P3:msiC4) P3:msiC4) P3:msiC4) P3:msiC4) P4:area(C3) P5:ampl(C2) P5:ampl(C2

CSA output for Q=30, 20, 10, 5, 3, 1.2, 0.6 ke-

L.Demaria - Results from RD53A and perspectives -

### Q-1,2ke- for different return to base line (IK=55,100,155)

TREDI 2019 - Trento 25 Feb 2019

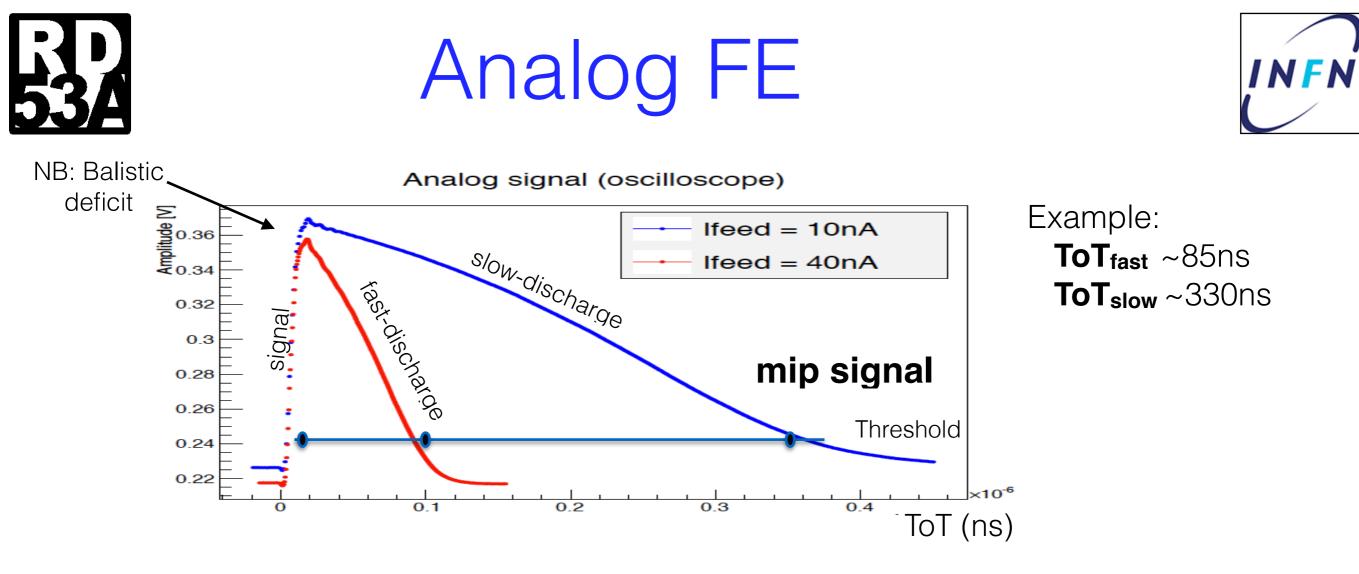

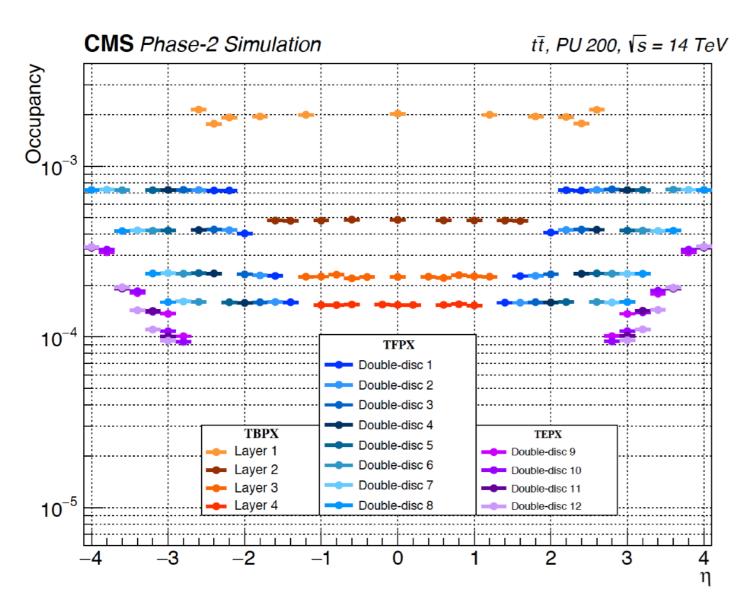

TOT is analog dead-time, therefore is has to be kept small is order to determine a negligible inefficiency.

Fake hits have to be kept negligible wrt signal

|        | Осс     | AFE<br>ineff | mip ToT | Fake/<br>Occ | Fake    |

|--------|---------|--------------|---------|--------------|---------|

| L1     | 2E-03   | 0,5 %        | 62ns    | 1 %          | 2E-05   |

| L1     | 2E-03   | 1 %          | 125ns   | 1 %          | 2E-05   |

| L2     | 8E-04   | 0.5 %        | 156ns   | 1 %          | 8E-06   |

| L3     | 2E-04   | 0,2 %        | 250ns   | 1 %          | 2E-06   |

| L4     | 1,5E-04 | 0,2 %        | 330ns   | 1 %          | 1,5E-06 |

| lowest | 1E-04   | 0,2 %        | 500ns   | 1%           | 1E-06   |

|        |         |              |         |              | *       |

Value used by RD53 up to review

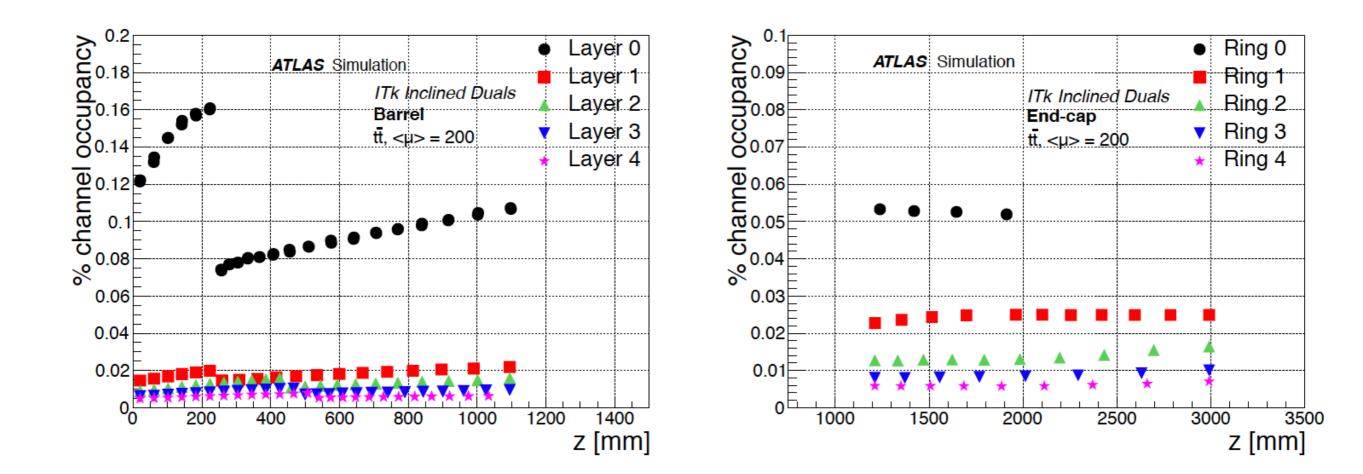

# Atlas occupancies

https://cds.cern.ch/record/2285585/files/ATLAS-TDR-030.pdf

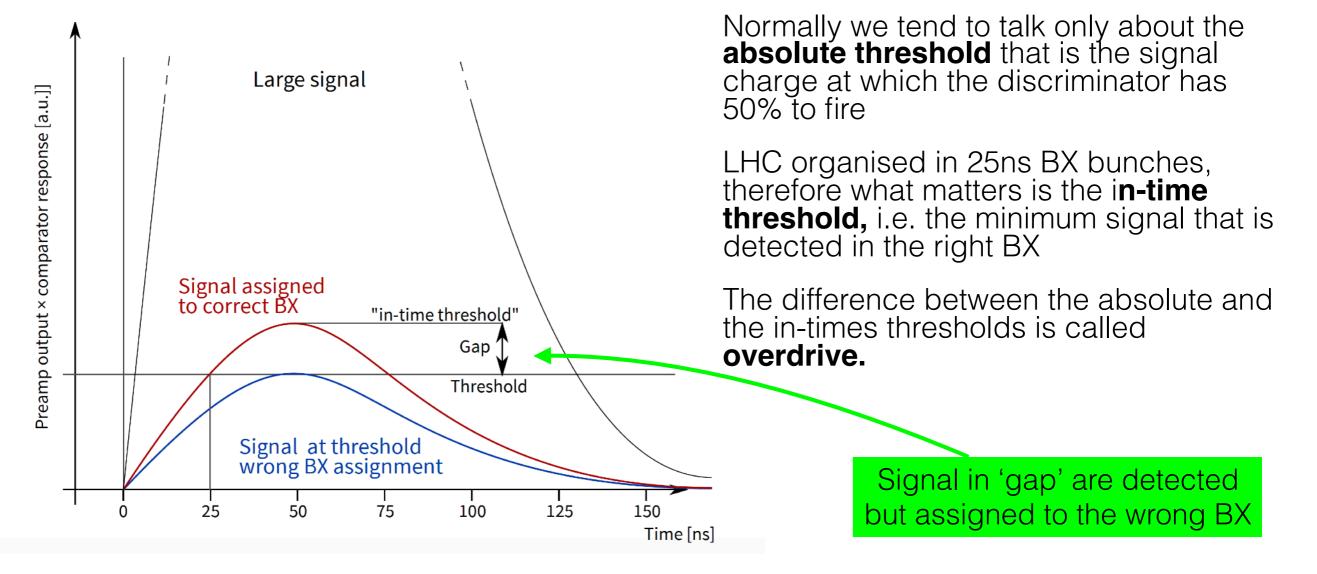

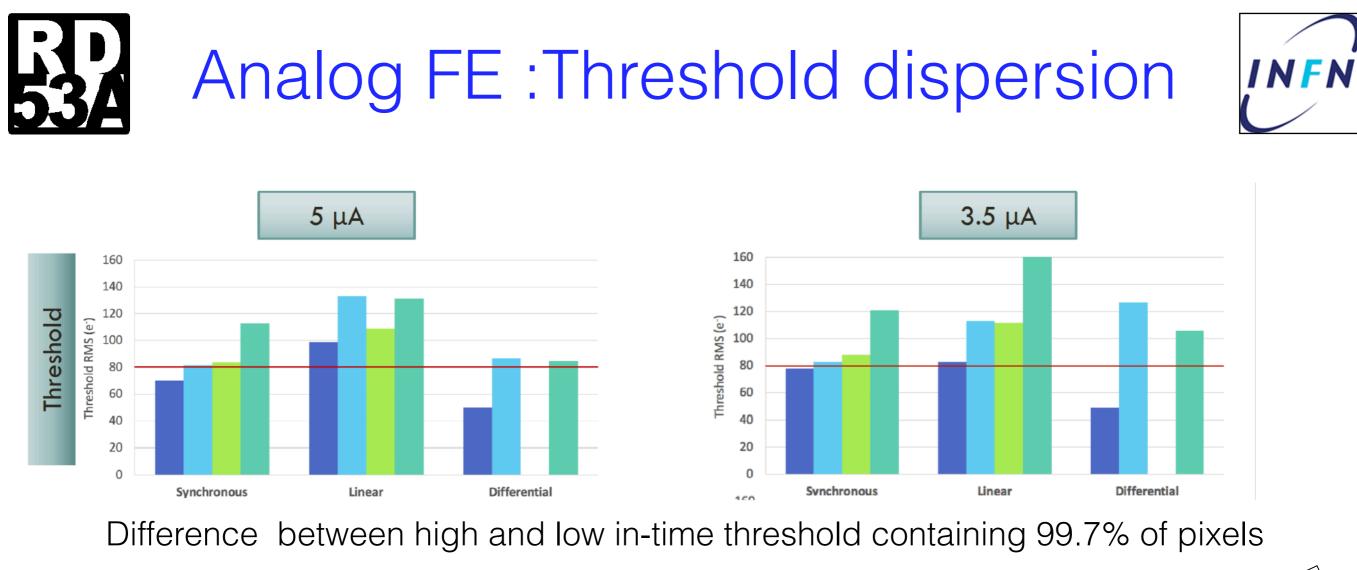

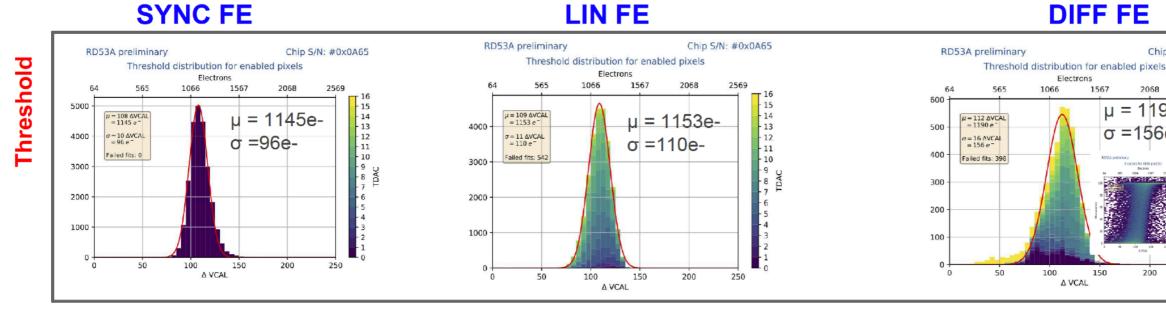

# Analog FE :threshold(s)

- 1. Only in-time threshold matters

- 2. Overdrive generate OOT pile-up: 50e- correspond ~1% OOT-pile up

### Overdrive = 50e- in L1 = 2E-5 of hits that are ~Fake hits

# Analog FE :overdrive

L.Demaria - Results from RD53A and perspectives -

TREDI 2019 - Trento 25 Feb 2019

L.Demaria - Results from RD53A and perspectives -

TREDI 2019 - Trento 25 Feb 2019

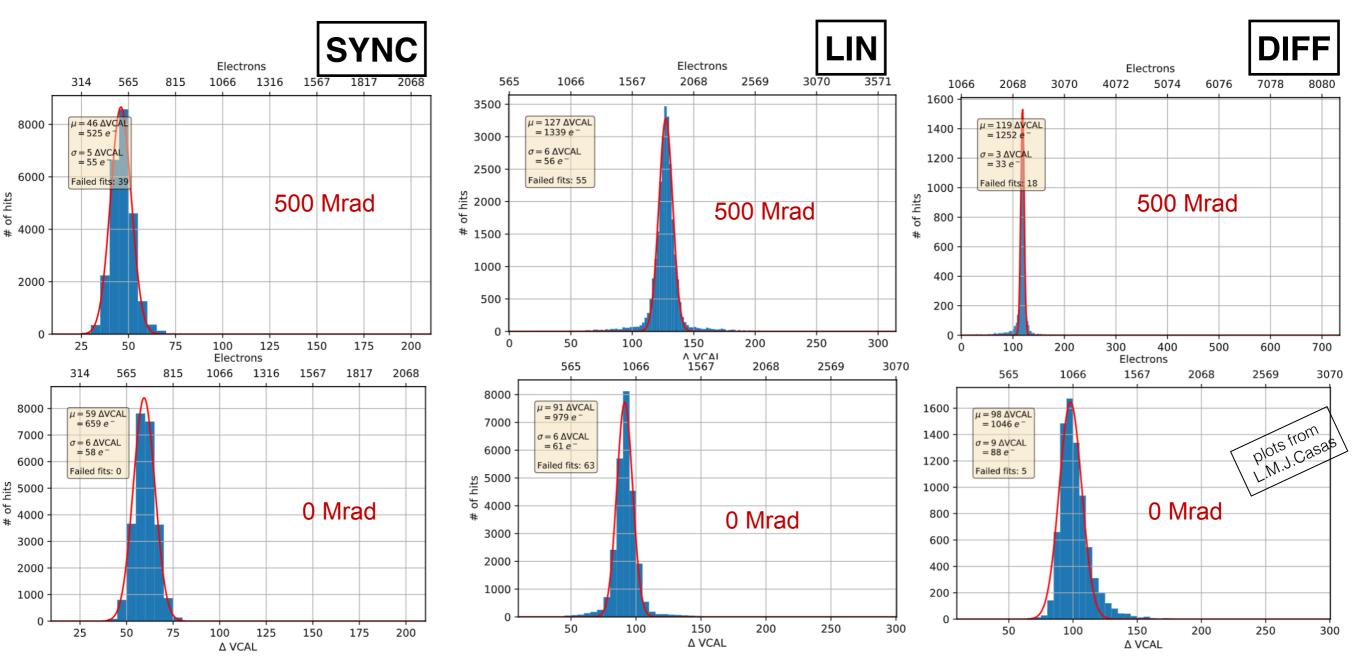

# AFE Radiation hardness

Irradiation with x-ray@cold, RD53A powered on and tested/readout continuously Striking good results - chip works, all three AFE work with low **thresholds** !

other irradiation results show the robustness of Analog FE

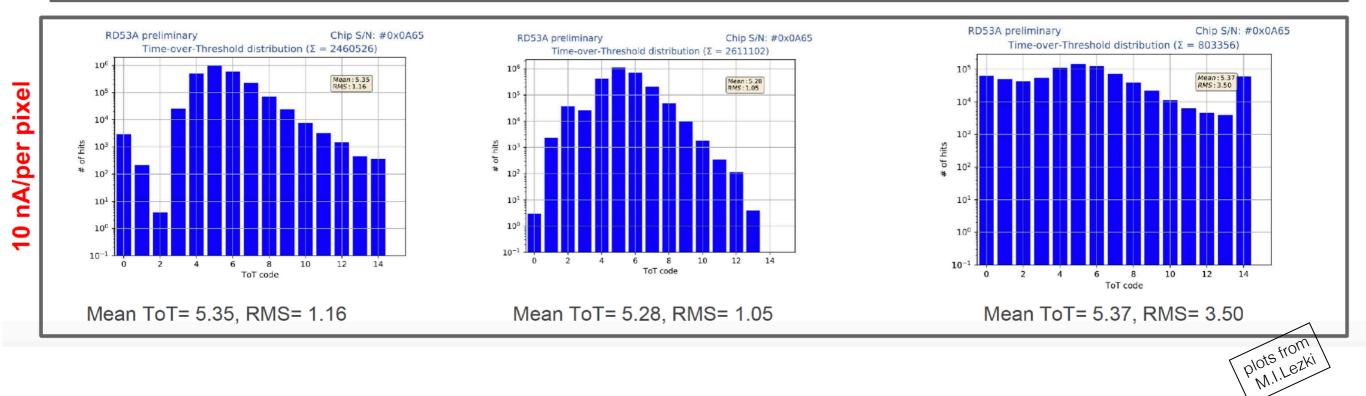

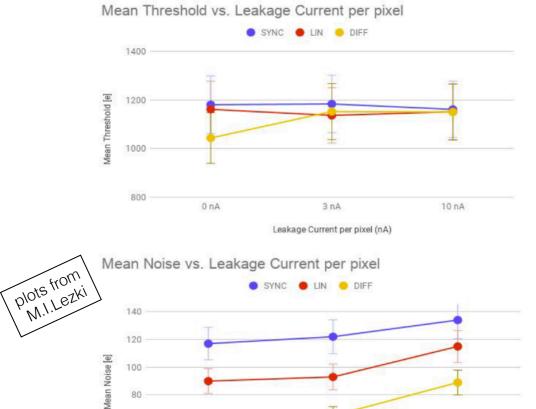

### AFE vs Leakage current

plots from M.I.Lezki

Chip S/N: #0x0A65

2569

250

2068

$\mu = 1190e$ -

200

σ =156e-

### **Threshold Dispersion 10nA / per pixel**

#### Vth= 135, IBIAS KRUM SYNC=50

#### Vth1=113, Vth2=0, VFF= 64, LCC=400, PreCompDiff=512

150

**DIFF FE**

1567

Electrons

1066

100

A VCAL

50×50 µm<sub>2</sub>(MPP W2-54GNA) no PT, 100 µm thickness - chip #0x0A65, irradiated fluence (neg/cm<sub>2</sub>) = 3.00E+15

L.Demaria - Results from RD53A and perspectives -

TREDI 2019 - Trento 25 Feb 2019

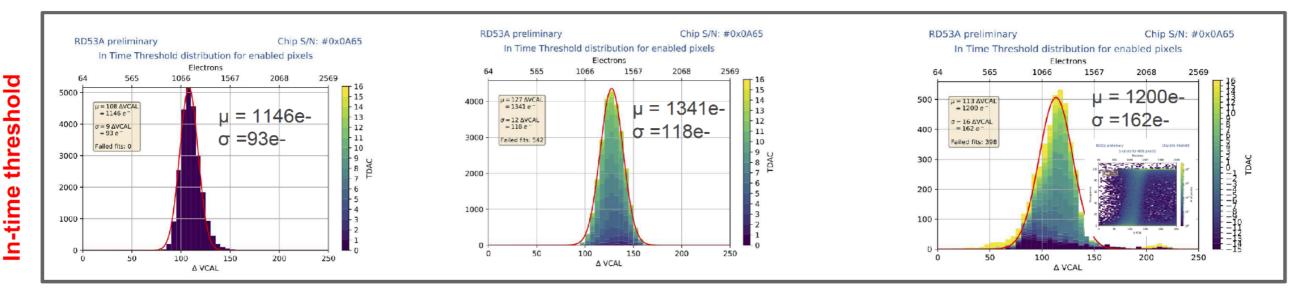

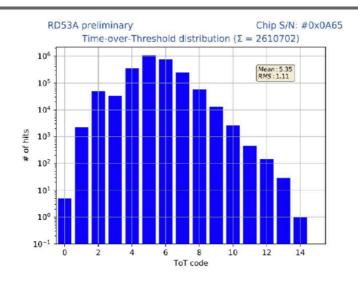

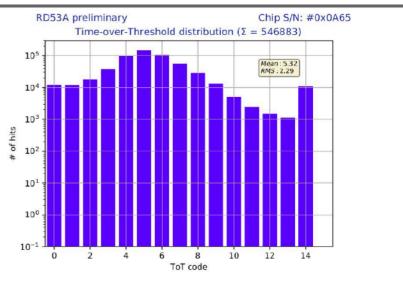

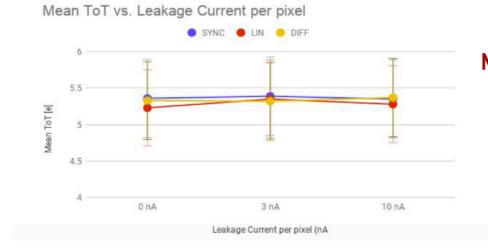

# Analog FE:ToT for Q=6ke-

LIN FE

#### SYNC FE

nA/per pixel

က

Mean ToT= 5.39, RMS= 1.21

Mean ToT= 5.35, RMS= 1.11

### DIFF FE

Mean ToT= 5.32, RMS= 2.29

## AFE Summary

|           | ENC with<br>assembly | Threshold dispersion             | Overdrive<br>@5uA 1200e- | Fake hits<br>@thr=1200e- | ТоТ        | ToT res (for<br>6ke=125ns) |

|-----------|----------------------|----------------------------------|--------------------------|--------------------------|------------|----------------------------|

| Linear FE | 80-115e-             | .1113ke- rms;<br>1-1,1ke- perc.  | ~300e-                   | 1,E-07                   | linear     | 500-1000e-                 |

| Diff FE   | 65-90e-              | .08ke- rms;<br>1,25-1,7ke- perc. | 0-40e-                   | 1,E-12                   | not-linear | 500-1000e-                 |

| Synch FE  | 120-130e-            | .0811ke- rms;<br>.565ke- perc.   | 0                        | 1-5E-7                   | linear     | 50-1000e-                  |

### ALL FE needs to be modified from RD53A version

#### Linear FE :

- non-linearity of TDAC fixed

- working to decrease overdrive

#### Synchronous FE

- improving AZ circuit (current spike, stability in time)

- working in improvement of ENC and matching with simulations

#### Differential

- defining solution to solve timing issues : Analog/Digital interface and speed of discriminator

- understanding operational stability at cold, high leakage current

- working to understand high irradiation

# Analog FE review

#### **Conclusions**

- In this document we have presented measurement results showing that the three front-ends have shown strong points but also imperfections. Unfortunately and due to timing, the cause of some of the imperfections are to this date not understood. Based on the technical facts exposed in this document, the review committee believes that the Linear Front End is the design that presents a lower risk in its integration into a full scale chip. The reviewers recommend the designers to follow the recommendations that have been exposed in this document and to study the performance of the comparator for its optimization (with minor modifications).

- The reviewers would like to encourage the other teams to continue investigating the limitations on their front-ends.

Basically : continue to work but in urgent need the lowest risk on chip integration is the Linear FE

# Conclusions

- RD53A shows excellent results: low power, low threshold particle detection with 4-bits signal digitisation at extreme particle rates of HL\_LHC are demonstrated for large scale ASIC. Radiation hardness is proved up to at least 500 Mrad

- Sensor R&D is now based on using RD53A. Several test beam are on-going for different type of sensors and level of irradiation and will bring lot of results and information

- ATLAS and CMS chips are planned to be submitted during 2019 as implementation of the RD53 design

- All Analog FE could be made to work for Phase-2 Pixel detector, but improvements is needed in all of them. More measurements and work is needed to better define the Analog FE : work is not finished.

- comparative measurements with all species of sensor

- only planar 50x50 and 25x100 have been used

- only one irradiated module have been deeply tested

- ATLAS and CMS need to take decision very soon

BACKUP

- Single amplification stage for minimum power dissipation

- Krummenacher feedback to comply with the expected large increase in the detector leakage current

- Asynchronous, low power current comparator

- Threshold adjusting with global 8bit DAC and local 4 bit DAC single pixel for threshold tuning

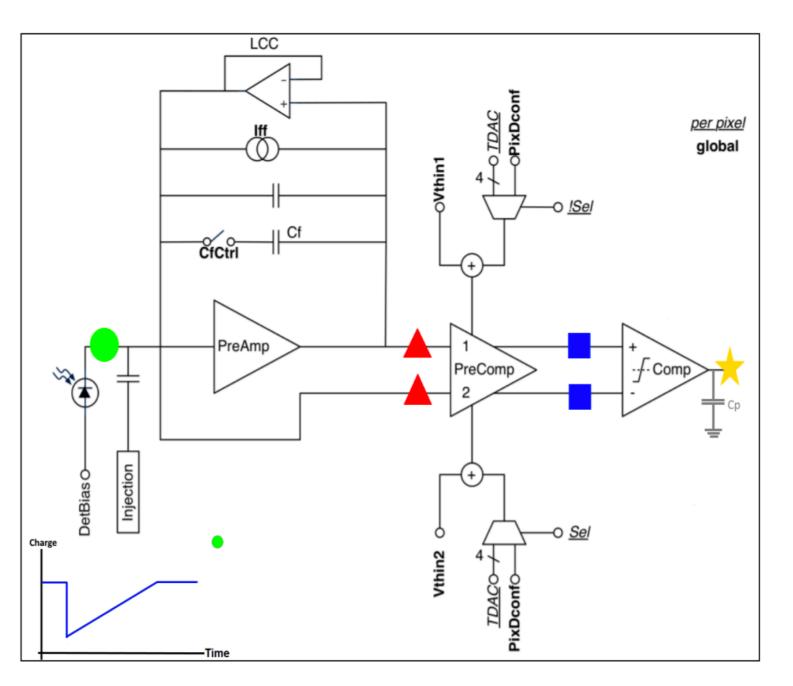

# Differential FE

- Continuous reset integrator first stage with DC-coupled precomparator stage

- Two-stage open loop, fully differential input comparator

- Leakage current compensation

- Threshold adjusting with global 8bit DAC and local 4+1 bit DAC

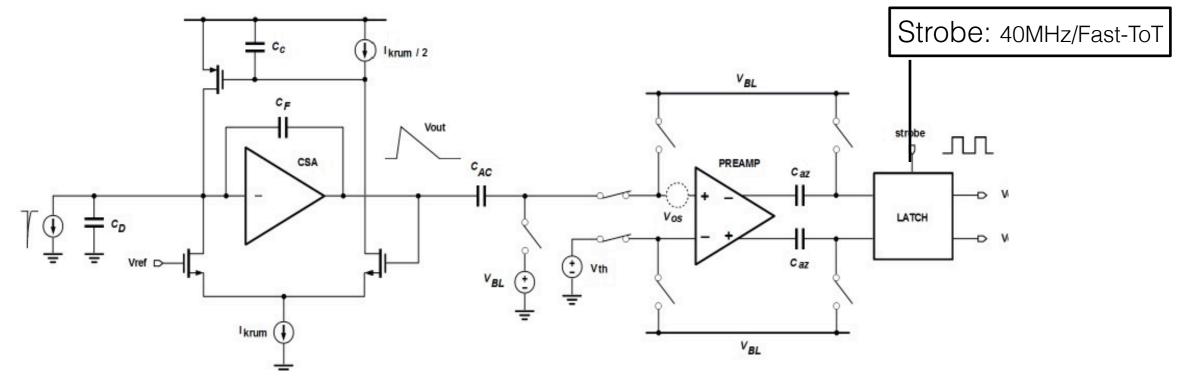

- Telescopic-cascoded CSA with Krummenacher feedback for linear ToT charge encoding

- Synchronous hit discriminator with track-and-latch comparator

- In-time threshold ~ absolute threshold

- No local trimming needed, threshold tuning done using the auto-zeroing technique

- Efficient self-calibration can be performed according to online machine operations (take about 4-600ns every 80 μs, during Abort Gap which is 3us long), so even if some parameters like radiation or T change, tuning is re-optimized immediately

- No trimming-DAC -> less prone to SEU misconfiguration -> pixels don't risk to become too noisy

- ToT counting using 40 MHz clock or Fast local oscillator using latch as local oscillator (30-400 MHz)

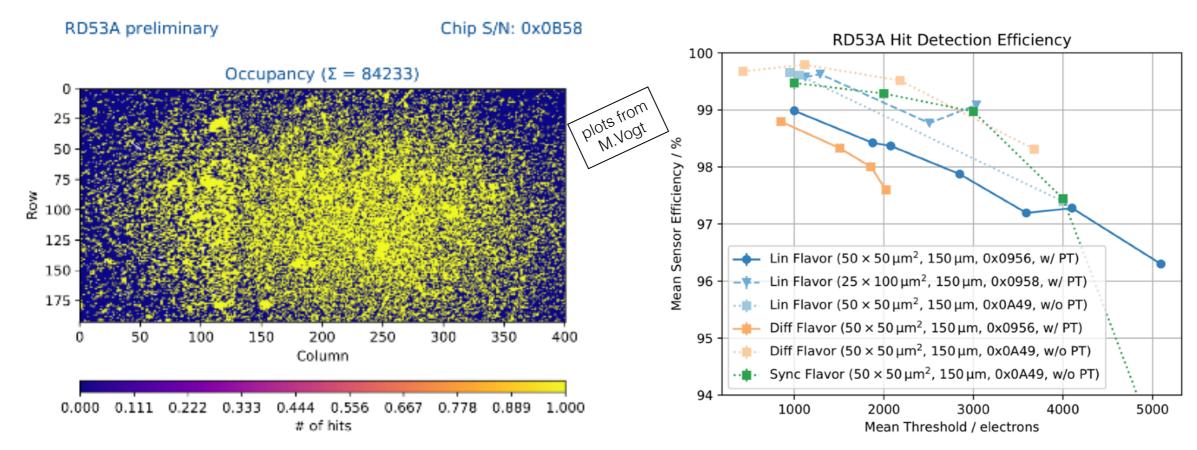

# Measurements with Modules: test-beams

- Test beam done by RD53 to understand chip more than the sensors

- Preliminary studies show similar results for the three FEs

- Now several test-beam have been done (AIDA-2020, ATLAS, CMS) by the sensor community to study planar and 3D silicon sensors. From October also irradiated modules have started to be studied.

- Low thresholds (~800e- to 1200e-) are normally achieved

- Lot of results are coming

- Important learning curve for everybody in the sensor and RD53 community : tuning of FE is important and has to be optimised depending on the detector and its conditions

80

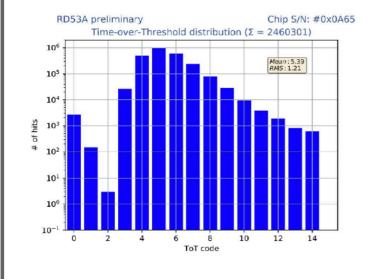

60

40

0 nA

#### Mean Threshold vs. Leakage Current per pixel (nA)

- All FEs almost have the same threshold dispersion for 10nA scenario.

- LIN FE has less mean threshold than SYNC and DIFF for 3nA scenario.

#### Mean Noise vs. Leakage Current per pixel (nA)

3 nA

Leakage Current per pixel (nA)

10 nA

#### Mean ToT vs. Leakage Current per pixel (nA)

All FEs tuned to the target ToT in all configurations.

3