# Testbeam characterization of irradiated SINTEF 3D pixel sensors

Andreas L. Heggelund<sup>1</sup>

A. Kok<sup>2</sup>, O. Koybasi<sup>2</sup>, M. Povoli<sup>2</sup>, A. Summanwar<sup>2</sup>, O. Dorholt<sup>1</sup>, O. M. Rohne<sup>1</sup>, A. L. **Read<sup>1</sup>**, **H. Sandaker<sup>1</sup>**, **B. Stugu<sup>3</sup>**, **M. E. Lauritzen<sup>3</sup>**

> **University of Oslo** 1) SINTEF MiNaLab, Oslo 2) **University of Bergen** 3)

On behalf of

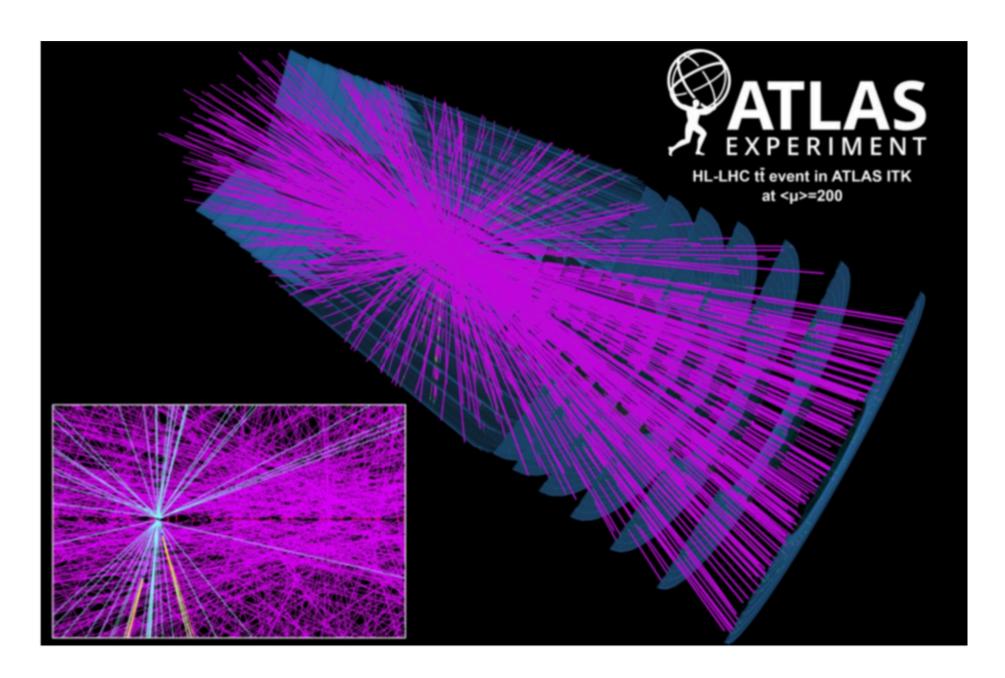

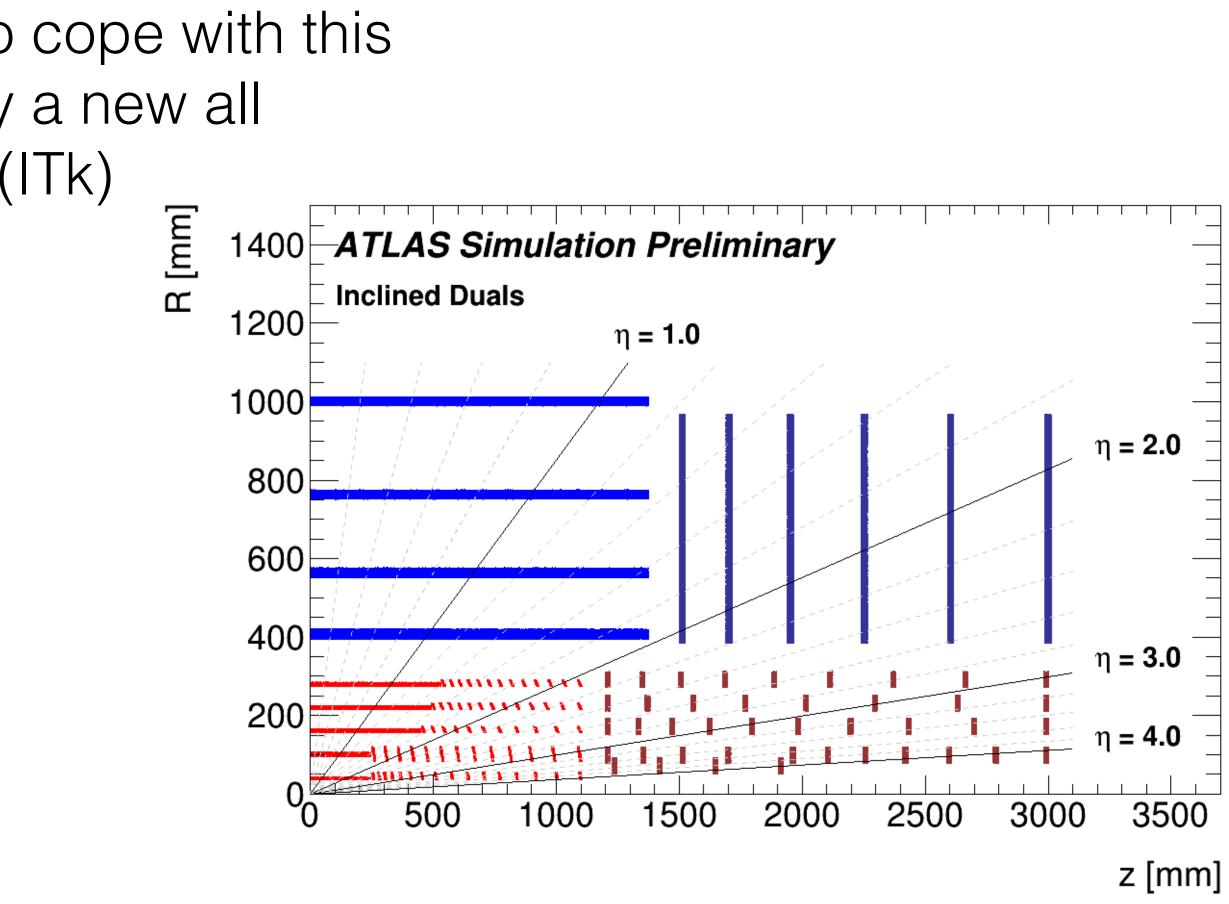

### Upgrade of the LHC and ATLAS

- By 2026 the High-Luminosity LHC should be completed

- Large increase in radiation levels

- The ATLAS detector will be upgraded to cope with this

- Entire Inner detector will be replaced by a new all silicon detector called the Inner Tracker (ITk)

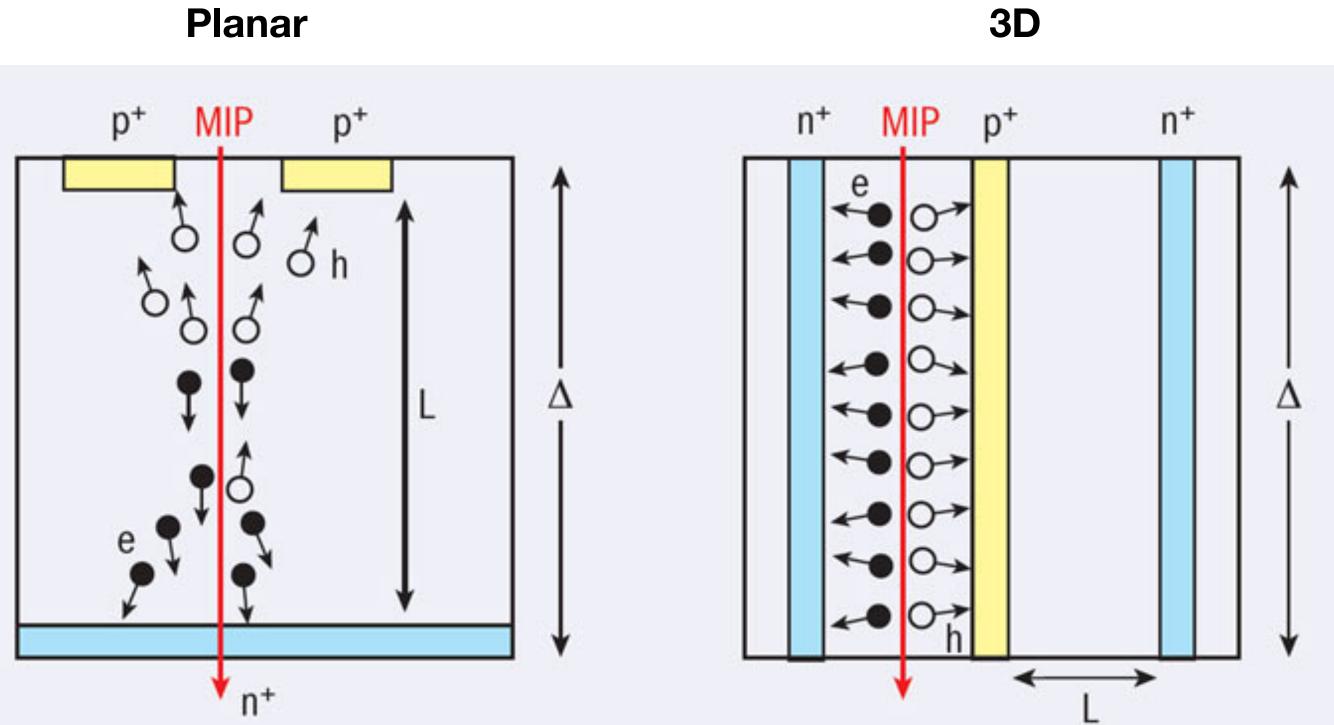

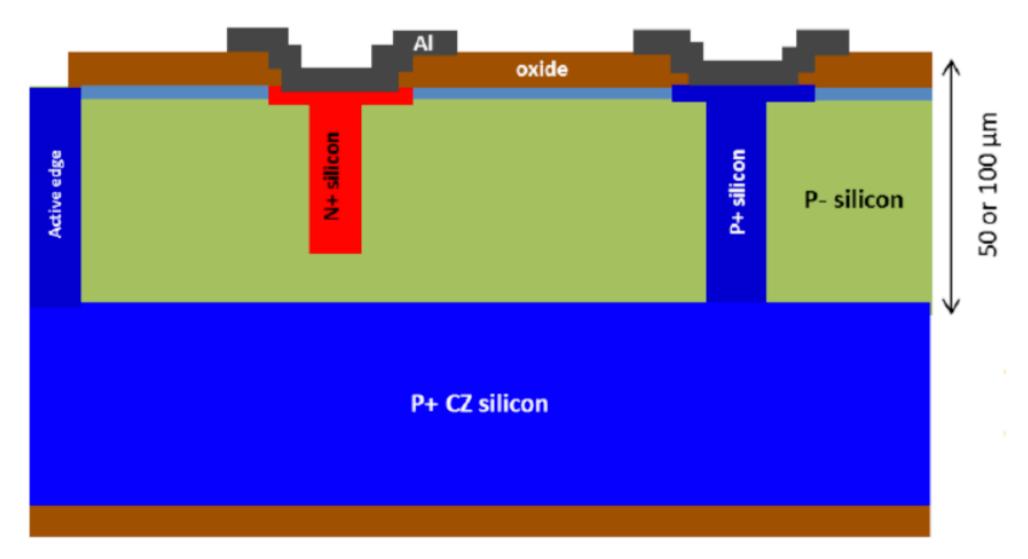

# 3D silicon pixel detectors

-> Lower operation voltage and higher radiation hardness

Different electrode geometry than planar pixel devices

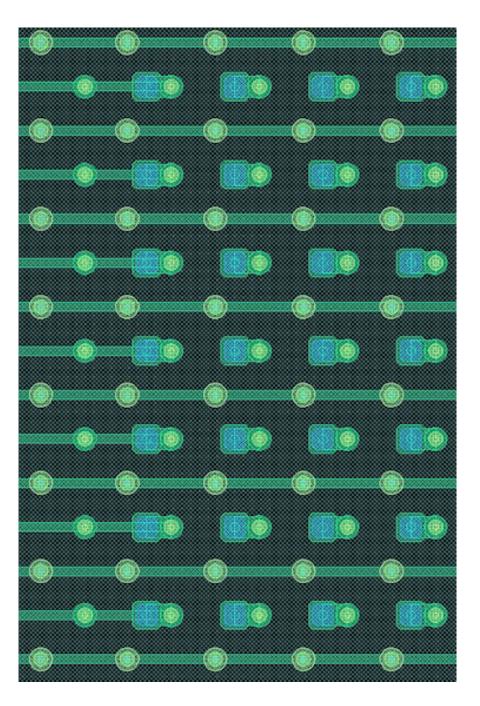

# SINTEF prototyping Run 4

- Full 3D active edge Si-on-Si sensors

- 50 100  $\mu$ m active layer, column diameter drawn as 3  $\mu$ m

- Active edge trench 2.5  $\mu$ m wide

- 50x50  $\mu$ m pixel size

- 1 electrode pr. pixel cell

- Bias electrodes etched through bulk

- Readout electrode column not connected to support wafer -> shows some efficiency

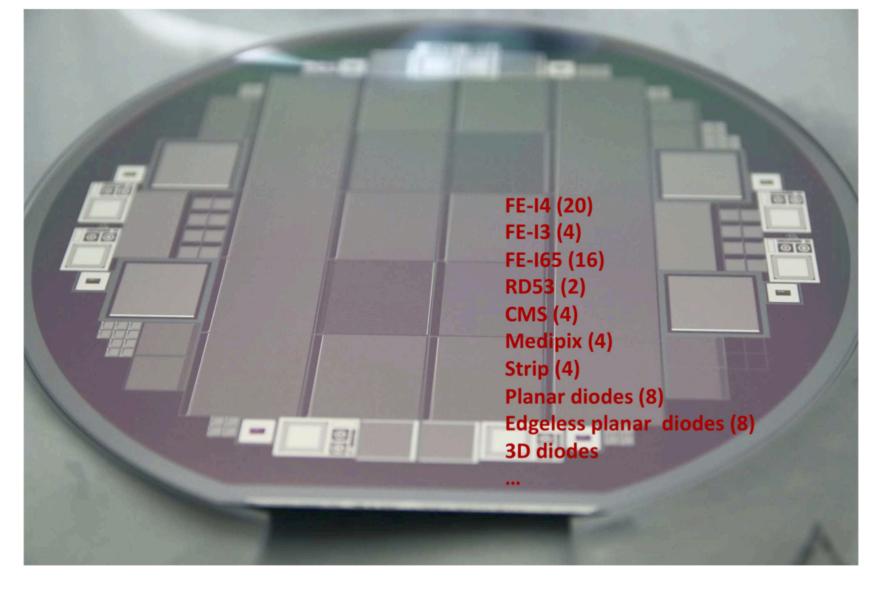

# Fabrication and yield

- Wafer floorplan has a number of layouts, notably the IBL-generation (FE-I4 compatible) and the ITk prototype (RD53A compatible)

- Most FE-I4 (20), 2 RD53 on each wafer.

- Manual probing on temporary metal show a yield of ~70% (FE-I4)

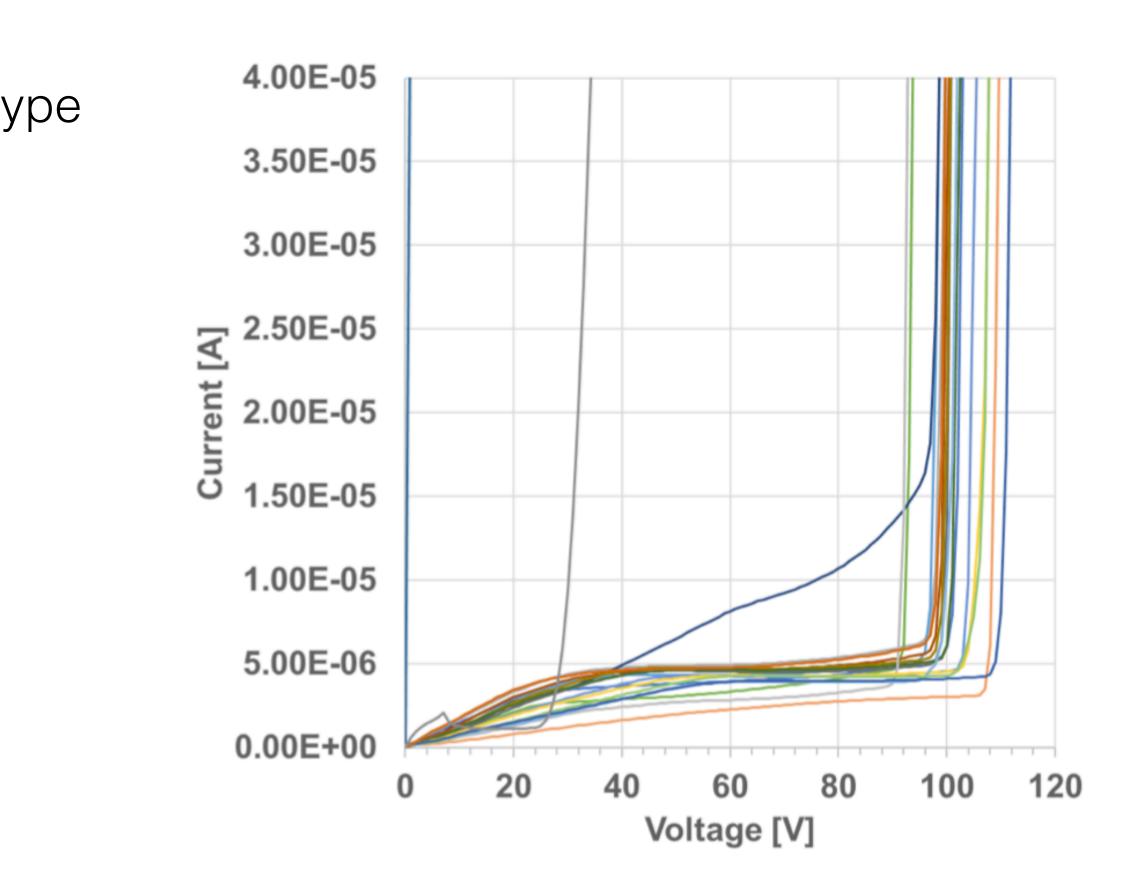

- Breakdown at -100V

I-V curves for all FE-I4 sensors on one wafer

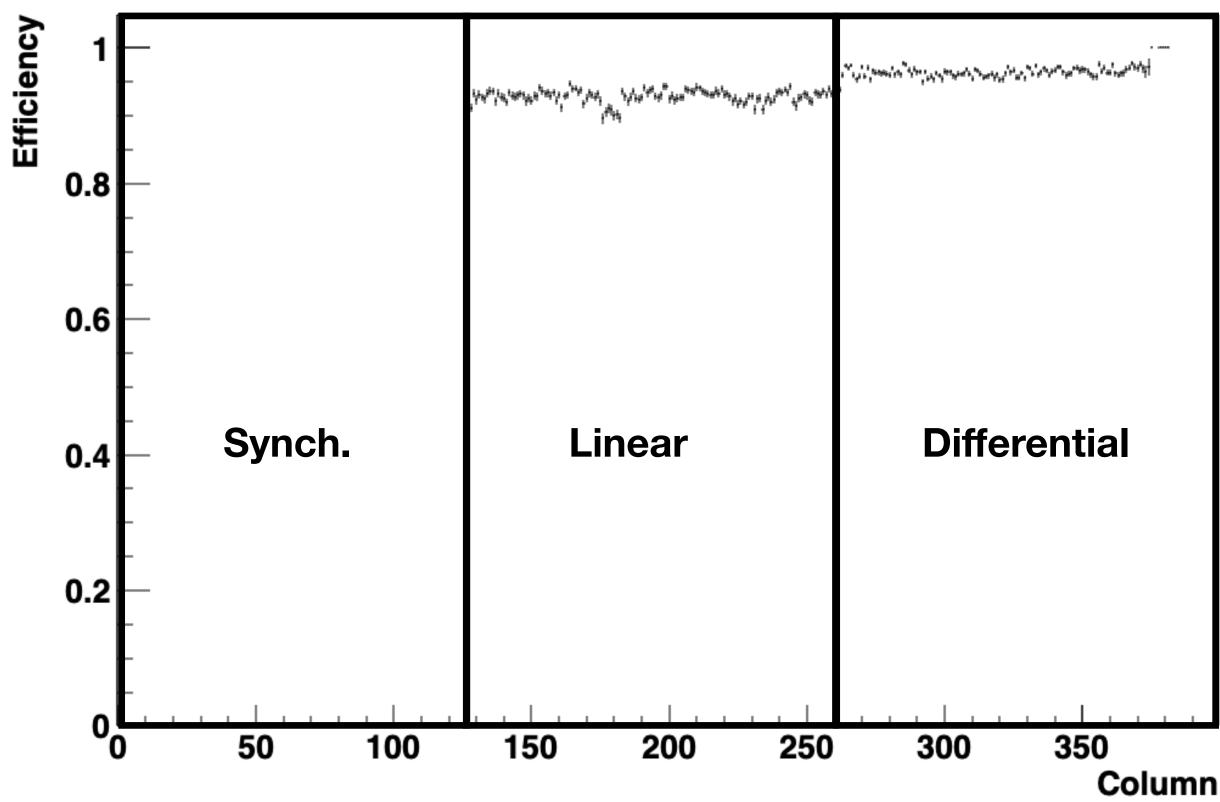

- ATLAS ITk prototype ASIC

- Contains 3 different front ends:

- 1. Synchronous

- 2. Linear

- 3. Differential

Characterized the sensors using the linear and differential front ends

### RD53A

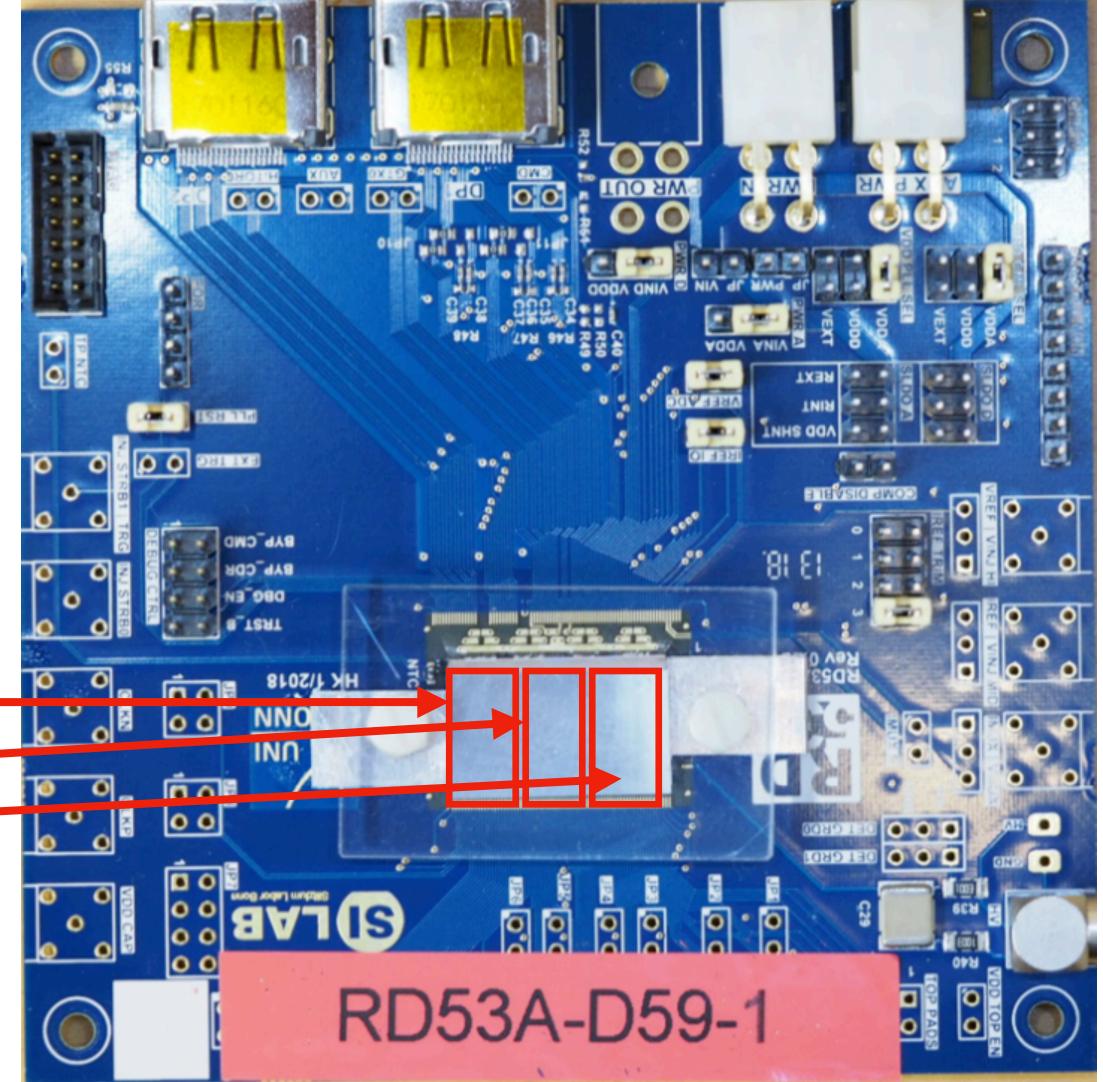

- Under-bump metallisation (UBM) and Flip-Chip was done at Fraunhofer IZM in berlin.

- 8 wafers selected for this, 4 of which was back-side thinned

- Mounting and wire-bonding to SCCs was done at the University of Oslo

RD53A hybrid assemblies ready for mounting

### Further processing

### Bench test of modules

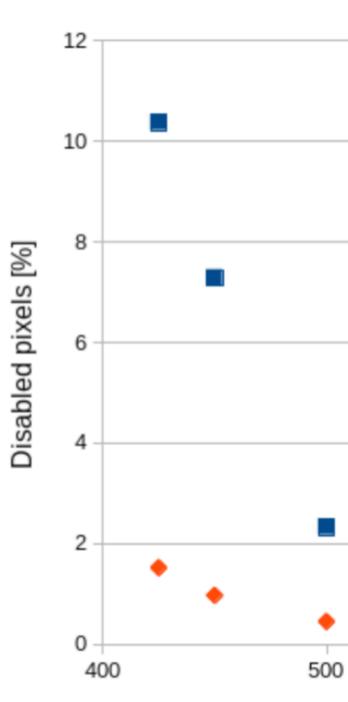

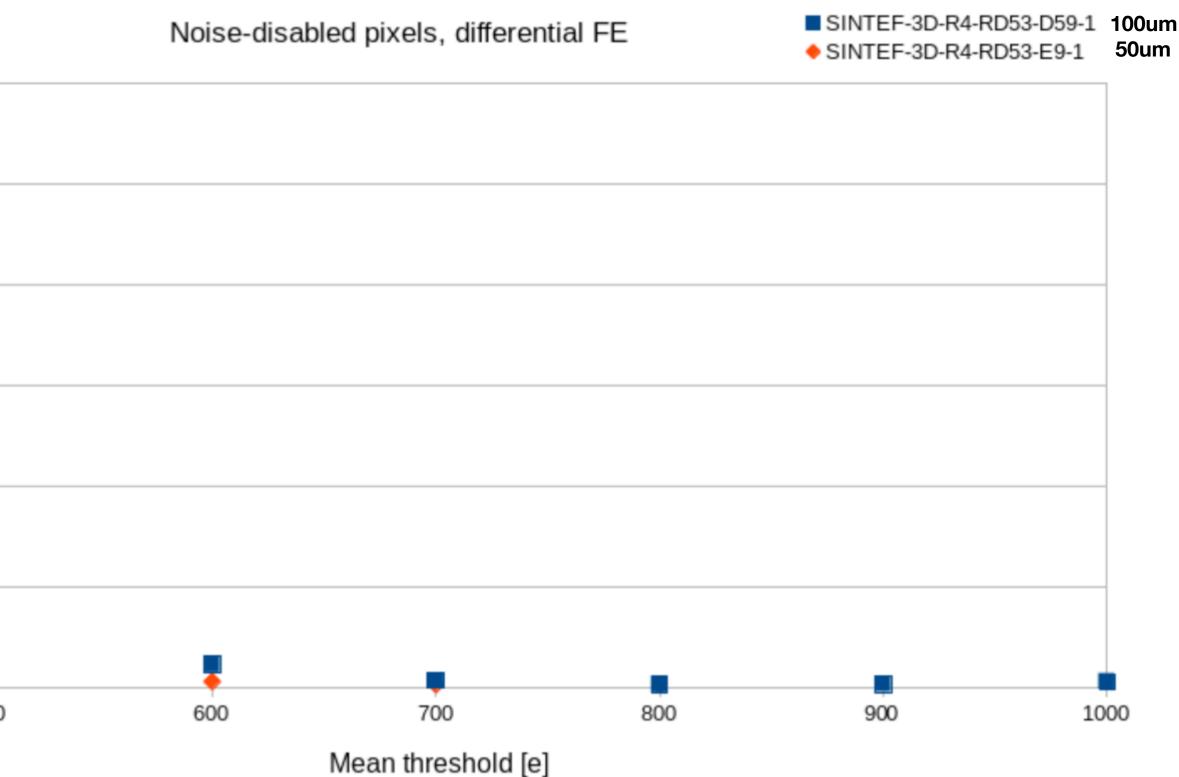

- RD53 asic with RD53 compatible sensor chip

- Scans show a relation between noise and device thickness as we go to lower thresholds

- Thinner device -> lower capacitance -> lower noise -> fewer disabled pixels

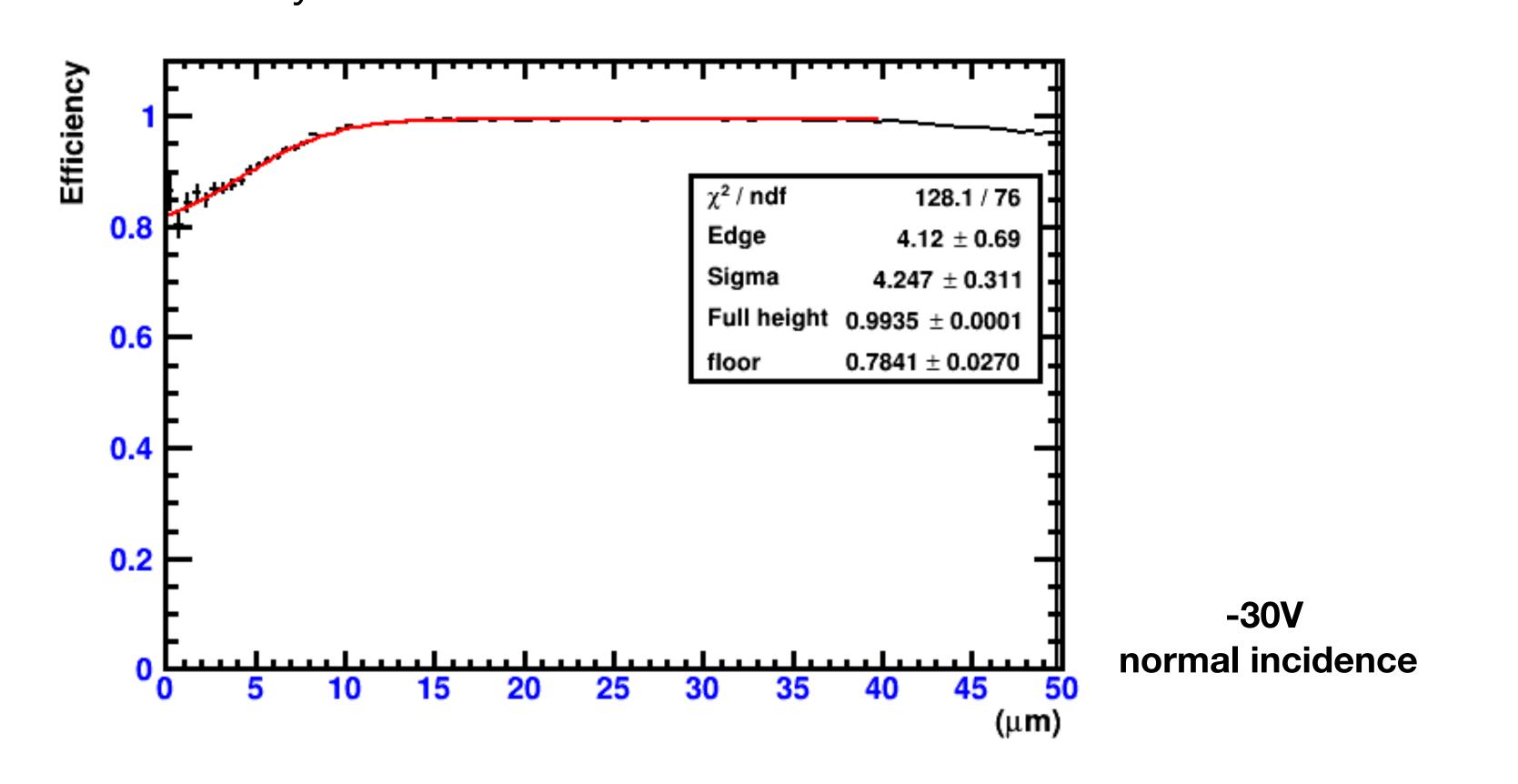

### Testbeam at CERN - unirradiated

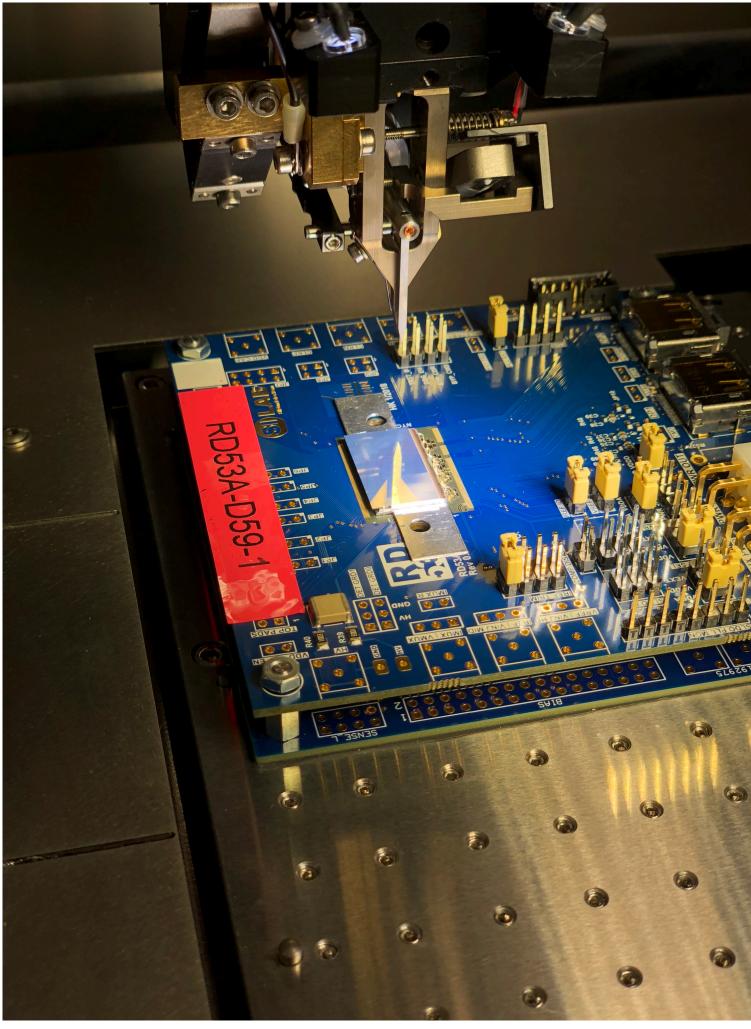

- Tested un-irradiated modules at CERN

- In October/November we tested 1 RD53A module (D59-1)

- Normal incidence

- Data taken at bias voltages from -10V to -120V.

### Testbeam at CERN - unirradiated

• Efficiency >98%

#### • Edge of fit = observed diameter of $4.1 \pm 0.7 \mu m$

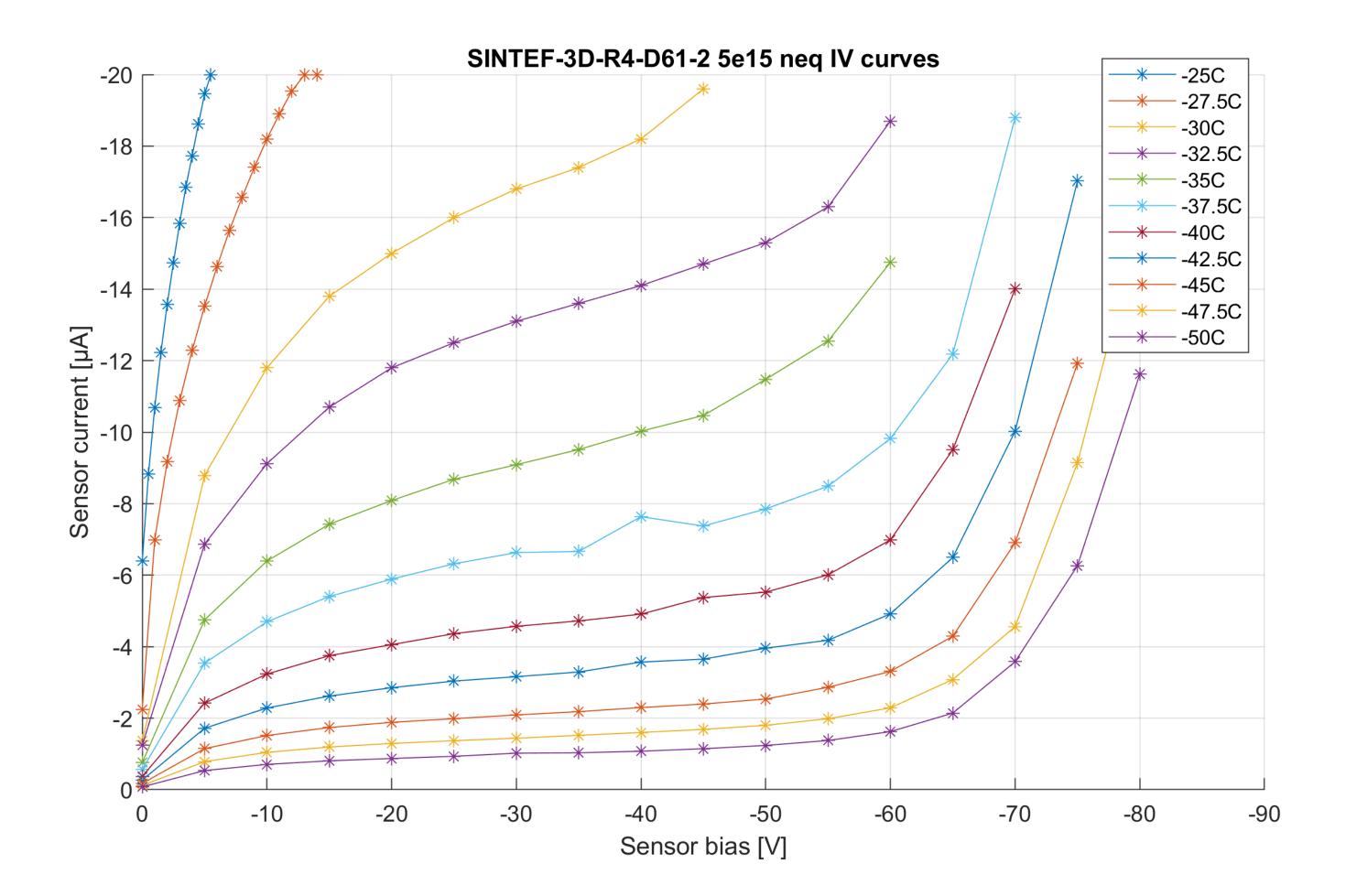

# Irradiation and local tests

- Irradiation at Karlsruhe (Germany) and Josef Stefan institute (Slovenia)

- Nominal fluence 5x10<sup>15</sup> neq/cm2

- IV curves show operational conditions at ~ -40°C

- Module taken to testbeam at DESY in December 2018

- Plan to bring more irradiated modules to DESY in March (Target fluence of 1x10<sup>16</sup> neq/ cm2)

### Testbeam at DESY

- Irradiated module (fluence)  $5x10^{15}neq/cm2$ )

- 100um thick device, 50x50um pixel size

- Electron beam -> more multiple scattering

- Cooling by dry ice down to -50°C

- Tuned to ~1000e<sup>-</sup>

- Bias voltages between -15V and -60V

- Data taken at normal incidence

### Efficiency analysis - irradiated

- Reconstructed using EUTelescope and analysed with TBmon2

- Difference between linear and differential FE

- Overall efficiency for all runs ~94%

#### Efficiency vs Column Distribution DUT 30

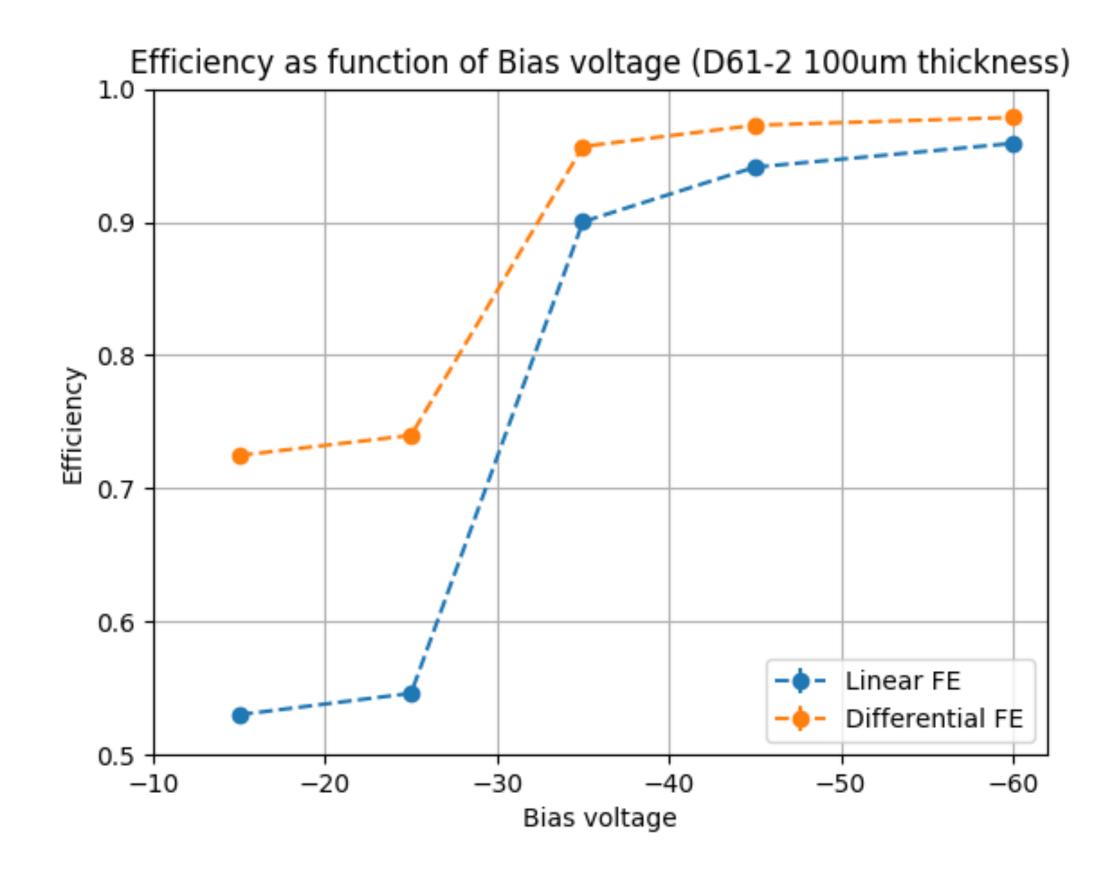

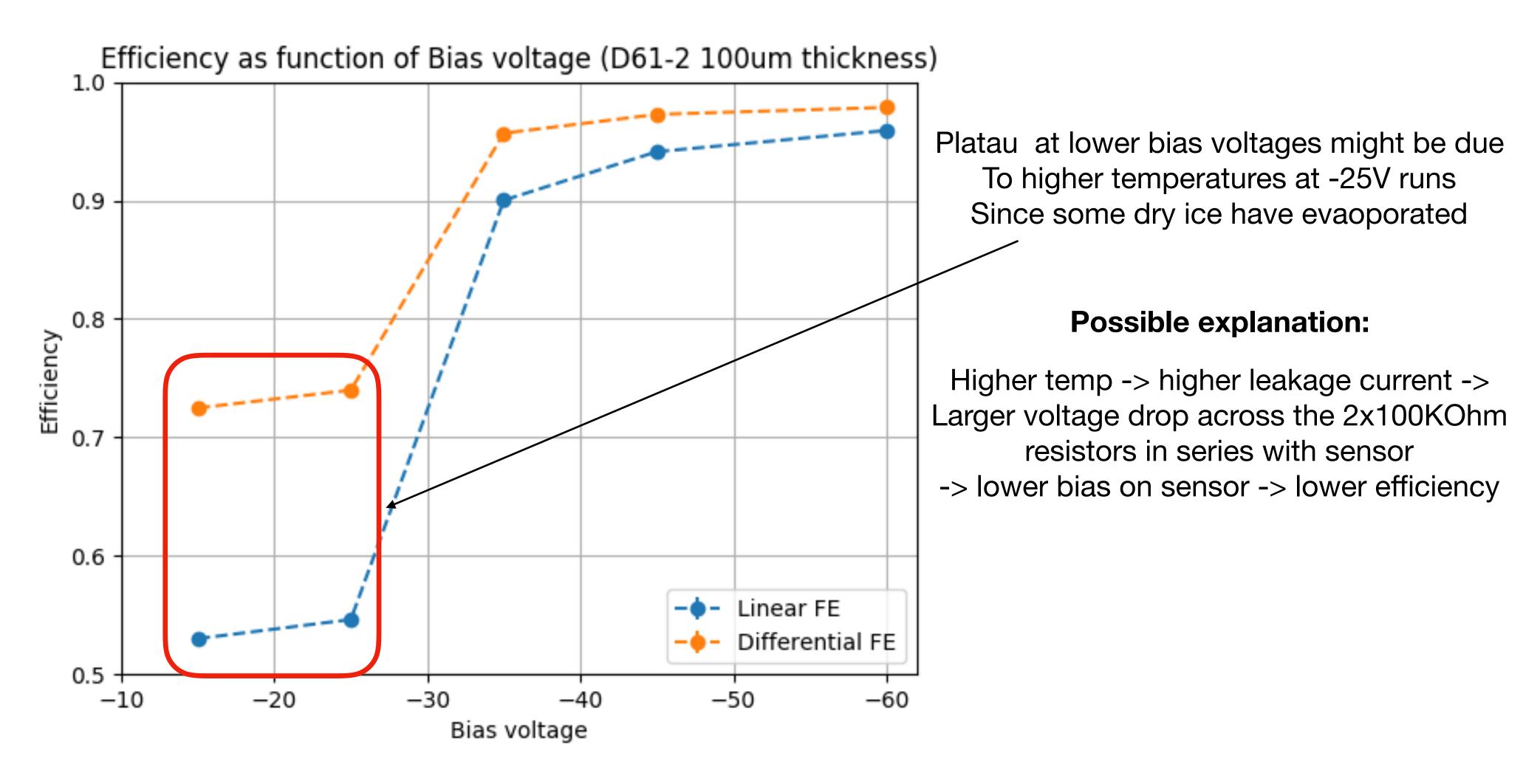

### Efficiency vs. Bias voltage - irradiated

- Difference between linear and differential FE decreases with applied bias voltage

- Efficiency for differential FE >97% at -45V

- Efficiency for linear FE >94% at -45V

## Conclusion and outlook

- SINTEF 3D Run-4 achieved very high test-metal yield

- with UBM

- Successfull flip-chip to FE-I4 and RD53 ASICs

- fluence of 5x10<sup>15</sup>neq/cm2

### **Outlook:**

- Efficiency measurements after fluence of 1x10<sup>16</sup>neq/cm2

- Finishing 3 more Run-4 wafers

- Expect Run-5 results before summer

• SiSi wafer backside thinning workflow implemented, integrated

Promising efficiency measurements of 100um devices after a

# Backup slides

### Backup