STREAM 3rd Annual Meeting, Siddharth Bhat- CPPM

# Main developments at CPPM

Siddharth Bhat CPPM, Marseille ESR-02

### • Milestone 1

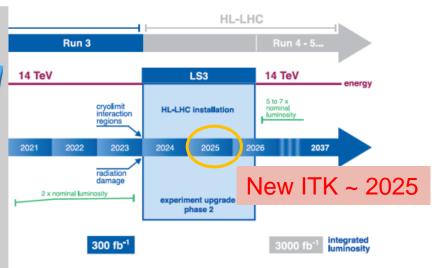

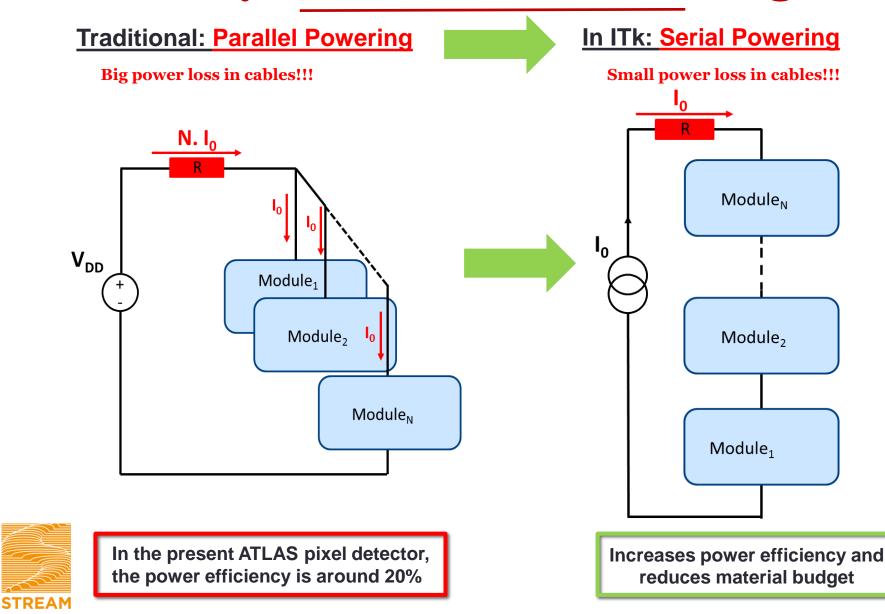

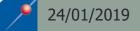

Developments towards a **Serial Powering** implementation in a monolithic CMOS technology for a ATLAS ITk upgrade.

### • Milestone 2

Design and measurements of Single Event Upsets (SEU)

tolerant memories for the ATLAS ITk upgrade.

24/01/2019

CENTRE DE PHYSIQUE DES Particules de marseille

**CPPM**

## ITk tracker

24/01/2019

CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE CPPM

## ITk tracker

**STREAM**

## ITk tracker

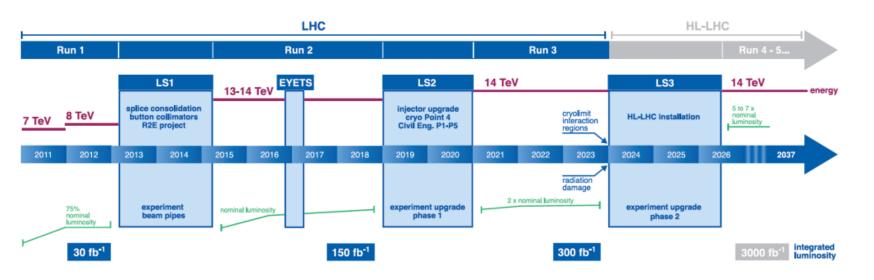

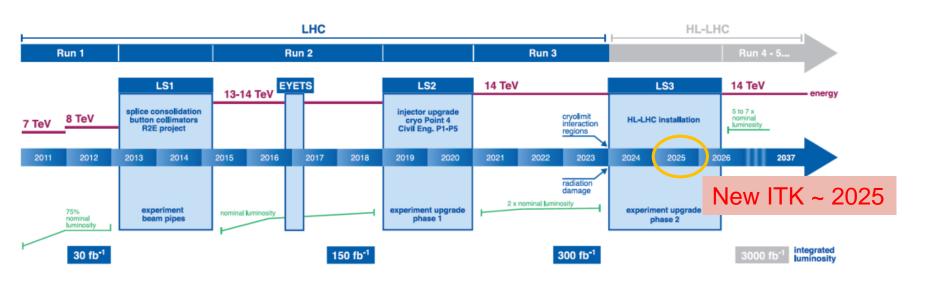

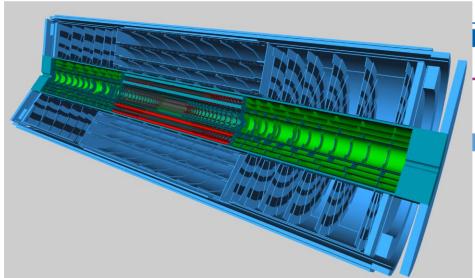

- New tracker for HL-LHC based on silicon only technologies.

- The new pixel detector will have **5 layers (Lo to L4)**.

- Upgraded hybrid detectors using **RD53 IC** will be used for the first 4 layers.

- Possibility of using CMOS Depleted Monolithic Active Pixel Sensors in L4: on-going discussion.

Finalizing and preparing for production.

|   |                                             | ATLAS-HL-LHC     |                  |  |

|---|---------------------------------------------|------------------|------------------|--|

|   |                                             | Outer            | Inner            |  |

| L | Required Time Res.<br>[ns]                  | 25               | 25               |  |

|   | Particle Rate<br>[kHz/mm²]                  | 1000             | 10 000           |  |

|   | Fluence [n <sub>eq</sub> /cm <sup>2</sup> ] | 10 <sup>15</sup> | 10 <sup>16</sup> |  |

|   | Ion. Dose [Mrad]                            | 80               | 1000             |  |

CENTRE DE PHYSIQUE DES Particules de marseille

CPPM

### Aix\*Marseille Why choose Serial Powering?

6

CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE CPPN

Aix\*Marseille

CENTRE DE PHYSIQUE DE Particules de marseill

CPPM

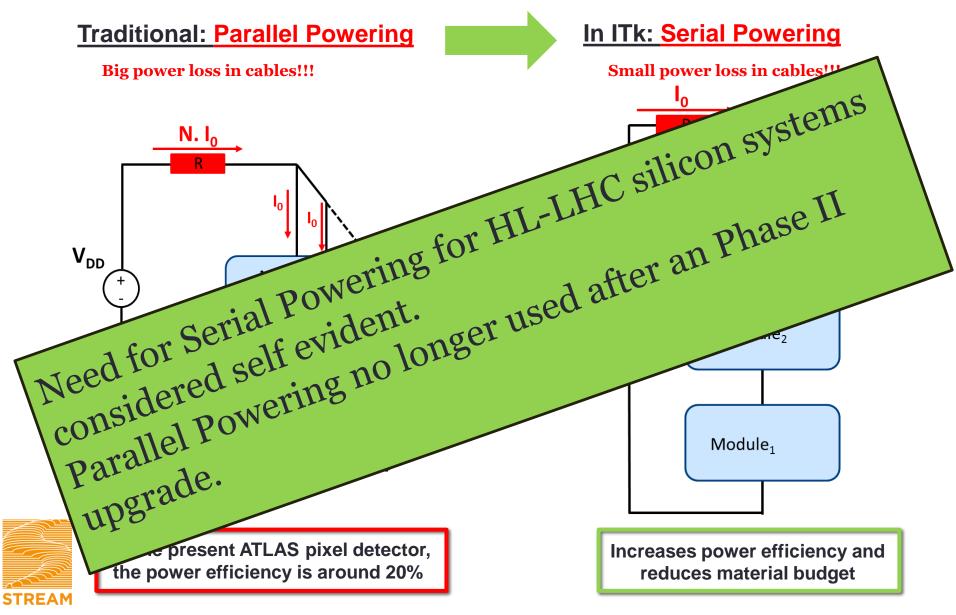

### Shunt-LDO: to power electronics

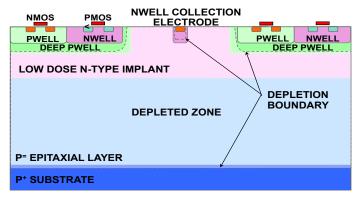

### TJ initial modified process

- Novel modified process developed in collaboration with the foundry.

- Adding a planar **n-type layer** significantly improves depletion under deep pwell.

- Pixel dimensions:

- 36 x 42 µm<sup>2</sup> pixel size

- 3 µm diameter electrodes

- Measured capacitance < 5fF

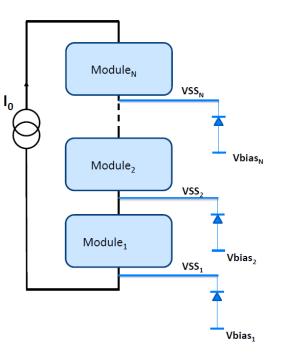

#### In order to polarize the sensor in same way

- $(VSS_N Vbias_N)$  must be constant.

#### **Requirements for Sensor**

HV to pwell = -6 V HV to substrate = -20 V

24/01/2019

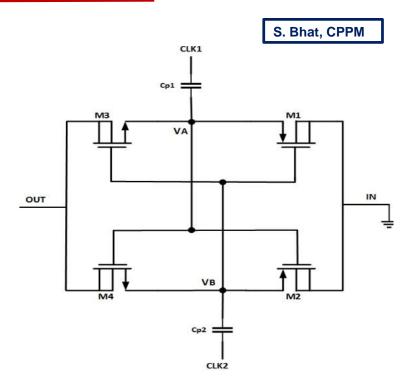

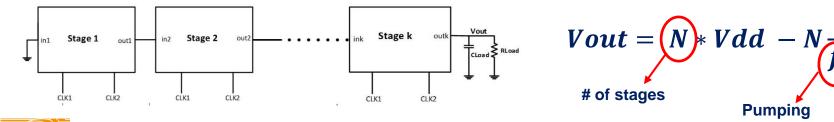

### Charge Pump: to power sensor

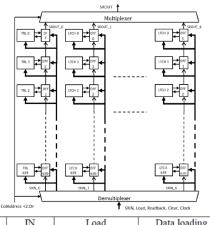

- Cross-coupled architecture of charge pump.

- Two parallel, complementary cross-coupled parts operate in opposite phases.

- The charge pump has several stages.

- The operating frequency is 640 MHz.

frequency

#### **Generating higher voltages**

STREAM

STREAM 3rd Annual Meeting, Siddharth Bhat- CPPM

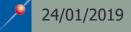

## Simulation results

### **Three test structures:**

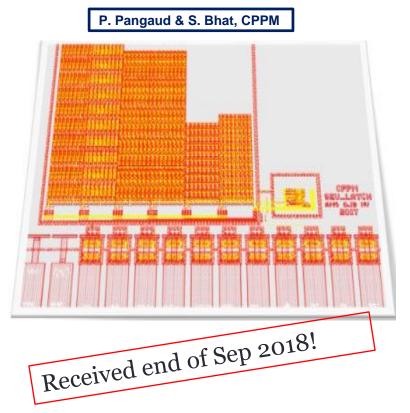

Submitted in August 2018!

- 6-stages charge pump

- 19-stages charge pump

- SWITCH

CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE CPPM

## Milestone 2

STREAM

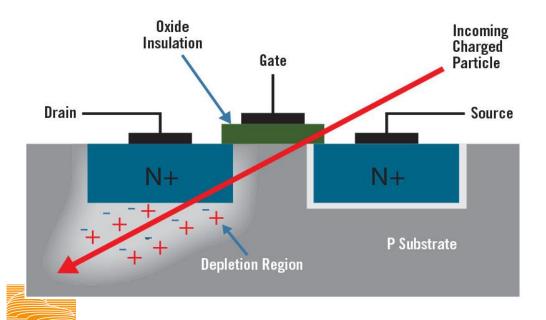

## Single Event Upset (SEU) mechanism

• Energetic particle strikes — Creates ionization path with free e<sup>-</sup> and holes

Creates single event transient (SET)

"Change in memory state"

https://www.lanl.gov/science/NSS/ issue1\_2012/story4full.shtml

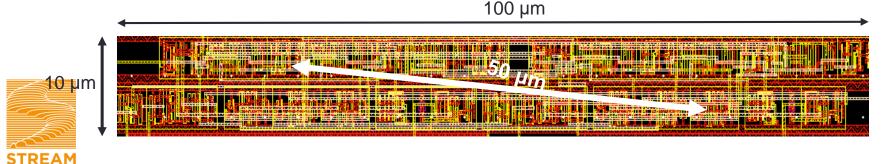

### SEU tolerant memories in AMS 0.18 µm

• Block size : 1.3 mm × 1 mm

#### Different flavors of latches:

- Col6 : DICE Latch "Dual Interlocked Storage Cell"

- Col5 : Standard Cells "LHX1\_HV"

- Col4 : SPLIT Triple redundancy with standard cells

- Col3 : SPLIT Triple redundancy with standard cells

- Col2 : Triple redundancy standard cells

- Col1 : Triple redundancy DICE latch

- Additional Functions

- Columns selector

- Digital buffer output

- DeepNwell and HV

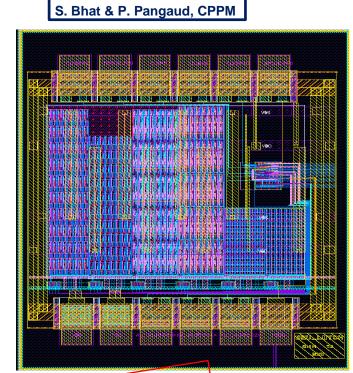

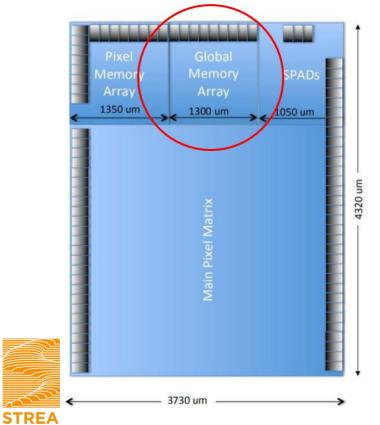

### SEU tolerant memories in TowerJazz 0.18 µm

• Block size : 1 mm × 1.3 mm

#### **Different flavors of latches:**

- Col6 : DICE Latch "Dual Interlocked Storage Cell"

- Col5 : Standard Cells

- Col4 : SPLIT Triple redundancy with DICE cells

- Col3 : SPLIT Triple redundancy with standard cells

- Col2 : Triple redundancy standard cells

- Col1 : Triple redundancy DICE latch

- Additional Functions

- Columns selector

- Digital buffer output

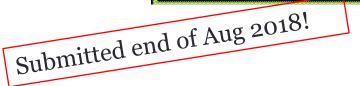

### SEU tolerant memories in LFoundry 0.15 µm

• Block size : 1.3 mm × 1 mm

#### Different flavors of latches:

- Col8 : SRAM

- Col7 : SPLIT Triple redundancy with DICE cells

- Col6 : SPLIT Triple redundancy with standard cells

- Col5 : Triple redundancy with DICE cells

- Col4 : Triple redundancy with standard cells

- Col<sub>3</sub> : Enhanced DICE Latch

- Col2 : DICE Latch "Dual Interlocked Storage Cell"

- Col1 : Standard Cells

16

- Additional Functions

- Columns selector

- Digital buffer output

24/01/2019

CPPM

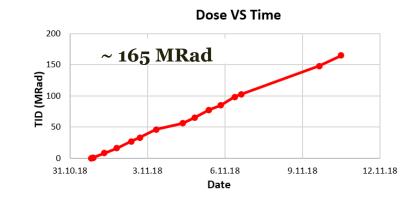

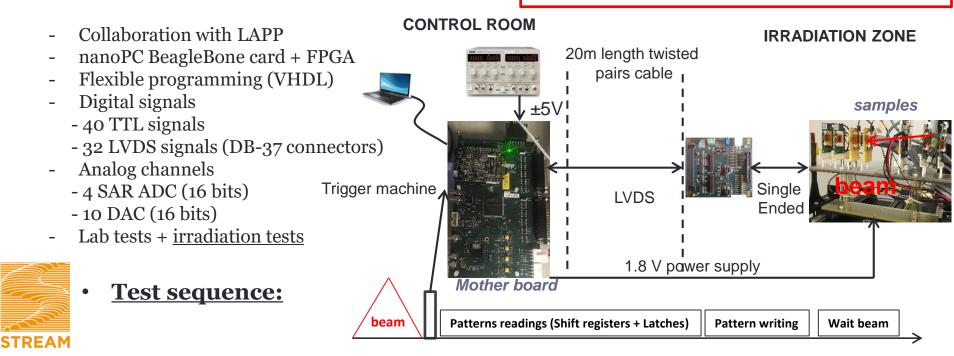

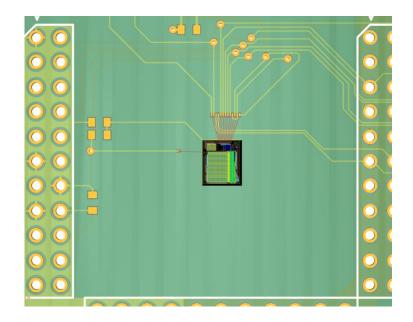

### **Experimental Setup**

- beam size 1cm<sup>2</sup>

- mean dose rate 1.1 MRad/hr

- TID: 165Mrad

- exposure time 10 days

- 2 AMS chips were installed

#### Mother board V2

Dose does not affect the behavior of the AMS SEU chip

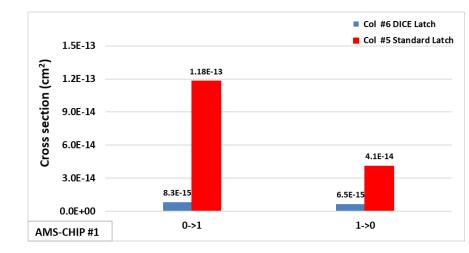

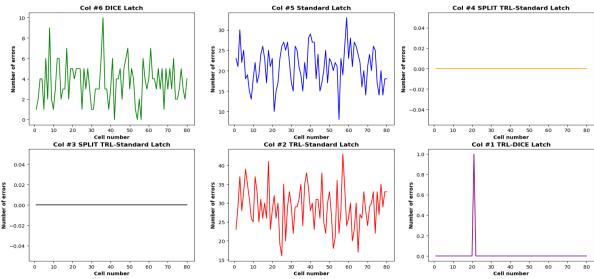

### DICE test results

- We stored enough data to extract an acceptable statistic for SEU.

- 80 cells per type of latch and we reached a spill number > 10000.

- Both the chips show similar behavior under the beam.

- Cross section of the standard latch ~ 66.5 E-15 cm<sup>2</sup>

- Cross section of DICE latch <u>~ 4.7 E-15 cm<sup>2</sup></u>

DICE is x 15 more robust than the Standard Latch

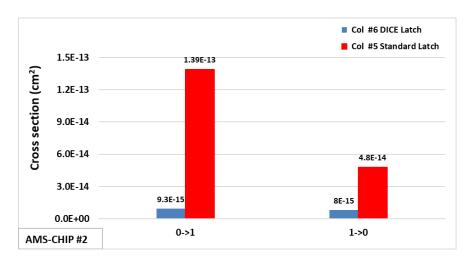

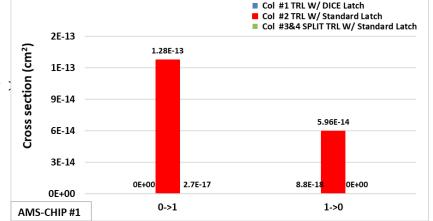

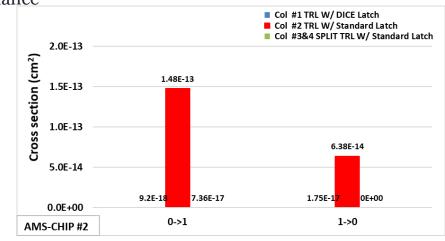

### TRL versions

**TRL with standard latch**

TRL with DICE latch

SPLIT TRL with standard latch

- 3 TRL versions have been designed and tested at CERN.

- TRL with standard latch.

- 2<sup>nd</sup> version with DICE latch.

- 3<sup>rd</sup> version: triplication of the standard latch and increasing the distance between a minimum distance between 2 bits (~50 μm).

### TRL test results

- We stored enough data to extract an acceptable statistic for SEU.

- 80 cells per type of latch and we reached a spill number : 10000.

- Both the chips show similar behavior under the beam.

- Cross section of the TRL W/ standard latch:

<u>~ 14.8 E-14 cm<sup>2</sup> (Defect in the design)</u>

- SPLIT TRL W/ standard latch shows very good performance with the cross section ~7.3 E-17 cm<sup>2</sup>

- TRL W/ DICE latch shows very good performance as well with the cross section <u>~ 1.7 E-17 cm<sup>2</sup></u>

TRL W/ DICE is ~x3000 robust than the Standard Latch

### Conclusion

Marseille

- Shunt-LDO Regulator for Electronics :

- The block is able to generate constant voltage of 1.8 V upto 1.5 A of input current for Serially Powering CMOS modules in ATLAS ITk .

- A test chip was submitted in a MPW submission in Aug 2018.

- Charge Pump for Sensor Bias :

- From the simulations  $\rightarrow$  2 versions of the charge pump circuit show stable response wrt sensor leakage current **upto 500 \muA**.

- SEU Radiation Hard Cells :

- Designed Single Event Upset tolerant test chips in AMS/TJ/LF technologies in order to study the different architectures for various technologies.

- From the measurements of AMS, the designed DICE latch showed very promising results compared to standard latch.

- Keeping the area almost same as standard latch, the **DICE is** ~ **15x immune to SEU.**

- Recently, submitted the 2 SEU test chips in a MPW submission in TJ and LF technology.

### Outlook

- Testing of Shunt-regulator and charge pump test chips in a Serial Powering .

- Testing of SEU test structures in TJ and TSI technologies under the proton beam.

### **Backup**

STREAM 3rd Annual Meeting, Siddharth Bhat- CPPM

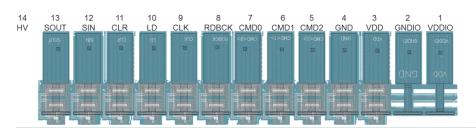

# ATLASpix2 and Test Board

23

Aix+Marseille

| LD    | IN | Load     | Data loading                  |

|-------|----|----------|-------------------------------|

| CK    | IN | Clock    |                               |

| RDBCK | IN | ReadBack | Latches data<br>loading in SR |

| CLR   | IN | Clear    | Reset                         |

STREAM 3rd Annual Meeting, Siddharth Bhat- CPPM

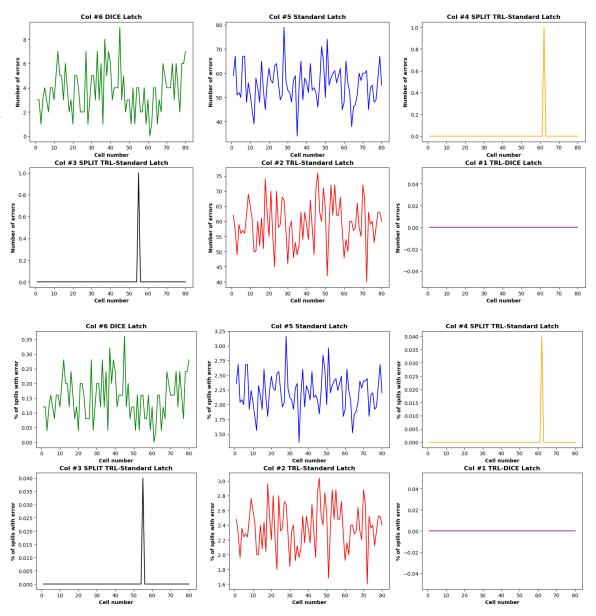

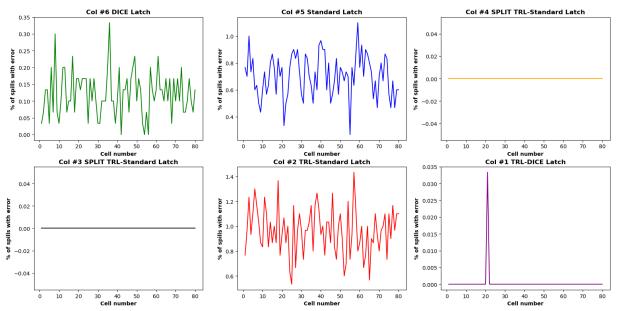

### Errors with pattern all "0" for Chip #2

- # errors VS the cell # is shown.

- Col#5 and col# 2 shows similar behaviour.

- # acquisitions : 2500

- # spills : 2500

- Col #1,#3, #4 are very robust.

% spills W/ errors VS cell # is shown.

Aix\*Marseille

24

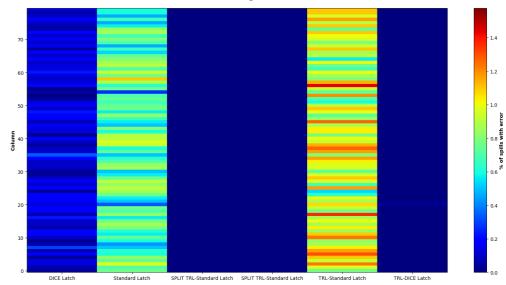

### Errors with pattern all "1" for Chip #2

- # errors VS the cell # is shown.

- Col#5 and col# 2 shows simil behaviour.

- # acquisitions : 3000

- # spills : 3000

- Col #1,#3, #4 are very robust.

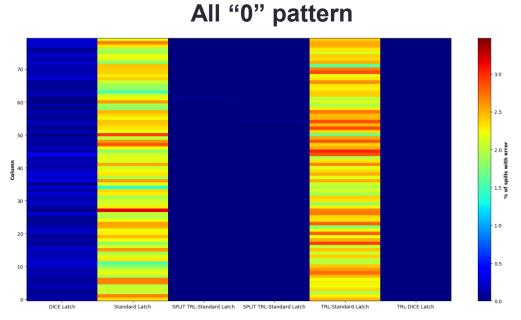

### Error mapping for all "0" and all "1" for chip#2

- # errors VS the cell # is shown.

- Col #5 and col # 2 shows similar behaviour.

- # acquisitions > 3000.

- # spills ~ 3000

- Error variation between DICE and standard latch can be seen.

- Col #1, #3, #4 are very robust.

Aix\*Marseille

26

All "1" pattern

#### CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE CPPM

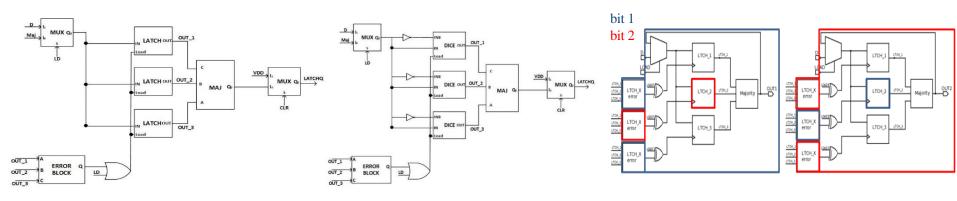

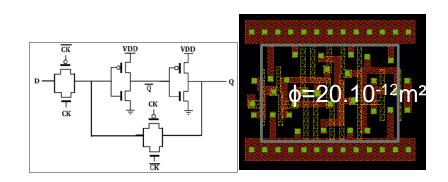

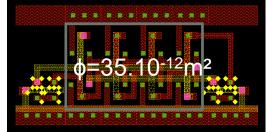

# Latch(s) description

- Standard cell "LHX1\_HV" from the CORELIB\_HV Lib

- Active area  $\phi = 20.10^{-12} \, \text{m}^2$

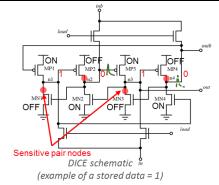

- DICE "Dual Interlocked Storage Cell" cell

- DICE latch structure is based on the conventional cross coupled inverters: Active area

- The charges deposited by a ionising particle strike one node can't be propagated due to the stability of this architecture.

- If 2 sensitive nodes (corresponding to the OFF transistors drain area) are affected simultaneously, the immunity is lost and the DICE latch is upset

STREA(Standard cell "LHX1\_HV" is the reference)

CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE CPPN

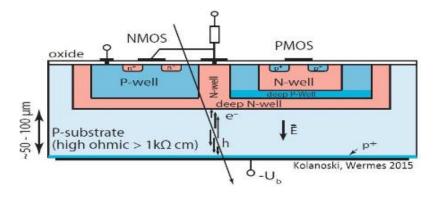

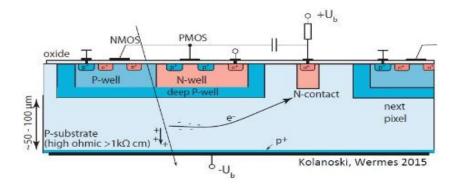

Depleted Monolithic Active Pixel Sensors (DMAPS)

#### 2 lines of development followed : (a) large electrode design / (b) small electrode design

- matured over several years

- radiation hardness (TID & NIEL) proven

- rate capability for L4 (and even L3/L2) shown

- timing close to specs

- $(\rightarrow$  LF / AMS)

- very promising wrt. timing and power

- Vendor already established at CERN

- rate capability for L4 (and even L3/L2) shown

- fast timing due to small C

- radiation hardness -> Sept. 2018

$(\rightarrow TJ)$

CENTRE DE PHYSIQUE DES PARTICULES DE MARSEILLE CPPM

| Column # (Design)              | Area<br>(µm²) | Distance b/w 2 sensitive<br>nodes<br>(D <sub>2</sub> N- μm) |

|--------------------------------|---------------|-------------------------------------------------------------|

| 1. TRL W/ DICE latch           | 400           | 20                                                          |

| 2. TRL W/ standard latch       | 360           | 8                                                           |

| 3. SPLIT TRL W/ standard latch | 500           | 50                                                          |

| 4. SPLIT TRL W/ standard latch | 500           | 50                                                          |

| 5. Standard latch              | 20            | -                                                           |

| 6. DICE latch                  | 30            | 3.5                                                         |