# Bias circuit and FE design for small electrode monolithic sensors

Francesco Piro ESR 12 Sv. Heinz Pernegger CERN EP-ADE-ID

- TowerJazz 180nm technology

- Malta Powering scheme

- New DAC concept

- DACs implementations

- Voltage DAC

- Current DAC

- FE simulations

- Threshold dispersion and ENC

- Training and courses

# Sensor in the TowerJazz 180nm technology

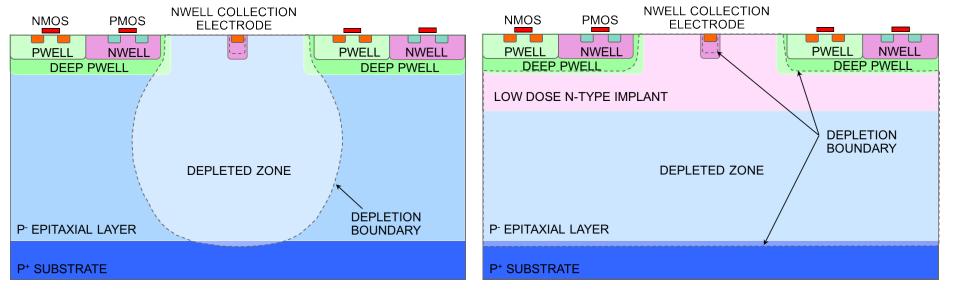

#### STANDARD PROCESS

**Small collection electrode** design with high resistivity (> 1 k $\Omega$  cm) p-type epitaxial layer (25  $\mu$ m  $\rightarrow$  MIP ~1500 e<sup>-</sup>)

Deep p-well shielding n-well to allow full CMOS

**Reverse bias** (~6 V): reduce input capacitance and increase depletion volume

#### MODIFIED PROCESS

Adding a **planar n-type layer** to improve depletion under the deep p-well near the pixel edges

A fully depleted epitaxial layer results in faster charge collection and **better radiation tolerance** No circuit or layout changes required

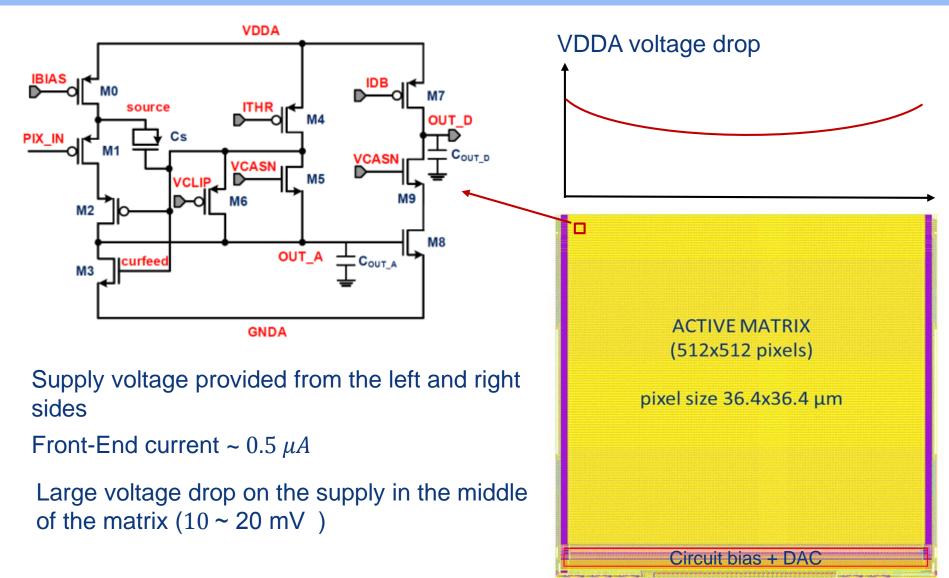

# **MALTA Powering scheme**

# **MALTA DACs concept**

2 *cm*

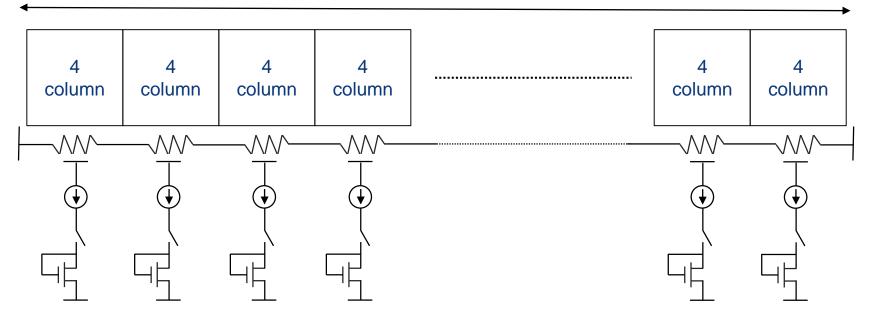

Modular design:

- Current and voltage DACs distributed at the bottom of the column

- -Number of bits depends on Matrix width

- 1 unit every 4 columns

512 columns / 4 = 128 => 2<sup>7</sup> => 7 bit

- Not flexible layout to increase DAC resolution or number of DACs

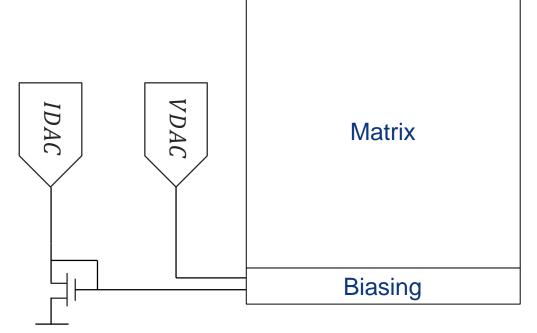

# **MiniMALTA DACs concept**

Non Modular design:

- Local DACs implemented to save space  $(\sim 5 x)$

-Number of bits independent from the Matrix width (8 bits DACs implemented) -Easy to increase the number of DACs and biasing lines towards the FE -Flexible layout

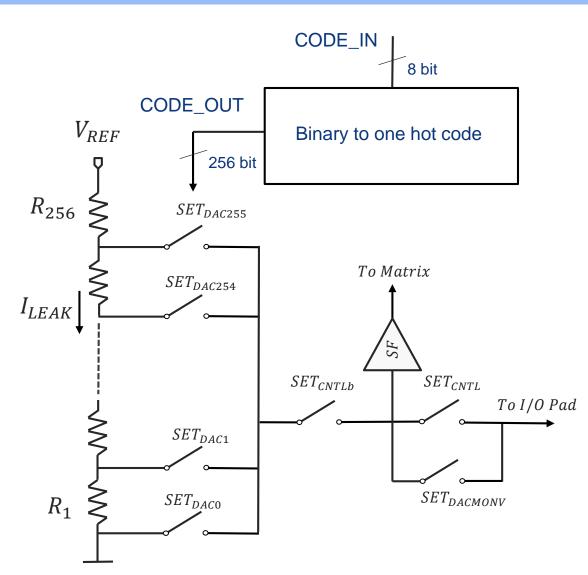

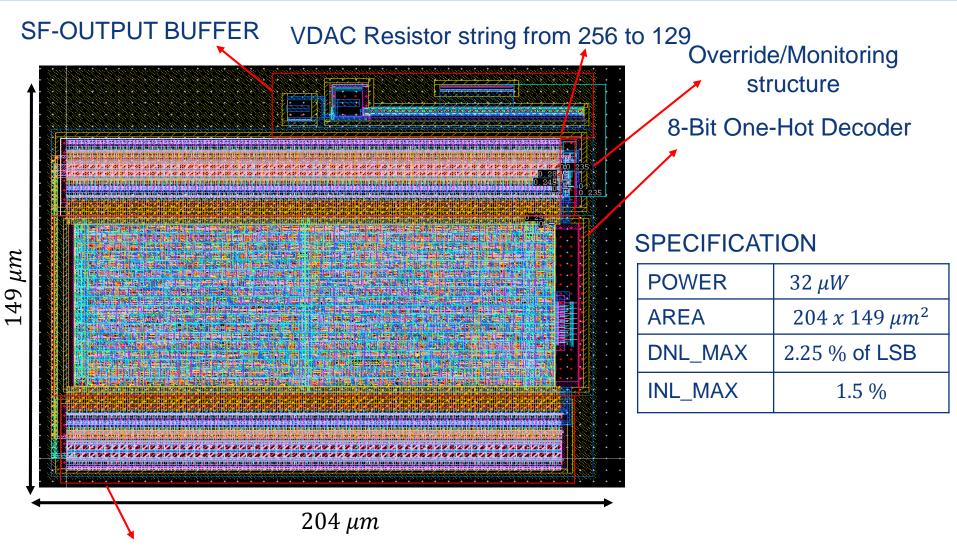

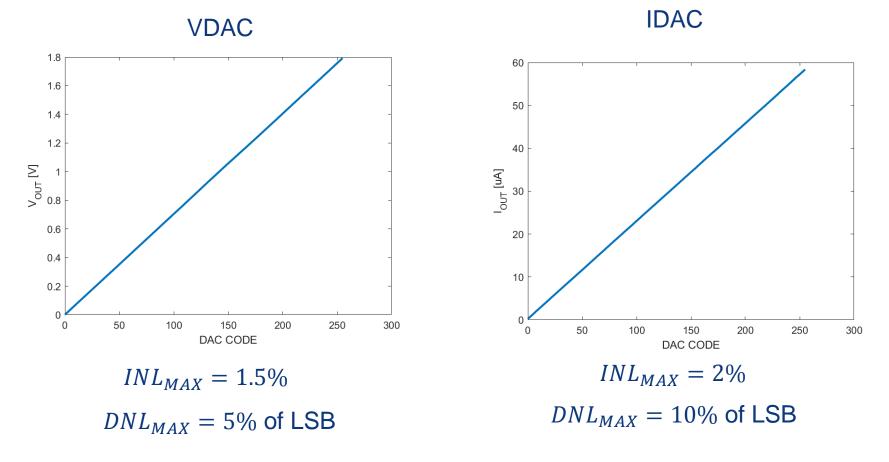

# **Voltage DAC – Implementation**

One Hot Encoding 8 *bits* resolution (0 ~ 1.8 V)  $LSB \approx 7.03mV$ One resistor for each DAC to guarantee a better modularity.

**Resistor string**

Possibility to override and monitoring the DACs.

VDACs outputs buffered to cope with the leakage current in the pixels.

#### **Voltage DAC – Structure layout**

VDAC Resistor string from 128 to 1

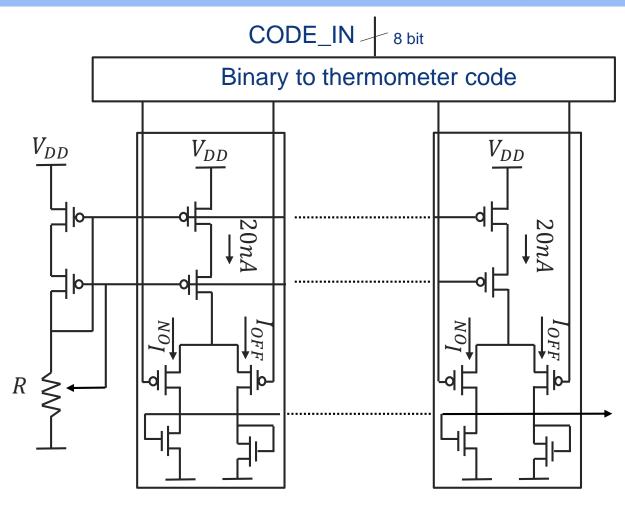

#### **Current DAC - Implementation**

pMOS current source array

Thermometer encoding

8 bits resolution (0 – 5uA) LSB  $\approx 20 nA$

Cascode to guarantee a better linearity

TID effects depend on biasing voltage: same load on both  $I_{ON}$  and  $I_{OFF}$ .

Possibility to use it with a Bandgap reference for PVT independence.

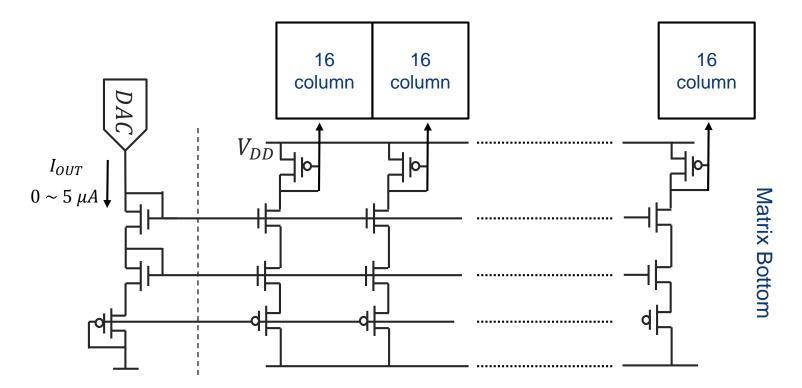

# Last biasing stage - Implementation

Last biasing stage distributed under the matrix as in MALTA. Cascode to guarantee a better linearity.

PMOS on ground to have ground uniformity despite voltage drops.

Biasing structure distributed at the bottom of the matrix all over the matrix.

Additional current mirrors to adjust the current ranges for the different biasing currents.

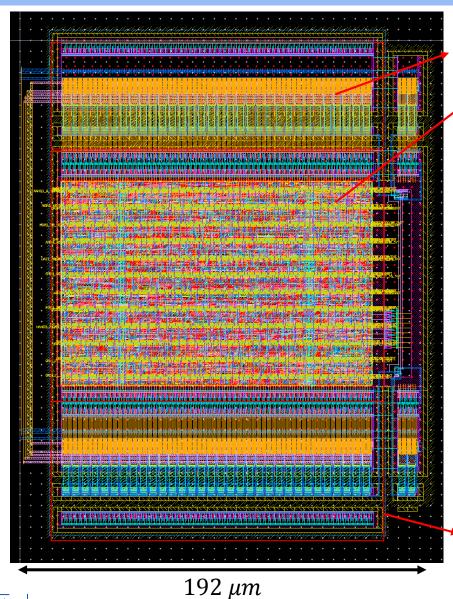

#### **Current DAC – layout**

IDAC Current sources from 256 to 129

8-Bit Thermometer Decoder

Same current reference used for all the IDAC on the chip

#### SPECIFICATION

| POWER   | 14 μW                     |

|---------|---------------------------|

| AREA    | $192 \ x \ 237 \ \mu m^2$ |

| DNL_MAX | 5.6 % of LSB              |

| INL_MAX | 3 %                       |

IDAC Current sources from 128 to 1

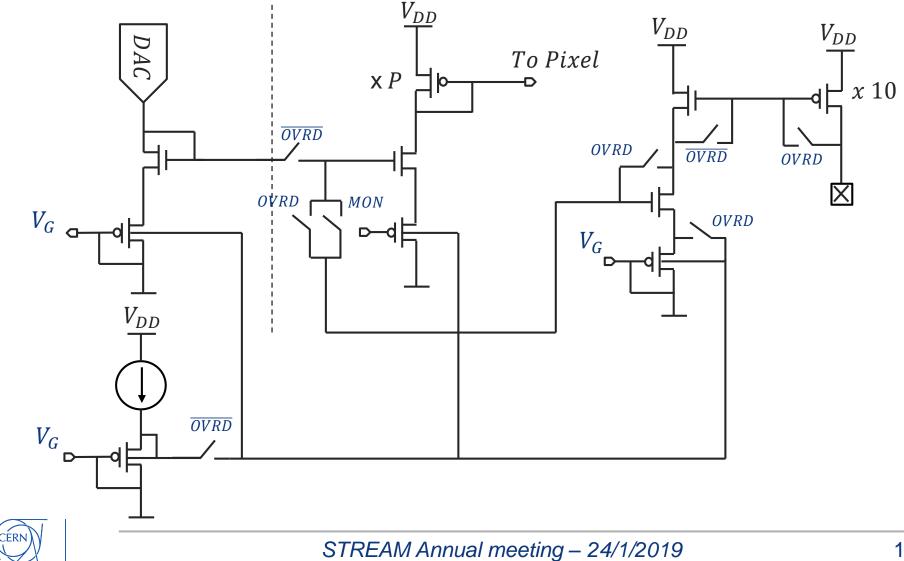

#### **OVERRIDE-MONITORING**

Circuit for override and monitoring implemented under the PADs, through a system of switches.

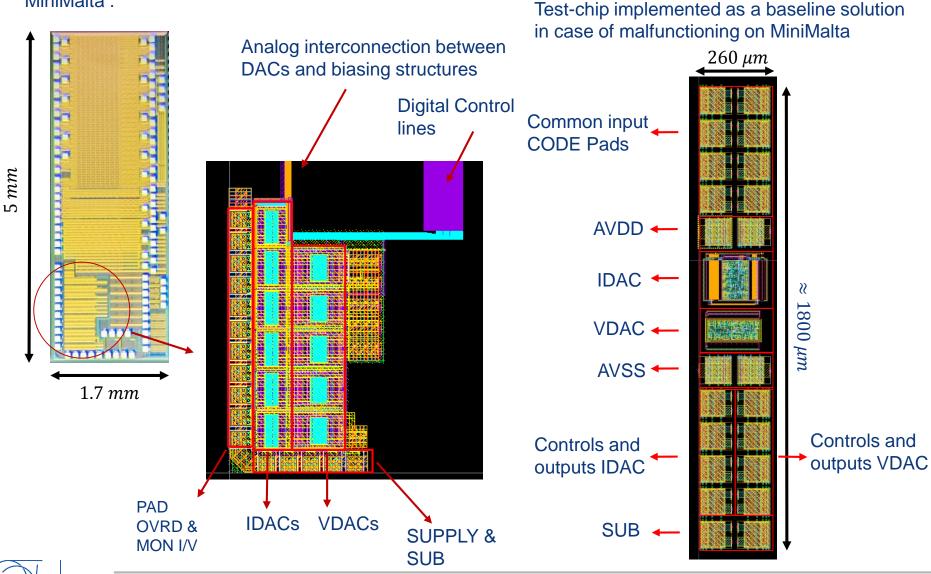

# Integration in MiniMALTA and testchip

#### MiniMalta:

#### **DACs testing**

MPW submitted in August 2018 and arrived on 7<sup>th</sup> January 2019.

MiniMalta DACs tested in monitoring mode.

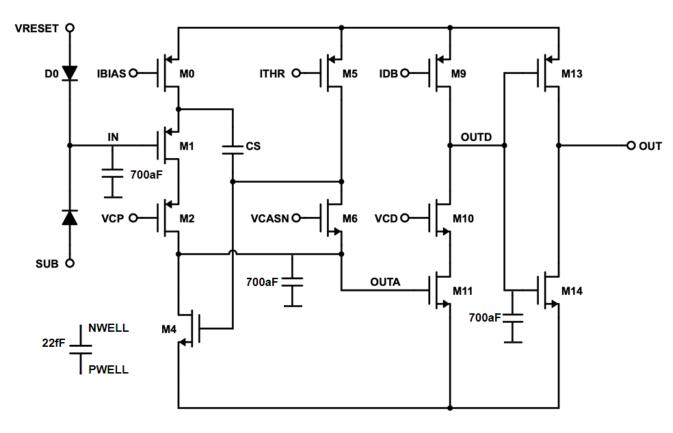

# **FE developments**

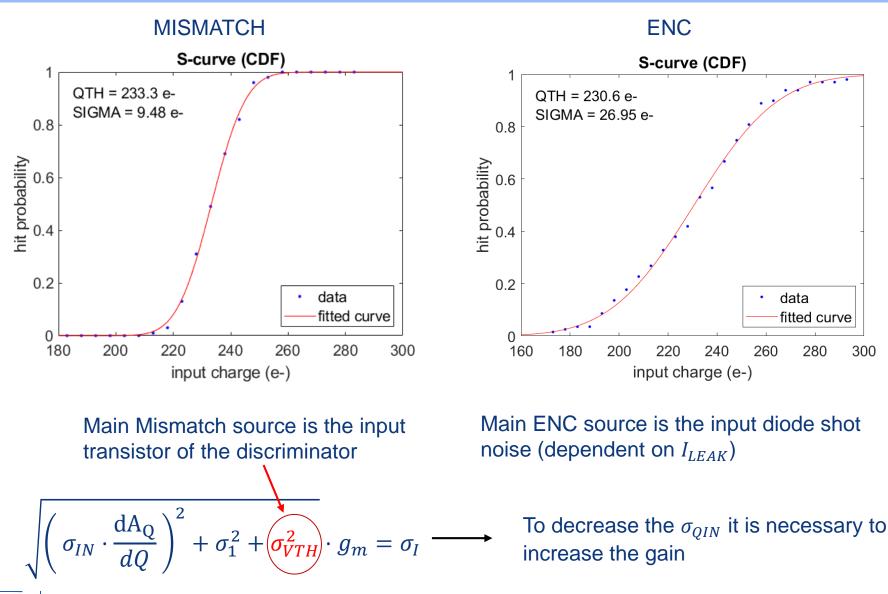

FE simulations to improve Mismatch (threshold uniformity) and ENC (Equivalent Noise Charge)

FE schematic and configuration as in MALTA.

Parasitic routing capacitances and well capacitances in test-bench cell.

Simulations performed both in diode and PMOS reset case (with PSP model to have a better model of the noise)

Simulation performed with  $I_{LEAK} = 200 \ pA$  (typical value after irradiation).

#### **FE developments**

CERN

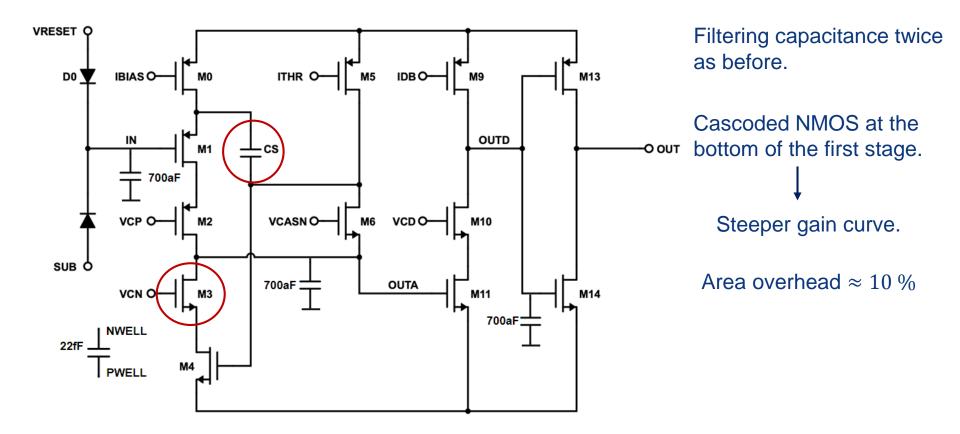

#### **New FE schematic**

#### **New FE results**

#### S-curve (CDF) S-curve (CDF) 1 QTH = 233.3 e-QTH = 230.6 e-SIGMA = 9.48 e-SIGMA = 26.95 e-0.8 0.8 hit probability 9.0 9.0 hit probability 0.6 0.4 0.2 0.2 data data • fitted curve fitted curve 0 0 180 200 220 240 260 300 240 280 160 180 200 220 260 280 300 input charge (e-) input charge (e-) S-curve (CDF) Noise S-curve for front-end 1 QTH = 99.88 e-QTH = 97.1 e-SIGMA = 8.59 e-ENC = 4.01 e-0.8 0.8 hit probability 9.0 hit probability 6.0 0.2 0.2 data • data • fitted curve fitted curve 0 0 80 90 100 110 120 60 80 100 120 140 input charge (e-) input charge (e-)

ENC

#### **Training and Courses**

#### **EPFL courses:**

-Advanced Analog CMOS IC Design -PLL and Oscillators

#### **Europractice course at IMEC, Leuven:**

Digital physical implementation flow (feat low power)

**PRINCE2 at The Academy, Eindhoven:**

Intensive course on project management

Training course on Entrepreneurship at CERN, Geneva:

Course on business planning and modelling

#### Thank you for the attention