1

### Integration of a Crosspoint switch in the COMPASS DAQ in 2018

D. Steffen

- 1. Motivation and Concept of the Switching Network Topology

- 2. Hardware Design and Implementation of the Crosspoint Switch

- Hardware Layout

- Software Developments

- 3. Performance in 2018 DY run and Outlook

### Contents

- 1. Motivation and Concept of the Switching Network Topology

- 2. Hardware Design and Implementation of the Crosspoint Switch

- Hardware Layout

- Software Developments

- 3. Performance in 2018 DY run and Outlook

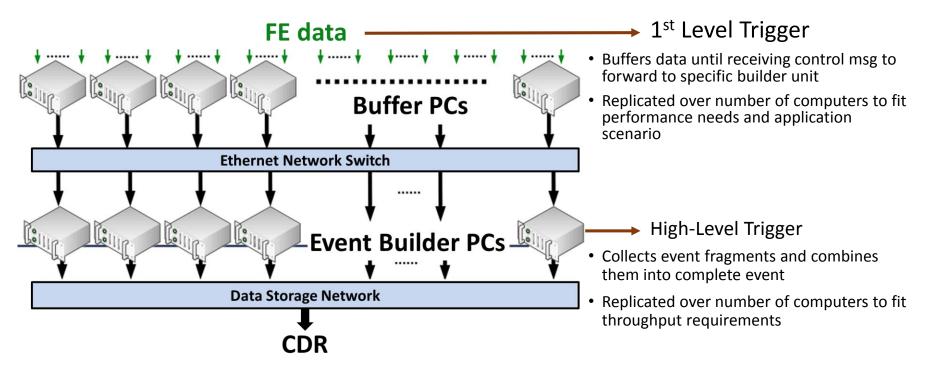

# **Traditional Event Building**

Event Building(EB): combination of logically connected, but physically split data fragments

Sophisticated traffic shaping to optimize throughput of EBnetwork switch (buffer utilization and data rate) and load on EB computers

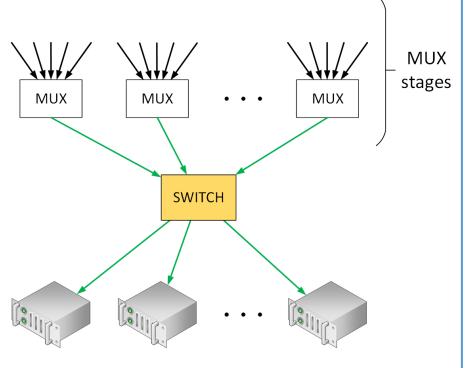

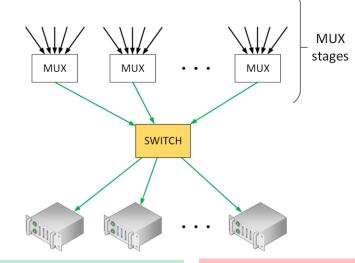

### Hardware Event Building

- Usage of FPGAs and exploiting its properties:

- Parallel processing

- Pipeline architectures

- Continuation of the pipeline architecture in FEE

- o Collecting of all data in one FPGA-module

- Optional multiplexing stages to reduce number of incoming links

- Distribution of fully assembled events to different computer nodes

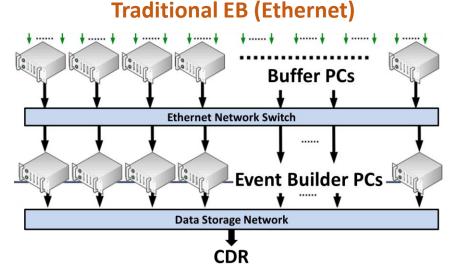

### Traditional vs Hardware EB

#### **Advantages**

- Easy integration of redundancy elements (traffic shaping according to load on nodes)

- Usage of massproduced components and standards

#### **Disadvantages:**

- Throughput limited by EB-network switch

- Inefficient usage of max. bandwith due to:

- Improper comm. pattern (N senders -> 1 receiver) => network congestion

- Data overhead due to addressing etc.

Hardware EB

#### Advantages:

- Independence of network switch

- Efficient usage of link bandwidth (no addressing etc.)

- High reliability

#### **Disadvantages:**

- Strong dependence on reliability of network nodes (no rerouting possibility in case of hardware failure)

- No possibility for dynamic network optimization (e.g. load balancing)

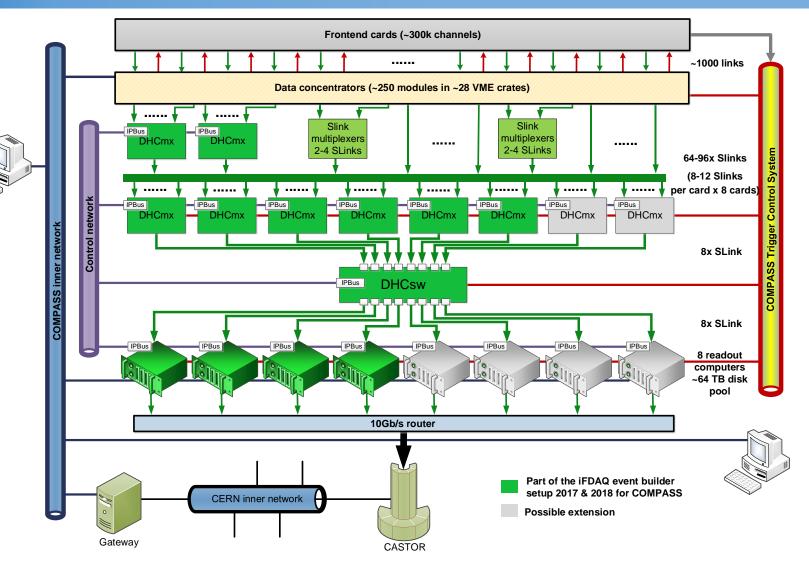

### iFDAQ setup in 2018 DY

CERN

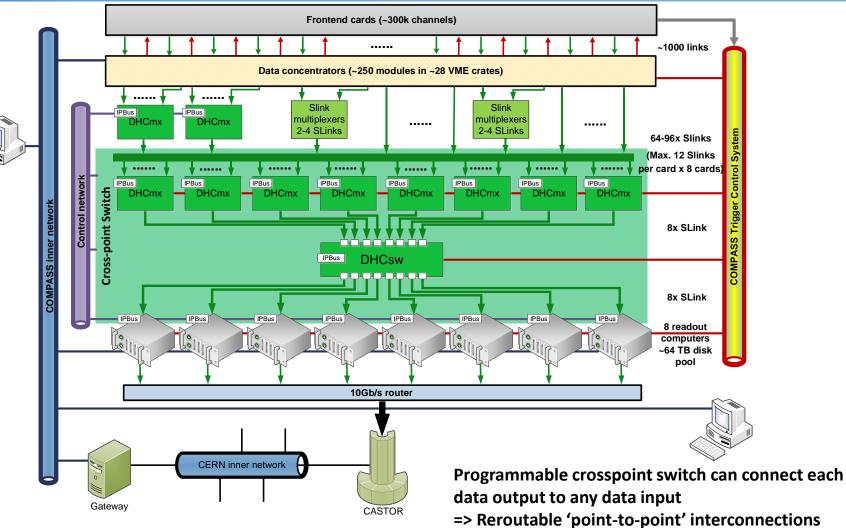

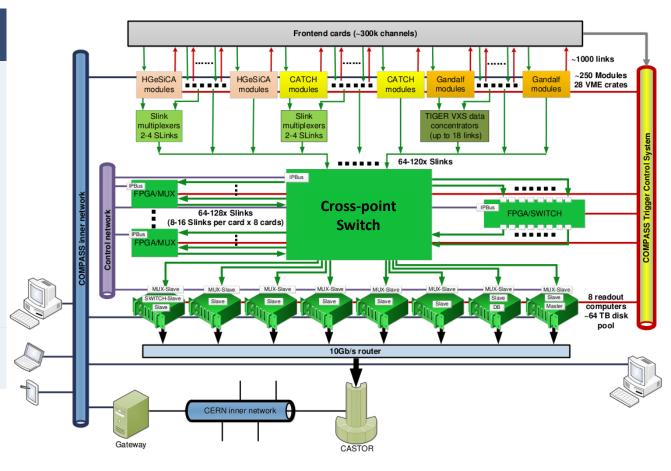

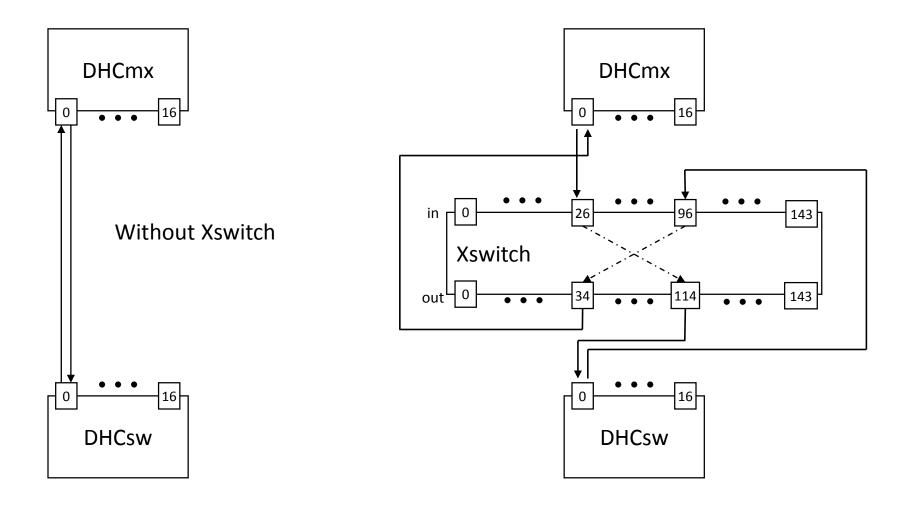

# Switching Network Topology

### **Crosspoint Switch - Integration**

### **Cross-point Switch**

#### $\circ$ connects:

- FE electronics

- DHCmx modules

- DHCsw module

- Spillbuffers

#### ○ purpose:

- Ease of load balancing

- System redundancy to compensate hardware failures

- ⇒ provides fully customizable network topology

### Contents

- 1. Motivation and Concept of the Switching Network Topology

- 2. Hardware Design and Implementation of the Crosspoint Switch

- Hardware Layout

- Software Developments

- 3. Performance in 2018 DY run and Outlook

Dominik Steffen | DAQFEET | 11/02/2019

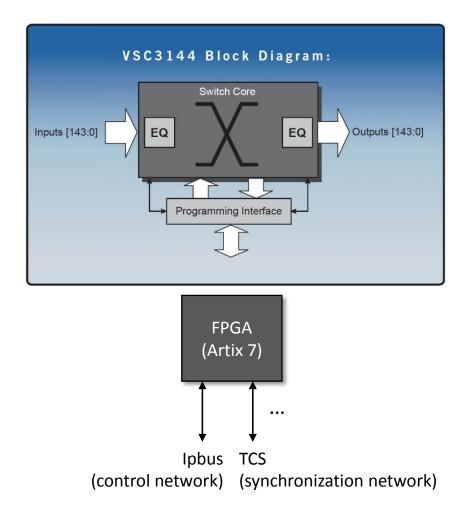

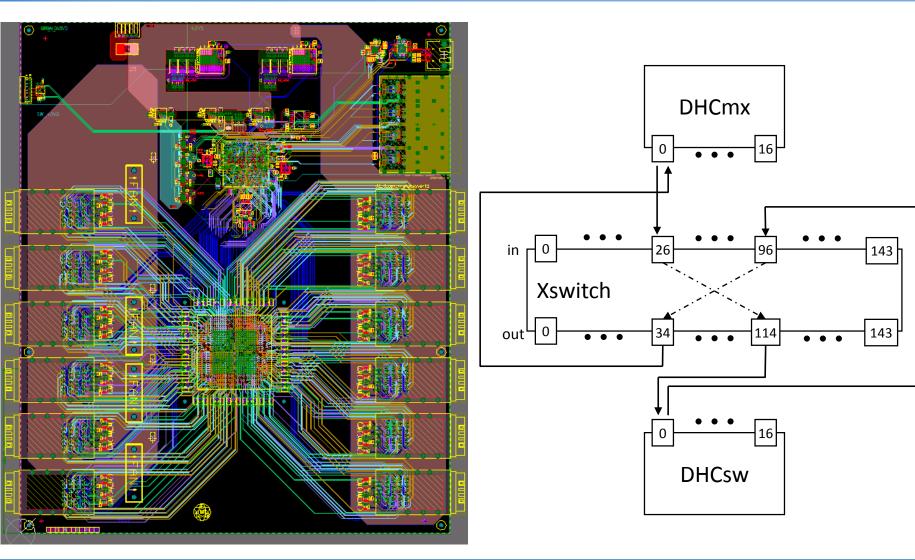

144 x 144 strictly non-blocking cross-point switch

Hardware: Vitesse VSC3144

- Up to 6.5 Gbps bandwidth per port

- No registers used in data path i.e. asynchronous data path => no restrictions on the phase, frequency, or signal pattern of any input (protocol independent)

- 45mm x 45mm 1072-pin BGA package

- Core programming on port-by-port basis

OR simultaneous issuing of multiple

queued assignments (low latency: ns)

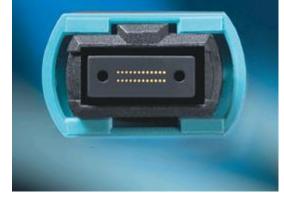

### **MPO** connectors

- High density fiber technology necessary

→ Multi-fiber Push-On technology

- Easy installation due intuitive push-pull latching sleeve mechanism

- MPO harness cable to interface with LCstandard used so far in iFDAQ

### 24 Fibers MPO/MTP Connector

# Crosspoint Switch – Hardware Design

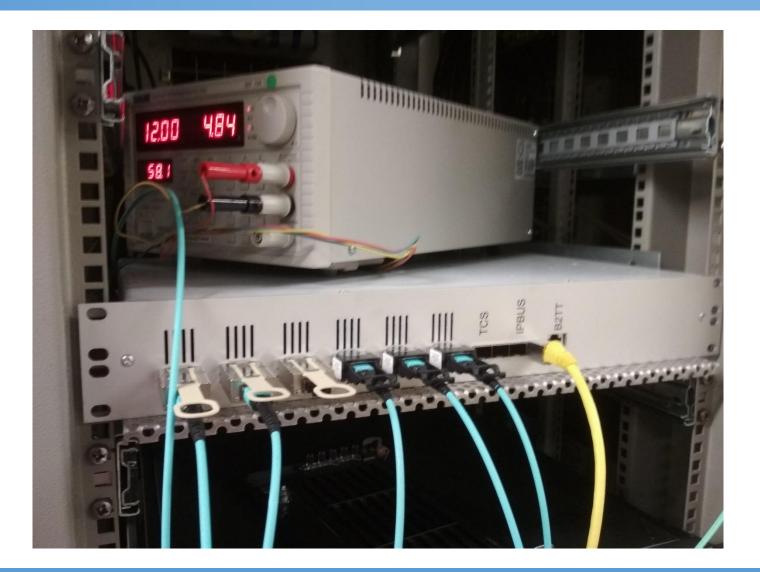

### **Crosspoint Switch Components**

$\circ$  interfaces:

- 12 x 12 channel CXP transceiver (MPO fiber connectors)

- Ethernet for IPbus

- JTAG

- TCS (Trigger Control System) receiver

### $\odot$ Switching and Control:

- Vitesse VSC3144-02 fully configurable 144x144, asynchronous, 6.5 Gbps crosspoint switch

- Xilinx Artix-7 FPGA for switch control and monitoring

#### Interface FPGA – Crosswitch:

- 90 MHz, 11-bit parallel data bus

- Multiple program assignments can be queued and issued simultaneously ⇒ fast programming (<< 1us)</li>

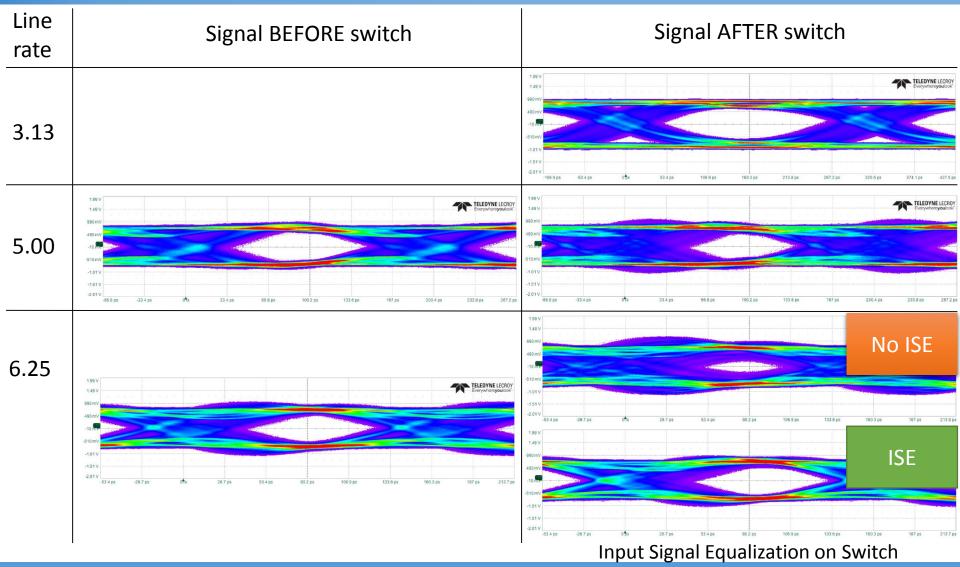

### **Crosspoint Switch – Signal Distortion**

CERN

# Crosspoint Switch in COMPASS DAQ

# Crosspoint Switch in COMPASS DAQ

# Software Development

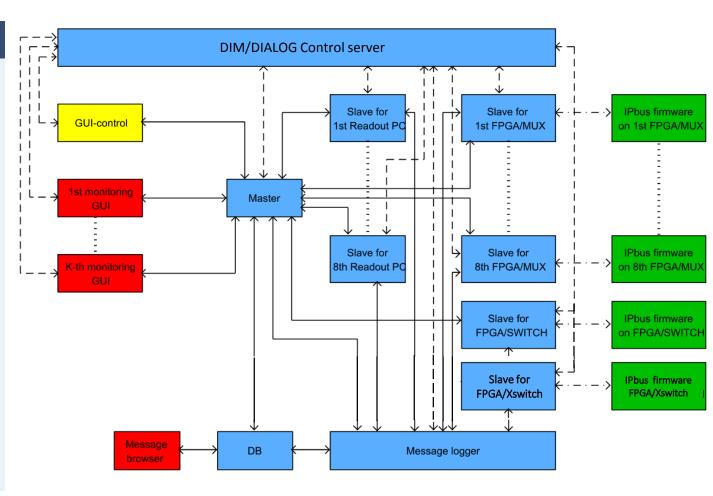

#### **Multilayer System:**

- Master is the main control process

- Slave-control monitors and controls the DHCs (hardware nodes)

- Slave-readout: readout, verification, and transformation of the data

- Runcontrol GUI is a graphical user interface

- MessageLogger stores informative and error messages into the database

- MessageBrowser provides an intuitive access to messages stored in the database

#### Software Operating Mode ERI DB table holding information DB table holding information **Control Slave for** modules $\leftarrow \rightarrow$ Xswitch about module interconnections **FPGA/Xswitch** XswitchUI web configuration interface - • × Xswitch Connections Ports (16) MUX12 SMC12 RE15 🧹 921 R Tools DAQ Module SlaveControl on pccore15 Attached Equipment on cage: 0 10.152.72.230 Port 0 Src-ID: 619 ECAL2 3 Port: 0 Ports (16) 0 2 4 6 8 10 1 3 5 7 9 11 0 2 4 6 8 10 1 3 5 7 9 11 SWITCH SWITCH RE11 CXP 0 CXP 6 / 944 R Port 1 DAQ Module SlaveControl on pccore15 10.152.72.234 Src-ID: 620 ECAL2 4 Port: 0 Port 2 Src-ID: 146 SciFi-L7 Port: 0 SMC01 RE11 Ports (16) 0 2 4 6 8 10 1 3 5 7 9 11 0 2 4 6 8 10 1 3 5 7 9 11 MUX01 CXP1 🧹 945 R DAQ Module SlaveControl on pccore15 Port 3 10.152.72.238 NOTHING CONNECTED Port 0: → 944 SWITCH (Port 0) Disconnect Port 4 0 2 4 6 8 10 1 3 5 7 9 11 0 2 4 6 8 10 1 3 5 7 9 11 Src-ID: 144 SciFi-J\_5 Port: 0 **R** Port 1: ← 2 Mastertime\_1 (Port 0) Disconnect Xswitch Firmware Version 4121830 CXP 2 R Port 2: ← 978 SMUX-Mastertime/Trigger (Port 0) Disconnect Port 5 Src-ID: 618 ECAL2\_0 Port: 0 R Port 3: ← 977 SMUX-Trigger1 (Port 0) Disconnect Port 6 R Port 4: ← 976 SMUX-Trigger2 (Port 0) Disconnect 0 2 4 6 8 10 1 3 5 7 9 11 0 2 4 6 8 10 1 3 5 7 9 11 Src-ID: 145 SciFi-J\_6 Port: 0 61 °C СХР З R Port 5: ← 981 SMUX-Scalers (Port 0) Disconnect Port 7 **R** Port 6: ← 998 SMUX-SciFI-J-1 (Port 0) Disconnect Port: 0 Src-ID: 148 SciFi-J/D\_1 **R** Port 7: ← 997 SMUX-Veto (Port 0) Disconnect Port 8 0 2 4 6 8 10 0 2 4 6 8 10 CXP 4 Src-ID: 740 GEM\_5 Port: 0 1 3 5 7 9 11 R Port 8: ← 996 SMUX-SVS (Port 0) Disconnect 1 3 5 7 9 11 R Port 9: ← 999 SMUX-Scaler (Port 0) Disconnect Port 9 Src-ID: 739 GEM\_4 Port: 0 R Port 10: ← 750 PGEM\_1 (Port 0) Disconnect Port 10 0 2 4 6 8 10 R Port 11: ← -- Select equipment --\$ CXP 5 CXP 11 1 3 5 7 9 11 1 3 5 7 9 11 Src-ID: 960 SciEiBeamMon 2 Port: 0 R Port 12: Not connected. Connect Port 11 R Port 13: Not connected. Connect Src-ID: 985 SMUX-MWPC-A Port: 0 R Port 14: Not connected. Connect R Port 15: Not connected. Connect

#### Dominik Steffen | DAQFEET | 11/02/2019

### Software Operating Mode DB table holding information DB table holding information **Control Slave for** modules $\leftarrow \rightarrow$ Xswitch about module interconnections **FPGA/Xswitch** Powers Xswitch on transition 'Slaves started' $\rightarrow$ 'Configured' No apparent changes for shifter • Sends configuration commands on transition Web Configuration Tool can be used between 'Slaves started' $\rightarrow$ 'Configured' to reconfigure topology without human intervention (Monitors Xswitch module in states: 'Configured', 'Dry Run', and 'Run') **IPbus firmware FPGA/Xswitch**

### Affected DB tables

Existing table

### New tables

| Port connection |         |         |  |  |  |

|-----------------|---------|---------|--|--|--|

| Port out        | Port in | Runtype |  |  |  |

| 357             | 587     | 4       |  |  |  |

| Xswitch connections |     |  |  |  |

|---------------------|-----|--|--|--|

| Port id             | In  |  |  |  |

| 357                 | 892 |  |  |  |

| 587                 | 888 |  |  |  |

| Xswitch pairs |    |     |      |       |  |

|---------------|----|-----|------|-------|--|

| Port id       | In | Out | Cage | Fiber |  |

| 892           | 26 | 34  | 2    | 11    |  |

| 888           | 96 | 114 | 3    | 2     |  |

### Interconnection example

### Interconnection example

### Contents

- 1. Motivation and Concept of the Switching Network Topology

- 2. Hardware Design and Implementation of the Crosspoint Switch

- Hardware Layout

- Software Developments

### 3. Performance in 2018 DY run and Outlook

# Performance during 2018

- First installation attempt in April failed due to wrong mapping

- Step-by-step installation starting from June

- Incidents during run: 2 (over 5.5 months)

- Wrong powering procedure during start-up after power cut led to failing programming of interconnections => Bug fixed in software

- One "unknown" failure => Fixed by reset of the X-switch, not reproducible in the Lab, did not repete

### **Xswitch – Spare Situation**

- 2 working modules in Munich

- 1 module broken (damage caused by water)

- VSC3144 module discontinued by manufacturer

- => alternatives for future modules by MACOM:

| Part Nmb   | Max Data Rate | Switch Matrix | Unit Price [\$] |

|------------|---------------|---------------|-----------------|

| M21601G-12 | 12.5 Gbps     | 120x120       | 897.44          |

| M21605G-12 | 12.5 Gbps     | 160x160       | 1217.95         |

- Fully non-blocking array crosspoint switch

- Four integrated temperature sensors with programmable alarm

- JTAG boundary scan

- Programmable input equalization to compensate for up to 27 dB of loss at 6.25 GHz

- Low latency, less than 2 ns