THIS IS A SIMPLE TEST OF THE JTAG, ONLY USEFUL TO TEST THE BIDIRECTIONAL COMMUNICATION

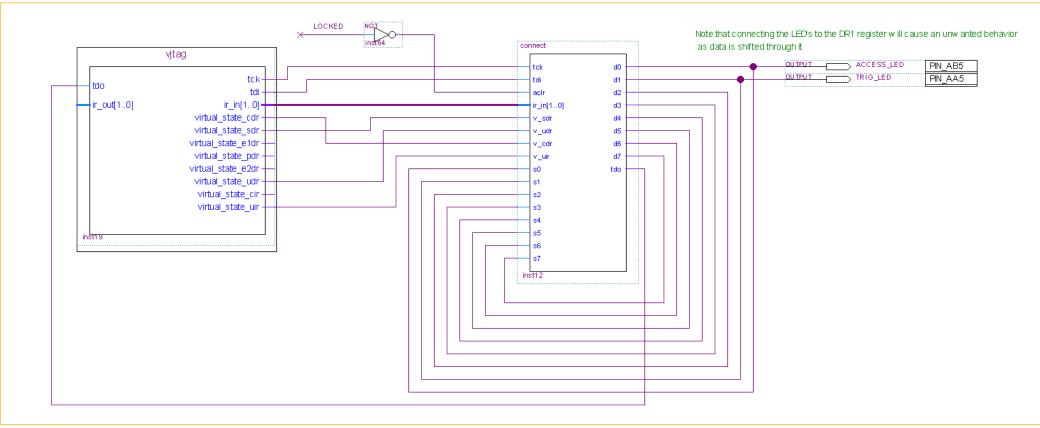

THIS IS A SIMPLE TEST OF THE JTAG, ONLY USEFUL TO TEST THE BIDIRECTIONAL COMMUNICATION. THE PROJECT IS BASED ON THE V26, WAS ONLY ADDED THE INTERFACE TO THE JTAG connected to the LED in our board.

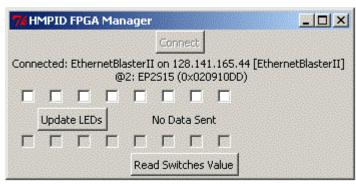

In order to test was written a tcl script form.tcl, running the command "quartus\_stp -t form.tcl"

Raúl Arteche Díaz (24/Jan/2019)

```

☐-- LEDs interface with JTAG

-- Based on a verilog code made by harrym 2014

☐ -- INSTRUCTION:

-- 00: bypass

iprocess (tck)

-- 01: read dip-switch

72

begin

-- 10: update LEDs

73

if rising edge (tck) then

L-- 11: not used (=bypass)

74

if(aclr = '0') then

75

DRO <= (others => '0');

-- VHDL version for HMPID JTAG Test Raul Arteche 2019

76

DR1 <= (others => '0');

11

77

else

LIBRARY ieee;

12

78

case ir in is

13

USE ieee.std logic 1164.all;

79

when KEY =>

use IEEE.NUMERIC STD.ALL;

14

if(v cdr = '1') then

15

use ieee.std logic unsigned.all;

81

DR1 <= 87 & 86 & 85 & 84 & 83 & 82 & 81 & 80;

use IEEE.math real.all;

16

82

else

17

83

if(v sdr ='1') then

18

entity connect is

84

DR1 <= tdi & DR1(7 downto 1);</pre>

19

port(

85

end if:

20

tck

: in

std logic;

86

end if;

tdi

std_logic;

21

: in

87

22

std logic;

aclr

: in

88

when LED =>

23

ir in : in std logic vector(1 downto 0);

89

if(v sdr = '1') then

v sdr : in std logic;

24

90

DR1 <= tdi & DR1(7 downto 1);</pre>

25

v udr : in std logic;

91

end if:

26

v_cdr : in std logic;

92

27

v uir : in std logic;

93

when BYPASS =>

28

94

if(v sdr = '1') then

29

: in

std logic;

95

DRO <= tdi & DRO(1);

architecture rtl of connect is

: in

std logic;

96

end if:

49

31

: in

std logic;

97

50

constant BYPASS : std_logic_vector(1 downto 0 ) := "00";

32

: in

std logic;

51

: std logic vector(1 downto 0 ) := "01";

constant KEY

98

when others =>

33

: in

std logic;

52

constant LED

: std logic vector(1 downto 0 ) := "10";

99

if(v sdr = '1') then

34

: in

std logic;

53

100

DRO <= tdi & DRO(1);

54

signal DRO

35

86

: in

std logic;

: std_logic_vector(1 downto 0 );

101

end if:

55

signal DR1

: std logic vector(7 downto 0 );

36

з7

std logic;

102

end case;

56

signal data_out : std_logic_vector(7 downto 0 ) := "000000000";

37

103

end if:

57

38

d0

: out std logic;

58

104

end if;

begin

39

d1

: out std logic;

59

105

end process;

d2

40

: out std_logic;

60

tdo <= DRO(0) when (ir in = BYPASS) else DR1(0);

106

d3

41

: out std logic;

61

107

process (v udr)

d4

d0 \ll data out(0);

42

: out std_logic;

108

begin

d1 <= data out(1);

43

d5

: out std logic;

109

if(ir in = LED) then

d2 <= data out(2);</pre>

44

d6

: out std logic;

110

data out <= DR1;

d3 <= data out(3);

d7

45

: out std logic;

111

d4 \ll data out(4);

end if;

46

tdo

: out std_logic

d5 <= data out(5);

112

end process;

Raúl Arteche Díaz (24/Jan/2019)

47

d6 <= data out(6);</pre>

113

d7 <= data_out(7);

end connect;

114

end rtl;

70

```

```

44

□proc open port {} {

global blaster name

44

global test device

45

46

open device -hardware name $blaster name -device name $test device

47

proc close port {} {

50

catch {device unlock}

51

catch {close device}

52

53

proc connect jtag {} {

55

global blaster name

56

global test device

57

global displayConnect

58

59

foreach hardware name [get hardware names] {

60

61

if { [string match "USB-Blaster*" $hardware name] } {

62

set blaster name $hardware name

63

64

65

if { [string match "EthernetBlasterII on 128.141.165.44*" $hardware name] } {

66

set blaster name $hardware name

67

68

69

70

foreach device name [get_device_names -hardware name $blaster_name] {

71

if { [string match "@1*" $device name] } {

set test device $device name

73

74

75

set displayConnect "Connected: $hardware name \n $device name"

76

.btnConn configure -state disabled

77

.btnSend configure -state active

78

.btnRead configure -state active

79

80

```

#### Conclusions:

- Is probed the possibility to communicate with the JTAG EthernetBlasterII using a TCL script.

- If the test of the LEDs example work as expected, will probe the bidirectional communication using the JTAG.

- A full VHDL implementation is possible of this example allowing the integration in the new firmware.

- The final data o parameter to monitor using the JTAG need to be discussed in the future.