# CPUs, GPUs and accelerators

# x86

# Intel roadmap for 2019-

- Intel focusing on new spaces IoT, AI, DL, self-driving cars, ... where AMD cannot yet compete

- 3D chip stacking

- Enabled by Foveros interconnect technology

- FPGA

- Intel Nervana Al Processor NNP-L-1000 (H2 2019-)

- Accelerates AI inference for companies with high workload demands

- Optimized across memory, bandwidth, utilization and power

- Spring Crest 3-4x faster training than Lake Crest, introduced in 2017

- Supports bfloat16

# Intel server micro-architectures (1/2)

| Microarchitecture | Technology | Launch year | Highlights                                                                                                                                                       |

|-------------------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Skylake           | 14nm       | 2015        | Improved frontend and execution units<br>More load/store bandwidth<br>Improved hyperthreading<br>AVX-512                                                         |

| Cascade Lake      | 14nm++     | 2019        | Vector Neural Network Instructions (VNNI) to<br>improve inference performance<br>Support 3D XPoint-based memory modules and<br>Optane DC<br>Security mitigations |

| Cooper Lake       | 14nm++     | 2020        | bfloat16 (brain floating point format)                                                                                                                           |

14NM

2020

2020

14NM/10NM PLATFORM

INTEL OPTANE PERSISTENT MEMORY

INTEL DLBOOST: VNNI

SECURITY MITIGATIONS

NEXT GEN INTEL DLBOOST: BFLOAT16

**LEADERSHIP PERFORMANCE**

# Intel server micro-architectures (2/2)

| Microarchitecture | licroarchitecture Technology |       | Highlights                                                                                                                                                   | CPU codename                     |  |  |

|-------------------|------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Sunny Cove        | 10nm+                        | 2019  | Single threaded performance<br>New instructions<br>Improved scalability<br>Larger L1, L2, µop caches and 2nd level<br>TLB<br>More execution ports<br>AVX-512 | Ice Lake Scalable<br>Tiger Lake? |  |  |

| Willow Cove       | 10nm                         | 2020? | Cache redesign<br>New transistor optimization<br>Security Features                                                                                           | ?                                |  |  |

| Golden Cove       | 7/10nm?                      | 2021? | Single threaded performance<br>AI Performance<br>Networking/5G Performance<br>Security Features                                                              | ?                                |  |  |

#### Other Intel-related news

- Record Q3 2018 results

- Data-centric revenue rose 22%

- PC revenue rose 16%

- Could not keep up with demand for the latest Xeon chips in 2018

- Serious issues with 10nm process as years behind scheduled

- Pushing 14nm process to its limits

- Claims that volume delivers on track for late 2019 and later

- Being superseded by 7nm sooner than intended, which will be based on EUV lithography

- Hopes that it will put Intel on track with Moore's Law

- Itanium family to be discontinued in 2021

#### AMD News

- Next gen desktop Matisse CPU (7nm) using Zen2 core achieves IPC parity with Intel, consumes less power and supports PCIe 4.0

- Improved branch predictor unit and prefetcher, better micro-op cache management, larger micro-op cache, increased dispatch bandwidth, increased retire bandwidth, native support for 256-bit floating point math, double size FMA units, double size load-store units

- CSC announced an upcoming supercomputer using 3125 64-core EPYC "Rome" CPUs in 2020

- Market trend

- Revenues increased by 23% over 2018 and profitability at its highest since 2011

# AMD EPYC Naples (since Q2 '17)

AMD EPYC processors target the datacenter and specifically (not limited to) mono-processor servers. EPYC Naples (Zen architecture) is a single chip made up of 4 separate dies (multi-chip module), interconnected with Infinity Fabric links.

Main specs:

- 4 dies per chip (14nm), each die embedding IO and memory controllers, no chipset, SP3 sockets

- range of frequencies : 2.0-2.4 GHz, turbo up to 3.2 GHz

- 8 DDR4 memory channels with hardware, on the fly, encryption, up to 2600 MHz

- up to 32 cores (64 threads)

- up to 128 PCI gen3 lanes per processor (64 in dual )

- TDP range: 120W-180W

EPYC Naples processors have similar computing power compared to Intel Skylake processors (HS06 benchmarks on close frequencies and core count CPUs) with cutoff prices up to 49% (AMD claim).

Mostly compatible with Intel based x86, sparing for user code modifications.

# AMD EPYC Rome (starting Q2 '19)

Next AMD EPYC generation (Zen2 based), embeds 9 dies (8 CPU 7nm chiplets for 1 I/O 14 nm die). All I/O and memory access is concentrated into a single die.

Main specs:

- 9 dies per chip : a 7nm single IO/memory die and 8 CPU 7nm chiplets

- 8 DDR4 memory channels, up to 3200 MHz

- up to 64 cores (128 threads) per processor

- up to 128 PCI gen3/4 lanes per processor

- SP3 / LGA-4094 sockets

- TDP range: 120W-225W (max 190W for SP3 compatibility)

Claimed +20% performance per zen2 core (over zen), +75% through the whole chip with similar TDP over Naples.

Available on DELL C6525 chassis starting from october.

# Manufacturing technologies

- 10nm

- Intel will ramp up in 2019, late by several years

- Relies on DUVL (deep ultraviolet lithography) (193nm wavelength laser) requiring heavy use of multipatterning, which is problematic

- 7nm

- Uses EUVL (extreme ultraviolet lithography) (13.5nm wavelength laser) reducing use of multipatterning and reducing costs

- $\circ$  Intel on track and will start at the end of 2019

- TSMC already making or will make chips for AMD, Apple, Nvidia and Qualcomm

- Samsung Foundry started production and will make POWER CPUs for IBM from 2020

- GlobalFoundries put it on hold indefinitely

- 5, 3, ? nm

- Design costs increase exponentially

- [to be expanded]

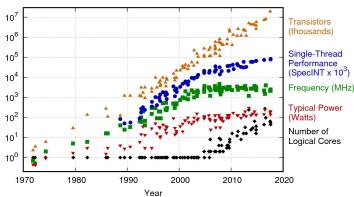

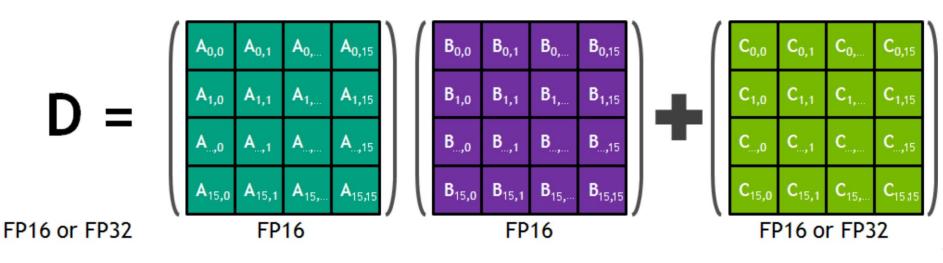

# **GPUs - Architecture**

- For what concerns raw power GPUs are following the exponential trends wrt number of transistors and cores

- New features appear unexpectedly, driven by market

42 Years of Microprocessor Trend Data

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2017 by K. Rupp

|                                                                  |                                                       |                                                        |                                                              |                                                                          |                    |                     | _      | ction Cache                                            |                                                     | 1.0.5                                                      |                                                                           |                                                                                  |                  |                     | _      |

|------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|---------------------|--------|--------------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|---------------------|--------|

| L0 Instruction Cache<br>Warp Scheduler (32 thread/clk)           |                                                       |                                                        |                                                              |                                                                          |                    |                     |        | L0 Instruction Cache<br>Warp Scheduler (32 thread/clk) |                                                     |                                                            |                                                                           |                                                                                  |                  |                     |        |

| Dispatch Unit (32 thread/clk)                                    |                                                       |                                                        |                                                              |                                                                          |                    |                     |        | Dispatch Unit (32 thread/clk)                          |                                                     |                                                            |                                                                           |                                                                                  |                  |                     |        |

|                                                                  |                                                       |                                                        |                                                              |                                                                          | 4 x 32.            |                     |        |                                                        |                                                     |                                                            |                                                                           |                                                                                  | 4 x 32           |                     |        |

| FP64                                                             | INT                                                   | INT                                                    | FP32                                                         | FP32                                                                     |                    |                     |        | FP64                                                   | INT                                                 | INT                                                        | FP32                                                                      | FP32                                                                             |                  |                     |        |

| FP64                                                             | INT                                                   | INT                                                    | FP32                                                         | FP32                                                                     |                    |                     |        | FP64                                                   | INT                                                 | INT                                                        | FP32                                                                      | FP32                                                                             |                  |                     |        |

| FP64                                                             | INT                                                   | INT                                                    | FP32                                                         | FP32                                                                     |                    |                     |        | FP64                                                   | INT                                                 | INT                                                        | FP32                                                                      | FP32                                                                             |                  |                     |        |

| FP64                                                             | INT                                                   | INT                                                    | FP32                                                         | FP32                                                                     | TENSOR<br>CORE     |                     | TENSOR | FP64                                                   | INT                                                 | INT                                                        | FP32                                                                      | FP32                                                                             | TENSOR<br>CORE   | TENSOR<br>CORE      |        |

| FP64                                                             | INT                                                   | INT                                                    | FP32                                                         | FP32                                                                     |                    |                     | CORE   | FP64                                                   | INT                                                 | INT                                                        | FP32                                                                      | FP32                                                                             |                  |                     |        |

| FP64                                                             | INT                                                   | INT                                                    | FP32                                                         |                                                                          |                    |                     |        | FP64                                                   | INT                                                 | INT                                                        |                                                                           | FP32                                                                             |                  |                     |        |

| FP64                                                             | INT                                                   | INT                                                    | FP32                                                         |                                                                          |                    |                     |        | FP64                                                   | INT                                                 | INT                                                        | _                                                                         | FP32                                                                             |                  |                     |        |

| FP64                                                             | INT                                                   | INT                                                    | FP32<br>LD/                                                  | FP32                                                                     | LD/                | LD/                 | SFU    | FP64                                                   | INT                                                 | INT                                                        | FP32<br>LD/                                                               | FP32<br>LD/                                                                      | LD/              | LD/                 | SFU    |

| Warp Scheduler (32 thread/clk)                                   |                                                       |                                                        |                                                              |                                                                          |                    |                     |        |                                                        |                                                     |                                                            |                                                                           |                                                                                  |                  |                     |        |

| Dispatch Unit (32 thread/clk)<br>Register File (16,384 x 32-bit) |                                                       |                                                        |                                                              |                                                                          |                    | clk)                |        |                                                        | Wa                                                  | rp Sch                                                     | edule                                                                     | r (32 t                                                                          | hread/           | clk)                |        |

|                                                                  | Dis                                                   | patcl                                                  | n Unit                                                       | (32 th                                                                   | read/cl            | lk)                 |        |                                                        | Di                                                  | spatcl                                                     | h Unit                                                                    | (32 th                                                                           | read/c           | lk)                 |        |

|                                                                  | Dis<br>Regi                                           | spatch<br>ister                                        | n Unit<br>File (1                                            | (32 th<br>16,384                                                         | read/cl            | lk)                 |        |                                                        | Di<br>Reç                                           | spatcl<br>Jister                                           | h Unit<br>File ('                                                         | (32 th<br>16,384                                                                 |                  | lk)                 |        |

| FP64                                                             | Dis<br>Regi<br>INT                                    | ister                                                  | n Unit<br>File (1<br>FP32                                    | (32 th<br>16,384<br>FP32                                                 | read/cl            | lk)                 |        | FP64                                                   | Di<br>Reg<br>INT                                    | spatcl<br>gister                                           | h Unit<br>File ('<br>FP32                                                 | (32 th<br>16,384<br>FP32                                                         | read/c           | lk)                 |        |

| FP64                                                             | Dis<br>Regi<br>INT<br>INT                             | ister<br>INT<br>INT                                    | n Unit<br>File (1<br>FP32<br>FP32                            | (32 th<br>16,384<br>FP32<br>FP32                                         | read/cl            | lk)                 |        | FP64                                                   | Di<br>Reç<br>INT                                    | spatcl<br>jister<br>INT<br>INT                             | h Unit<br>File (*<br>FP32<br>FP32                                         | (32 th<br>16,384<br>FP32<br>FP32                                                 | read/c           | lk)                 |        |

|                                                                  | Dis<br>Regi<br>INT                                    | ister                                                  | n Unit<br>File (1<br>FP32                                    | (32 th<br>16,384<br>FP32<br>FP32<br>FP32                                 | read/cl            | lk)<br>-bit)        |        |                                                        | Di<br>Reg<br>INT                                    | spatcl<br>gister                                           | h Unit<br>File (*<br>FP32<br>FP32<br>FP32                                 | (32 th<br>16,384<br>FP32<br>FP32                                                 | read/c<br>4 x 32 | lk)<br>-bit)        |        |

| FP64<br>FP64                                                     | Dis<br>Regi<br>INT<br>INT<br>INT                      | ister<br>INT<br>INT<br>INT                             | h Unit<br>File (1<br>FP32<br>FP32<br>FP32                    | (32 th<br>16,384<br>FP32<br>FP32<br>FP32<br>FP32                         | read/cl            | lk)<br>-bit)<br>SOR | TENSOR | FP64<br>FP64                                           | Di<br>Reç<br>INT<br>INT<br>INT                      | spatcl<br>jister<br>INT<br>INT<br>INT                      | h Unit<br>File (*<br>FP32<br>FP32<br>FP32<br>FP32                         | (32 th<br>16,384<br>FP32<br>FP32<br>FP32                                         | read/c           | Ik)<br>-bit)<br>SOR | TENSOF |

| FP64<br>FP64<br>FP64                                             | Dis<br>Regi<br>INT<br>INT<br>INT<br>INT               | ister<br>INT<br>INT<br>INT<br>INT                      | File (1<br>FP32<br>FP32<br>FP32<br>FP32                      | (32 th<br>16,384<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32                 | read/cl<br>4 x 32· | lk)<br>-bit)<br>SOR |        | FP64<br>FP64<br>FP64                                   | Di<br>Reg<br>INT<br>INT<br>INT                      | spatcl<br>ster<br>INT<br>INT<br>INT<br>INT                 | h Unit<br>File (*<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32                 | (32 th<br>16,384<br>FP32<br>FP32<br>FP32<br>FP32                                 | TEN              | Ik)<br>-bit)<br>SOR |        |

| FP64<br>FP64<br>FP64<br>FP64                                     | Dis<br>Regi<br>INT<br>INT<br>INT<br>INT               | ister<br>INT<br>INT<br>INT<br>INT<br>INT               | File (1<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32      | (32 th<br>16,38<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32          | read/cl<br>4 x 32· | lk)<br>-bit)<br>SOR |        | FP64<br>FP64<br>FP64<br>FP64                           | Di<br>Reg<br>INT<br>INT<br>INT<br>INT               | spatcl<br>gister<br>INT<br>INT<br>INT<br>INT<br>INT        | h Unit<br>File (*<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32         | (32 th<br>16,384<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32                         | TEN              | Ik)<br>-bit)<br>SOR |        |

| FP64<br>FP64<br>FP64<br>FP64<br>FP64                             | Dis<br>Regi<br>INT<br>INT<br>INT<br>INT<br>INT        | ister<br>INT<br>INT<br>INT<br>INT<br>INT<br>INT        | FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32 | (32 th<br>16,38<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32          | read/cl<br>4 x 32· | lk)<br>-bit)<br>SOR |        | FP64<br>FP64<br>FP64<br>FP64<br>FP64                   | Di<br>Reg<br>INT<br>INT<br>INT<br>INT<br>INT        | spatcl<br>sister<br>INT<br>INT<br>INT<br>INT<br>INT        | h Unit<br>File (*<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32         | (32 th<br>16,384<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32                 | TEN              | Ik)<br>-bit)<br>SOR |        |

| FP64<br>FP64<br>FP64<br>FP64<br>FP64<br>FP64                     | Dis<br>Regi<br>INT<br>INT<br>INT<br>INT<br>INT<br>INT | ister<br>INT<br>INT<br>INT<br>INT<br>INT<br>INT<br>INT | FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32 | (32 th<br>16,384<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32 | read/cl<br>4 x 32· | lk)<br>-bit)<br>SOR |        | FP64<br>FP64<br>FP64<br>FP64<br>FP64<br>FP64           | Di<br>Reg<br>INT<br>INT<br>INT<br>INT<br>INT<br>INT | spatcl<br>jister<br>INT<br>INT<br>INT<br>INT<br>INT<br>INT | h Unit<br>File (*<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32 | (32 th<br>16,384<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32<br>FP32 | TEN              | Ik)<br>-bit)<br>SOR | TENSOF |

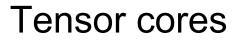

Tensor cores integrated on the GPU

Fast half precision multiplication and reduction in full precision

Useful for accelerating NN training/inference

# **GPUs - Programmability**

- NVIDIA CUDA:

- C++ based (supports C++14)

- Many external projects

- New hardware features available with no delay in the API

- OpenCL:

- Not supported by NVIDIA

- Can execute on CPU/iGPU/NVIDIA/AMD and recently Intel FPGAs

- Overpromised in the past, with scarce popularity

- Compiler directives: OpenMP/OpenACC

- Latest gcc and llvm include support for CUDA backend

- AMD HIP:

- Similar to CUDA, still supports only a subset of the features

- GPU-enabled frameworks to hide complexity (Tensorflow)

# **GPUs - Programmability**

Issue is performance portability and code duplication

At the moment, only possible solutions are based on trade-offs and DSL for very simple codes

• might work very well for analysis/ML, less for reconstruction

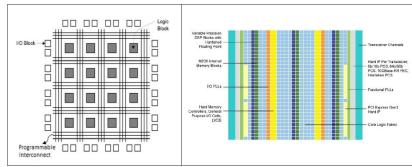

#### **FPGA**

- Players: Xilinx (US), Intel (US), Lattice Semiconductor (US), Microsemi (US), and QuickLogic (US), TSMC (Taiwan), Microchip Technology (US), United Microelectronics (Taiwan), GLOBALFOUNDRIES (US), Achronix (US), and S2C Inc. (US)

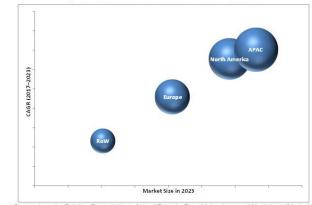

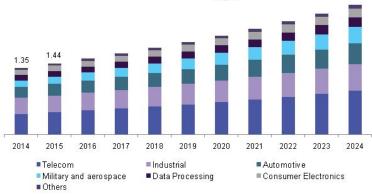

- Market was valued at USD 5.34 Billion in 2016 and is expected to be valued at 9.50 Billion in 2023

- Growing demand for advanced driver-assistance systems (ADAS), developments in IoT and reduction in time-to-market are the key driving factors

- Telecommunications held the largest size of the FPGA market in 2016

Source: Investor Relation Presentations, Annual Reports, Expert Interviews, and MarketsandMarket Analysis

#### FPGA Market, by Region, 2023 (USD Billion)

#### **FPGAs for Application Acceleration**

Source: https://www.nextplatform.com/2018/10/15/where-the-fpga-hits-the-server-road-for-inference-acceleration/

|                                                                          | 20 nm                                                                |                                                | 16 nm        |                                                                                            | 14 nm                                         |                |  |

|--------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------|--------------|--------------------------------------------------------------------------------------------|-----------------------------------------------|----------------|--|

| Process Technology                                                       | Intel®                                                               | Xilinx®                                        | Intel®       | Xilinx®                                                                                    | Intel®                                        | Xilinx®        |  |

| Best Performance Or<br>Fastest, Most Powerful                            |                                                                      | Virtex <sup>®</sup><br>UltraScale <sup>®</sup> |              | Virtex <sup>®</sup> UltraScale+ <sup>®</sup><br>Zynq <sup>®</sup> UltraScale+ <sup>®</sup> | Intel <sup>®</sup><br>Stratix <sup>®</sup> 10 |                |  |

| Best Price/performance/watt Or<br>Balance of cost, power,<br>performance | Intel <sup>®</sup> Arria <sup>®</sup> 10                             | Kintex<br>UltraScale <sup>®</sup>              |              |                                                                                            |                                               |                |  |

| Cost-Optimized Or<br>Low system cost plus performance.                   | Intel <sup>®</sup> Cyclone <sup>®</sup><br>1.100/Gottent/www/us/en/p | rogrammable/docum                              | entation/mtr | 422491996806.html#qom1512594                                                               | 527835fn_soc_va                               | riab_avail_xlx |  |

#### **FPGAs for Application Acceleration**