A monolithic silicon pixel sensor in SiGe BiCMOS for the FASER high granularity preshower detector

SPEAKER: FULVIO MARTINELLI - FULVIO.MARTINELLI@CERN.CH

12<sup>TH</sup> INTERNATIONAL CONFERENCE ON POSITION SENSITIVE DETECTORS - BIRMINGHAM 2021

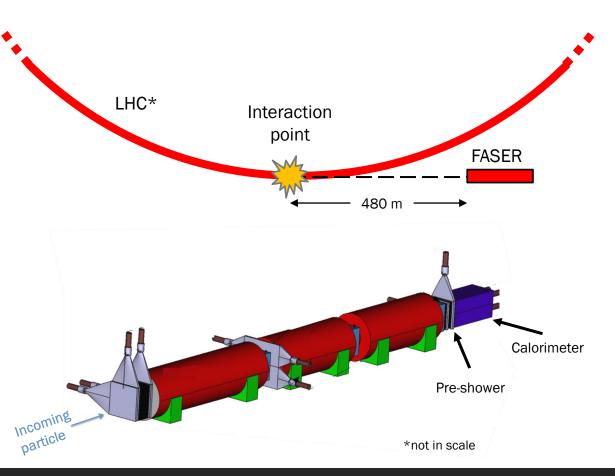

### FASER experiment

- Main goal: research on the dark matter through detection of Long Lived Particles (LLP).

- Extension of the physics program of other experiments at LHC.

- Exploiting the huge pion source provided by LHC ( $N_{\pi} \approx 10^{17}$ ).

- Collaboration among 20 institutes.

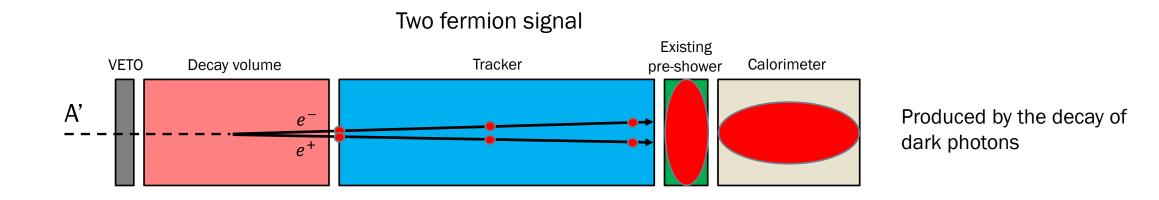

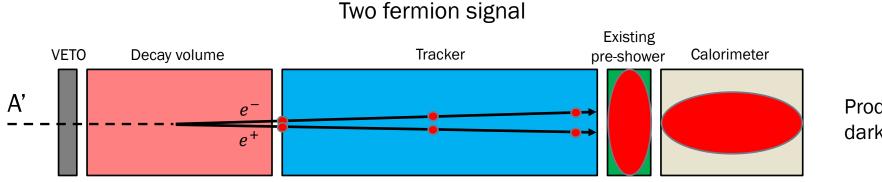

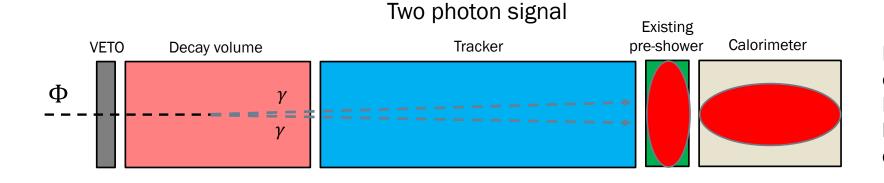

### FASER experiment: signals

### FASER experiment: signals

Produced by the decay of dark photons

Possible indication of the existence of Axion Like Particles (ALP). NOT detectable with current FASER system.

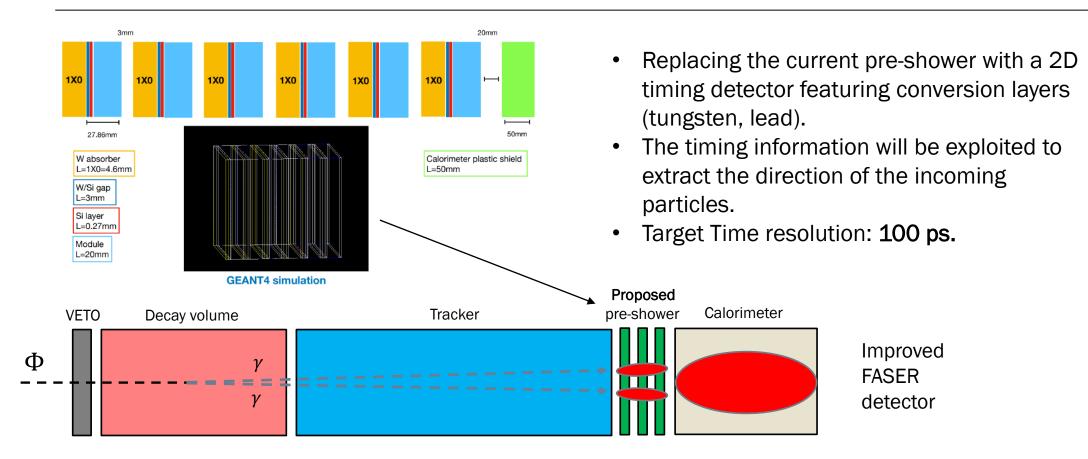

### FASER experiment: proposal

# Pixel characteristics and reconstruction

Charge distribution [fC]

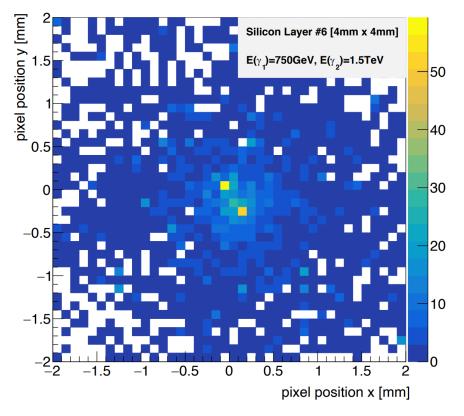

- In order to better reconstruct the electromagnetic showers, we need the ability to reconstruct clusters of hits.

- Charge information for each pixel needs to be recorded and acquired.

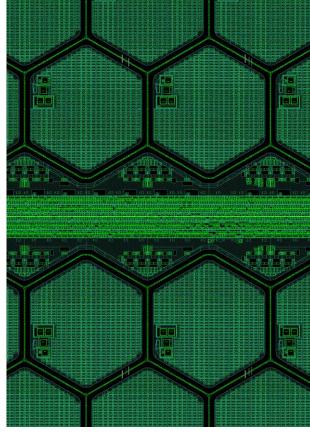

- Our choice: 65 µm side hexagonal pixels.

- Hexagonal shape in order to reduce the peak electric field at the edges.

- GEANT4 simulations highlighted that photon signals can produce input charges in a few fC to various tens of fC range.

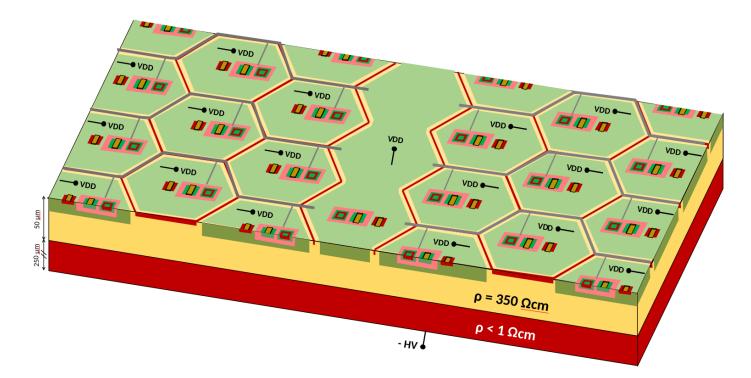

# Sensor cross-section and technology

- Monolithic pixel detector.

- 130 nm SiGe BiCMOS technology provided by IHP Microelectronics.

- Custom high-resistivity 50 µm EPI layer. HV=-120 V, complete depletion.

- Pixels integrated as triplewells.

- Front-end electronics integrated in pixel.

### Chip architecture

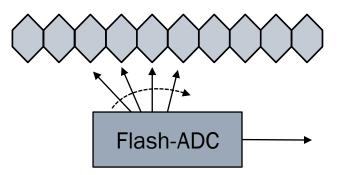

## Polling and analog memory

- The charge needs to be measured for each pixel.

- The idea is to store the data on a capacitor (via a sample and hold) in each pixel and convert it on the fly with a flash ADC. 256-to-1 MUX.

- The capacitor is charged with a constant current during the TOT.

- The same ADC will poll all the pixels in a superpixel and convert them as needed.

## Pre-production chip specs

| Technology                    | IHP 130 nm SiGe BiCMOS     |

|-------------------------------|----------------------------|

| Pixel size                    | 65 µm side – hexagonal     |

| Matrix size                   | 64 by 128 (7.2 by 15.3 mm) |

| Positive supply               | 1.2 V                      |

| Current consumption (Analog)  | 24 mA                      |

| Current consumption (Digital) | 26 mA                      |

| Power consumpion              | 7 μW/pixel                 |

| Input charge dynamic range    | 1 fC to 64 fC              |

| Readout time                  | ~26 µs (typical)           |

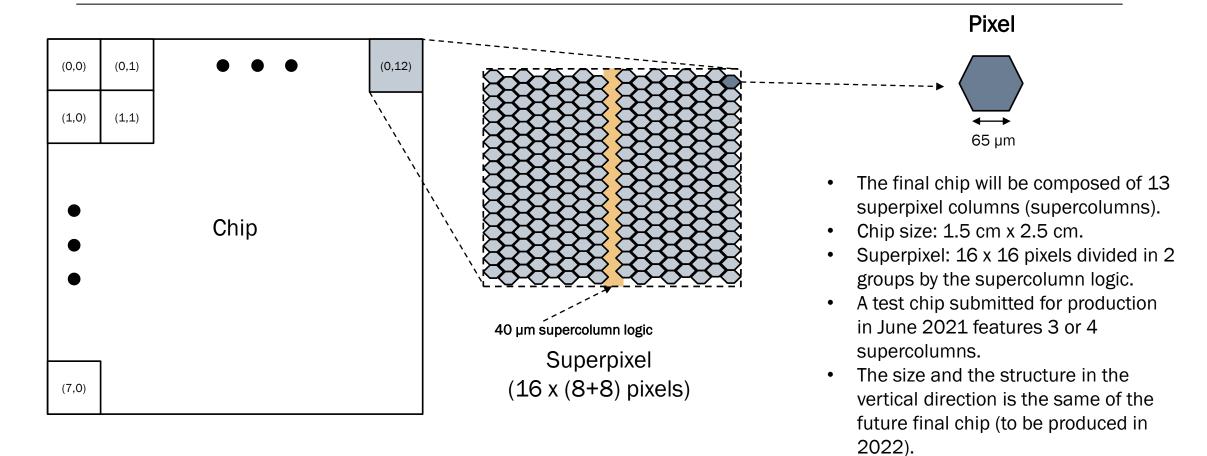

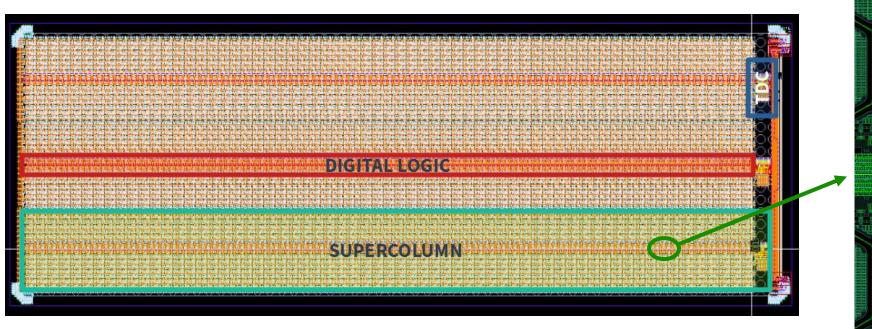

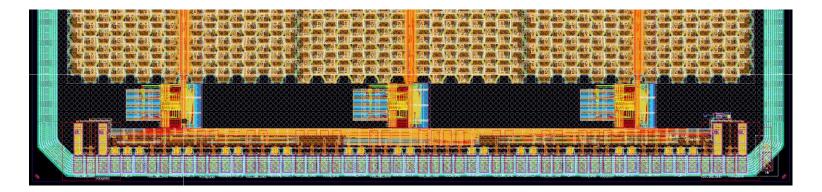

# Chip floorplan and supercolumn logic

- The chip is divided in "supercolumns" (128 by 16 pixels) with a ~40  $\mu m$  slice of digital logic in between.

- The digital logic includes the MUX, the flash ADC, a small programming logic to mask the pixels and the entire readout logic for all the pixels in the supercolumn.

- Moreover, a data pruning system is implemented to increase the speed of the readout.

- The physical design of this block presented some challenges as its aspect ratio is very unusual (1.5 cm by 40  $\mu$ m).

### Chip floorplan and pixel layout

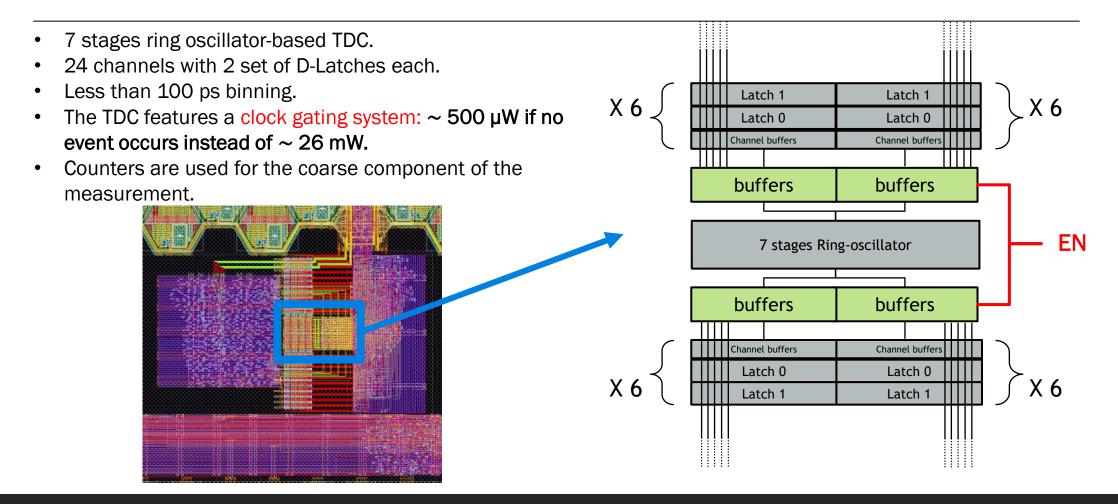

### TDC

### End of column and periphery

- The TDC outputs are fed into an end-of-column block to be read out.

- The end-of-column block connects the supercolumn logic with the periphery.

- SPI slow control to mask individual pixels and control biases

- Double LVDS 200 Mb/s output link.

- Bandgap, global DACs to provide biases (the chip has no analog input).

- The periphery logic is agnostic to the number of supercolumns: the design can easily be resized with minimal changes.

### Conclusions and next steps

- 3 different test chip have been submitted and will be available for testing in the next few months.

- We prioritized making the chip easily testable (standard I/O, common pinout).

- We also chose a easily scalable architecture, a fundamental feature to reduce the design time.

- The scaled up version with 13 supercolumns should be submitted in March 2022.

## Appendix

### MUX solution characteristics

### Pros

- This architecture is much smaller than using a TDC channel for each pixel.

- It cuts the amount of memory by a factor 256 (pixels in a superpixel).

- A 256-to-1 multiplexer is less than 5 µm wide.

- The flash ADC is a very simple design (as long as we do not need great accuracy, 4 bits is fine for us).

#### Cons

- The time to complete a readout is critical as the capacitors cannot store the charge indefinitely.

- Unfortunately a 256-to-1 analog multiplexer poses challenges.

- When switching between codes we have to make sure pixels are not short-circuited.

- The analog MUX has a certain capacitance associated to its active path. It needs to be discharged before reading the next pixel.

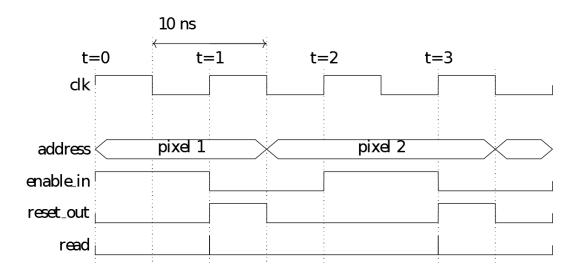

- When **reset\_out** is 1, the input of the ADC is charged to VDD.

- **enable\_in** added to avoid activating unwanted addresses during readout.

- Careful timing needs to be introduced to manage the switching, making it at least 2 clock cycles per switch.

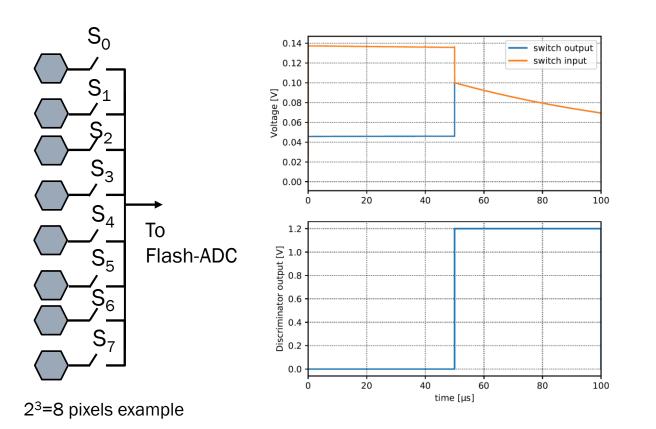

- Naive approach for the MUX design: a switch per pixel, all connected to the same line.

- **Problem:** due to the large capacitance connected to each switch, half of the charge will be lost during switching.

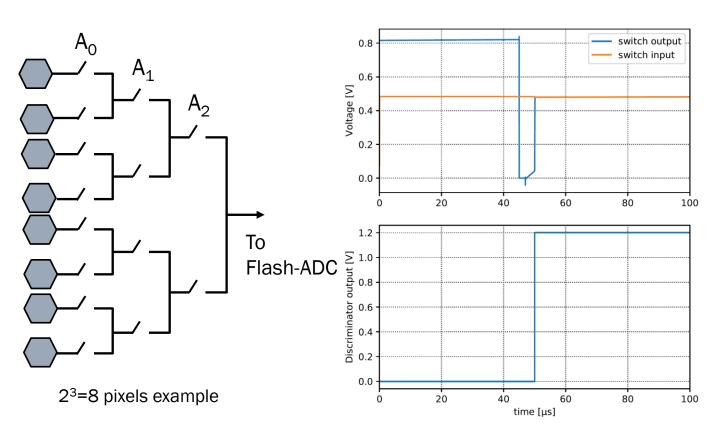

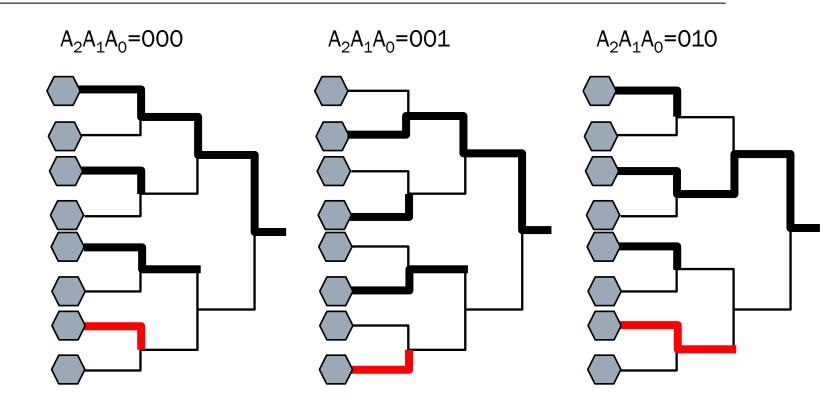

- **Proposed design**: multi-stage approach.

- 8 stage of 2-to-1 MUXs in series.

- Lower capacitance seen at each node.

- Problem of the proposed design: the polling leads to the sharing of the charges of the pixels with 'higher' addresses.

- This is due to the switching of the LSB of the address (A<sub>0</sub> in the example).

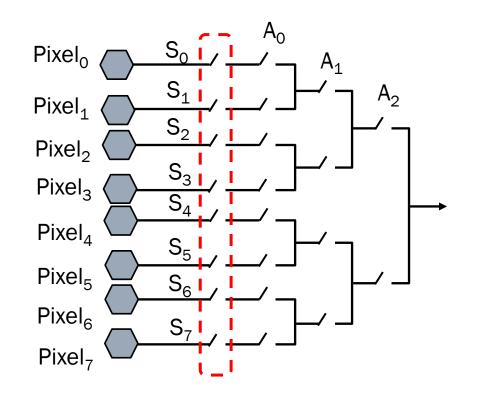

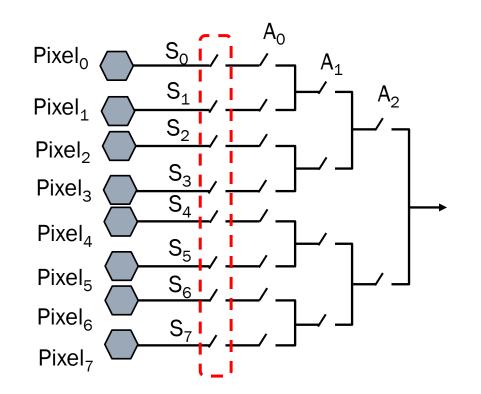

- Solution: additional switches connected to the MUX inputs.

- Solution: additional switches connected to the MUX inputs.

- For this example:

- Pixel<sub>2-3</sub>: S<sub>2-3</sub> AND with A<sub>1</sub>

- Pixel<sub>4-5</sub>: S<sub>4-5</sub> AND with A<sub>2</sub>

- Pixel<sub>6-7</sub>:  $S_{6-7}$  AND with  $A_1, A_2$

- In a N-bit case, there will be 2<sup>N-1</sup> couples of pixels.

- The couples can be coded in binary words C of N-1 bit.

- It is possible to demonstrate that the i-th couple needs a number of AND inputs equal to the number of 1s in the corresponding word C.

- In the N=8 case the number of additional AND inputs needed will be:

$$\begin{pmatrix} 7\\1 \end{pmatrix} + \begin{pmatrix} 7\\2 \end{pmatrix} 2 + \begin{pmatrix} 7\\3 \end{pmatrix} 3 + \begin{pmatrix} 7\\4 \end{pmatrix} 4 + \begin{pmatrix} 7\\5 \end{pmatrix} 5 + \begin{pmatrix} 7\\6 \end{pmatrix} 6$$

$$+ \begin{pmatrix} 7\\7 \end{pmatrix} 7 \approx 400$$

• In the token ring solution, 256 **D-flip-flops** are required.

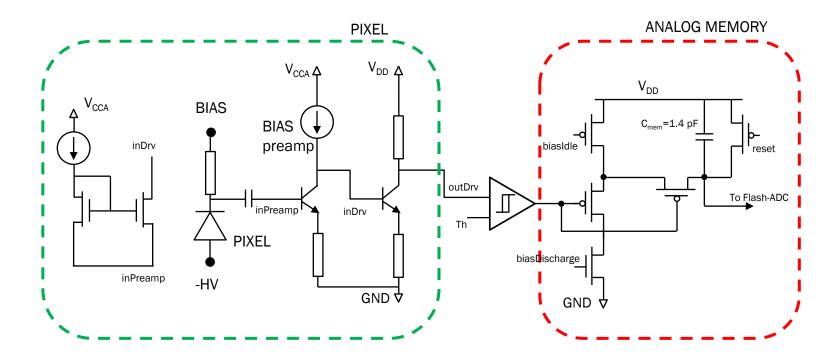

### Front-end architecture

- BJT-based preamp with MOS feedback

- Low-power discriminator (that can be outside of the pixel area)

- Analog memory

- Discriminator output activates the charging of the capacitor  $\rm C_{\rm mem}.$

- reset and biasIdle are used to discharge C<sub>mem</sub> when no hit occurs and to deal with leakage respecively.

### Test chip variants

Three chips were submitted:

- A 4-supercolumn reference design.

- A **3-supercolumn variant** with BJT-based discriminators featuring lower pixel-to-pixel mismatch.

- A **3-supercolumn variant** with counters instead of mux + ADC (safe).

- This version has triple the dead area compared to the other two. The supercolumn logic is 3 times thicker due to the addition of LFSR counters replacing the analog memory system.

- The periphery and readout logic is unchanged among them.

### **Pixel Calibration**

- The limiting factor for the dynamic range at the low end is the pixel-topixel threshold mismatch.

- The issue could be solved with a local tuning DAC, but there was no space for it and for its configuration register.

- 8 thresholds are distributed to different areas to reduce this effect through 8 bit DACs.

- The version with BJT-based discriminators are designed to solve this issue: BJTs are 'vertical' with sharper and more precise doping profiles.