# ATLAS Japan ITk

Univ of Tsukuba Daigo Harada

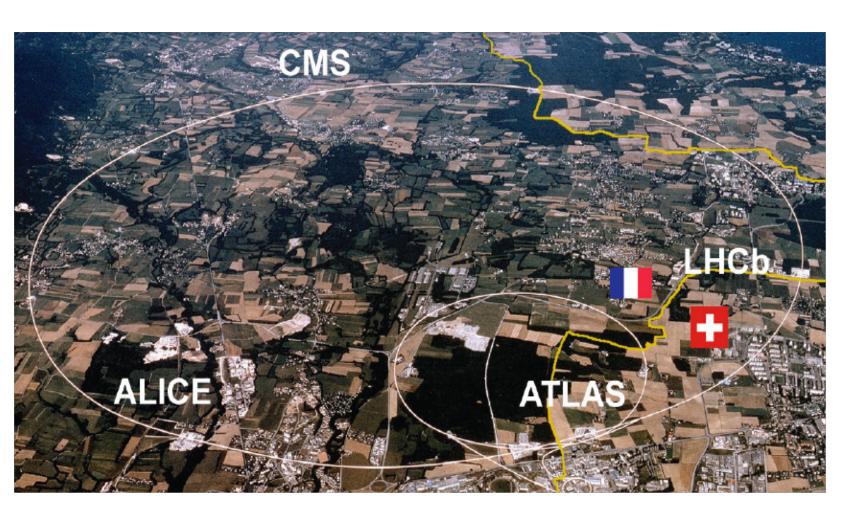

### LHC

- The largest (27km) pp hadron collider in the world.

- 13 TeV Center of Mass energy

- 4 collision position (ATLAS, CMS, ALICE, LHCb)

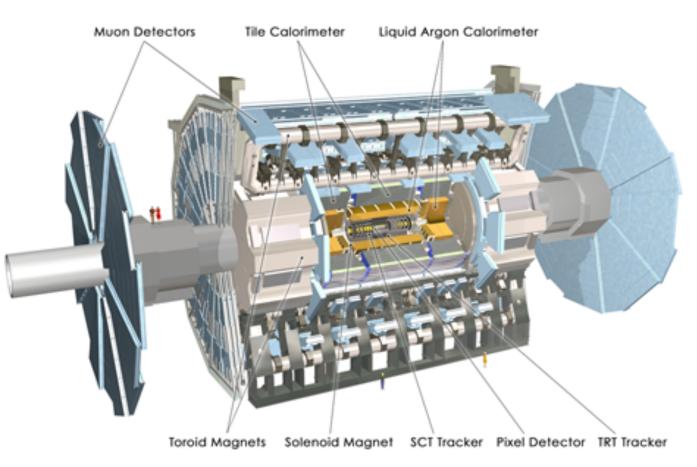

#### ATLAS

height 25m, length 44m weight 7000t

#### three type sensors

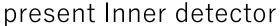

- Inner detector <- our group first part of ATLAS to see the decay products of the collisions very compact and highly sensitive

- Calorimeters

measure the energy a particle loses as it

passes through the detector

- Muon detectors detect muon using muon chambers

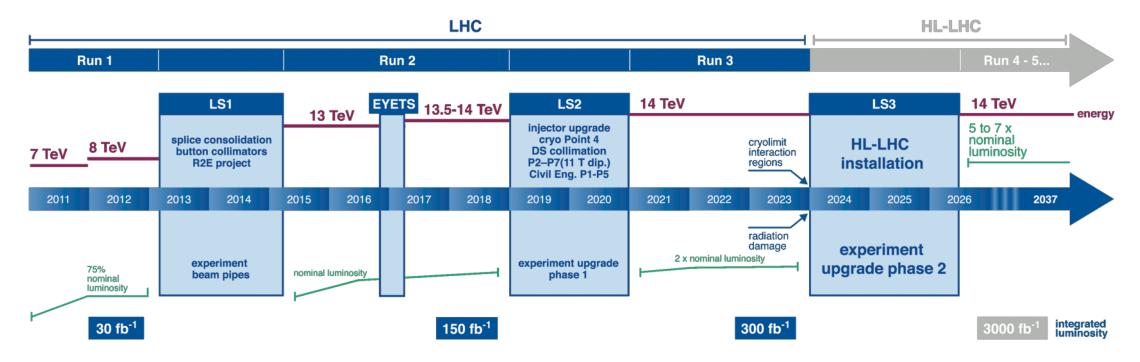

#### HL-LHC

The LHC will become High-Luminosity-LHC(HL-LHC) at 2026.

The benefits are measurements and studies of rare processes.

Peak luminosity: 5-7 x  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup> ~ x 5-7

Average pile-up: up to  $\sim 200 \sim x 5$

Integrated luminosity:  $3000 \text{ fb}^{-1} \sim \times 10$

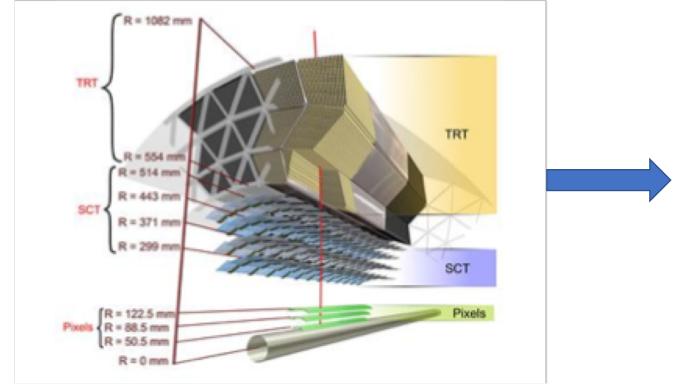

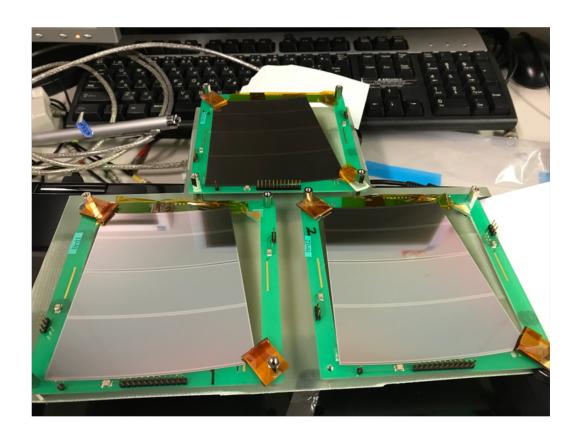

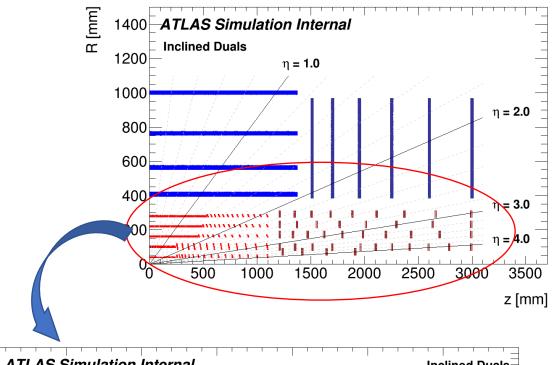

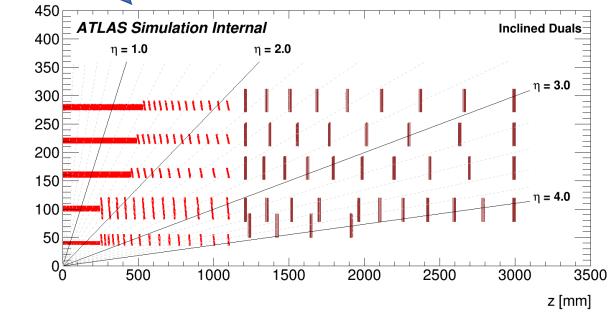

#### ITk

for HL-LHC ATLAS detector will upgrade.

- replace all silicon sensor strip/pixel detector

- cover large area ( $\eta = 4.0$ )

- to reduce hit occupancy small pixel/strip size

- high radiation resistivity

HL-LHC Inner detector (ITk)

### strip detector

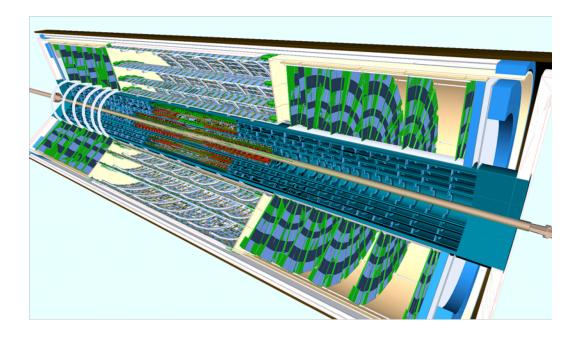

large area of ITk are strip detector. strip sensors have already been under pre-production Japan group QC/QA

# Japanese QA/QC overview

Japan takes responsibility on ½ barrel sensor (~6,000) production and associated QC/QA

QC: everything at HPK

❖ IV+CV ···. as HPK provides

❖ AC probing

3 half moon's per batch (~50)

DC probing

~10 batches/month

Image capture/warp meas.

24h stability

QA: Tsukuba mini CCE/IV/CV MD8 IV/CV CYRIC irradiation (twice/year) as cross-check of monthly Birmingham irradiation mini/MD8<del>/TS</del>

TS surface properties

#### production

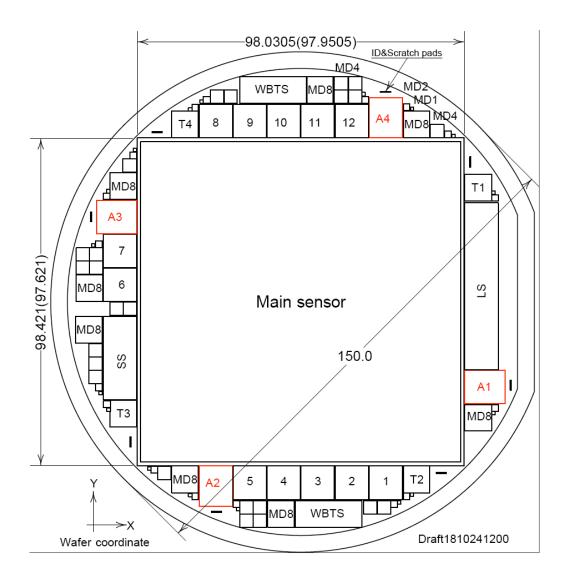

- All the Monitor test structures (except 8x8 and 4x4 diodes) can be inserted in one single test chip.

- Monitor diodes an minis placed close to test chip to form a "test Si piece"

- Four instances across the wafer

- In discussions with HPK it was agreed that in production they could cut:

- Piece 1: 1 test chip + diodes

- Piece 2: 1 mini sensor

In 2-3 wafers per batch (40-50)

### pixel detector

pixel detector is innermost sensorin ITk.

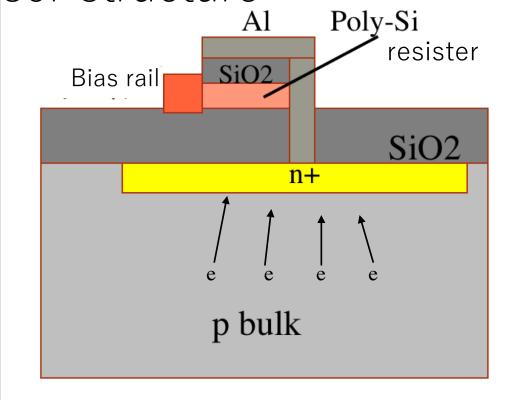

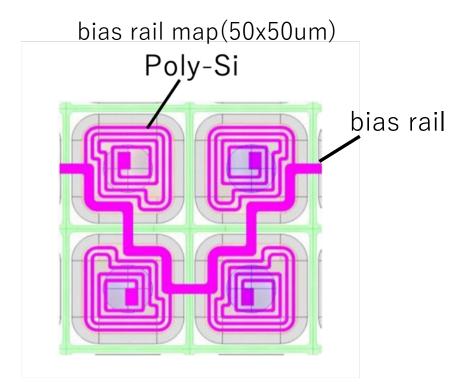

$1^{st}$  layer is 3D sensor and  $2^{nd}$  to  $5^{th}$  layers are n+ in p  $50 \times 50$ um or  $25 \times 100$ um(1/5 size of present sensor) Japan group develop  $3^{rd}$  to  $5^{th}$  sensor these area fluence is  $3.0 \times 10^{15}$

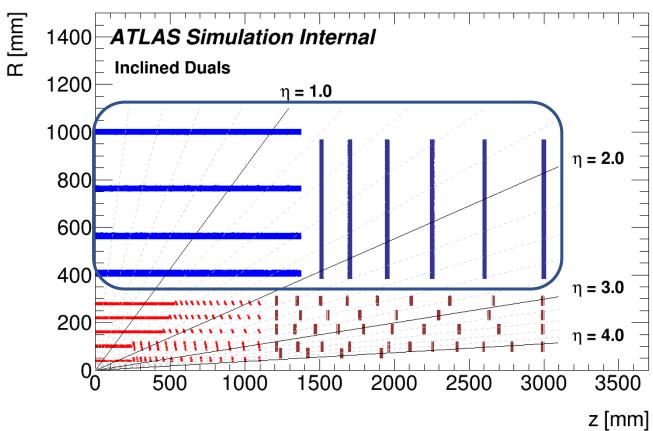

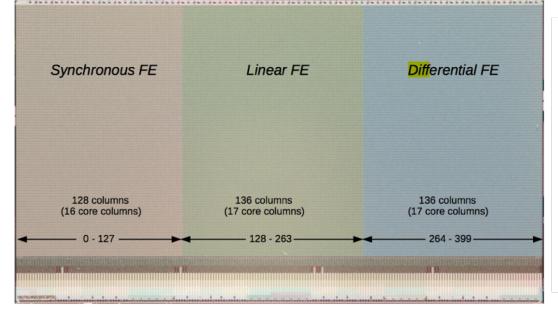

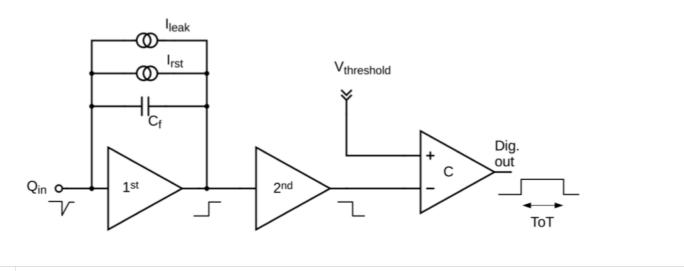

#### RD53A readout ASIC

RD53A is new readout ASIC for test bump pitch is 50x50 um to improve radiation resistivity, 65um process 3 front end type by region

| Feature                     | RD53A                                      | Prod. spec.                                | Comment                                 |  |

|-----------------------------|--------------------------------------------|--------------------------------------------|-----------------------------------------|--|

| Input pitch                 | $50  \mu \text{m} \times 50  \mu \text{m}$ | $50  \mu \text{m} \times 50  \mu \text{m}$ | aspect ratio defined by sensor          |  |

| Bump columns $\times$ rows  | 400 × 192                                  | $400 \times 384$                           |                                         |  |

| Input polarity              | Negative                                   | Negative                                   |                                         |  |

| Min. stable threshold       | 600 e <sup>-</sup>                         | 600 e <sup>-</sup>                         | with 50 fF load, $4\mu$ A/pixel analog. |  |

| In-time threshold           | < (thresh.+600 e <sup>-</sup> )            | < (thresh.+600 e <sup>-</sup> )            | varies w/ front end                     |  |

| Hit loss to in-pixel pileup | ≤1%                                        | ≤1%                                        | at 75 kHz avg. hit rate                 |  |

| Single pixel noise (ENC)    | <100 e <sup>-</sup>                        | <100 e <sup>-</sup>                        | with 50 fF load; varies w/front end     |  |

| Trigger latency             | <12.8 µs                                   | <35 µs                                     |                                         |  |

| Trigger mode                | single level                               | two level                                  |                                         |  |

| Current/pixel, analog       | 3-4 μΑ                                     | <4 μΑ                                      | varies w/ front end                     |  |

| Current/pixel, digital      | 4 μΑ                                       | 4 μΑ                                       | @ 75 kHz/pixel and 1 MHz trigger        |  |

| Current, periphery          | <150 mA                                    | <200 mA                                    | 4 enabled output drivers                |  |

| Command & control           | serial 160 Mbps                            | serial 160 Mbps                            | DC-balanced, no separate clock          |  |

| Output                      | $4 \times 1.28\mathrm{Gbps}$               | $4 \times 1.28\mathrm{Gbps}$               |                                         |  |

| Output protocol             | Aurora 64b/66b                             | Aurora 64b/66b                             | can use 1 to 4 lanes                    |  |

| Data aggregator output      | none                                       | bf 5.12 Gbps                               |                                         |  |

sensor structure

n+ in p bulk structureNo need to be full depletion to collect signal

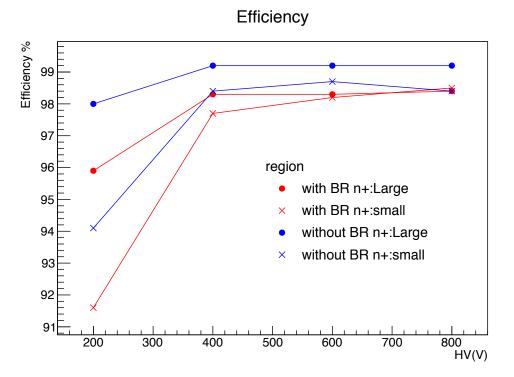

Japan group introduce bias rail structure for HV test without ASIC when production.

bias rail connect all pixel, and drop ground level.

bias rail sensor is large noise and low efficiency compare to w/o bias rail sensor. to solve these issue,

low noise sensor w/ bias rail

- large poly-Si resister

- small Al size

for high efficiency w/bias rail

■ large n+ pad

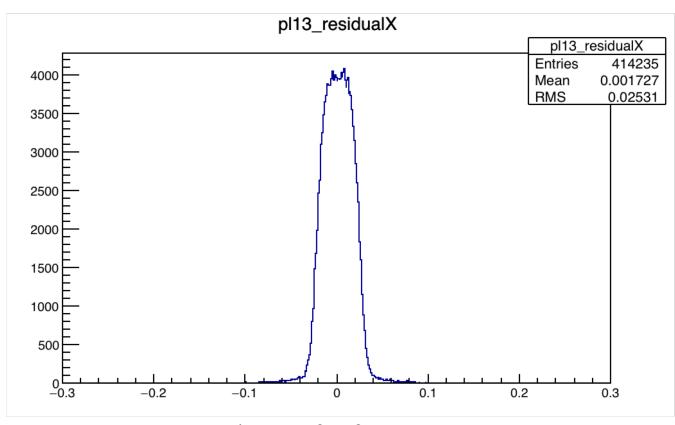

## position resolution

test beam @CERN SPS

#### Radiation resistant

$3^{\rm rd}$  sensor's fluence is  $3.0 \times 10^{15}\, 1 \rm MeV~n_{eq}$  during 10 years.

ATLAS request: Efficiency is >97% after radiation damage.

proton irradiation at CYRIC Tohoku University result of testbeam, w/ bias rail sensor efficiency is over 97% when 400V bias voltage

#### 600V

w/o bias rail structure large n+ efficiency  $99.23 \pm 0.01$

#### other test

■ RD53A ASIC probe test before flip chip, RD53A operation check using probe card remove broken RD53A before flip chip, because flip chip is high cost.

■ Threshold tuning test FEI4 pixel detector set in current ATLAS tracker has problem about tuning threshold. check about RD53A.