# A 4-Channel 10-Gbps/ch CMOS VCSEL Array Driver with on-chip Charge Pumps

Xing Huang,<sup>a,b</sup> Datao Gong,<sup>b</sup> Quan Sun,<sup>b</sup> Chufeng Chen,<sup>a,b</sup> Di Guo,<sup>a</sup> Suen Hou,<sup>c</sup> Guangming Huang,<sup>a</sup> Szymon Kulis,<sup>d</sup> Chonghan Liu,<sup>b</sup> <u>Andy Tiankuan Liu</u>,<sup>b</sup> Paulo Moreira,<sup>d</sup> Andrea Rodriguez,<sup>d</sup> Hanhan Sun,<sup>a,b</sup> Jan Troska,<sup>d</sup> Le Xiao,<sup>a</sup> Li Zhang,<sup>a,b</sup> Wei Zhang,<sup>a,b</sup> Jingbo Ye<sup>b</sup>

<sup>a</sup>Central China Normal University,

<sup>b</sup>Southern Methodist University,

<sup>c</sup>Academia Sinica,

dCERN

## Outline

- Motivation

- Design of charge-pump VCSEL Array Driver (cpVLAD)

- Measurement results

- Summary

## Motivation

2 4 6

8 10

Bias Current [mA]

12

Jan Troska's presentation in TWEPP 2017: https://indico.cern.ch/event/608587/contri butions/2614150/

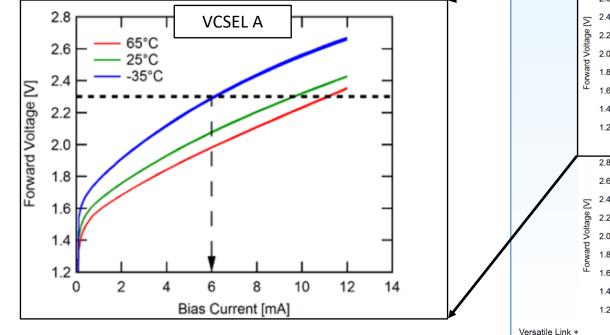

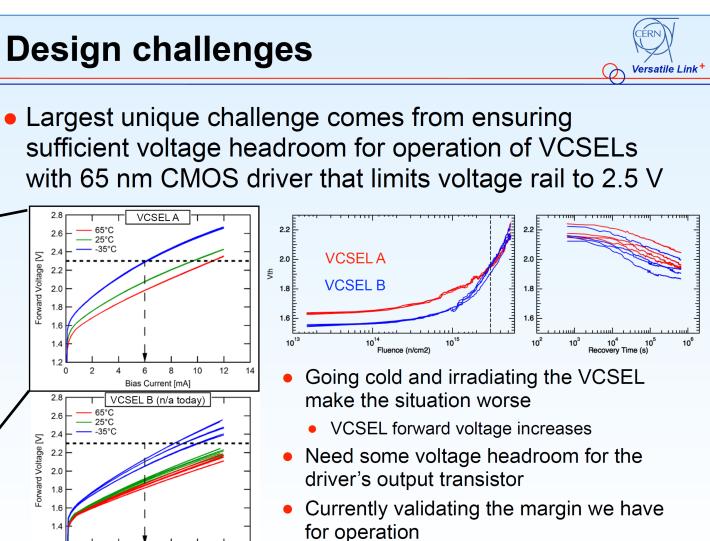

Low temperature and radiation increase the VCSEL forward voltage and compress the headroom.

jan.troska@cern.ch

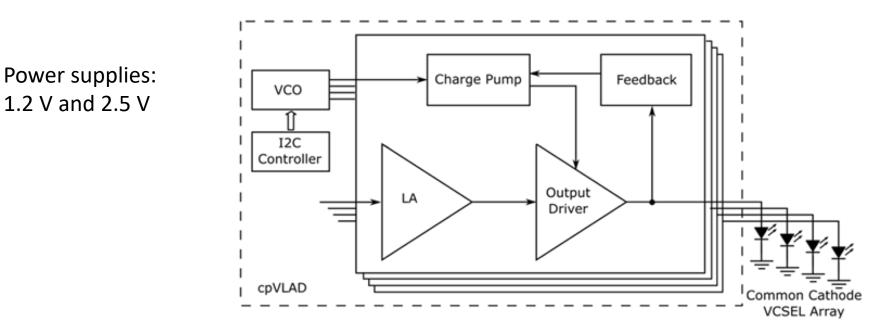

## Diagram and key features

• The on-chip charge pump generates a voltage higher than 2.5 V for each output driver.

- The feedback circuit adjusts the output voltage of the charge pump so that when the forward voltage of the VCSEL diode, the CP output voltage changes accordingly.

- A shared VCO provides a clock signal for each charge pump.

- Only 1.2-V core devices are used in the whole design for radiation tolerance. Careful checks are performed to make sure no overdriving violation.

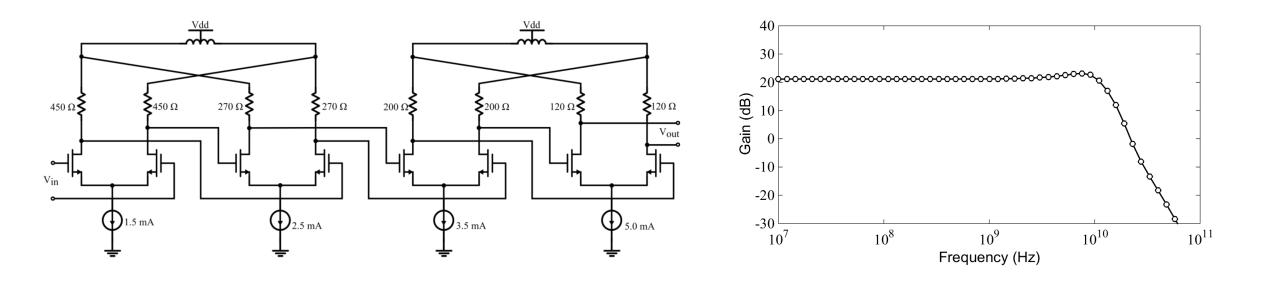

## Design of limiting amplifier (LA)

- A four-stage LA amplifies the signal amplitude from 100 mV to 800 mV (peak-peak).

- Two amplifiers share a peaking inductor to save the chip area.

- The overall LA achieves a total gain of 21.5 dB and a bandwidth of 12.0 GHz with a power consumption of 15 mW at the typical corner, 1.2 V, 27 °C.

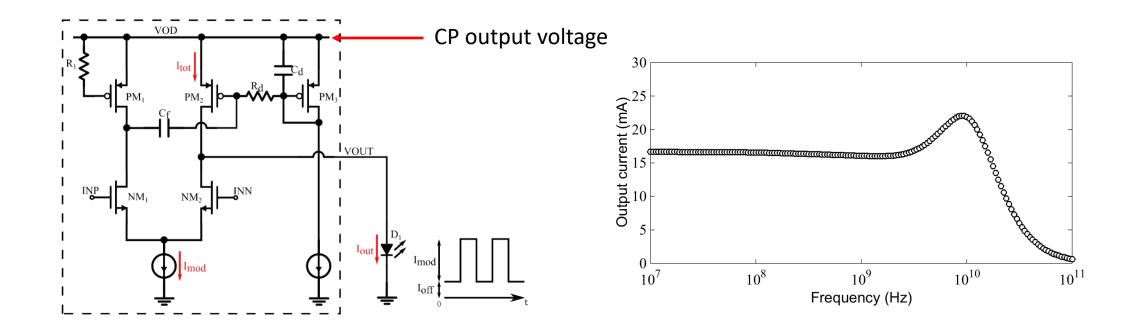

## Design of output driver

- The output driver receives the differential outputs from the LA and provides the bias current and the modulation current to the laser diode.

- The bandwidth shown in the figure is 20.3 GHz at the typical process corner, 2.5 V, 27 °C.

## Design of charge pump

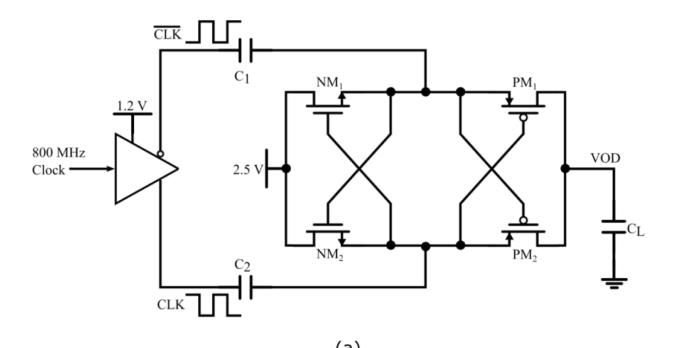

- The charge pump uses crossconnected NMOS and PMOS transistors driven by an 800 MHz 1.2 V clock from the VCO to boost the 2.5 V power supply to a higher voltage for the output driver.

- The 800 MHz clock comes from the VCO. The frequency is chosen to reduce capacitor area and voltage ripple.

VOD

$-C_L$

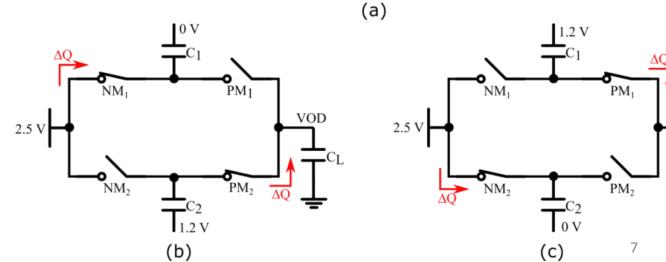

## Design of feedback circuit

- The negative feedback circuit keeps the voltage difference between the CP output and the anode of VCSEL constant when the VCSEL forward voltage changes.

- The voltage difference is programmable.

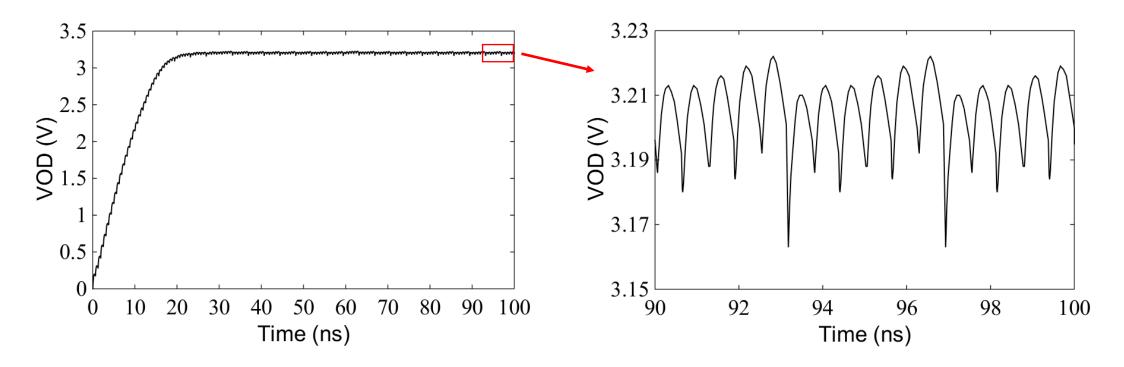

## Simulation of the charge pump power up

- In 30 ns after the power up, the output voltage of the charge pump settled to a steady voltage of about 3.2 V with a peak-to-peak ripple of 60 mV in a typical operating condition.

- An optimized combination of a load capacitor (155.4 pF) and an 800-MHz VCO frequency is chosen based on the area and process performance consideration.

- The final charge pump module takes an area of 200 um x 1000 um and is integrated into each channel of the cpVLAD.

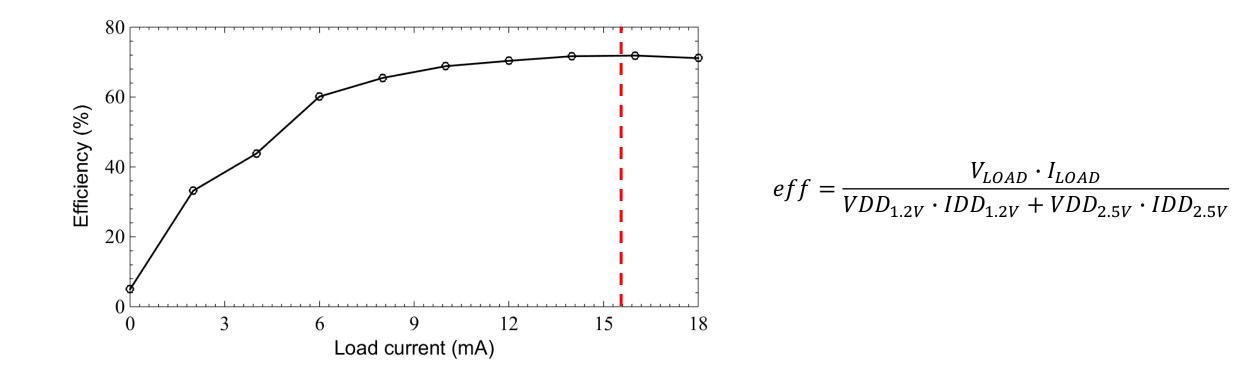

### Simulated efficiency of the charge pump

• When the load current is 16 mA, the power efficiency of the charge pump is 70.5 %.

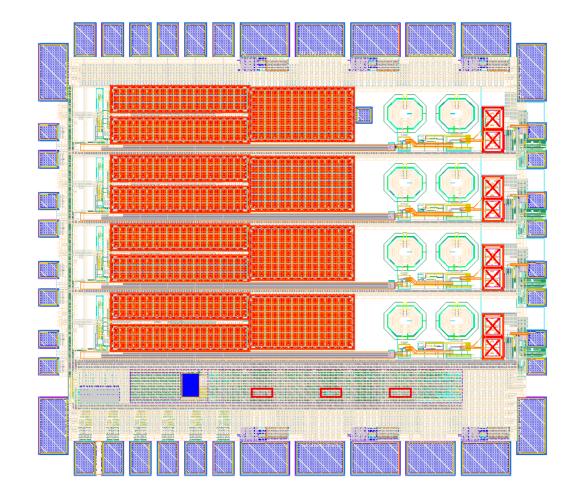

#### Layout

die 1.85 mm x 1.635 mm

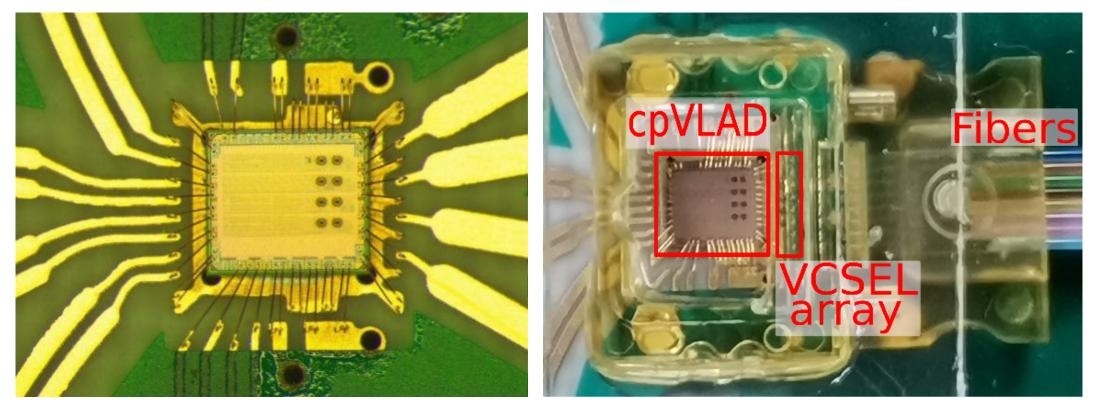

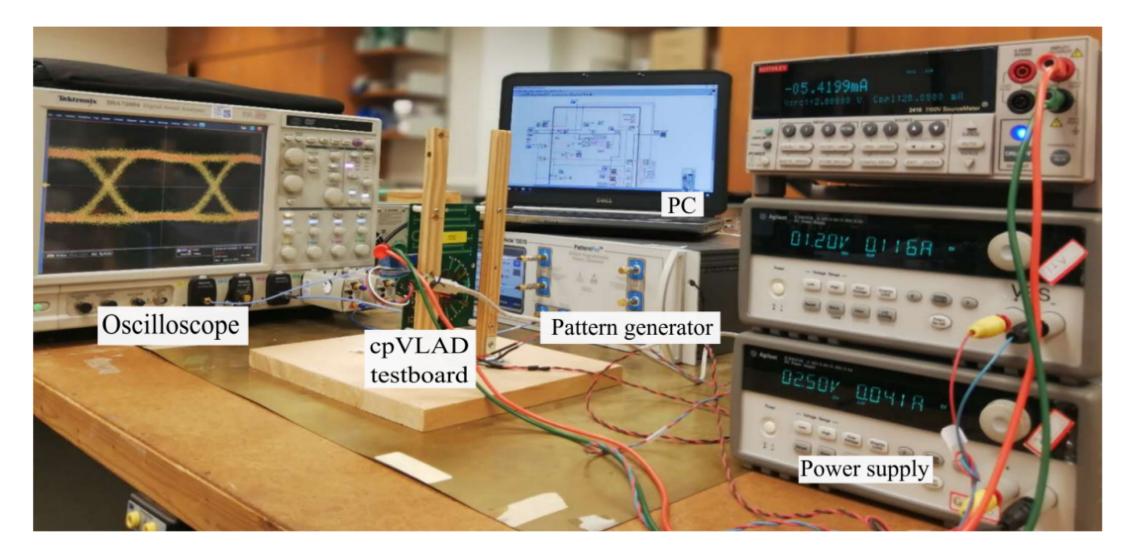

## Photographs of the cpVLAD

Electrical test boards

optical test boards

• Electrical test boards and optical test boards are assembled at CERN.

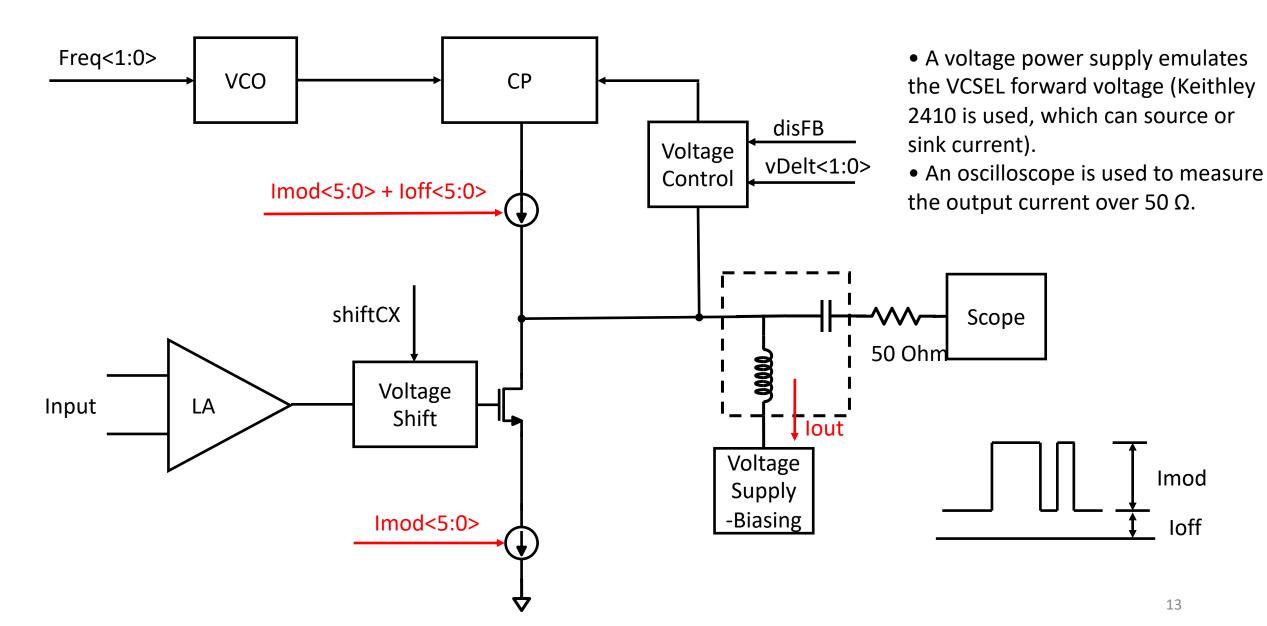

## Block Diagram (ch1-3) – Electrical Test

13

Imod

loff

#### Test setup

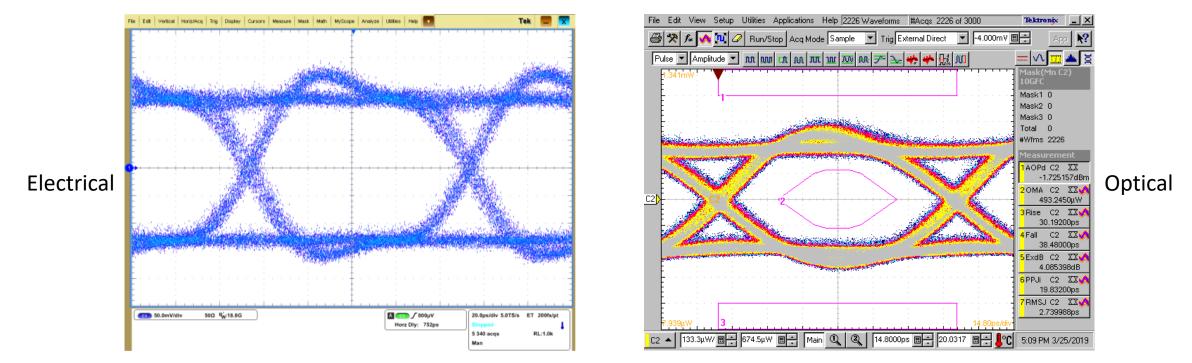

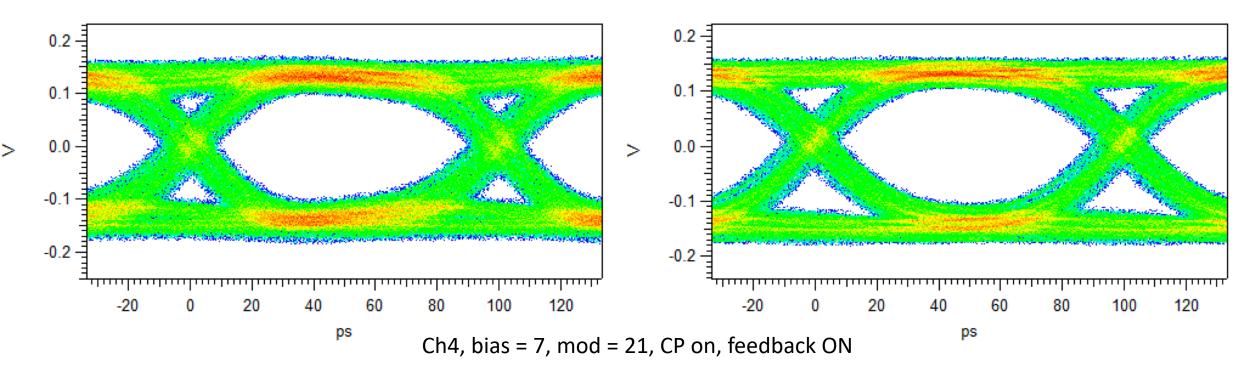

## Eye diagrams

- Both the electrical and optical eye diagrams were measured at 10 Gbps with the input amplitude of single-ended 200 mV.

- The total jitter of the electrical eye diagram is 24.4 ps (peak-peak) at the Bit Error Rate (BER) of 1x10<sup>-12</sup> with a random jitter of 0.91 ps (RMS).

- The tested average optical power (AOP) is -2.76 dBm. The optical modulation amplitude (OMA) is 373.67 μW.

- The power consumption of the cpVLAD is 79.5 mW/channel

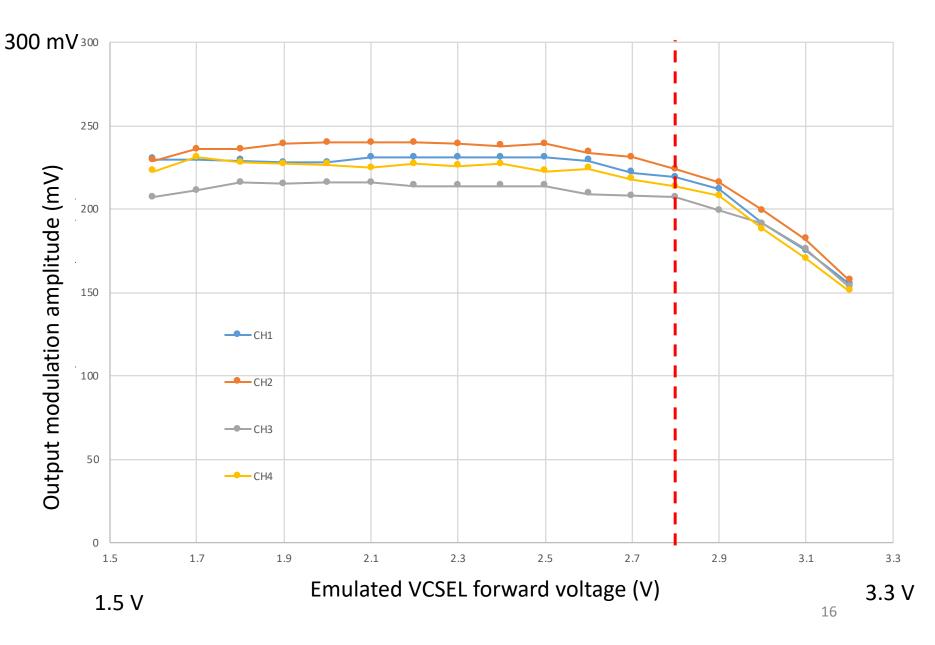

## Headroom improvement

- The charge pump function was verified in the electrical test by increasing the DC voltage of the external biastee structure.

- The cpVLAD can survive up to 2.8 V forward voltage with a stable modulation output.

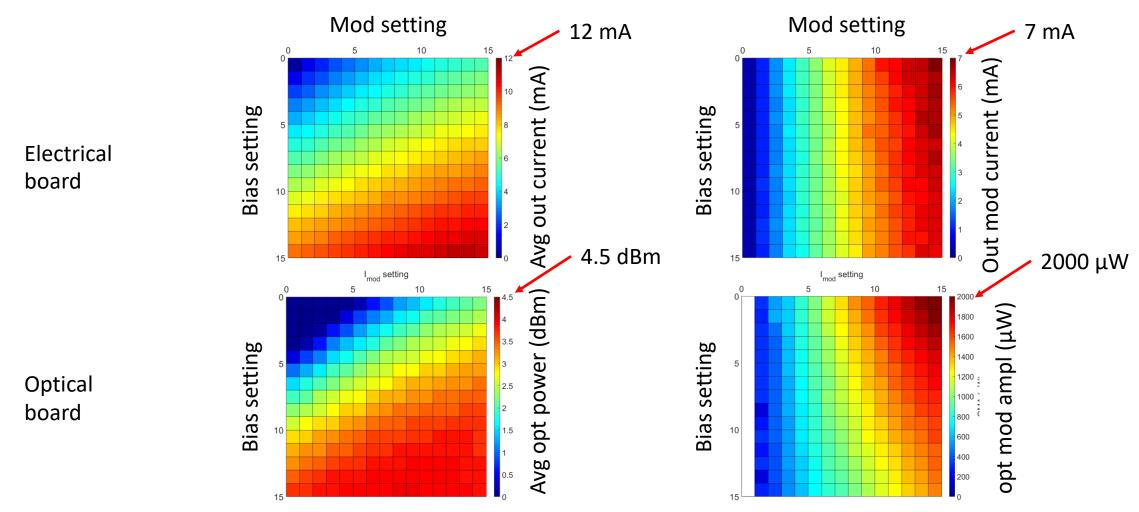

## Current sweeping

- The electrical output average current and the optical average power follow the same trend

- The electrical output modulation current correlates only the I<sub>mod</sub> setting but hardly the I<sub>bias</sub> setting, the OMA range at with a small I<sub>off</sub> setting is less than that with a large I<sub>off</sub> setting

#### Temperature test results

-35 °C, Vbias-tee = 2.8 V

+65 °C, Vbias-tee = 1.8 V

- The ambient temperature of the VL+ is specified to be from -35 °C to +65 °C.

- The cpVLAD has been verified that the cpVLAD can operate in the whole temperature range.

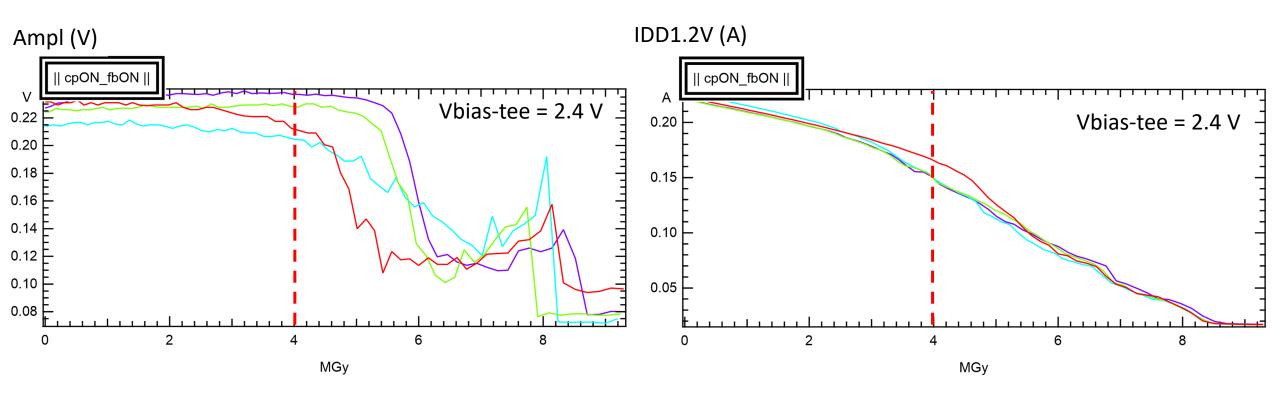

### Irradiation test results

- Irradiated in x rays while powered on

- One electrical test board, 69 hours, total dose 9 MGy, dose rate 130 kGy/h

- One optical test board, 90 hours, total dose 6.3 MGy, dose rate of 70 kGy/h

- cpVLAD functioned properly in 4 MGy.

## Summary

- A four-channel 10-Gbps/ch VCSEL array driver ASIC, cpVLAD, with on-chip charge pumps has been designed and prototyped in a 65-nm CMOS technology.

- □With 1.2 V and 2.5 V supply voltages, cpVLAD functions with an emulated VCSEL forward voltage of up to 2.8V with the power consumption of 79.5 mW/channel.

- □ cpVLAD has been tested for operating in the temperature range of from -35 °C to +65 °C.

- **C**cpVLAD has been verified for up to 4 MGy.