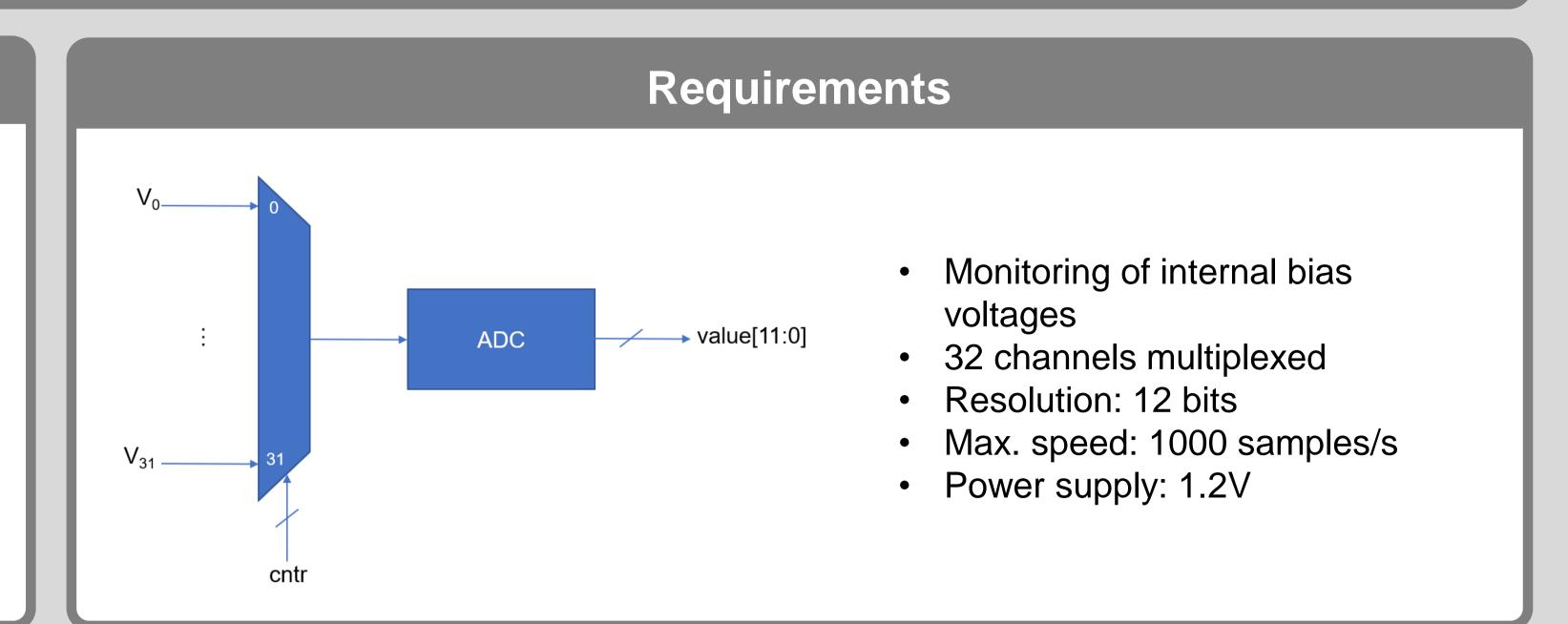

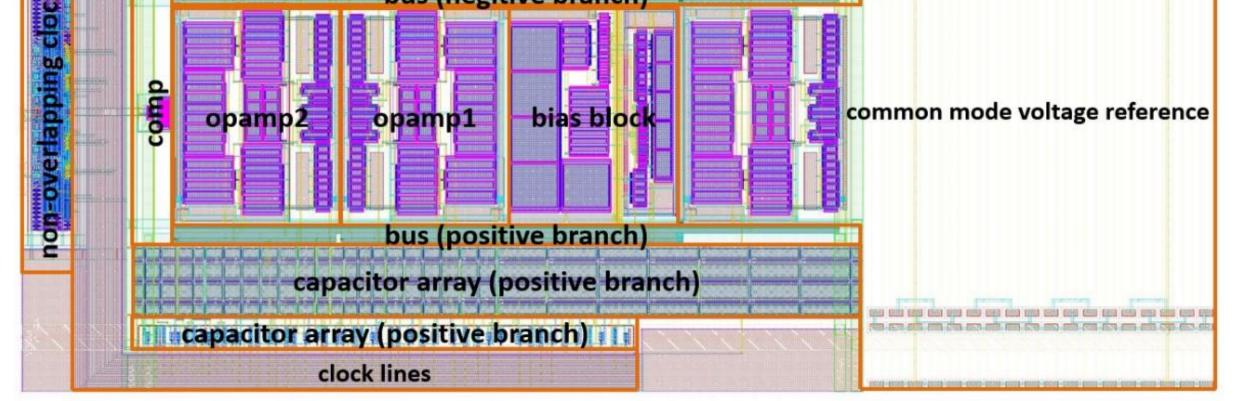

## A Monitoring 12-bits Fully Differential Second Order Incremental **Delta Sigma Converter ADC for TimePix4**

Raimon Casanova<sup>1</sup>, Tianya Wu<sup>1,2</sup> 1) Institut de Física d'Altes Energies (IFAE), Barcelona, Spain 2) Central China Normal University, Wuhan, China

## Introduction

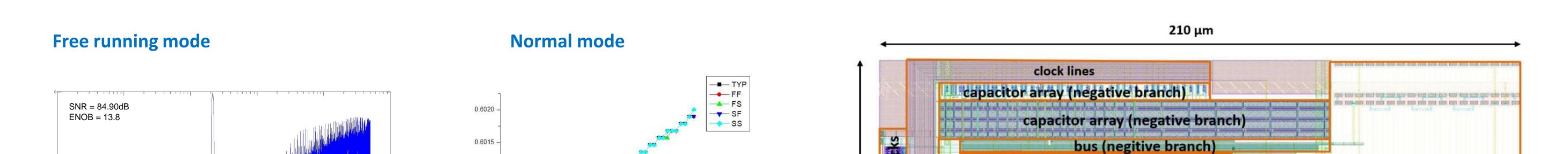

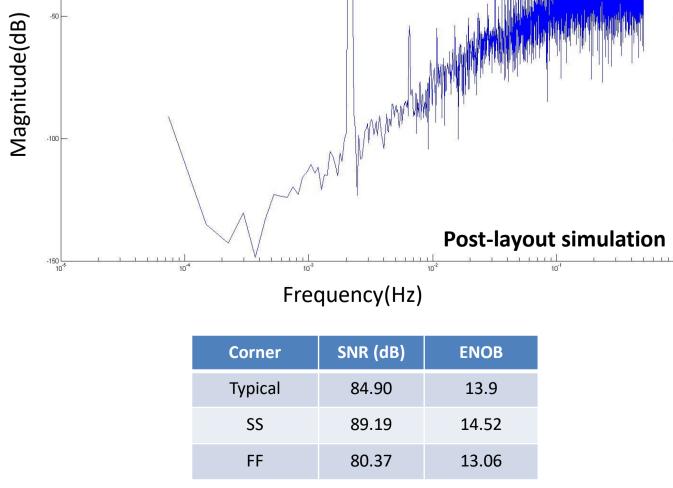

SAR converters are usually the natural choice to implement monitoring ADCs. Additional circuits for calibration are needed to compensate process variations which become more important for high resolutions and in deep-submicron technologies. This poster presents a 12-bits second-order incremental sigma delta converter for TimePix4 fabricated in TSCM 65nm. It does not need calibration and is robust to process variations because most of the signal processing is performed in the digital domain. It provides a maximum conversion rate of 1kHz/s, enough for monitoring the internal signals of the chip, consuming only 8µW. Simulations show a SNR of 84.9dB operating in free-running mode.

## Incremental Delta Sigma Converter

- Delta sigma converters offer high resolution and moderate speeds. •

- Most of the digital processing is performed in the digital domain:

- Robust to analog parameter variations

- Technologically scalable

- Incremental Delta Sigma converters can be considered delta sigma converters operating in transient mode which can be reset periodically.

- Main features:

- Sample to sample conversion

- Provide high resolution

- Low offset and gain errors

- Resetable (it can be multiplexed between multiple channels)

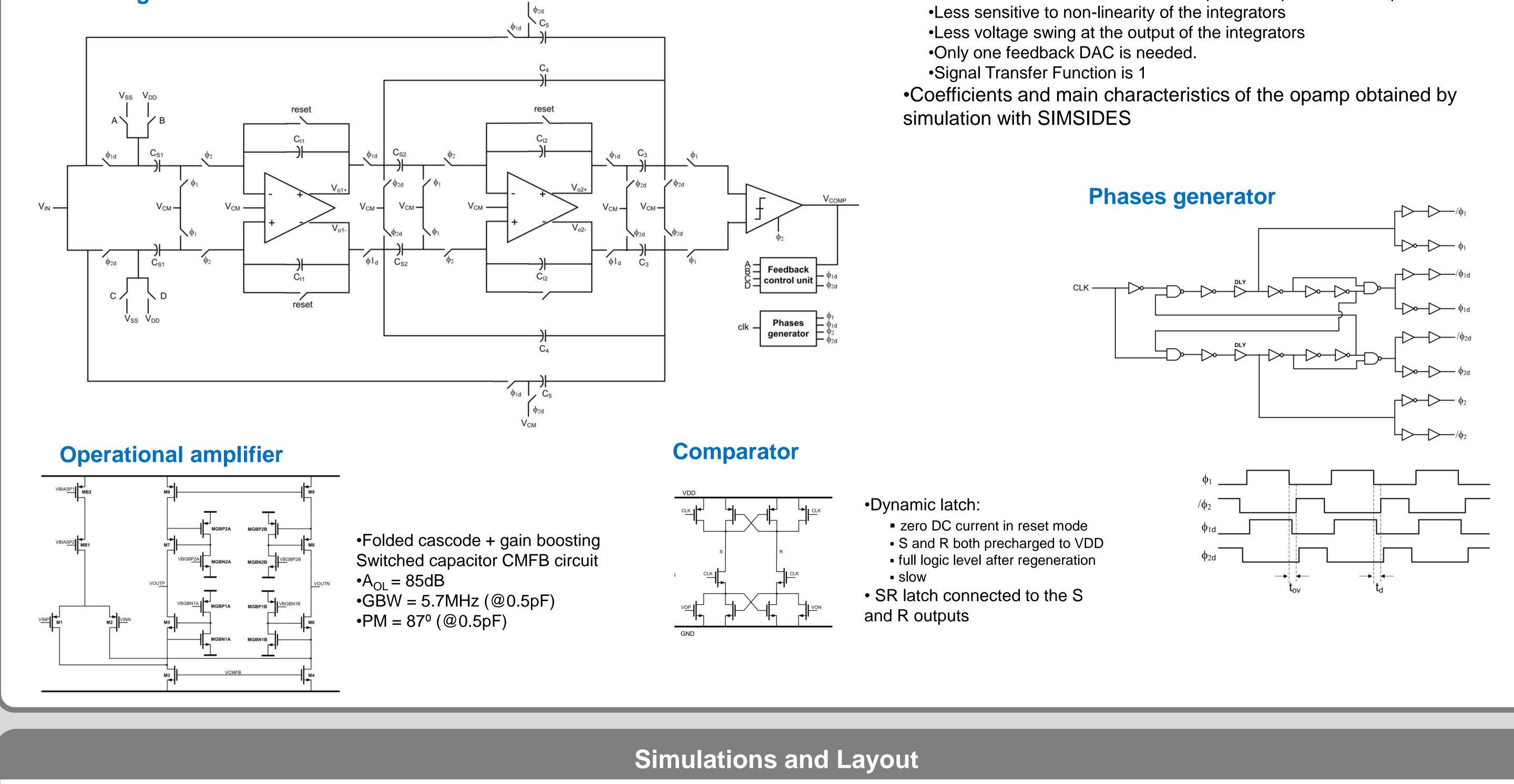

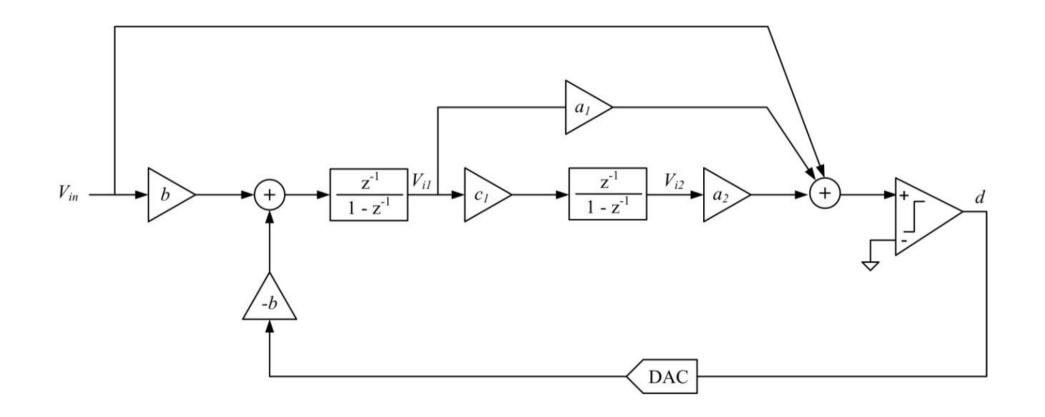

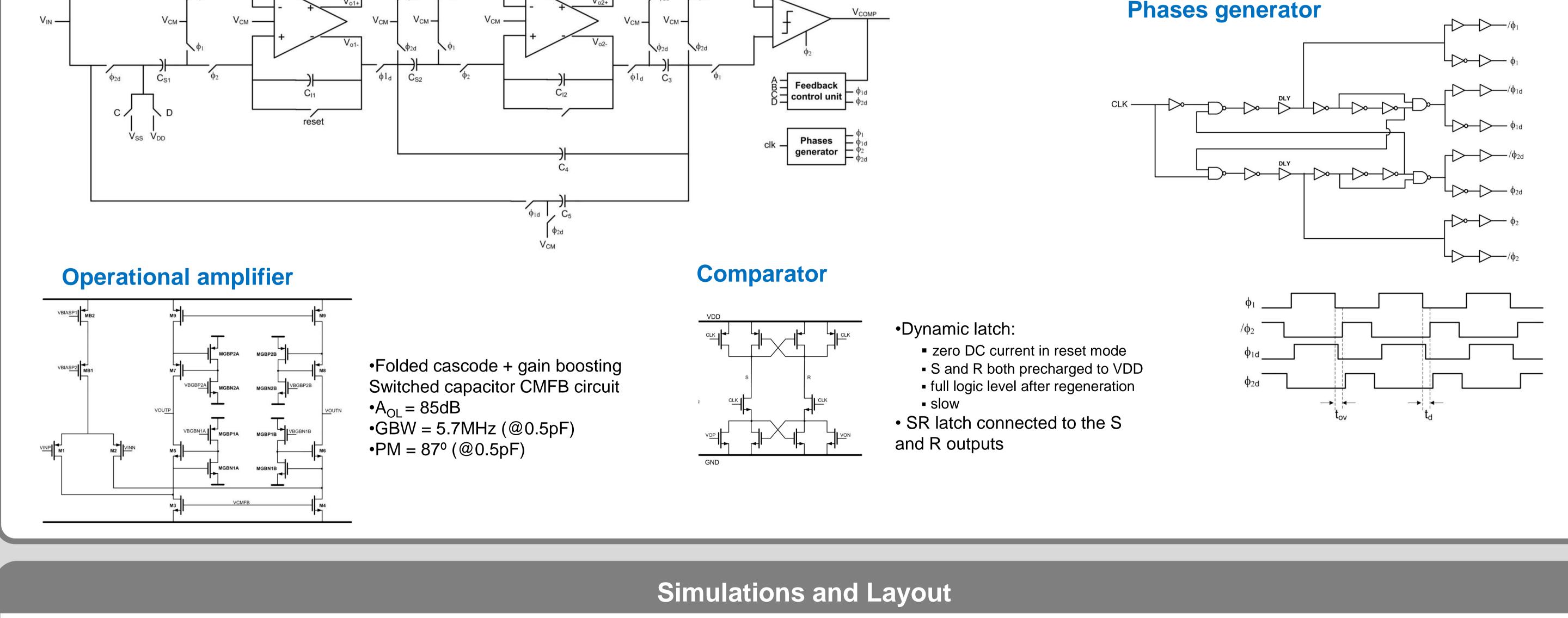

•2<sup>nd</sup> order Cascaded Integrators Feed Forward (CIFF) architecture:

- •Tradeoff between area, conversion speed and power consumption

100 µm

- Sinusoidal input signal:

- Amp:0.55 V

- Freq. 543 Hz

- OSR = 210

- FFT: 64 \* 210

- Simulation time: 2 days

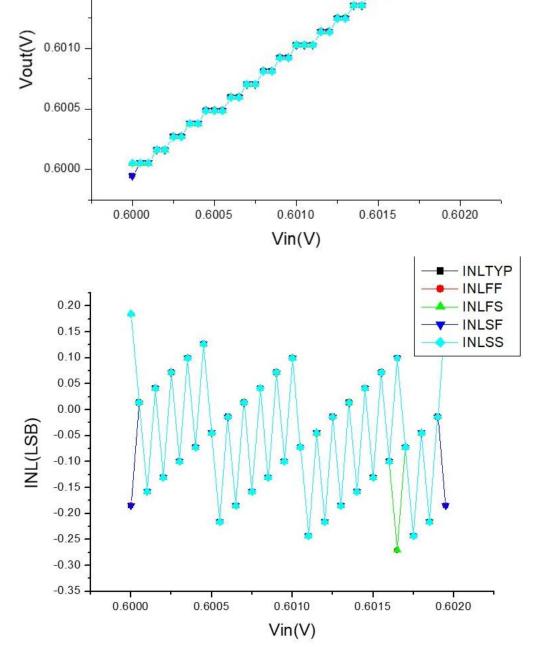

•Not possible to simulate the whole dynamic range (long simulation time) •Only small regions analzsed

| Main features               |                                                                     |

|-----------------------------|---------------------------------------------------------------------|

| Bias voltage                | 1.2V                                                                |

| Full scale voltage          | 1.1V                                                                |

| Resolution                  | 12bits                                                              |

| Max. conversion rate        | 1190samples/s                                                       |

| Power consumption           | 3.5μW (Delta sigma modulator)<br>4.5μW (VCMRF)<br><b>Total:</b> 8μW |

| OSR                         | 210                                                                 |

| Max. oversampling frequency | 250kHz                                                              |