# SEU test of 110 nm CMOS UMC technology

D. Calvo

P. De Remigis, M. Fisichella, R. Wheadon (INFN-Torino) S. Mattiazzo (INFN-Padova and Dip Fisica, Università di Padova) E. Verroi (INFN-TIFPA)

F. Tommasino (INFN-TIFPA and Dip Fisica Università Trento) A. Zambanini (ZEA – Electronics Systems, FZ Juelich)

E [MeV]

87.66

95.40

141.61

162.66

190.81

218.91

247.04

### SEU TEST using the CHANNEL CONFIGURATION REGISTERS of PASTA, FIRST PROTOTYPE of the READOUT ELECTRONICS of the SILICON STRIP DETECTOR of PANDA

- PASTA ASIC developed by JLU Giessen, FZ Juelich and INFN Torino

- Chip developed in 110 nm UMC technology

- Challenging requests on power dissipation (≈ 4mW/ch) and size  $(4.5 \times 3.2 \text{ mm}^2)$

- 64 channels, nominal clock frequency of 160 MHz

- ToT measurements, 8 bit (dyn. range) charge resolution

- Radiation tolerant circuits to Single Event Upset (SEU) effects are implemented

- TMR (Triple Modular Redundancy) technique for registers just 1 bit long

- Hamming Encoding for registers longer than 1 bit

- Channel configuration word 42 bits long (13 bits with TMR) and 8 registers with Hamming Encoding for a total of 29 bits)

Sensitive volume:

$1 \times 1 \times 1 \mu m^3$

Testing board with PASTA

## TEST with ION BEAMS @ SIRAD FACILITY in the LABORATORIO NAZIONALE di LEGNARO – INFN (ITALY)

- DAQ based on LABView and VIRTEX 6 FPGA

- Balanced sequence of 1 and 0 is used to configure the channel configuration register of each channel (TMR: 5 bits set to 1, 8 bits to 0; Hamming Encoding: 12 bits set to 1, 17 bits to 0)

- The **procedure to detect SEU** events foresees:

- a writing command to configure the ASIC

- a reading phase till a SEU is detected

- the SEU event is registered

- the sequence starts again from a new writing command

- The DAQ program counts the number of times when a bit changes its value and writes it to the output file

- D.U.T. is placed in the vacuum chamber

- Long cables limit clock frequency to 50 MHz

- 7 different type of ions were used to evaluate the SEU cross section of the chip under test (2688 bits for the 64 channels)

| ţį                      | F F                   |     | χ² / n | df      | 1         | 134.6 / 4          |  |  |

|-------------------------|-----------------------|-----|--------|---------|-----------|--------------------|--|--|

| Cross Sectio            |                       |     | p0     |         | 10.3±     | 0.3284             |  |  |

| SS (                    | 10 <sup>-10</sup> = ± |     | p1     | 1.499e- | 08±9.6    | 608e-10            |  |  |

| S                       |                       |     | p2     | 1.525e- | -12 ± 5.0 | 048e-11            |  |  |

|                         | F <sub>T</sub> /      |     |        |         |           |                    |  |  |

|                         | 10 <sup>-11</sup> = / |     |        |         |           |                    |  |  |

|                         | E/                    |     |        |         |           |                    |  |  |

|                         | 10                    |     |        |         |           |                    |  |  |

|                         | $10^{-12}$ 0 1 2      | 3 4 | 5 (    | 6 7     | 8         | 9                  |  |  |

|                         |                       |     | _      | •       | Ede       | <sub>ep</sub> [MeV |  |  |

| SEU cross section       |                       |     |        |         |           |                    |  |  |

| in hadronic environment |                       |     |        |         |           |                    |  |  |

|                         |                       |     |        |         |           |                    |  |  |

$\Sigma : 3.6 \cdot 10^{-16} \text{ cm}^2 / \text{bit}$

(following the procedure described in ref: M. Huhtinen and F. Faccio, NIMA 450 (2000))

E<sub>dep</sub> [MeV]

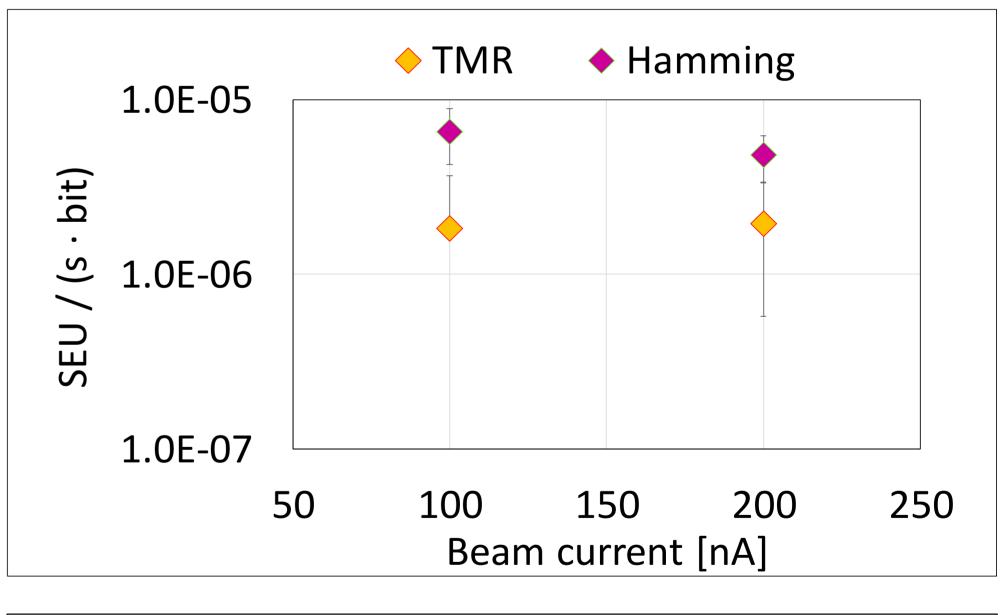

# TEST with PROTON BEAM @ the EXPERIMENTAL ROOM of INFN-TIFPA in the PROTON-THERAPY CENTRE of TRENTO (ITALY)

- D.U.T. is placed in front of the beam line exit

- Short cables allow to perform measurements at the nominal clock frequency of 160 MHz

- To compare information to the results obtained at LNL, additional measurements with 50MHz clock frequency were performed

- Proton beam energy: 131.3 MeV

- Beam current up to 300 nA

| Beam current [nA]             |                       |                       |  |  |  |  |

|-------------------------------|-----------------------|-----------------------|--|--|--|--|

| 100                           | 200                   | 300                   |  |  |  |  |

| Proton flux on the chip [p/s] |                       |                       |  |  |  |  |

| (10% of error)                |                       |                       |  |  |  |  |

| $2.8 \cdot 10^{8}$            | 5.5 · 10 <sup>8</sup> | 7.8 · 10 <sup>8</sup> |  |  |  |  |

| _                             | 50 MHz                | 50 MHz                |  |  |  |  |

| 160 MHz                       | 160 MHz               | _                     |  |  |  |  |

#### **COMPARISON of RESULTS obtained** with IONS and PROTONS

@  $7.8 \cdot 10^8$  p/s on the chip

- proton test → direct measurement  $2.19 \cdot 10^{-6} \, SEU/(s \cdot bit)$

- ion test  $\rightarrow$  using evaluated  $\Sigma$  $2.26 \cdot 10^{-6} \, \text{SEU/(s·bit)}$

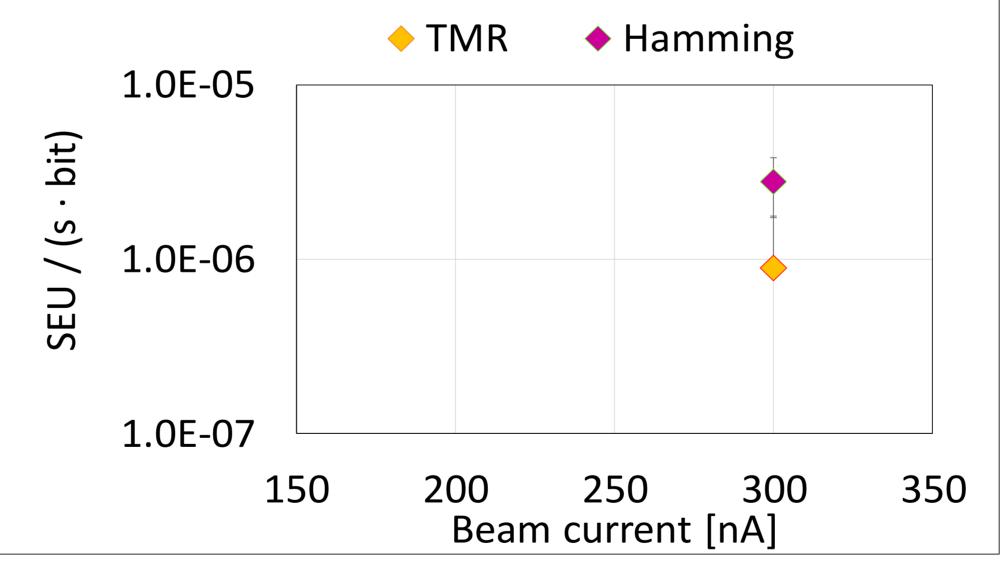

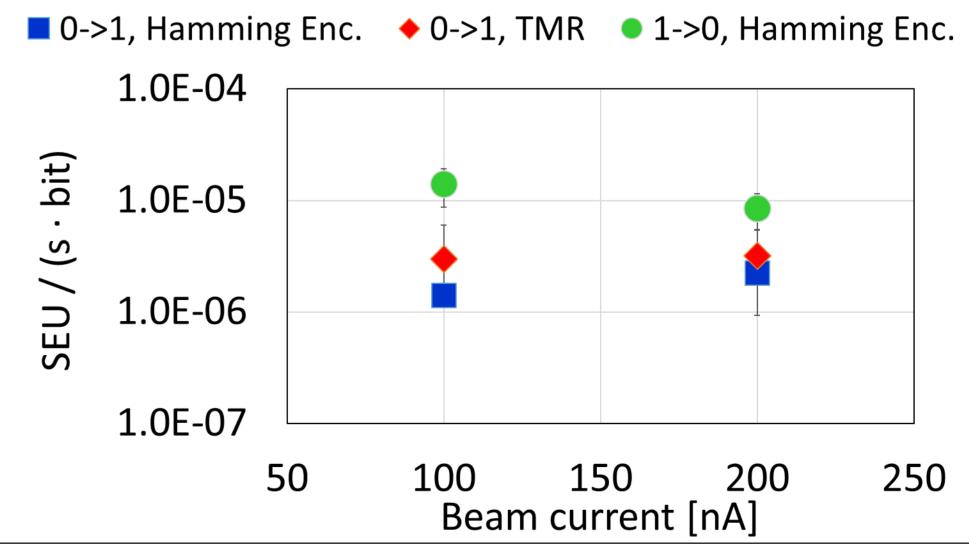

# Clock @ 50 MHz

- The number of SEUs for all the bits with TMR (and for registers with Hamming Encoding) increases with the beam intensity since at 200 nA no SEUs were detected

- Bits protected with TMR are more tolerant with respect to bits of registers implementing Hamming Encoding for  $1\rightarrow 0$  flip event; viceversa for  $0 \rightarrow 1$  events

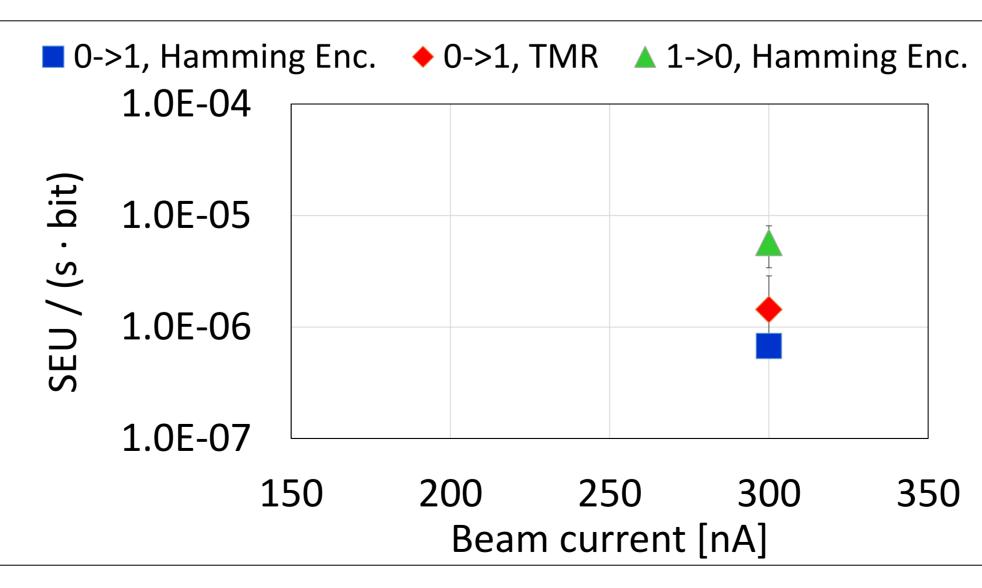

#### Clock @ 160 MHz

- The number of SEUs for all the bits of registers with Hamming Encoding decreases in the range of tested beam intensity. In the case of TMR, the SEUs number is stable.

- Bits protected with TMR are more tolerant with respect to bits of registers using Hamming Encoding for  $1\rightarrow 0$  flip event; viceversa for  $0 \rightarrow 1$  events