# System-on-Chip Workshop 12-14 June, CERN

### WELCOME!

https://indico.cern.ch/event/799275

# System-on-Chip Workshop

This workshop wants to be a forum to exchange experience and ideas, to identify commonality and differences, to propose common solutions wherever applicable, and to point out issues that need follow up.

Interest Group "System-on-Chip for Electronics" → Mailing list: system-on-chip@cern.ch

### **Organisation of the Workshop**

## **Organising Committee**

- We wish you a warm WELCOME!

- If you have questions on the organisation of the workshop or on your presentations, etc. please contact any of us.

- You can also send and email to the organizers: <u>SoC-Workshop-Organisers@cern.ch</u> or if it is of general interest: <u>System-on-Chip@cern.ch</u>

# **Overview of the Workshop**

|           | WED, June 12<br>Room 30/7-018   | THU, June 13<br>Room 40/S2-B01 | FRI, June 14<br>Room 40/S2-C01 |

|-----------|---------------------------------|--------------------------------|--------------------------------|

| Morning   | Manufacturer<br>Presentations 1 | Tutorials &<br>Presentations 1 | Tutorials &<br>Presentations 3 |

|           | Coffee/tea break                | Coffee/tea break               | Coffee/tea break               |

|           | Manufacturer presentations 2    | Tutorials &<br>Presentations 2 | Tutorials &<br>Presentations 4 |

|           | Lunch                           | Lunch                          | Lunch                          |

| Afternoon | Overview<br>and Use Cases 1     | Use Cases 3                    | System Aspects 1               |

|           | Tea/coffee break                | Tea/coffee break               | Tea/coffee break               |

|           | Use Cases 2                     | Use Cases 4                    | System Aspects 2               |

- Please have a look at <u>https://indico.cern.ch/event/799275</u>

- Note: use different rooms: WED: bldg. 30/7-18, THU&FRI: bldg. 40/Salle Bohr and Salle Curie.

- Rooms in bldg. 40 are limited to a capacity of 100 apologies! We will use Vidyo ...

- Coffee/tea is kindly offered by EP-ESE, EP-CMD and ATLAS.

- We will take minutes, in particular of discussions, which will be published later in Indico.

- Hope to have lively discussions ...

### **Motivation for the Workshop**

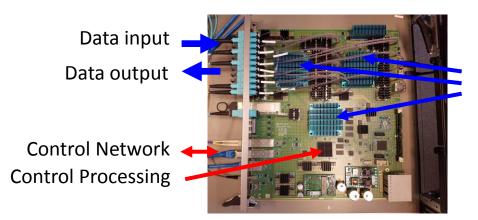

## **Electronics Modules**

Data Processing FPGAs

### Many electronics modules for trigger and readout in particle physics experiments have a similar structure:

- Several high-end FPGAs for processing, usually 1 to 5.

- Many high-speed links for data input and output, usually ~10 to ~500 links of 1 to 28 GBits/s (planned) .

- Something for control ... a System-on-Chip

### **Control** (send commands), **Configuration** (load data), **Monitoring** (collect data):

- Hardware related, e.g. settings and actual values of power, clock, optical chips, FPGAs, etc., usually using industry standard protocols like I2C, SPI, JTAG, etc.

- **Run control related**, i.e. related to physics/run (functionality implemented in firmware of FPGAs), e.g. control and status registers, memories, look-up tables, counters, physics data, etc.

## **Electronics Systems**

#### Legacy VME Crate In the past, very popular - VME: FPGA VME FPGA VME VMEIF Hardware control: CANbus SBC Run Control FPGA **Run control**: Single-Board Computer (SBC) Internal GbEthernet Bus or VME bridge and PC **Detector Control** CANbus Timing Clocks Update Ports Today, many new projects use ATCA: Fabric Interface [Full Mesh] 8 diff. pairs each) Control is oriented towards GbEthernet: Base Interface [Ethernet Dual Star] (4 diff. pairs each) Hardware control: PMR Stor 8 Ring/Test Lines Blade $\rightarrow$ IPMI $\rightarrow$ shelf manager $\rightarrow$ SCADA\* 48VDC Power ATCA Backplane Central Fabric Switch Blades **Run control:** Via hub module and base interface, or directly to each ATCA blade ... $\Rightarrow$ Need a new control strategy! \*SCADA = Supervisory Control And Data Acquisition

ATCA Hardware Platform Management

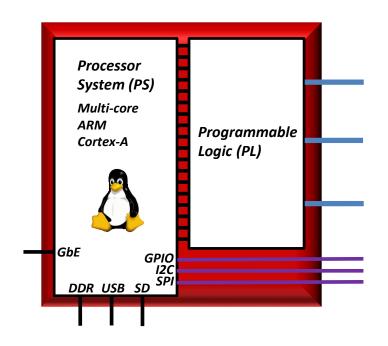

## System-on-Chip

### System-on-Chip:

Processor system + programmable logic  $\Rightarrow$  "CPU and FPGA"

- Processor system (PS) = like CPU:

- Currently all are multi-core ARM processors

- Has memory and peripherals, e.g. GbEthernet, I2C, SPI, GPIO, etc.

- Runs software: "bare-metal" application or operating system, e.g. Linux

### • Programmable logic (PL) = like FPGA:

- Has logic cells, memory blocks, and I/O links, e.g. Multi-Gigabit Transceivers (MGTs)

- Implements real-time data logic, interfaces to the other processing FPGAs, can implement more peripherals, e.g. 10GbEthernet, etc.

### → Examples of SoCs:

Xilinx Zynq SoC, Xilinx Zynq UltraScale+ MPSoC, Intel Stratix 10 SoC

This definition of SoC is more restrictive than in Wikipedia

We will hear from the manufacturers during this morning's session

## **Use of System-on-Chip**

- Interface between hardware and software

- Programmable Logic part of SoC very well known to hardware designers

- Processor System of SoC provides a lot of flexibility and integrates the electronics modules into the control network(s)

- Possibility to push more "intelligence" into the electronics modules

- Typical use cases for SoCs:

- Interactive tools

- Integration with Detector Control System for hardware control

- Integration with Run Control System for operational control

- Trigger processing

- Readout of physics data

- Physics-oriented calibration and monitoring tasks

- Etc.

We will see many examples during the "Use cases" and "Tutorials&Presentations" sessions

# System-on-Chip Workshop

### Concerns and issues on use of SoCs:

- Hardware/firmware part:

- Exchange of experience and of solutions:

Can we provide a common repository of IP blocks?

- Provide common hardware solutions:

Can we provide recommendation on the hardware choice? Is possible to build or purchase a common SoC mezzanine card for control?

- Software part: flexibility has a cost = support and maintenance

- How to organise network, in particular, with many, o(100-1000), SoCs: Network switches, IP numbers, boot services, etc.

- How to provide network security:

Technical control networks for experiments and beams have strict security requirements.

- Provide common software solutions:

Common support for operating system, drivers, libraries, tools?

- Provide long-term maintenance:

Can a common SoC mezzanine card address this issue?

### ... and probably more. Your input is important!

Many of these issues will be discussed during the "System Aspects" sessions

### Have a good workshop!