**EXPERIMENT**

INFN

# Readout demonstrator for a Large-Scale Pixel-Detector conforming to the ATLAS Phase-II Upgrade

Alessandro Gabrielli University of Bologna and INFN

On behalf of the ATLAS TDAQ Collaboration

Dec 2019

HSTD12 2019

Page 1 of 20

## OUTLINE

#### **ATLAS Pixel off-detector readout overview**

#### **Current status**

**ROD** vs **FELIX** cards **Readout** Evolution

#### **RD53A-to-FELIX readout chain**

Phase-I **FELIX** board π**LUP** board DAQ demonstrator

### **Conclusions and Future developments**

Also see "ATLAS ITk Pixel Detector Overview" by Craig Buttar and.....

<u>«Data-acquisition system developments for ATLAS pixel QA/QC test toward High Luminosity LHC»</u> by Kazuki Todome

## **The ATLAS Pixel Detector**

The **Pixel Detector** is the innermost subdetector of the **ATLAS** Experiment and part of the **Tracker** (Inner Detector)

Very critical area! Exposed to extremely high dose of radiation Today we have 92 million channels (pixels) altogether being read out

PARED

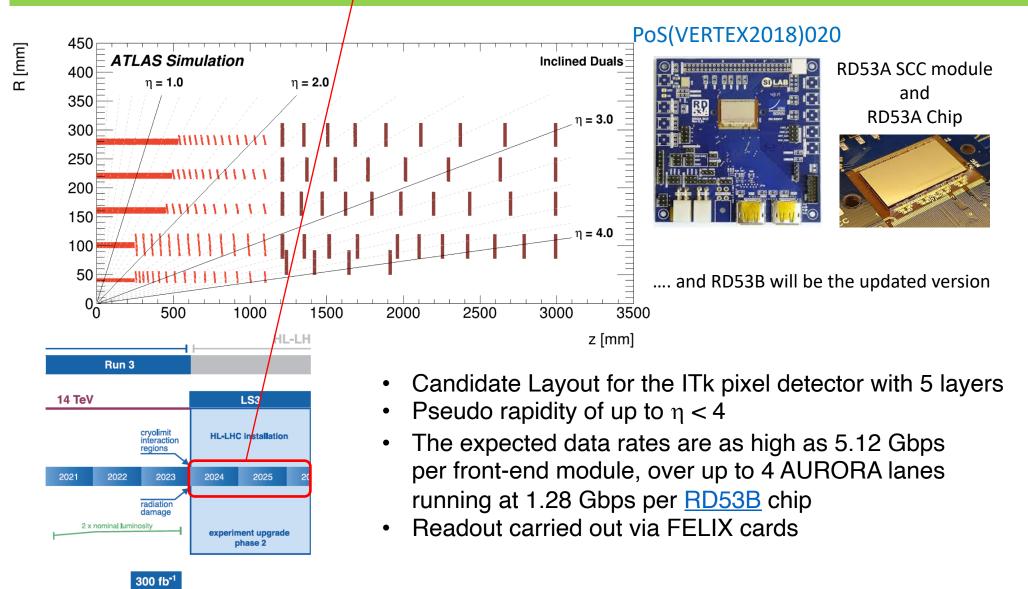

Phase-II ITK detector will consist of 9416 modules, 12.98m<sup>2</sup>, **5 billion channels**

IBL Pixel B-Layer

**Pixel Laver-1**

Pixel Layer-

**Pixel Disk**

id maanet

Forward SCT

Muon chambers

Transition radiation tracke

**Barrel SCT**

**Pixel Detectors**

25m

dronic end-cap and

Pixel Disk

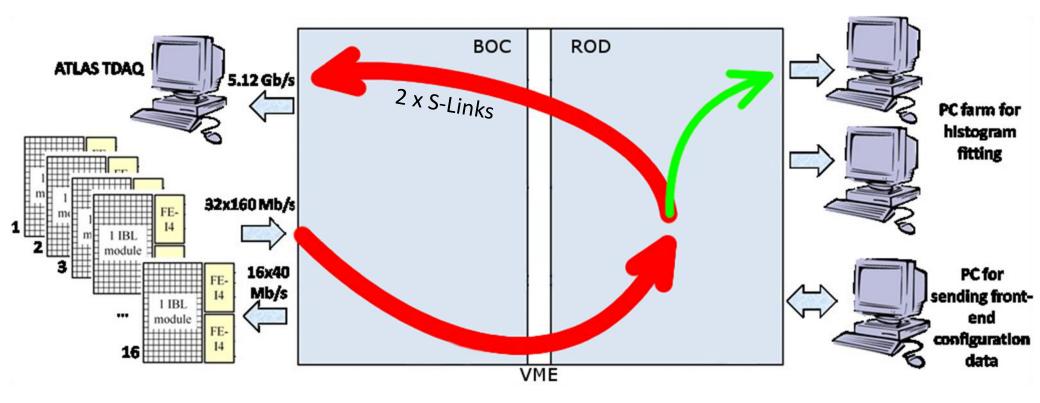

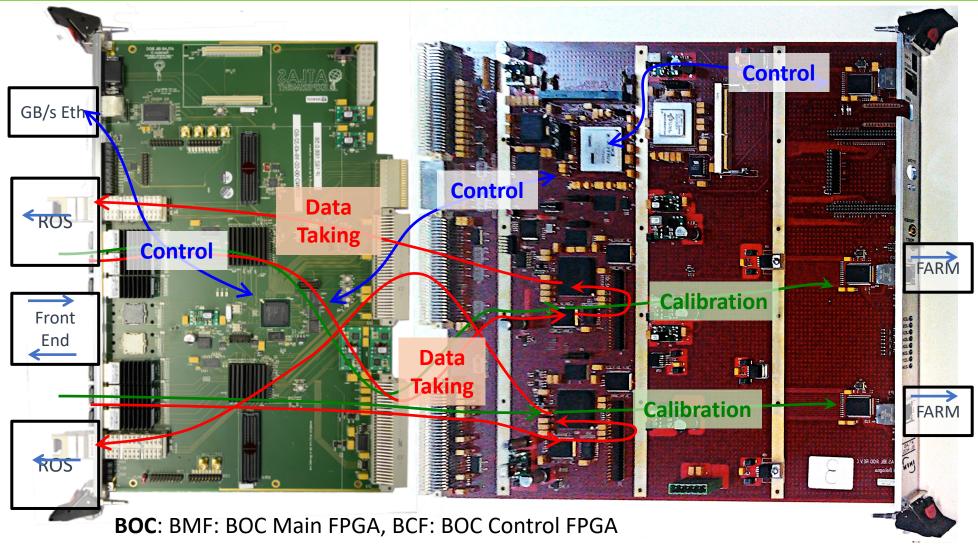

# ATLAS Current Pixel Detector Readout IBL/B-Layer/L1/L2/Disks - BOC ROD features

BOCBack Of CrateRODReadOut DriverIBLInsertable B-Layer read out with 32 FEI4 chips (readout chips)<br/>FEI4 data rate up to 160 Mbps → (32 x 160 = 5.12 Gbps)

HSTD12 2019

# ATLAS Current Pixel Detector Readout IBL/B-Layer/L1/L2/Disks - BOC ROD features

**ROD:** PRM: Program Reset Manager, Master and 2 x Slaves

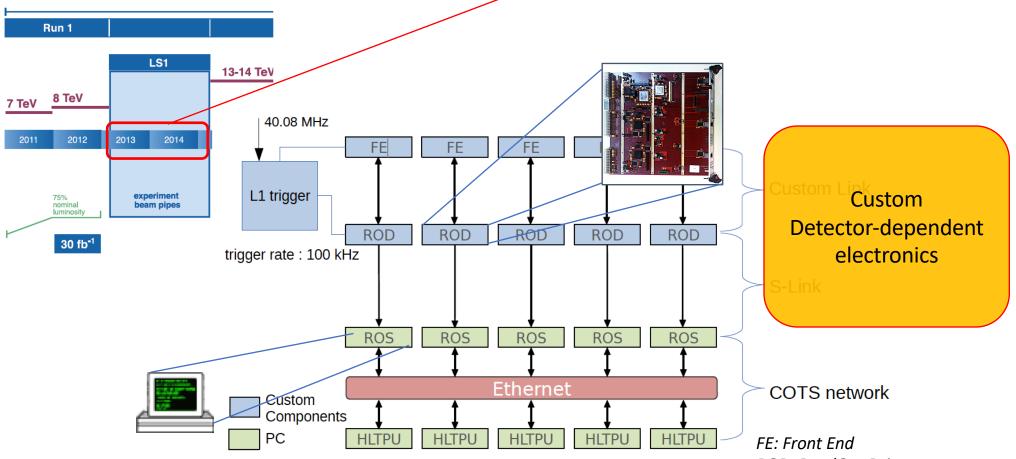

# Pixel DAQ today after Phase-0 upgrade (2017)

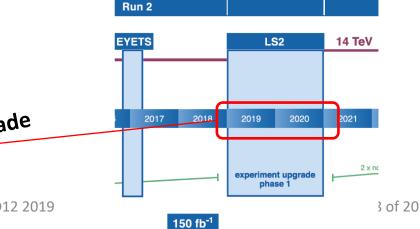

#### Points to be revised for the Upgrade of Phase-II

- Too much custom electronics

- Too rigid configuration (Detector Dependent)

- ROD card based on Firmware and Embedded Software

FE: Front End ROD: ReadOut Driver ROS: ReadOut System HLTPU: High Level Trigger Processing Unit COTS:Commercial Off the Shelf

HSTD12 2019

## **Phase-II** Pixel DAQ upgrade

Dec 2019

## The The FrontEnd Link eXchange (FELIX) readout system

https://atlas-project-felix.web.cern.ch/atlas-project-felix/

**FELIX**  $\rightarrow$  off-detector readout system common to all the sub-detectors

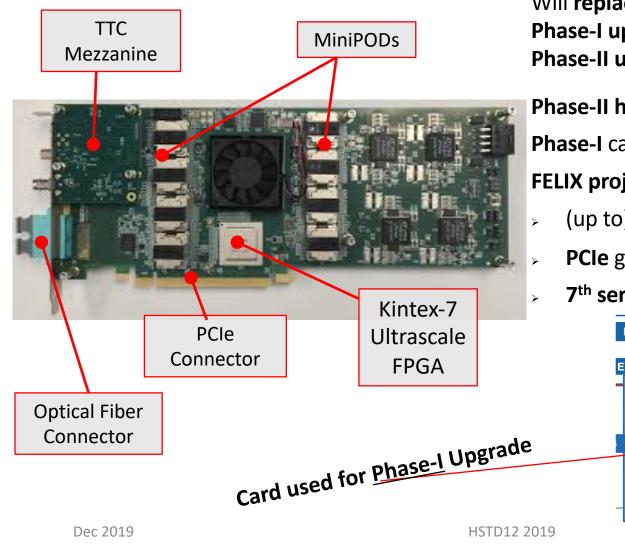

Will **replace the ATLAS RODs** during 2019-2021 **Phase-I upgrade** (partially) and during 2024-2026 **Phase-II upgrade** (completely)

Phase-II hardware design still under investigation

Phase-I cards under production

FELIX project involving several institutes

- (up to) 48 links (optical fibers)

- PCIe gen 3 technology  $\rightarrow$  >100 Gbps

- 7<sup>th</sup> series Kintex Ultrascale Xilinx FPGA

## The FrontEnd Link eXchange (FELIX) topology Phase-II Configuration

- Custom electronics greatly reduced

- ✓ Previous HW tasks replaced by SW tasks

✓ FELIX **DETECTOR-INDEPENDENT**

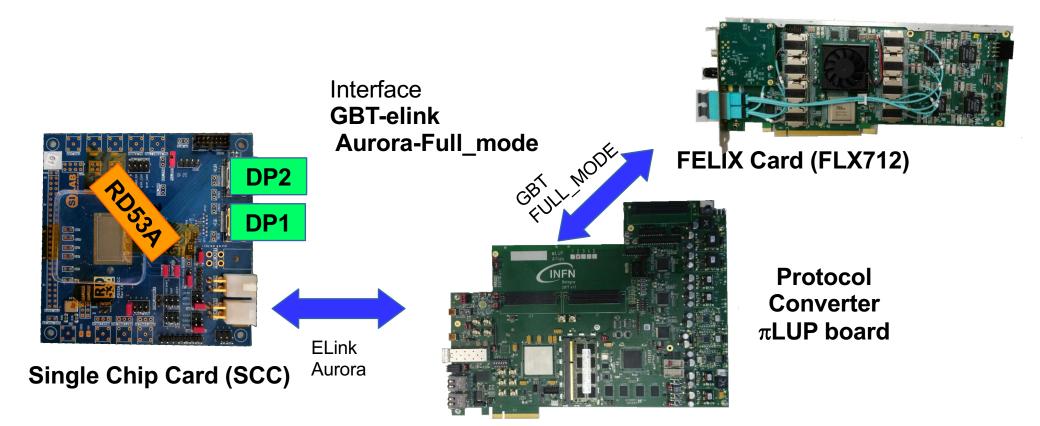

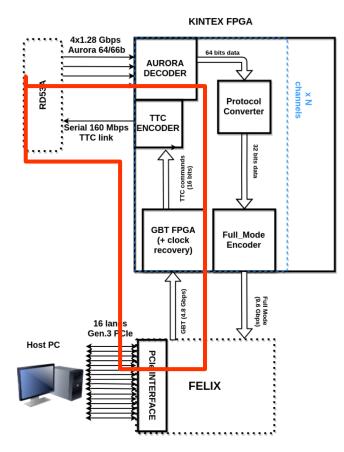

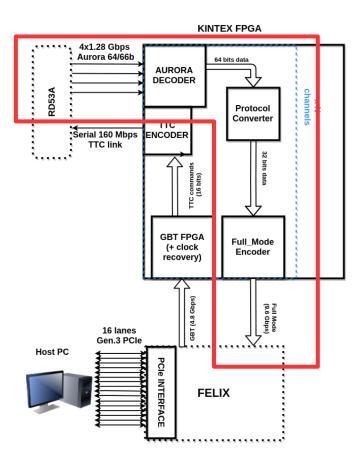

## **RD53A readout demonstrator (Pixel readout chip)**

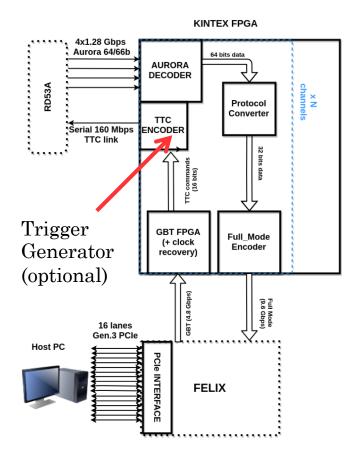

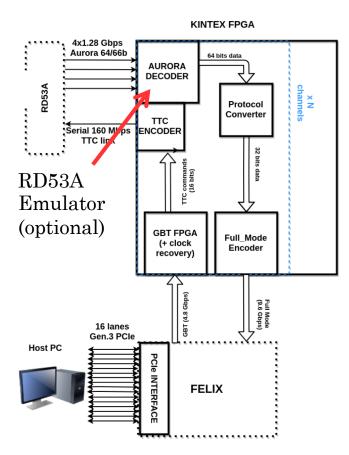

**Problem:** current FELIX firmware not compatible with RD53A/B output data **Solution**: use a **Protocol Converter** as a firmware and physical layer interface

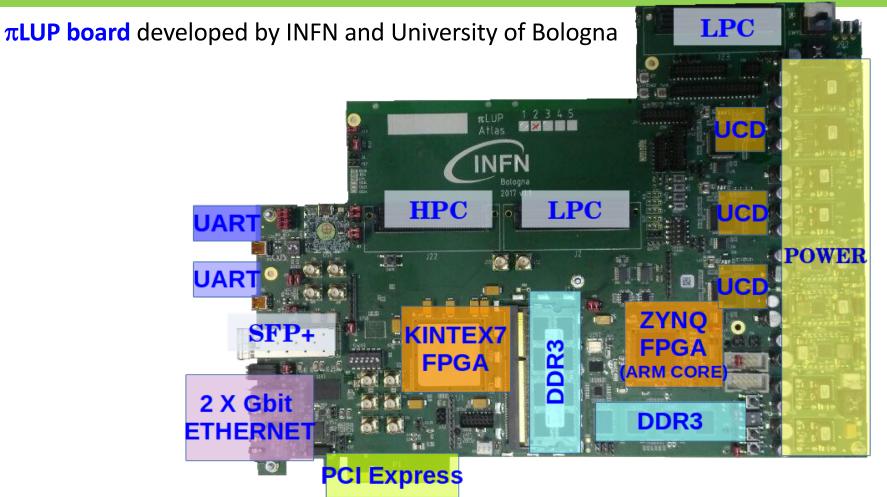

## $\pi$ LUP board

- Two 7<sup>th</sup> series Xilinx FPGAs in Master-Slave architecture

- Embedded ARM dual core processor

- ✓ PCIe bus  $\rightarrow$  32 Gbps

#### Main blocks:

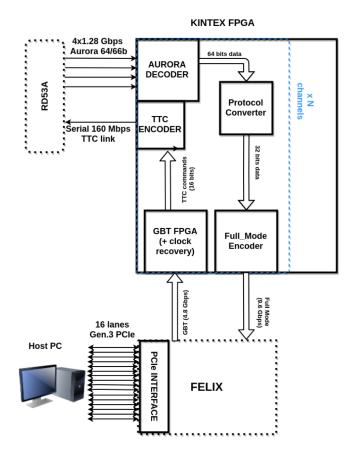

- ✓ **Configuration** (FELIX  $\rightarrow$  RD53A), decodes command from FELIX GBT and encodes them into RD53A compatible format

- ✓ Data taking (RD53A → FELIX) implemented, decodes Aurora 64/66b from SCC, merges 4 links into a single stream that is encoded into Full\_mode protocol

- Trigger generator (if no TTC available)

- **RD53A emulator** (optional) implemented into protocol converter

Can interface up

to 4 SCC chips

#### Main blocks:

- ✓ Configuration (FELIX  $\rightarrow$  RD53A), decodes command from FELIX GBT and encodes them into RD53A compatible format

- ✓ Data taking (RD53A → FELIX) implemented, decodes Aurora 64/66b from SCC, merges 4 links into a single stream that is encoded into Full\_mode protocol

- Trigger generator (if no TTC available)

- **RD53A emulator** (optional) implemented into protocol converter

Can interface up

to 4 SCC chips

#### Main blocks:

√

- ✓ Configuration (FELIX  $\rightarrow$  RD53A), decodes command from FELIX GBT and encodes them into RD53A compatible format

- Data taking (RD53A → FELIX) implemented, decodes Aurora 64/66b from SCC, merges 4 links into a single stream that is encoded into Full\_mode protocol

- Trigger generator (if no TTC available)

- **RD53A emulator** (optional) implemented into protocol converter

Can interface up

to 4 SCC chips

# πLUP: system interfaceFELIX: main DAQ boardMain blocks:

- ✓ **Configuration** (FELIX  $\rightarrow$  RD53A), decodes command from FELIX GBT and encodes them into RD53A compatible format

- ✓ Data taking (RD53A → FELIX) implemented, decodes Aurora 64/66b from SCC, merges 4 links into a single stream that is encoded into Full\_mode protocol

- Trigger generator (if no TTC available)

- RD53A emulator (optional) implemented into protocol converter

# πLUP: system interfaceFELIX: main DAQ boardMain blocks:

- ✓ **Configuration** (FELIX  $\rightarrow$  RD53A), decodes command from FELIX GBT and encodes them into RD53A compatible format

- ✓ Data taking (RD53A → FELIX) implemented, decodes Aurora 64/66b from SCC, merges 4 links into a single stream that is encoded into Full\_mode protocol

- Trigger generator (if no TTC available)

- **RD53A emulator** (optional) implemented into protocol converter

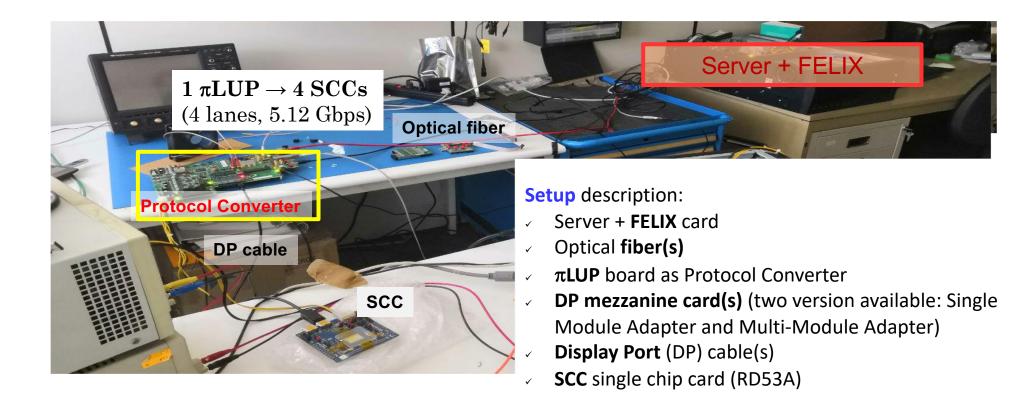

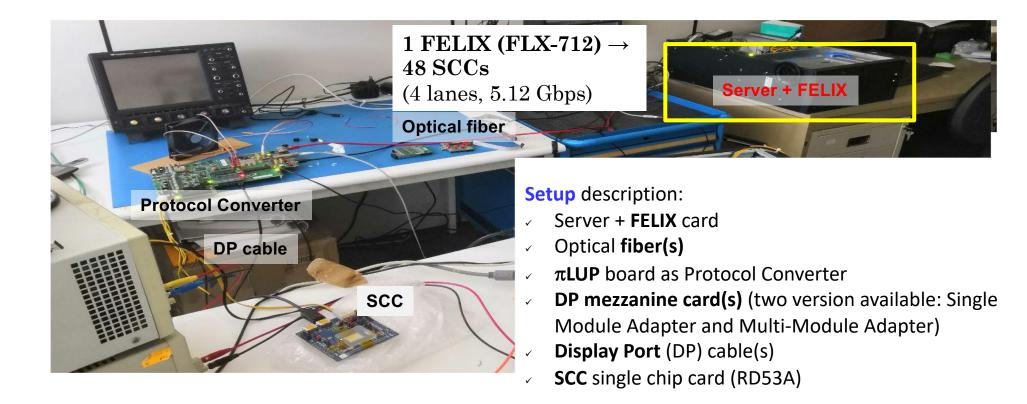

## Setup Overview System Integrated with FLX712 and RD53A

## Setup Overview System Integrated with FLX712 and RD53A

### **Setup at CERN**

#### **Example of an ANALOG SCAN**

#### **RD53A** – $\pi$ LUP – FELIX readout chain

- Up to 4 SCC chips interfaced with one  $\pi$ LUP

- Each SCC read out up to **4 x 1.28 = 5.12 Gbps**

- Readout software integrated with ITk Phase-II software

- Chip calibrations (Digital, Analog Scans)

Poster by Kazuki Todome «Data-acquisition system developments for ATLAS pixel QA/QC test toward High Luminosity LHC»

#### Current demonstrator is a **baseline** for the **Phase-II implementation**

## Conclusions

- ATLAS Pixel Detector fundamental to resolve particle tracks

- Pixel Detector upgraded to have more spatial resolution and channel density

- Readout system to be upgraded to face harsher environmental conditions

- **First prototype** (Front-End and readout chain) realized

- "Integrated" for FELIX cards and RD53A prototypes (Demo at CERN)

- Real FE chip (RD53B) and Phase-II readout system development still ongoing, updated version of FELIX cards will be used