# A novel SOI-PDD design for the CEPC vertex detector

Zhigang Wu<sup>a,b</sup>, Yunpeng Lu<sup>a</sup>, Yang Zhou<sup>a</sup>, Jing Dong<sup>a</sup>, Longlong Song<sup>a,b</sup>, Qun Ouyang<sup>a,b</sup>

a. State Key Laboratory of Particle Detection and Electronics (Institute of High Energy Physics, CAS), Beijing 100049, China b. University of Chinese Academy of Sciences, Beijing 100049, China

#### Introduction

Silicon pixel detectors are at the core of the detector system at the Circular Electron Positron Collider (CEPC). As the innermost part, it provides a extremely high impact parameter resolution. The vertex system is crucial for the Higgs flavor physics, such as H->bb, cc, gg.

It consists of three cylindrical layers of double-sided silicon sensors and mechanical support. The spatial resolution of innermost layer should be less than 3 μm, which is very difficult to achieve when the power consumption and readout speed is also important.

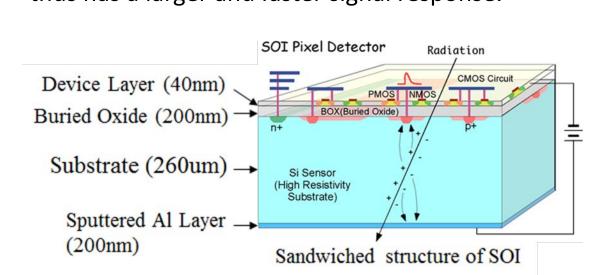

Currently, there are several R&D activities for CEPC vertex detectors. One is the CMOS, based on TowerJazz CIS 0.18 μm process, the other is the SOI, based on LAPIS 0.2 μm FD-SOI process [1]. Comparing with the standard CMOS technology, the SOI takes advantage of fully depleted sensors, thus has a larger and faster signal response.

Based on SOI technology, we developed Compact Pixel for Vertex 3 (CPV3). The design goal is to study new PDD sensor structure, explore low noise in-pixel circuit and realize a spatial resolution below 3 μm.

#### CPV3:

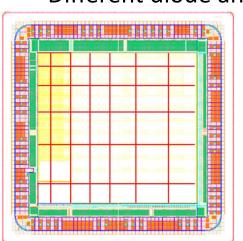

- Chip area: 6\*6 mm<sup>2</sup>, sensitive area: 4\*4 mm<sup>2</sup>

- Pixel area: 16\*20 μm² to gain a high resolution

- Pixel array: 240\*200, include analog and digital

- In-pixel discriminator and 3T analog readout

- Different diode and circuit design

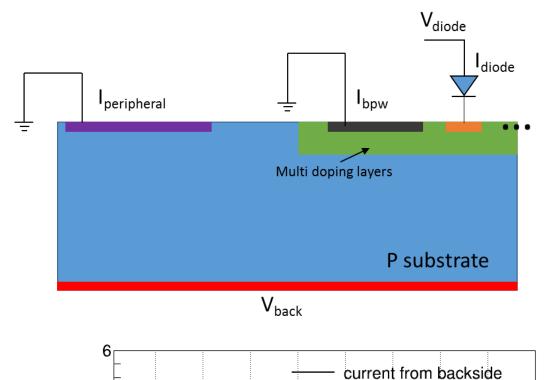

#### Sensor: Pinned Depleted Diode (PDD)

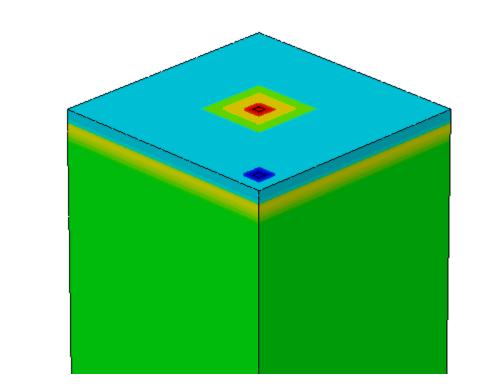

SOI-PDD structure is proposed by Shoji Kawahito [2] (Shizuoka U.). It has many advantages due to the multi doping layers:

- Pinned Si surface layer -> shielding layers to eliminate back-gate effect and cross-talk, reduction of surface leakage by 2 orders, reduction of signal loss due to Si-SiO<sub>2</sub> Interface traps

- Depleted charge collection electrode -> reduction of diode capacitance

- Lateral electric field -> improved charge collection efficiency

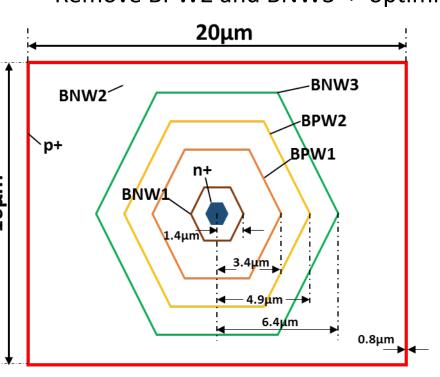

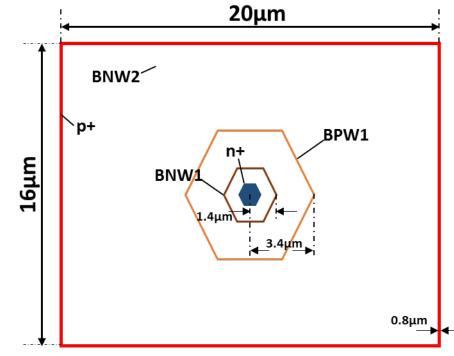

Several complex ring structures placed in area of 16\*20 μm<sup>2</sup>:

- Standard PDD structure

- Modify distance between BNW1 and BPW1 from 1 μm to 2 μm -> optimization of diode capacitance

- Remove BPW2 and BNW3 -> optimization of charge sharing effect

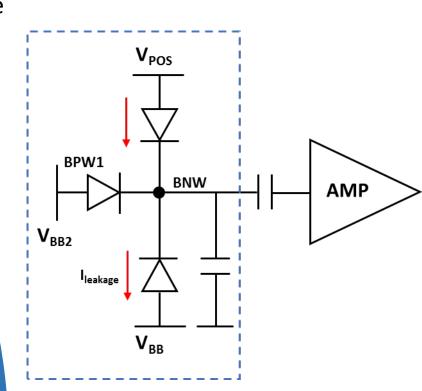

### Diode capacitance and bias

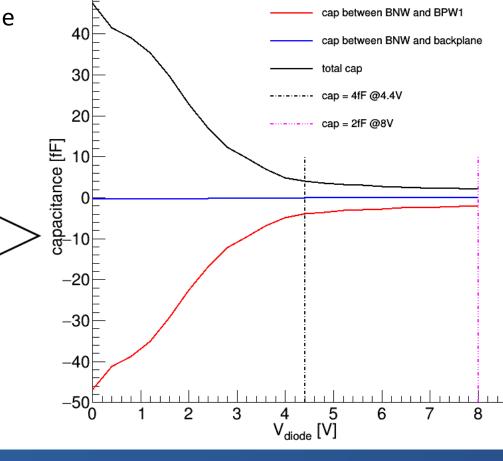

- Key issue of this PDD structure: relative large diode capacitance dominated by cap between BNW1 and BPW1

- At least +4V between BNW1 and BPW1 to gain a cap less than 4 fF Tradition solution: apply negative V<sub>BB2</sub> at BPW1, this voltage cannot

- exceed -2V otherwise the circuit above it won't work Our solution: apply positive V<sub>POS</sub> at BNW1 and the diode is ac-coupling

- with in-pixel circuit

- Advantages: larger V<sub>bias</sub> -> smaller C<sub>d</sub>, C<sub>d</sub> decreases from 4 fF to 2 fF if V<sub>bias</sub> increases from +4V to +8V, MIM capacitor to allow Vbias up to +10V

2% loss of signal over 100 μs integration time Leakage current around 100 fA/pixel thanks to the PDD structure

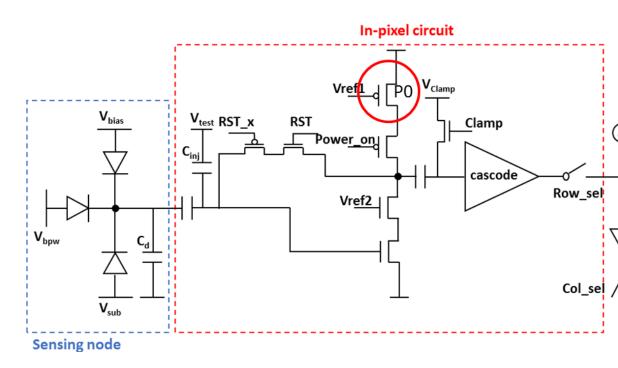

#### In-pixel circuit

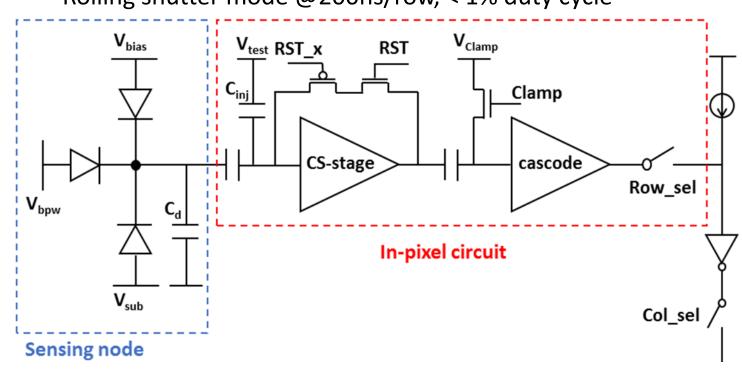

Even though SOI sensor has a 3 times larger signal than standard CMOS sensor, we still need a low noise in-pixel circuit to obtain a low threshold and better resolution performance. The baseline in-pixel circuit consists of:

- Common source amplifier as 1<sup>st</sup> stage

- DC gain ~13, 1 μA consumed only when the row is read out (static power consumption)

- Forced to initial state after readout by a pair of complementary reset transistors C<sub>ini</sub> = 0.27 fF for electrical pulse test

- Correlated Double Sampling (CDS) to reduce KTC noise

- Cascode amplifier as 2<sup>nd</sup> stage with its active load shared on the column line

- 4 μA consumed only when pixel is fired and read out(dynamic power consumption)

- Intrinsic threshold 525mV, adjustable by V<sub>clamp</sub>

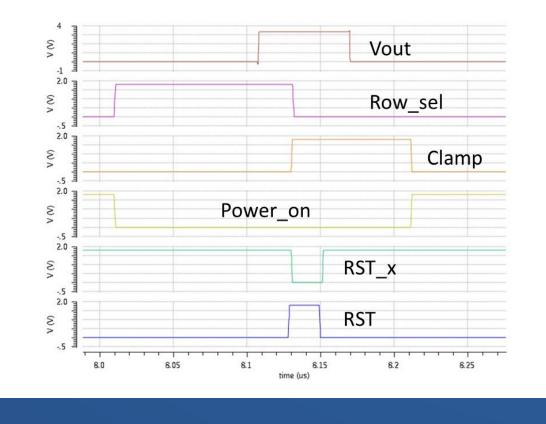

- Rolling shutter mode @200ns/row, < 1% duty cycle

Temporal Noise (TN)

PS

BNW2

BPW2

• Shot noise is negligible due to low leakage current

p-- substrate

- Thermal noise is the dominant component

- 6 e<sup>-</sup> achieved on CPV2 design [3]

- Fixed Pattern Noise (FPN)

BNW1

BNW3

- Excessive FPN has been an issue in CPV2 design • W/L =  $0.63/0.2 \mu m$  for the input Tr. of 1<sup>st</sup> stage

- W/L =  $2.4/0.2 \mu m$  for the input Tr. of  $2^{nd}$  stage

- Process variation added to the HSPICE model and qualified with CPV2 results

- Statistical simulation, FPN = 12 e<sup>-1</sup>

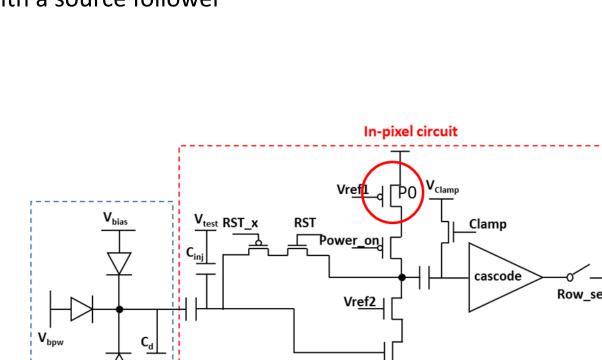

- Large dynamic range to characterize the PDD sensor CS-stage of the amplifier replaced by a

- cascode stage

- To mitigate the miller effect and to improve the CVF

- Carefully tuned to have a DC gain < 30 (for

- a proper dynamic range) • Optimized the size of P0 Transistor (as the

- active load) Discriminator replaced with a source follower

for analog output

Col\_sel

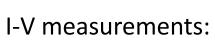

### Preliminary test results

current from peripheral

current from bpw

current from diode

-80 -70 -60 -50 -40 -30 -20 -10 0 V<sub>back</sub> [V]

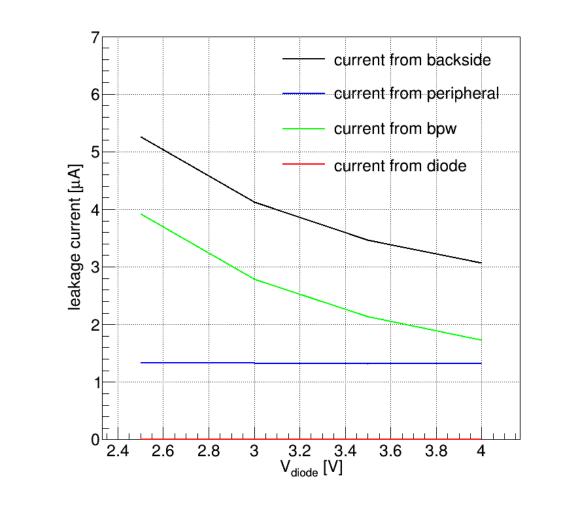

- Apply  $V_{diode} = 2.5V$ ,  $V_{bpw} = V_{peripheral} = 0V$

- $I_{diode} \approx 0$ , very small, due to the PDD structure

- Leakage current coming from peripheral dominates @low voltage (<70V)

- Leakage current coming from bpw dominates @high voltage (>70V)

- Leakage current coming from bpw can be suppressed

- by improving V<sub>diode</sub>

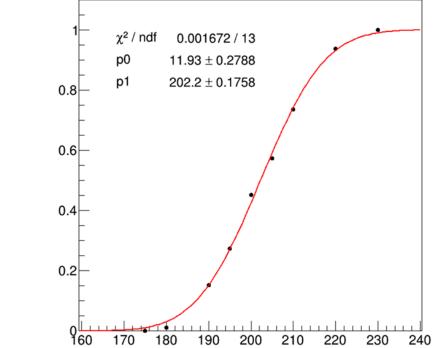

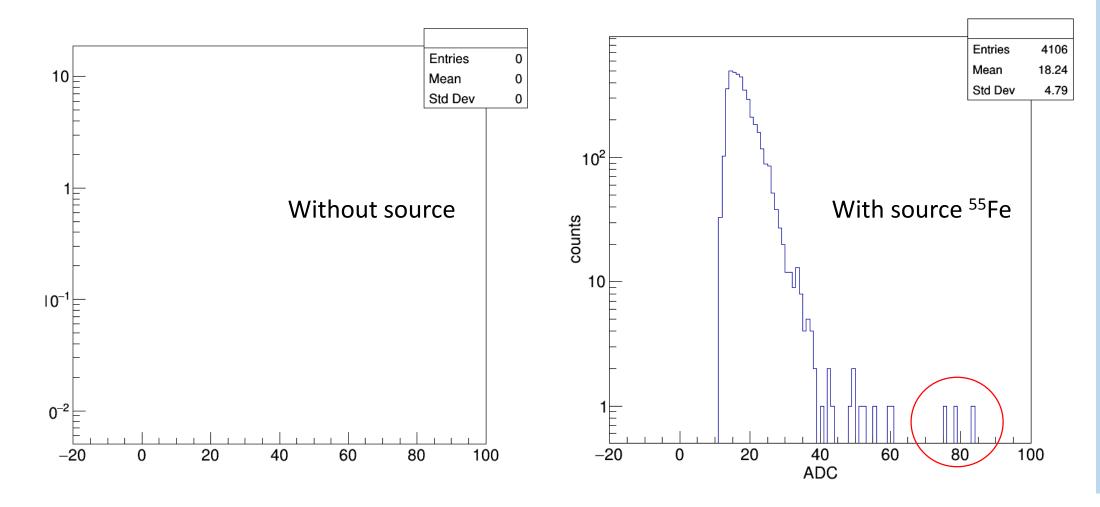

#### <sup>55</sup>Fe source measurements:

- 5.9KeV X-ray measured by 3T circuit

- Data collection for 1 hour with and without source

- |signal residual| > 10σ as cut condition No signals for experiment w/o source

- Clear signal for experiment with source

- Very low counting rate due to the low-level source, not fully depleted sensor and backside illumination

- This will be solved by applying a high-level <sup>55</sup>Fe source • C<sub>diode</sub> = 5fF if 5.9KeV energy => 80 ADC, expected from simulation

## Acknowledgements

This work is supported by the National Nature Science Foundation of China, Grant 11575220 and the CAS Center for Excellence in Particle Physics (CCEPP).

#### References

[1] Y. Arai et al., Development of SOI pixel process technology, in: 7th International Hiroshima Symposium on the Development and Application of Semiconductor Tracking Detectors, Nucl. Instrum. Methods Phys. Res. A 636 (1, Supplement) (2011) S31-S36.

[2] Kamehama H, Kawahito S, Shrestha S, et al. A low-noise Xray astronomical silicon-on-insulator pixel detector using a pinned depleted diode structure[J]. Sensors, 2018, 18(1): 27.

[3] Wu Z, Lu Y, Zhou Y, et al. A prototype SOI pixel sensor for CEPC vertex[J]. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 2019, 924: 409-416.