# RD53A WAFER PROBING SPECIAL PLOTS

M. Daas, Y. Dieter, T. Hemperek, F. Hinterkeuser, F. Hügging, H. Krüger, D-L. Pohl, M. Standke, M. Vogt

Silab, Physikalisches Institut, University of Bonn

15.04.19 ITk Week - CERN

#### **OVERVIEW**

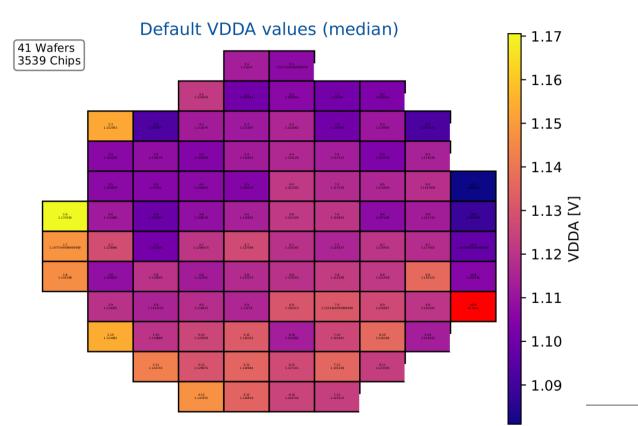

- Coming back to Aleksandra's observation from April 1<sup>st</sup>

- VDDA slightly lower on the right-hand side of wafer?

- Waferprobing data:

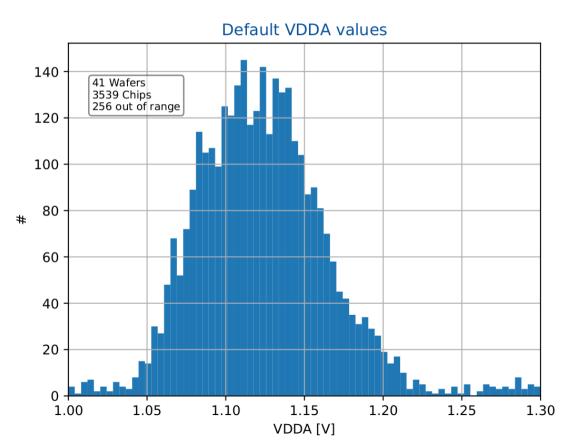

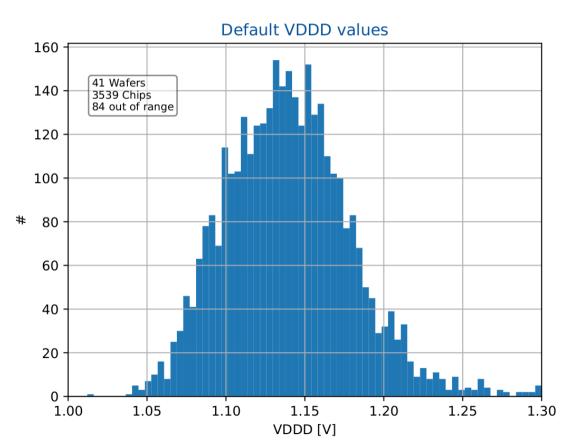

- Probed 41 wafers by now

- 3500 chips for statistical analysis

- So far only looked at trimmed VDDs (VDD @ optimal trim bit)

- Now: Compare VDD at **default** trim bit (16)

# **VDDA**

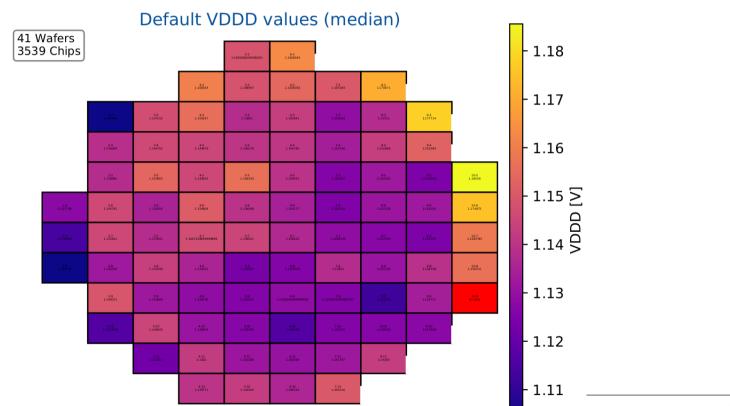

# **VDDD**

#### VDDA

#### VDDD

#### **OBSERVATIONS**

- Positional dependence of VDDA and VDDD on the chip position on the wafer

- Overall gradient ~ 80mV

- Sign of gradient is opposite for analog and digital

- Possible explanation:

- Master cells of analog and digital regulators are mirrored

- Process variations might have opposite effect

#### Conclusion

- There is an effect observed

- No reason to worry

- Absolute values of both VDD too low without trimming

- Mitigate by higher default trim value from software?

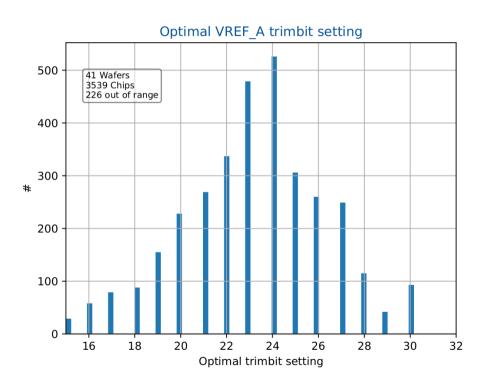

# VREF A TRIM

- Look again at optimal (VDD closest to 1.2V) trimbit setting

- Use VREF\_A\_TRIM = 24 as new default setting in software?

- Does not replace proper calibration but make initial communication easier

- Only concerns unprobed chips

- Will get optimal value from database

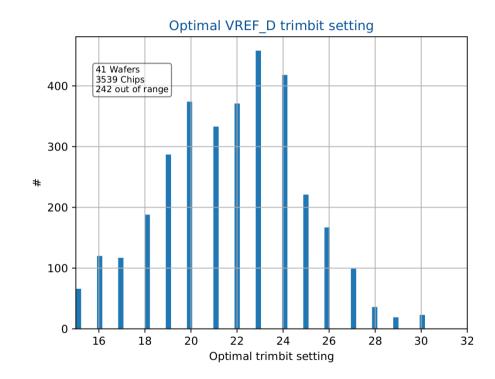

# VREF\_D\_TRIM

- Use VREF\_D\_TRIM = 23 as new default setting in software?

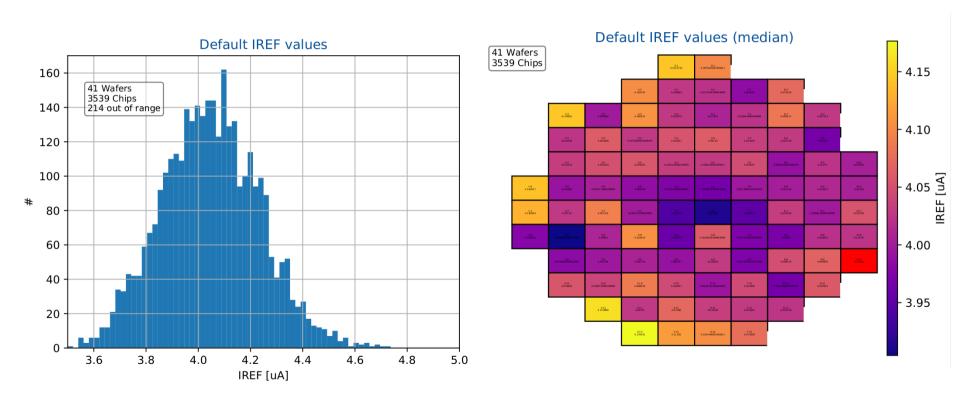

## **IREF**

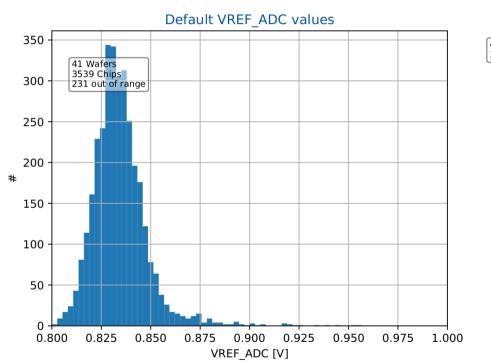

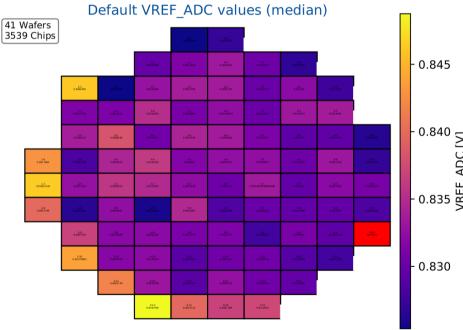

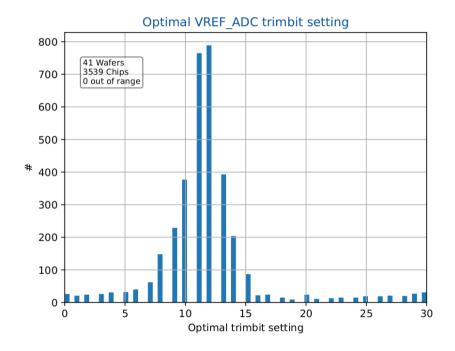

# VREF\_ADC

- Default trimbit setting is 0

- Use MON\_BG\_TRIM = 12 as new default setting in software?

# Backup

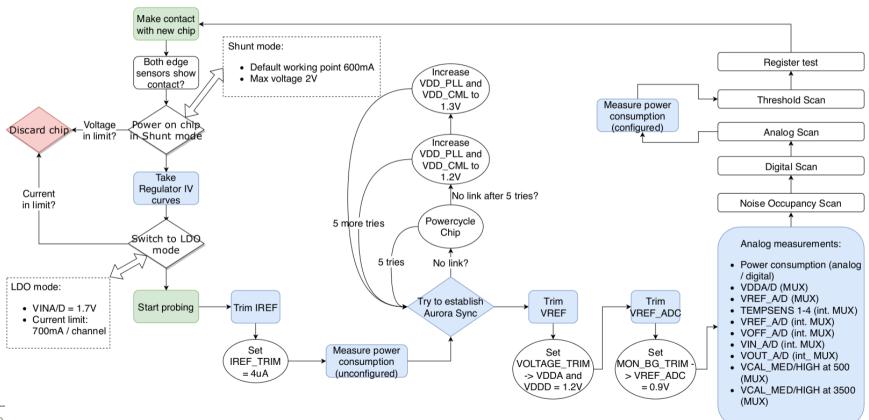

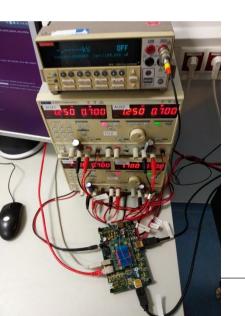

#### **SETUP**

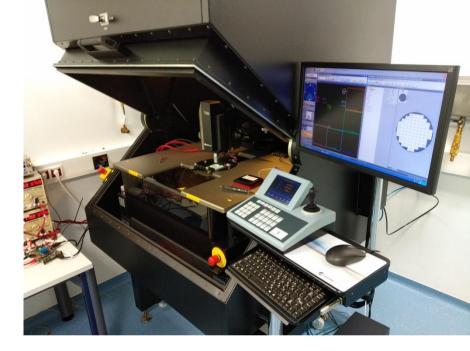

- Cascade Microtech (formerly Karl Suss)

PA-300-II semi-automatic 300mm probe station

- Generic LV power supplies (TTi QL355TP)

- Keithley SMU for analog measurements

- Probe card connected to BDAQ53 readout system

- Connection to BDAQ53 on one lane at 640 Mbit/s

- BDAQ53 software

- Communication with hardware based on basil

- Possible to implement / add different devices (Power supplies, SMUs, probe stations)

as long as it has some kind of documented interface

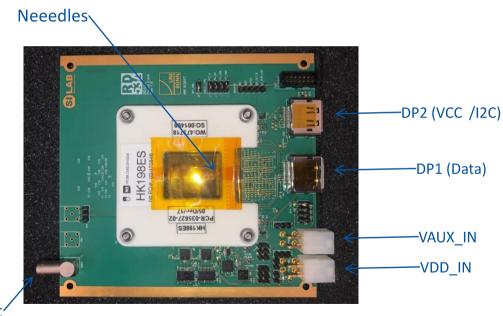

#### PROBE CARD

- Probe card modifications fixed

- Standard SCC mods: PLL\_RESET POR

- Two additional transistors to switch between Shunt- and LDO modes

- 11 cards produced, about ready to be distributed

- 3 for CERN, one already received

- 2 for Glasgow

- 2 for Torino

- 1 for LBNL

- All cards tested, some issues found

- Broken cards fixed by manufacturer

- To be tested again

Analog MUX output

### **TEST PROCEDURE**