# Status of LGAD development at BNL (and other silicon R&D activities)

G. Giacomini, W. Chen, G. D'Amen, D. Lynn, E. Rossi, A. Tricoli

# Outline

- Low Gain Avalanche Diode (LGAD) R&D

→ High Energy Physics and Photon Science

- fabrication

- measurements

- HV silicon JFET

- $\rightarrow$  for multiplexing in ATLAS ITk

- concept

- Measurements after irradiation (TRIGA, JSI, Ljubljana, Slovenia)

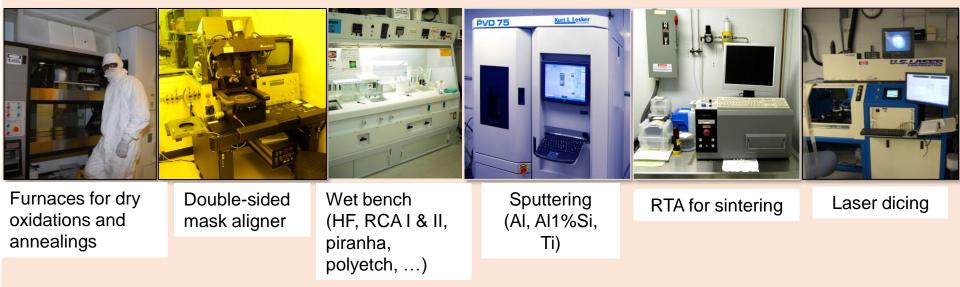

#### All silicon process done in BNL Instrumentation Division Class-100 Clean Room

+ dry etching and thin-film deposition, but we need to outsource:

- Ion implantation

- Polysilicon deposition

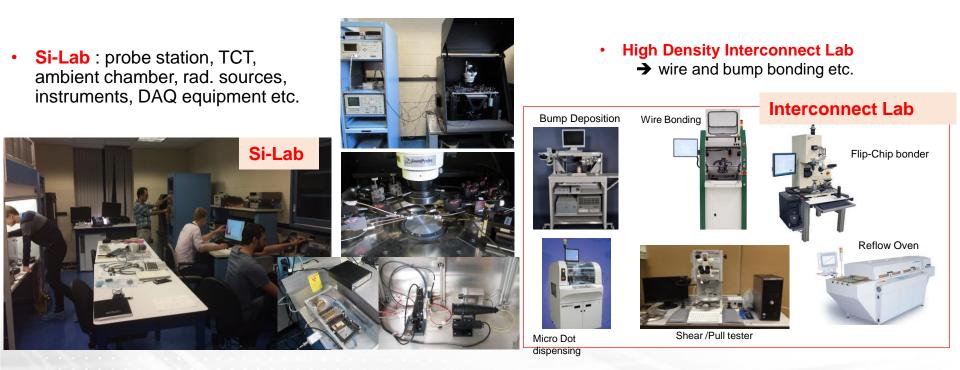

# Si-Fab, Si-Lab, and Interconnect Lab.

#### BNL resources used for Silicon R&D

- Silicon Fabrication Facility in BNL Instrumentation Div (Si-Fab)

- Capabilities for wire and bump bonding in BNL Instr. Div. (High Density Interconnect Lab.)

- Laboratory to fully characterize, design and simulate silicon sensors and exp. apparatuses (Si-Lab)

3

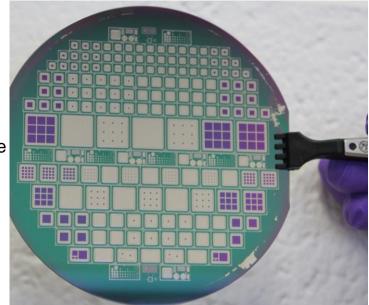

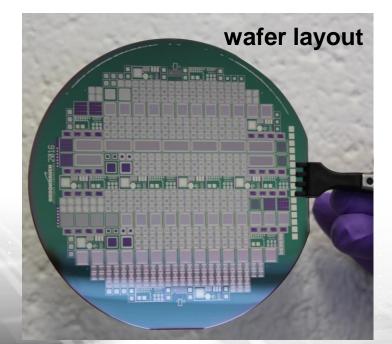

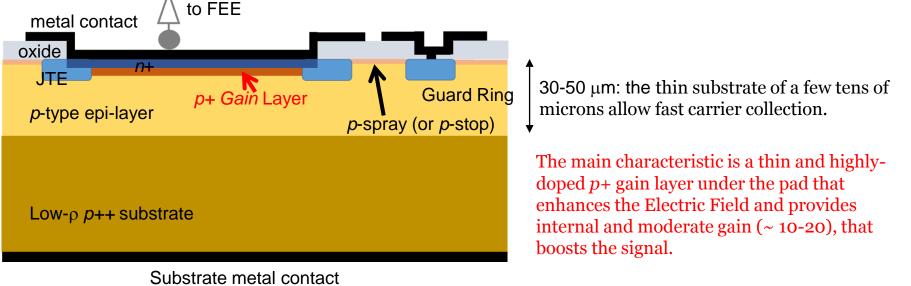

# LGAD fabrication at BNL

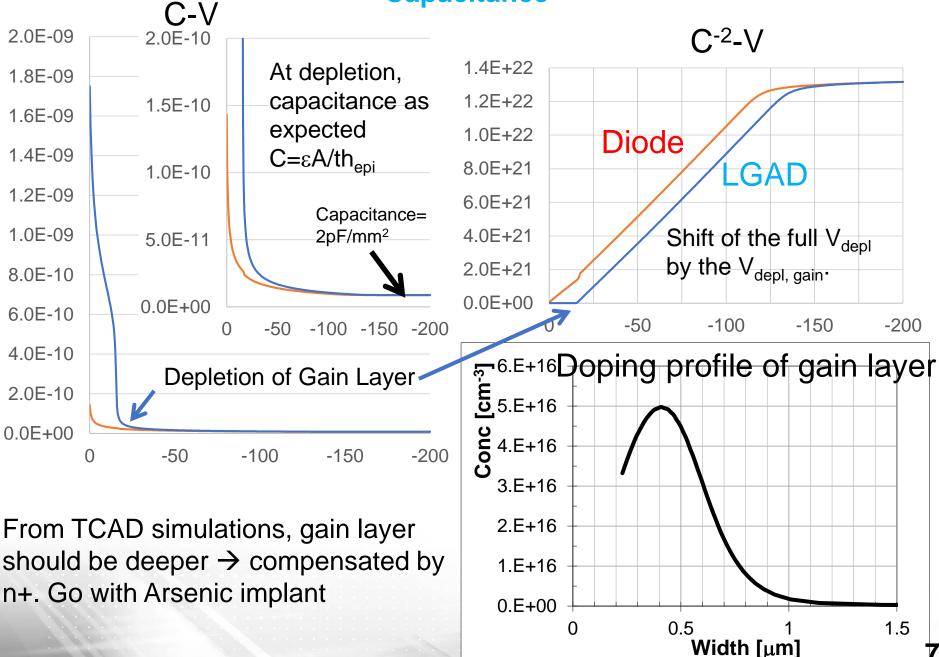

- 4" *p*-type epitaxial wafers (100), N<sub>A</sub>~<1e14cm<sup>-3</sup>, 50µm thick

(→ V<sub>depl</sub> ~120V). Also FZ used.

- 4 ion implantations (JTE and gain at high energy)

- 6 photolithographic masks

- *p*-spray isolation (patterned externally to the active area to avoid implant on gain region).

- Little thermal drive-in (mainly for the JTE Junction Termination Edge for protection from high E at the border of the shallow n<sup>+</sup> implant)

- layout with pads of 1x1 mm<sup>2</sup>, 2x2 mm<sup>2</sup>, 3x3 mm<sup>2</sup> and arrays.

G. Giacomini, et al. "Development of a technology for the fabrication of Low-Gain Avalanche Detectors at BNL", Nuclear Inst. and Methods in Physics Research, A 934 (2019) 52–57.

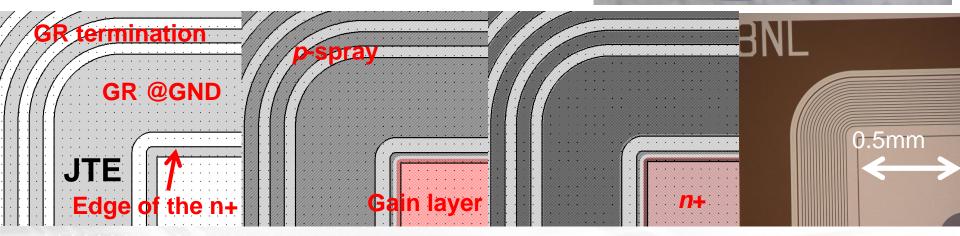

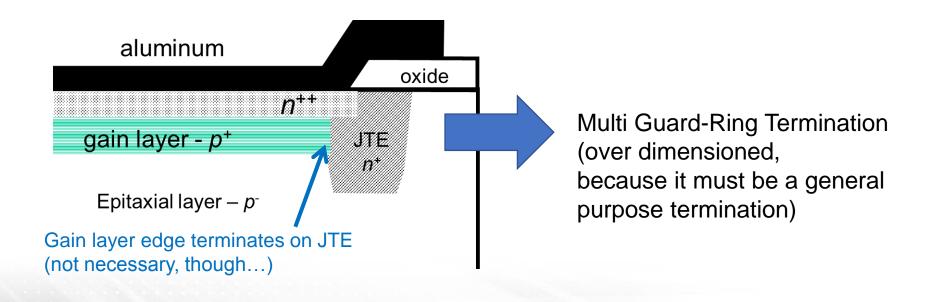

# LGAD fabrication at BNL

4 ion-implantations (Innovion, San Jose):

- JTE layer as deep as possible (~400keV)  $\rightarrow$  channeling effect on 100 substrates

- *p*-spray (2e12cm<sup>-2</sup>), external to the active area

- Gain layer as deep as possible, within the JTE

- N+ as shallow as possible

(to avoid compensation of gain layer)

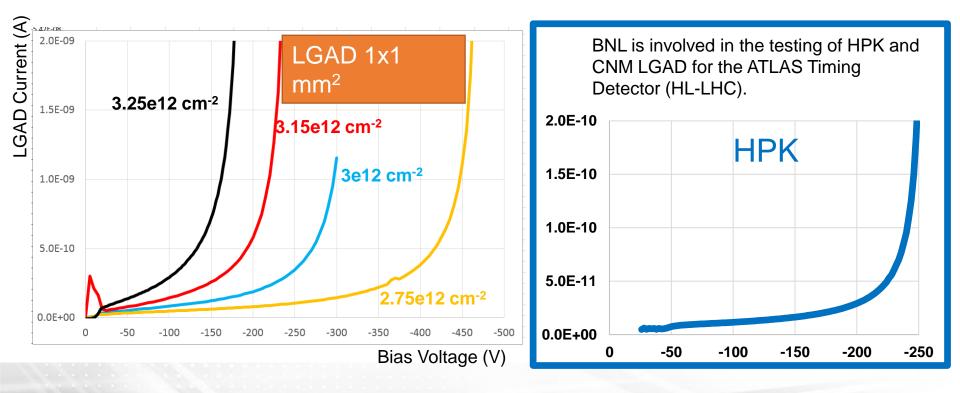

# I-V

#### BNL's LGADs :

- Leakage current as measured on diodes (gain=1) 1x1 mm<sup>2</sup> is ~ 10pA (1nA/cm<sup>2</sup>)

- · Consistent from batch to batch

- Clearly current depends on gain layer dose, so does the breakdown voltage

- GR can stand higher voltages

# **Capacitance**

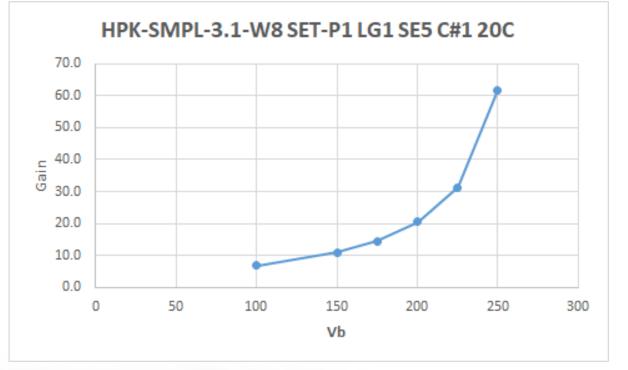

#### **Gain Measurements**

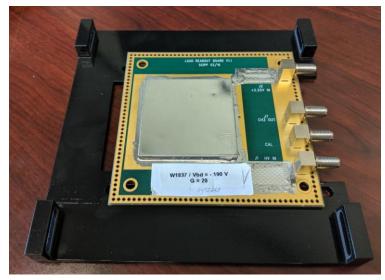

#### TA board from SCIPP 1Ghz scope (50Ohm termination) Waveform superimposition 0.08 data w1837\_10k 160 0.06 2.25 0.04 plitude [V] 0.02 сн3<sup>7</sup>0 **calibration** 0.00 -H\ -0.02 W1837 / Vbd ≈ - 190 V G ≈ 20 -0.04 time duration [seconds] 1e-9 Integral(waveform[Vs]) / R<sub>feedback</sub> $\rightarrow$ charge[C]

#### **CSA from BNL**

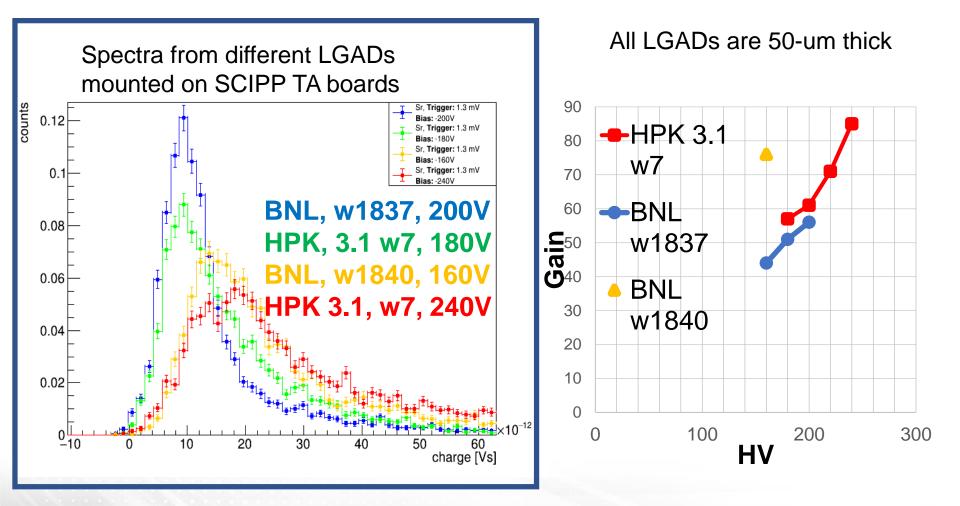

# **Gain Measurements -TA**

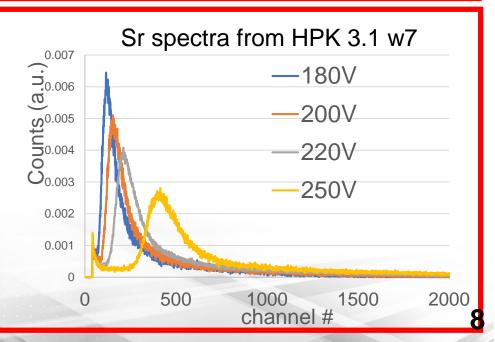

#### signals from a <sup>90</sup>Sr source, TA measurements

9

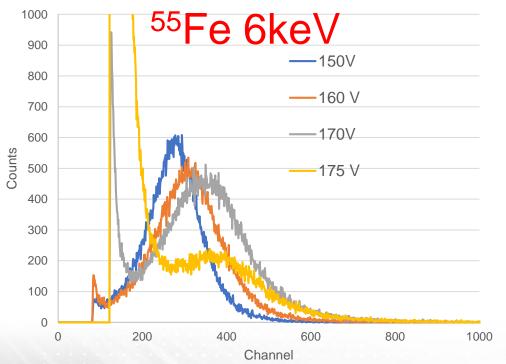

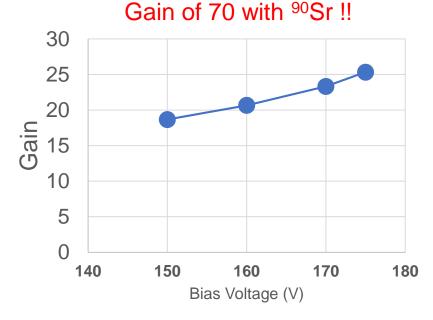

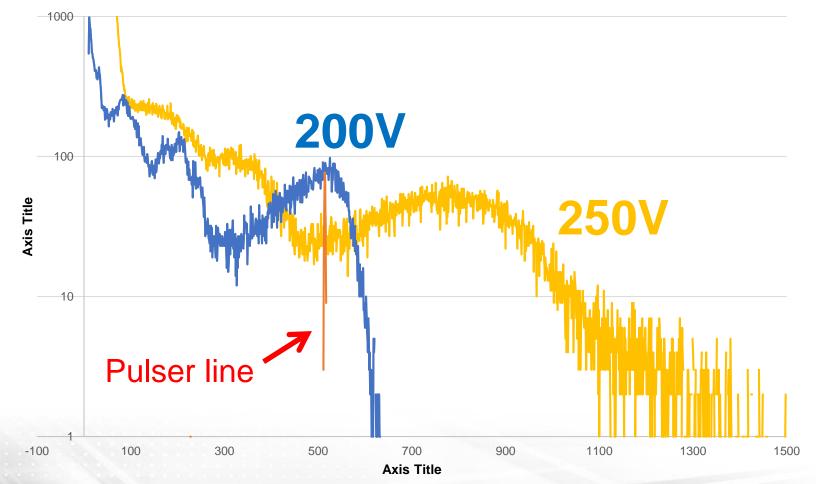

# **Gain Measurements - CSA**

### signals from X-ray sources

- <sup>251</sup> Am, <sup>55</sup>Fe + (Cu, Rb, Mo, Ag, Ba, Tb K lines generated by 60keV X-rays against targets)

- Signal from  $^{55}\text{Fe}$  ~  $^{1\!\!/_2}$  m.i.p. in 50µm of Silicon.

Broad peaks are due to multiplication noise. Pulser peaks are very narrow in this scale

- Gain much less than Gain measured with <sup>90</sup>Sr: different shape of the charge cloud

- <sup>55</sup>Fe higher than gain with <sup>251</sup>Am: shielding effects?

#### **Gain Measurements - CSA**

#### Also for HPK, gain with Sr >> gain with Gamma rays

241 Am Gamma Ray, HPK 3.1 w7

#### Next steps - 1

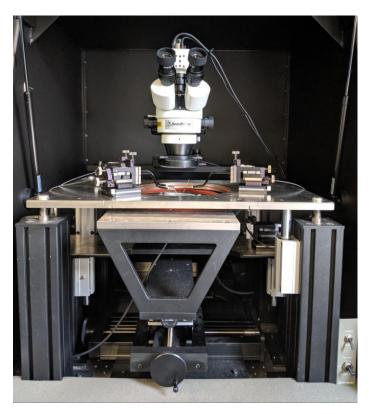

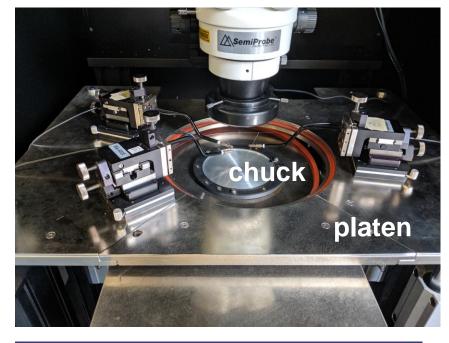

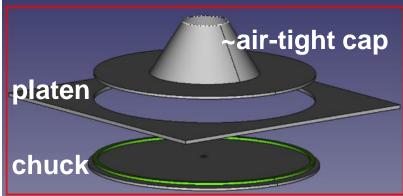

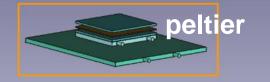

Upgrading of the probe station for "cold" I-V & C-V of irradiated devices

#### Irradiation campaigns:

- Los Alamos (800-MeV protons)

- Tandem Van der Graaff (BNL) (26-MeV protons)

- TRIGA JSI (neutrons)

- Up to 1e16 n/cm<sup>2</sup>, in steps

# Next steps - 2

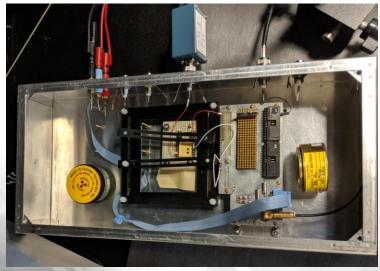

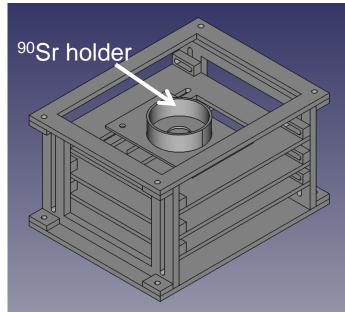

# **Telescope for timing measurements:** Beta scope as SCIPP SCIPP TA on 3D-printed support

#### Also multi-channel TA from FermiLab

#### 3D-printed telescope

#### climate chamber

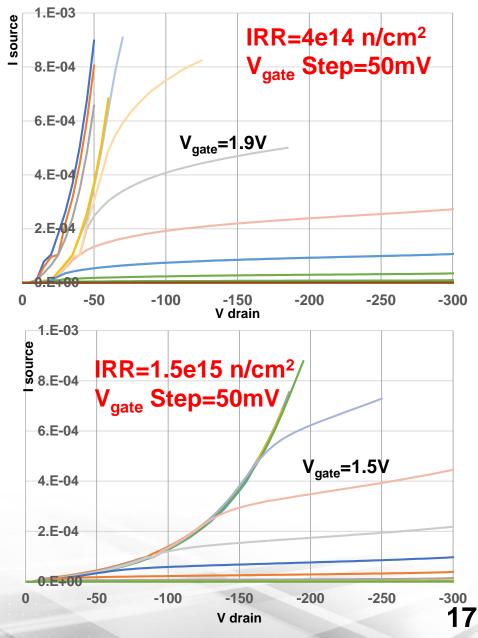

Irradiated at the TRIGA reactor at JSI with 4e14, 8e14, 1.5 e15 n<sub>eq</sub>/cm<sup>2</sup>

G. Giacomini, et al., "Fabrication and Electrical Characterization of High-Voltage Silicon JFETs", 2019 JINST 14 P05007.

G. Giacomini, et al., "High-Voltage Silicon JFET for HV Multiplexing for the ATLAS MicroStrip Staves" POS(TWEPP2018)030.

G. Giacomini, et al., "A HV Silicon vertical JFET: TCAD simulations," Nucl. Instrum. Methods A, vol. 919, 2019, pp. 119-124.

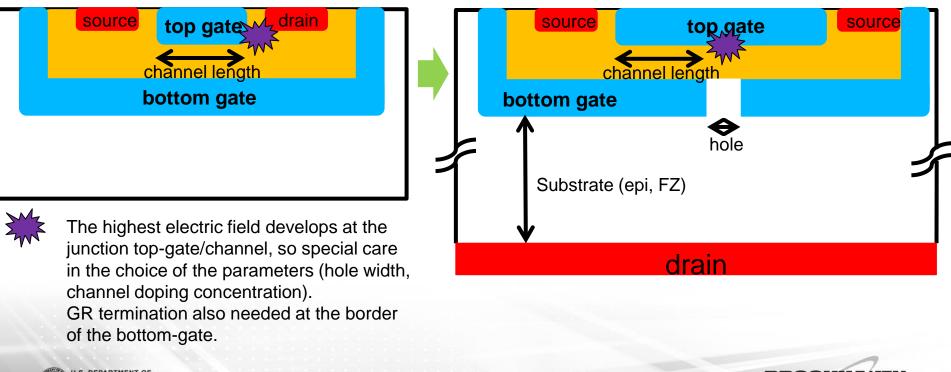

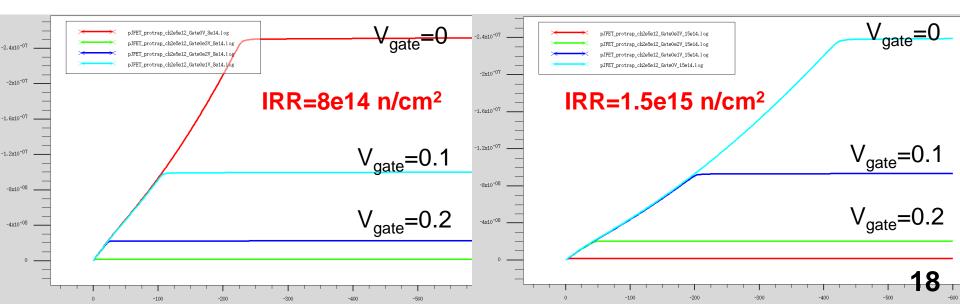

#### **The vertical HV Silicon JFET**

#### Originally, conceived as a rad-hard switch to be used in the ATLAS ITk HV-Mux. GaN JFETs are very rad-hard, so HV-Mux will go with GaN.

We can modify the structure of the standard JFET by making a gap in the bottom-gate.

Over the gap, the top-gate. The channel and the source as in the standard JFET. The drain is the back contact. The current flows (= drifts) from source to drain through the gap in the bottom-gate.

The high voltage applied to the drain falls in the thick substrate, being the bottom-gate almost a planar implant.

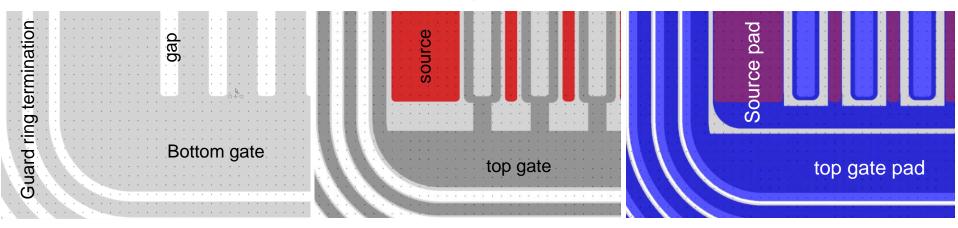

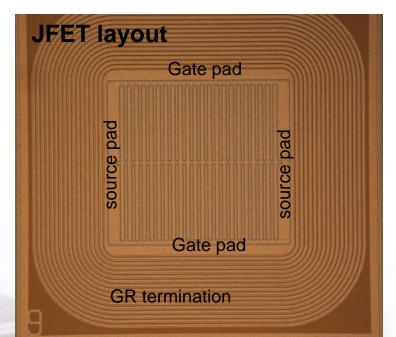

#### The layout

Interdigitated design to increase the gate width and thus the ON current (especially after irradiation).

The active area is  $1x1 \text{ mm}^2$ , which sets the gate width to 20 cm.

Triode configuration, top-gate connected to the bottom-gate.

6 photolithographic masks, 4 implants.

Both *n*-type and *p*-type JFET, on 4" epitaxial wafers (TOPSIL):  $50\mu$ m thick, N<sub>C</sub>~ 1e14cm<sup>-3</sup>.

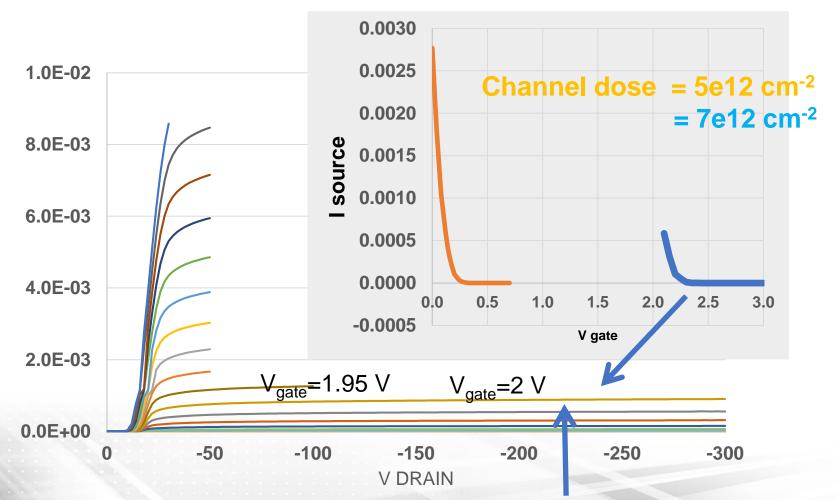

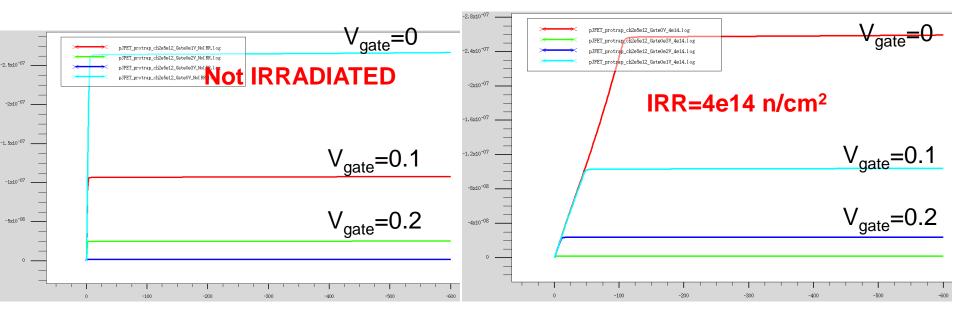

#### **I-V characteristics before irradiation**

Splittings on the channel dose.

At the lower doses, the channel was pinched-off already at V<sub>gate</sub>=0V The higher the dose, the lower V<sub>BD</sub>.

We irradiated the devices with higher current capability (but lower V<sub>bd</sub>) 16

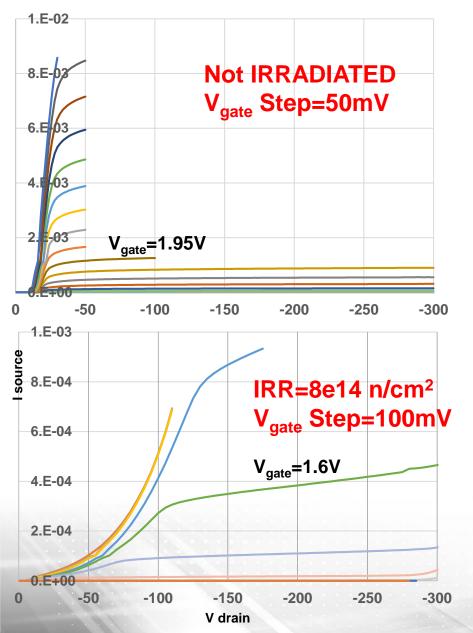

#### **Irradiation results**

#### Neutrons at TRIGA, JSI

#### **TCAD simulation of ideal irradiated HV-JFETs**

# **Conclusions and Outlook**

- Silicon Clean Room has fabricated LGAD with good performances Still, some place for improvement (shallower implants, ..)

- Silicon lab testing capabilities to be expanded (cold probe station, beta scope)

X-ray gain measurements to be closely investigated

HV-JFET fabricated tested and irradiated.

irradiation results to be understood by means of TCAD

# **BACK-UP**

#### LGAD structure

LGAD are intended to be used in HEP thanks to their fast-timing properties, (timing detectors for the upgrades of the ATLAS and CMS at the High Luminosity LHC).

- Same principle of APD but lower gain, without breakdown

- Electrons must initiate the avalanche, not holes  $\rightarrow p$ -type substrates/gain layers

- Multiplication layer must be uniform (no pixel or strips in the multiplication region: only pads ~mm<sup>2</sup>)

G. Giacomini, et al. "Development of a technology for the fabrication of Low-Gain Avala