## Status of the LHCb Upgrade

*Federico Alessio,* CERN on behalf of the LHCb Collaboration

FSP Meeting, 01/10/2019, Rostock, Germany

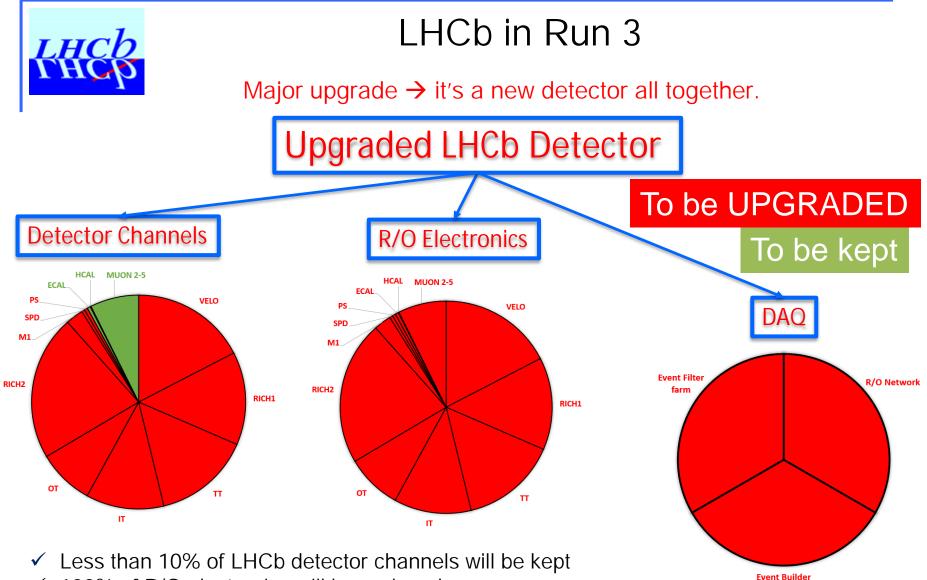

- ✓ 100% of R/O electronics will be replaced

- ✓ NEW DAQ system and DATA CENTER

\* not touching on RTA, offline and computing aspects which are covered in separate presentations

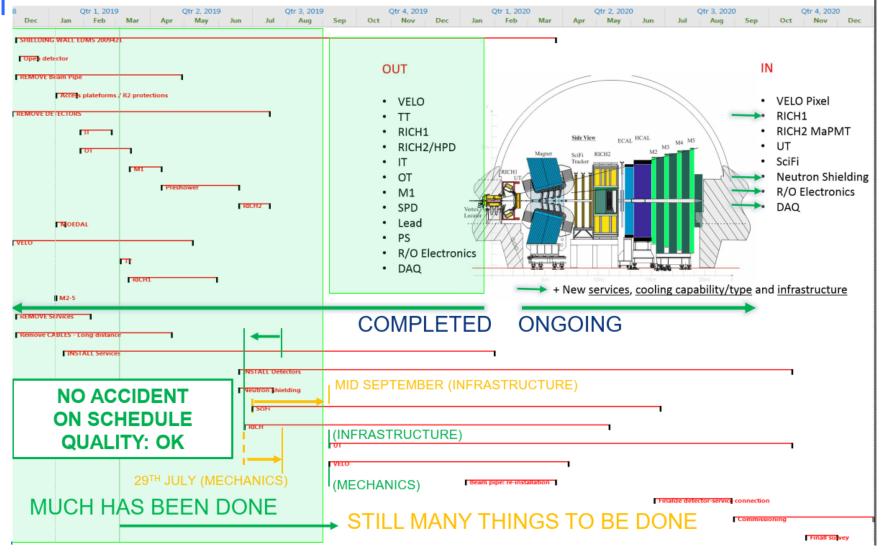

### Installation planning and status

LHCb Upgrade Status, 01/10/2019

F. Alessio, CERN

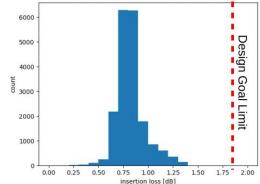

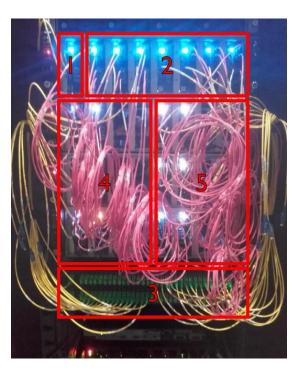

### Installation of fibers & data center

#### Fibers: installed 19008 (132 trunks)

- Only 44 pieces out of spec

- yield 99.77% vs contractual limit 95%

- Insertion loss < 1.4 dB @ 99.77%

#### Data center: 6 module fully delivered and pre-commissioned

- Many little "and not so little" bugs ironed out

Insertion Loss - All Fibers, 850 nm

LHCb Upgrade Status, 01/10/2019

# *гнср*

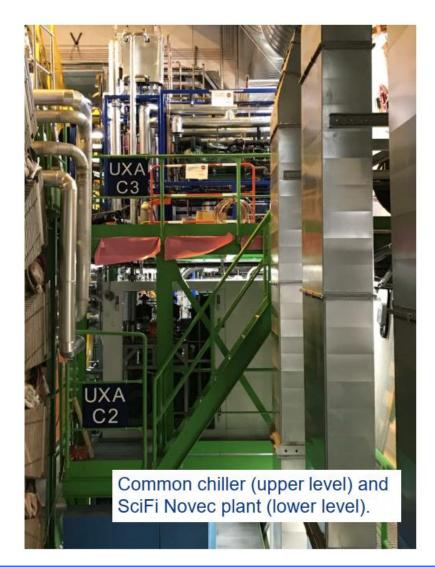

### Installation of detector cooling

LHCb Upgrade Status, 01/10/2019

## Installation of SciFi neutron shielding

- Shielding of the SiPM against neutron

- Installation already completed by end of June 2019

## Installation of RICH1 mechanics

- Magnet shielding modifications

- MaPMT support mechanics

- Gas enclosure

- Quartz window broken

- $\checkmark\,$  delay being absorbed in global planning

LHCb Upgrade Status, 01/10/2019

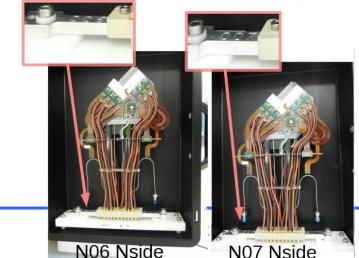

### VELO status: modules

Microchannel substrates (52): 49 wafers at CERN with a *minimum* of 55 grade A susbtrates.

Tiles (208): 300 at CERN, 220 qualified, almost done.

Interconnect flex sets (52): all available but mounting fault. All being reworked at CERN (expect done beg. Oct).

**GBTX hybrids** (104): 112 produced, being assembled. Issue with com loss at -15°C was understood (config fix)

FE hybrids (208): 157 delivered, being assembled, and delivery of 143 expected soon

VELO module components (for 52 modules + few spares)

LHCb Upgrade Status, 01/10/2019

Midplates, legs, capillary clamps (52): fully produced, no issue

LV harnesses (52): 11 produced. More coming.

**HV cable sets** (52): original design had a small modification on the C side.

**Cooling connector assemblies** (52): 62 delivered, 35 usable, more being produced

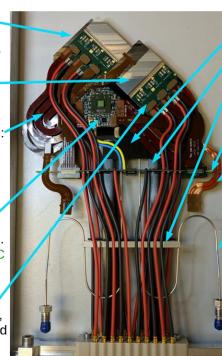

#### VELO module production

### VELO status: rest of production

Rest of Production: Respecting a "just in time" schedule, but some concerns for parts (tiles, microchannels, connectors) Mechanical production on track

- Commissioning plans underway at Liverpool

- Modules Integration sign-off by assembly sites

#### 1 prototype and 3 production RF boxes **completed** 4th production box to be completed in a few weeks.

|    | Leak<br>tightness | Shape         | Thickness                                                        | Comment                                                                                                                      |

|----|-------------------|---------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| A1 | $\checkmark$      | $\checkmark$  | ~ 500 µm to ~ 200 µm (min<br>150 µm) before and after<br>etching | Pathfinder R&D box. 17 etching<br>steps. Shape slightly deformed,<br>problably during transport                              |

| C1 | $\checkmark$      | $\checkmark$  | ~ 280 µm                                                         | First successful demonstration<br>of milling to 250 µm. Residual<br>thickness variations, though<br>small, disfavour etching |

| A2 | $\checkmark$      | $\checkmark$  | ~ 280 µm                                                         | Milled with granular offsets applied. Candidate for etching                                                                  |

| C2 | $\checkmark$      | $\checkmark$  | ~ 280 µm                                                         | Milled with highly granular<br>offsets applied. Candidate for<br>etching                                                     |

| A3 | In producti       | on, successfi | ul so far, expected resul                                        | ts similar to C2 and A2                                                                                                      |

## VELO commissioning activities

Will ramp-up in the coming month with production fading down.

Non final components to be replaced with time and their control integrated to  $\ensuremath{\mathsf{ECS}}$

VELO COMMISSIONING

Victor Coco

September 10, 2019

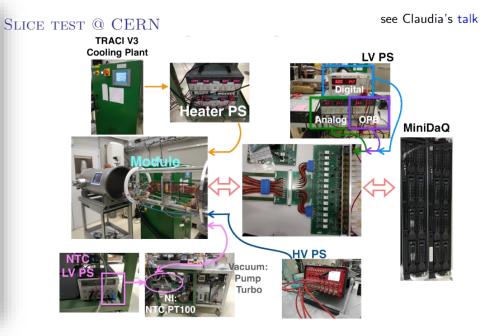

#### Complete slice test prepared at CERN

4 / 15

### VELO commissioning activities

|                   | 👙 Maddada 304  |                        |                                                       |                        |                            |                                                                                                                 | 10.12         |

|-------------------|----------------|------------------------|-------------------------------------------------------|------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------|---------------|

| evice Manager     | 65             | System                 | State                                                 |                        | Vie: 88-May-2018 14:87.16  |                                                                                                                 |               |

| ning on: Velo     |                | MINELAQ                | HEADY & A                                             |                        |                            |                                                                                                                 |               |

| there Logist Fish | Sub-System     | State                  | G Monael, OPE 10P                                     |                        |                            |                                                                                                                 |               |

| te ven            | Eng            | NOT BEADY 8            |                                                       | State                  |                            |                                                                                                                 |               |

| Ministry .        | MIP            | READY                  | Device<br>Medual OPD                                  | NOT REALY V B          |                            |                                                                                                                 |               |

|                   | TFC            | READY B                | 1 SA                                                  | 100100                 |                            |                                                                                                                 |               |

|                   | MiniDAQ_Eurado | NEXDY 2                |                                                       |                        |                            |                                                                                                                 |               |

| 20.72             |                |                        | Opto & Power Board                                    | Velo:Module0_OPB       |                            |                                                                                                                 |               |

|                   |                |                        | SCA Centrol                                           | Configuration Settings |                            | Resistor Settinos                                                                                               |               |

| 2                 |                | State                  | SCA CONTROL                                           |                        |                            |                                                                                                                 | hange Values  |

|                   | DAQ NO         | ALADY S'E              | ADC & KADC & Mosel OF                                 |                        | Set Apple                  |                                                                                                                 |               |

| Sub-System        | State          |                        | / GBLD @ / GELD @                                     |                        | Sel Apply                  |                                                                                                                 | Pre-Series v1 |

| TELLM             | NOT SEADY      |                        | × GRO Q × GPID B Reset B<br>× VTRx B × VTRx C Reset D |                        | Set Apply                  |                                                                                                                 | Pre-Series v2 |

| 15                | NOT BEADY      |                        | 2 VITE O 2 VITE O                                     |                        | Set Apply                  | VeloPix Digital Concernor                                                                                       |               |

| 8.3P              |                |                        | Acoly Acoly 0 0                                       | RxDV                   | Defaults                   | 1.5V Compensation point 200                                                                                     |               |

|                   |                |                        |                                                       |                        | Defaults                   | 2.5V Components plan 1 tion Evit                                                                                | = hedo Ohm    |

| <u></u>           |                | State                  | - DC/DC Power Converters                              |                        | - Laser Driver S           | ettions                                                                                                         |               |

|                   | PE NO          | READY E                |                                                       |                        |                            |                                                                                                                 |               |

| Sub-System        | State          |                        | Input Off Science                                     |                        | GELD BH                    | CBLD FH                                                                                                         |               |

| 098               | NOT DEADY      |                        | BH Analogue (1952) sine                               | or byta                | OWF                        | 1792(18/107116)                                                                                                 |               |

|                   |                |                        | IBA DAGREE STREET                                     | VP1-MD Analogue        | VTEx 8H                    | VTRA FM                                                                                                         |               |

| 1                 |                |                        | PH Acalogue (5.6512 volt                              | OF On Digital          | 0. Drahle                  | Constant Constant                                                                                               |               |

| <u></u>           |                | State<br>1 HEADT 2 T   | SHI Digital (S. 2013) and                             | VP2-NS: Analogue       |                            | 6                                                                                                               |               |

| $\sim$            | CPB NU         | HEADA NO T             |                                                       |                        |                            | STRO Bans                                                                                                       |               |

| Sub-System        | State          |                        | Actions Al OT On                                      | or on Digital          | O Disable L                | Disable Large                                                                                                   |               |

| Module0_OP8       | NOT READY      |                        | Module Oit On                                         | VF2-CSO Analogue       | VITEZ R                    | VITE ALCON                                                                                                      | in market     |

| Wedule1_OPE       | Exege 🕺        |                        | VelaPix Off On                                        | off on Digital         | O Disable L                |                                                                                                                 |               |

|                   |                |                        | - Celour Label Legend                                 | Catty Catty            |                            | the second se |               |

|                   |                | Control led by SCA Bit |                                                       |                        | VITE 6 A Pro-              |                                                                                                                 |               |

|                   |                |                        | 01 01 01.0                                            | O Disuble 1            | (monumente) Orabia) U mon  |                                                                                                                 |               |

|                   |                | Control led by SCA FH  | OF On 1981                                            | UTX4 8                 | VITE A pro-                |                                                                                                                 |               |

|                   |                |                        | OF Dr. Link 2                                         | O Diseble L            | ormenter the Ormable Carte |                                                                                                                 |               |

| kessages          |                |                        | Fall of the read-out chain<br>for Medicin Kack Side   |                        | VITAS A                    | VITe 35 A.                                                                                                      |               |

|                   |                |                        | Fat of the read-out chain                             |                        |                            |                                                                                                                 |               |

|                   |                |                        | for Medulo Front Side                                 | CTRL CTRL              | O Disable                  | O Deable L stra                                                                                                 |               |

- Integrate temperature monitoring and interlock board when ready.

- Integrate data analyses in "final" software environment.

- VeloPix setting optimisation, equalisation, noise scan, test pulses, IV scan, CCE scan, timing scan, online monitoring, ...

- Preliminary implementation for most of the procedures.

- $\blacktriangleright$  Several based on ECS  $\rightarrow$  change procedure and move to GWT data.

- ▶ To be integrated to our FSM, and analysis in LHCb software

- ► Tell40 router not ready yet → developed a decoder that time order GWT data output (see Tom's talk)

Tell40 router address to the set of the se

LHCb Upgrade Status, 01/10/2019

> Discussions with the online group and online data quality monitoring.

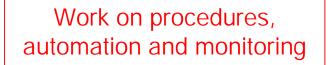

### UT status: production

To be produced: 68 staves + spares

#### COMPONENTS

#### Sensors:

- Type A: 1020 tested OK (60 not as good but usable).

- Types B,C,D: pre-series tested, expect 48xB, 16xC & 16xD by mid Sep.

Bare staves: 100% produced + spares

#### Data Flex: produced at CERN, ongoing

- Preproduction batches "Short-1" (27pc) and "Medium-1" (20pc) tested and delivered

- Batches Short-2to5 and Medium-2to5, and Long-1 in production (different stages).

- Production expected finished by ~end of Oct.

SALT chips: v3.5 OK, v3.8 pending tests

#### Hybrids: critical path

- 4-chip hybrids: firm chosen, started production

- This drives now the stave production schedule

- decided to use a "firm-validation" preproduction (~80 hybrids) from one of the bidding firms for the first 5 staves.

And inner staves: 8-ASICs, to be assessed.

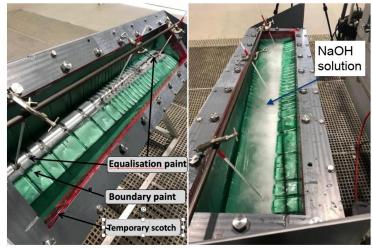

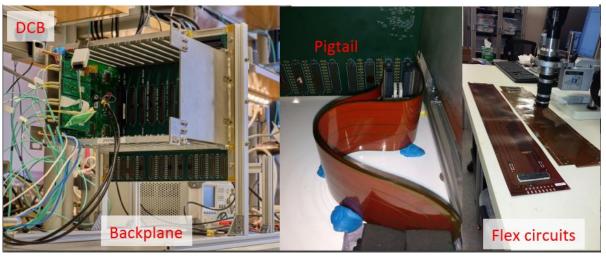

### UT commissioning activities

#### Slice test prepared at CERN

- Pre-production stave successfully shipped from USA

- First test of full stave with realistic power distribution and grounding, plus CO2 cooling and mechanics

- Two PEPI crates with two DCBs

- Connected to stave via flex cables

- One MiniDAQ2 with control and readout firmware

- $\checkmark$  Mostly excellent results up to now  $\rightarrow$  low noise

LHCb Upgrade Status, 01/10/2019

### **RICH** status: column production

- test column thoroughly tested

- RICH upgrade column production phase started

- mechanics for first five RICH 2 production column assembled, full RICH 2 mechanics produced

- Elementary Cells Quality Assurance: two facilities (Ferrara and Edinburgh) at full speed 80 ECs/week

- Photon Detector Module Digital Board Quality Assurance: assembly and testing (Cambridge, Oxford and Bucharest) at full speed

- cabling and fibre mounting strategies finalised for production chain

- flow of components (EC and PDMDB) from Quality Assurance test centres well synchronised to keep up with the column assembly schedule

- column assembly accelerating!

### first column assembled in June: test column

used to develop test protocol, DAQ infrastructure and tools. ECS...

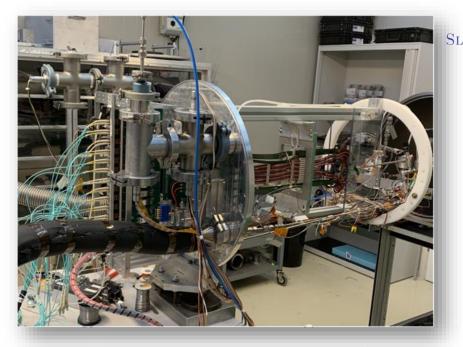

### **RICH** commissioning activities

### Columns being tested and commissioned @ CERN

Commissioning lab equipped with readout server + HV/LV + ECS

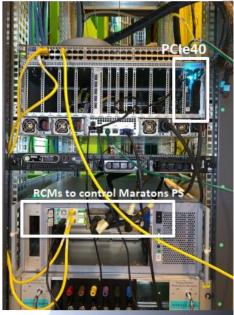

#### PCIe40 Server installed by Online group:

- 3 boards installed for RICH commissioning: 2 TELL40 and 1 SOL40

- temperature issues mitigated during summer

- Storage (file server) installed:

- 39 TB for data (dedicated 10Gb/s link to PCIe40 server)

- 2TB for shared software and WinCC projects (running elsewhere)

DAQ software:

- it can generate both MDF and FRG files

- Online monitoring under development

Test facility (very stable in the past months) allowed us to fully validate test column performing:

- test pulse injection runs to calibrate electronics (step run)

- threshold scans to set working points and calibrate MaPMTs gain (step run)

- dark counts runs

- dedicated runs for SIN

#### general news:

- switch to WinCC-OA 3.16 successful

- OPC-UA servers for Caen (HV), Maraton (LV) and ELMBs (temperature and humidity monitoring) installed and working

#### HV:

- recipes for CALIBRATION and PHYSICS runs created

- implementation of dynodes powering in the FSM

- almost complete implementation

DCS:

- LV control

- monitoring of temperature and humidity on the test column and SSB1 environment via ELMB

- Safety FSM, reacting to temperature too high or column temperature too close to the dew point, is running

- Calibration of SCA-ADC current source, used to monitor ~100 temperatures per column, is ongoing

- monitoring of the Pt1000 ADC registers from SCA will be done from the DCS project

LHCb Upgrade Status, 01/10/2019

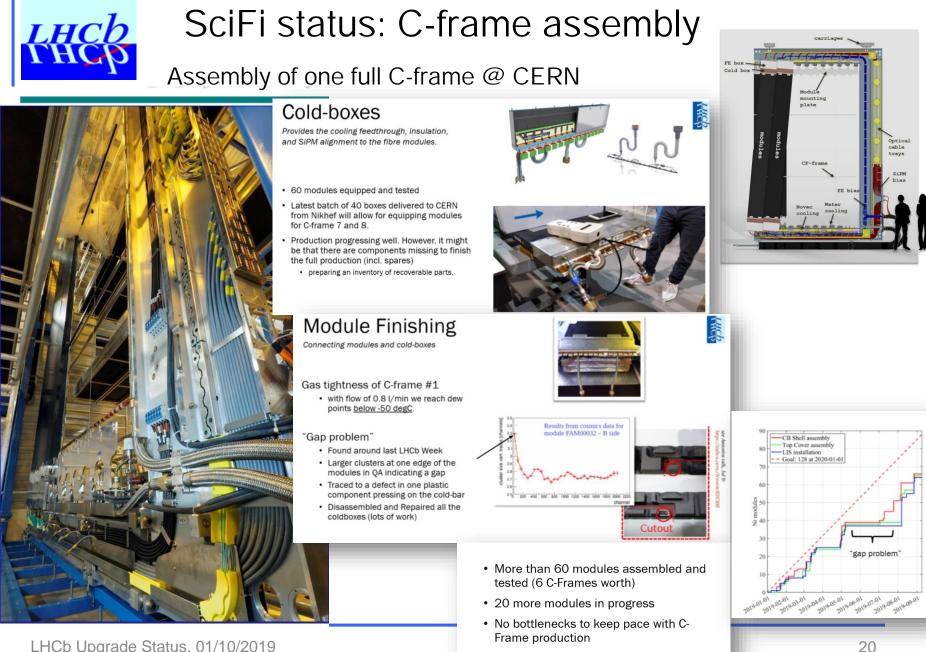

# **KHCK** SciFi status: FE electronics & commissioning

### Front-end Electronics

Digitises the SiPM signals, finds the cluster barycentre, output to PCle40

| PACIFIC Chip     | 100% produced and tested                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| PACIFIC Board    | 100% produced and tested (updated)                                                                                                    |

| Cluster Board    | 100% prodcued and tested (updated)                                                                                                    |

| Master Board     | Preseries 50 MBs: ok                                                                                                                  |

| [35% done]       | Main production (570 boards):<br>Batch 1: 96 MBs in July<br>Batch 2: 104 MBs in Aug (updated)<br>Next batches: 20 Sep, 08 Nov, 06 Jan |

| Mechanical Parts | 100% produced                                                                                                                         |

|                  |                                                                                                                                       |

| Front-end boxes  | Preseries (23) ready $\rightarrow$ frame1<br>Batch 1: 30 boards at CERN (updated)<br>Next batches: 30 FEBs/3 weeks                    |

#### In time wrt to the C-Frame assembly

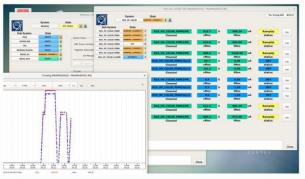

| FEE controls                                                                                                                                                   | Configure all HallROBs     Recipes Expert Tools Res HalROB to show     Filter by name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Controls exist<br>- Not final                                                                                                                                  | SFDAQFECT3L200M0H0 * ** SFDAQFECT3L200M0H0 on sfminidag02-dev-S40_01 Get ID 1 READ CONFIX Master Gat Read Configure Read Serial FSH SH SHARE GAT PW Next Serial FSH SHARE GAT PW Next Serial FSH SHARE GAT SHA |

| Main issues:                                                                                                                                                   | Cluster         MasterBoard         B0188C         FE         18           FPGAs         Halfs         0         1         2         3         4         5         7           Data G8Ts         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         61         6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <ol> <li>Prepare FSM         <ul> <li>Propagate states</li> </ul> </li> <li>Rewrite RESET             <ul> <li>No power-up at CONFIGURE</li> </ul> </li> </ol> | Cluster Board 0         Cluster Board 1         Cluster Board 2         Cluster Board 2           SCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ol> <li>Possibility to<br/>exclude slice of<br/>½ ROB</li> </ol>                                                                                              | PACIFIC Board 0         PACIFIC Board 1         PACIFIC Board 2         PACIFIC           PACIFIC 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# **LHCD** SciFi status: FE electronics & commissioning

### QA check of main series FE boxes ongoing

- Cabling checks : done

- Readout commissioning ongoing with final PCIe40 cards

- One C-frame quarter electronics installed

- $\checkmark$  6 x FEBs = 96 data links

- Further installation suspended due to

"condensation" problem on Novec and dry-gas lines

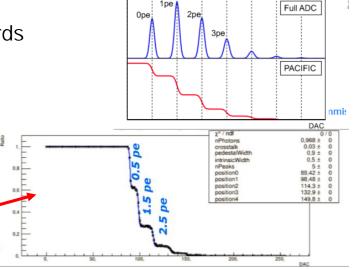

- First Light calibration done

- ✓ Scan of pulse delays between 0ns and 15ns in steps of 1ns  $\rightarrow$  being analyzed

- $\checkmark$  S-curves for all channels  $\rightarrow$  being analyzed

- Charge injection done

- ✓ Scan of pluse injection timing in steps of 3.125ns. All channel show a uniform plateau

- Bit-error rates tests performed: good results < 10<sup>-15</sup>

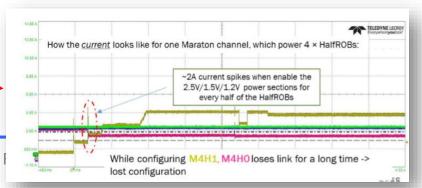

- Issue with GBT losing lock during FE reset

- Problem investigated, found and solved

- ✓ Issue when current consumption on Maraton channel > 10A

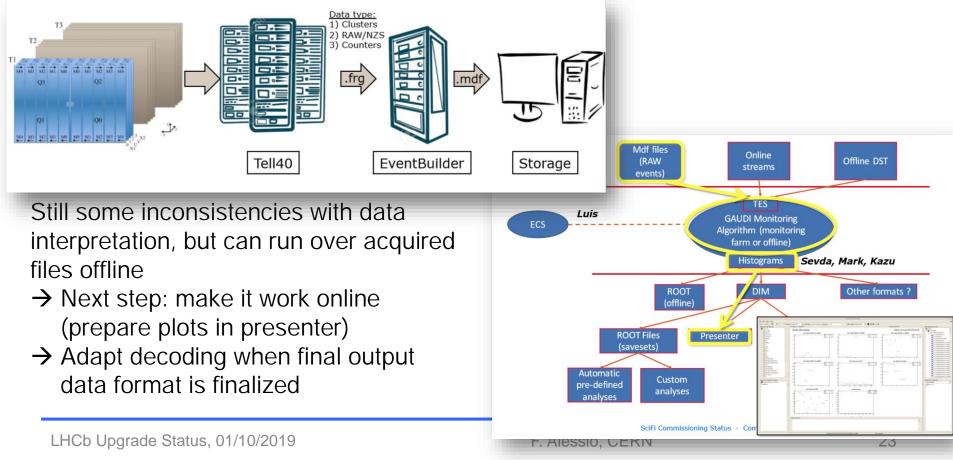

# SciFi commissioning of monitoring system

A lot of pioneering work ongoing in commissioning first monitoring system (of LHCb)

- Allows for fast analysis and visualization of acquired data

- Fast feedback when performing commissioning/calibrations

## SciFi commissioning summary

- Progress on many fronts, but also some worries:

- FEE control

- Major restructure ahead (RESET function, disable parts)

- Suffering from GBT instabilities

- Databases/recipes

- Database for Calibration values missing

- LV+DCS control

- Ok

- HV control

- Recipe creation from database values missing

- PCIe40

- All 3 final data formats in progress: 1) Cluster 2) NZS/RAW 3) Counters

- Cannot connect 48 links per pci40 ; only 4 pci40 cards installed

- Data monitoring

- Setting up Gaudi versioning non-trivial

- PACIFIC calibration

- Validation of S-curve fits needed for large number of channels

SciFi Commissioning Status - Commissioning meeting 10 Sep 2019 - Niels/Snow

### CALO status: production

### **New Electronics Status**

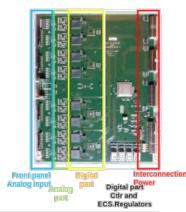

- ICECAL: 40MHz ASIC for CALO upgrade (new gain / low noise)

- FEB: front-end digitizer board, hosts 8 ICECAL, 40 MHz readout

- CB: control board

- · HV & Moni & Calib: control mezzanine, ECS mezzanine, GBT fanout

| Board<br>Type | Needed | Produced | Tested | Installed | Full production<br>Expected<br>delivery time | Comments                                                                 |

|---------------|--------|----------|--------|-----------|----------------------------------------------|--------------------------------------------------------------------------|

| ICECAL        | 2224   | 2x3050   | 100%   | n.a.      | completed                                    | 2 types (2 gains)                                                        |

| FEB           | 278    | 2        | 2      | -         | Finish in February<br>2020 *                 | 2+16 pre-series, then batches of $\sim$ 32                               |

| СВ            | 21     | -        | -      | -         | Finish in<br>December**                      | 3 boards to be received soon<br>Full production in parallel with the FEB |

| Ctrl mezz     | 66     | 100%     | 95%    | -         | completed                                    | Completion of the tests this summer                                      |

| ECS mezz      | 66     | 100%     | 95%    | -         | completed                                    | Completion of the tests this summer                                      |

| GBT<br>fanout | 12     | 100%     | 95%    | -         | completed                                    | Completion of the tests this summer                                      |

\* Found a producer mistake in the preprod of 2 (used wrong files) => delay of one iteration ~ 3 months

\*\* Because wait for 16 FEB before production

### CALO status: at the pit

#### Status at the pit

- The SPD/PS/Lead and old FEB electronics dismantling is completed

- some mechanical parts of the XCAL FEB will be re-used for the new boards:

- Front panels, handles, bars etc

- Almost all unnecessary old cables have been removed

- except SPECS

- The MARATON power supplies have been modified by Bruno Allongue

- The backplane and connection cables should also be adapted

- The procedure was tested at lab and at pit

- All crates will be modified in situ, at the platform, in September (?) and tested (test procedure to be defined)

- Detector side

- Removal of the very central HCAL PMTs, preparations to the installation of the new beam plug

- Replacement of ECAL signal connectors at the PMT side (tbc)

- Maintenance of the ECAL & HCAL movement systems

- Hardware and software

- A dedicated meeting will be organized in October

- No (or) limited detector displacement during some operations !

- To be planned

### MUON status: production

### **New Electronics Status**

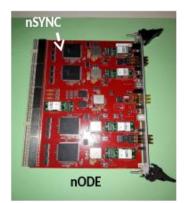

- nSYNCs, nODE: 40MHz readout, each nODE equipped with 4 nSYNCs

- nSB, nPDM: system configuration and pulsing

- nBP: custom Back Plane for nPDM/nSB crates

| Board Type | Needed (+<br>spares) | Produced | Tested | Installed | Full production<br>Expected<br>delivery time | Comments                                          |

|------------|----------------------|----------|--------|-----------|----------------------------------------------|---------------------------------------------------|

| nSYNC      | 760                  | 2800     | 2800   | 96        | Done                                         | All nSYNCS sent to the company for ODE production |

| nODE       | 148+42               | 24       | 17     | 8         | Dec*                                         | Pre-production delivered                          |

| nSB        | 120+20               | 20       | 20     | 14        | Oct - Nov*                                   | (new) Pre-production delivered                    |

| nPDM       | 8+2                  | 2        | 2      | 1         | Nov*                                         | Pre-production delivered                          |

| nBP        | 8+2                  | 2        | 2      | 1         | Nov*                                         | Pre-production delivered                          |

\* some delay compared to last LHCC, but not critical.

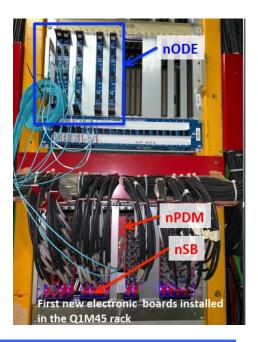

Started installation of nODE boards in the pit

### MUON status: commissioning at the pit

- The first test is ongoing with the commissioning rack:

- 1 PCle40 + Server

- 2 Primary PS + 2 RCMs to power up and control the 2 Maratons of each Muon rack

- Conditions approximately as in RUN3:

- PCle40 "DAQ" board, configured as SOL40

- 350m long fibers (from PCIe40 to nODE/nPDM)

- We are starting with the connectivity test:

- at first, to debug/test the new software, on a "good" detector region (Q1M4) where no IB have been removed

- then we move to all other regions

- Switch to the official online system as soon as available

**Commissioning Rack**

- the Q1M45 rack is now equipped with new electronics (for M4):

- 5 nODE (3 more available)

- 14 nSB + nPDM + nBP

**Communication with nSBs & nODEs is established:** we can configure them, read back, send pulses from nSBs to FEBs and receive counts from FEBs to nODEs (this part we need for the connectivity test)

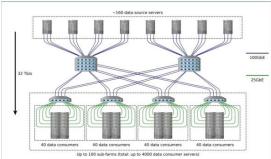

### ONLINE status: plan

### Online procurement and installation planning

| Item                                           | Date                                      |

|------------------------------------------------|-------------------------------------------|

| Long-distances fibers ready                    | Q3 19                                     |

| Data-centre ready                              | Q4 19                                     |

| ECS network and TFC distribution               | Q3 – Q4 19                                |

| Readout servers                                | Q4 19 – Q1 20                             |

| Event-builder network (core)                   | Q1 20 – Q2 20                             |

| Prototype storage                              | Q1 20 (together with IT department)       |

| Servers and storage (bulk)                     | Q4 20 Q1 21 (together with IT department) |

| GPGPUs OR event-builder network (distribution) | Q1 21                                     |

|                                                |                                           |

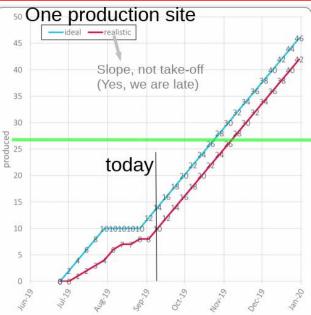

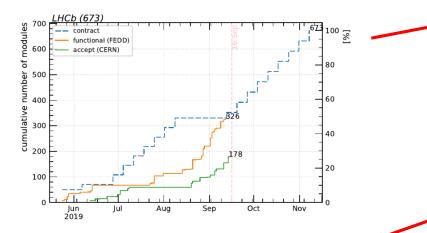

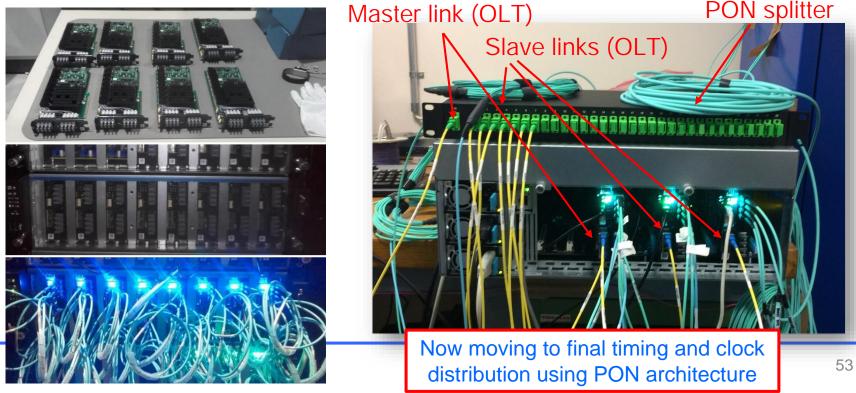

### ONLINE status: readout cards production

#### ~50% produced by end of September:

- Initial delay of ~5 weeks, now reduced to 2 weeks

- Investigating final needs  $\rightarrow$  are the numbers still enough?

#### Being "accepted" in IT4 Data Center

- Final operating conditions

- Using validated cards as injectors (SOL40) for cards to be validated (TELL40)

- Afterwards stored away

# **CHCC** ONLINE status: 1° fw/sw production release

Spent the past months in preparing first production releases of:

#### • central firmware and software

- → For commissioning and assemblies: control, readout, timing

- $\rightarrow$  Validation and continuous integration ongoing

- ✓ Firmware/software workshops 18-22/03 and 15-19/04 and 20-24/05 and 24-26 /06 and all summer...

#### Fundamental cooperation with sub-detector experts

- Adiabatic commissioning of sub-detectors and central systems

- → Checkpoints to follow sub-detectors development

- → At the same time, grow expertise in the community

- Such expertise will be necessary during detector commissioning!

#### Few aspects are still missing towards global commissioning:

- Timing distribution to FE with fixed latency

- Integrate system with Event Builder as in final configuration

- Scalable control firmware covering full 48 links

- Integrate in global system

- + a very long list of small little tasks...

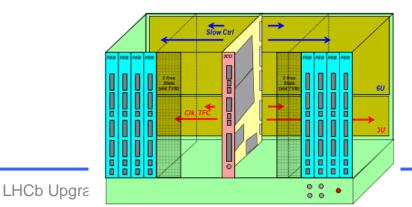

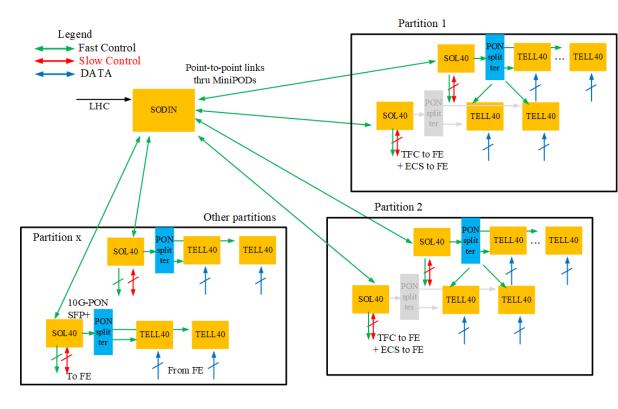

## ONLINE status: online integration

#### Developed setup for integration tests ("Vertical slice"):

- Identical final operating conditions

- Using bidirectional accepted cards as injectors (SOL40)

- Two partitions:

- Readout supervisor and interface cards (1-2)

- Optical splitter for clock and timing distribution (3)

- Readout cards (4-5, two partitions)

- Production versions of:

- Firmware

- Control system

- Event building

- HLT

- Storage

### Plan to use it for:

- PCIe40 testing, multi-card integration, WinCC

- Event Builder validation/review/testing Finishing

- Integration with production releases

- Ultimately for monitoring + HLT + online + storage integration

→ Now

→ November

$\rightarrow$

> April

### ONLINE status: event builder

#### Two options on the table: dedicated vs distributed

- $\rightarrow$  Reviewed on June 6, 2019

- Check for appropriate performance, scalability, usability and cost

- Probe possible risks, both technical and financial

Conclusion:

- Confident that the EB team can get both solutions to work (distributed w/ deep buffers)

- The cost does not seem to be a determining factor in the choice

- Set of recommendations

- Continue testing the distributed options

- Set up complete data-flow chain with eventbuilding, monitoring and ECS in the Vertcal Slice test (ongoing)

- Prepare a document describing flow-control and overflow handling and dead-time accounting

#### Dedicated EB (TDR baseline)

Technology: Infiniband

+ Ethernet for Distribution

#### Distributed EB

Technology: **Ethernet** Switches: deep-buffer (expensive) vs shallow-buffer (cheap)

### → Final choice by December 2019

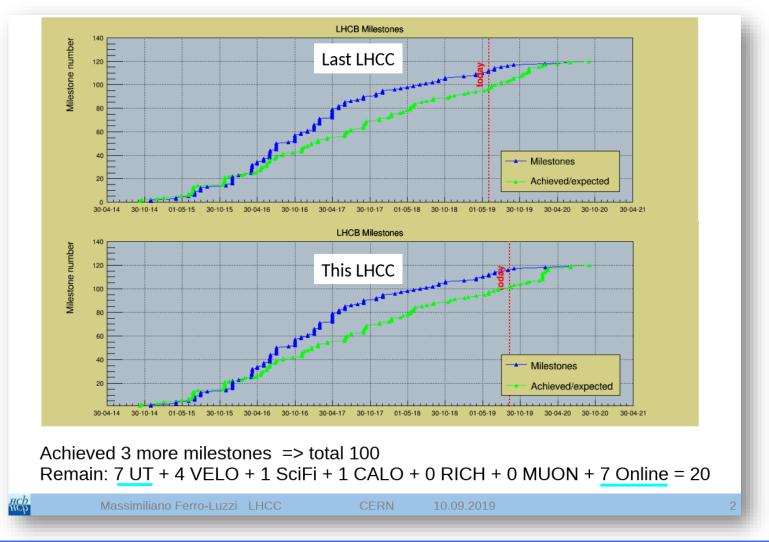

### LHCb Upgrade milestones plot

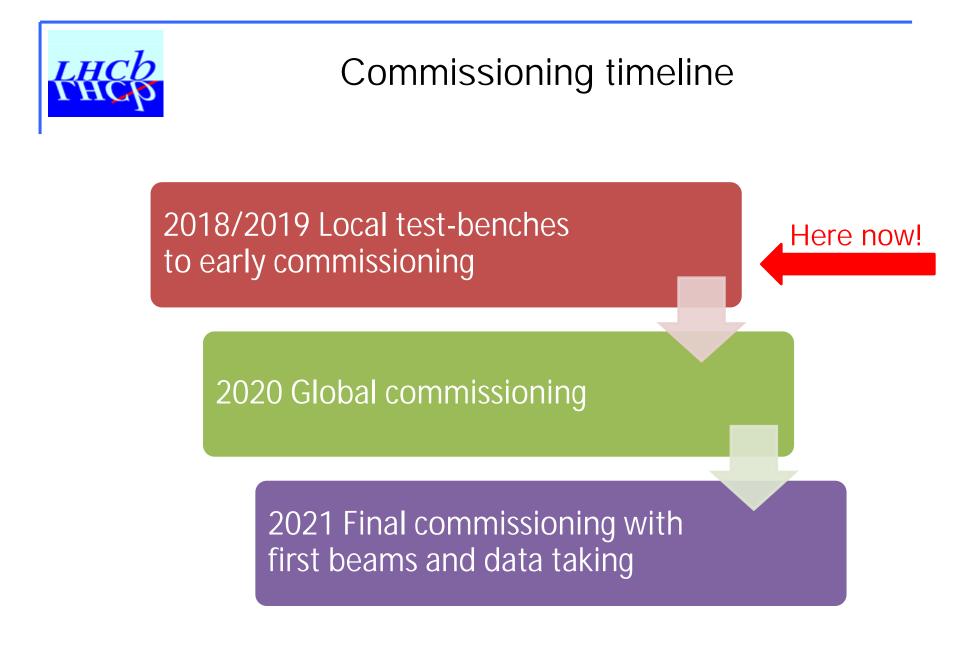

# **KRCP** Early commissioning to global commissioning

Currently moving from local test-benches to early commissioning

- most delicate phase: move towards "final" and "global" systems coherently

- develop tools targeting final system already

- final software/firmware/hardware commissioning currently ongoing

- ✓ early commissioning phase

- sub-detectors need to move in parallel towards developing tools

- The tools are system tests

- ✓ Test-beams, validation slices, assembly setups are the *opportunities* to be able to arrive at the commissioning step ready and prepared

- ✓ Gauge the level of preparedness at each step

- global commissioning can start once central online infrastructure is installed and commissioned itself!

- to start beginning of 2020

- ✓ overlap between local commissioning and global commissioning

- ✓ adiabatic inclusion of new sub-systems as they become ready

- ✓ coordination between sub-detector activities and centralized (online) activities

## Global commissioning short-term goals

Spring:

- Readout part of a detector (slice test) with new electronics

- Coordinate the needs from sub-detectors (early) commissioning

Currently all sub-detectors are equipped with central hardware and software to kick-start local commissioning work and follow production

Summer: make sure we arrive at the Online commissioning ready

- New PCIe cards coming in now

- → currently being accepted/validated in Online

- Keep track of sub-detectors' development

- o Make sure to move ahead in parallel with development

- Broken record: It's not just the cards: monitoring, infrastructure, Event Building, ECS...

Autumn:

- Central online system commissioning

- Fibers + data center then TFC and ECS

- Iron out last issues with central tools

- o Continuous integration and validation framework developed

- Support sub-detectors with commissioning to be ready for 2020

Here now!

# Next steps in the next months (aka commissioning milestones)

First thing in the pipeline  $\rightarrow$  Online commissioning

1. Data center commissioning

- 2. PCIe40 acceptance, validation

- All SOL40s already tested

- Now testing first batch of TELL40s using SOL40s as data generators

- 3. Vertical slice party

- New cards + timing distribution + partitioning + WinCC + EB + HLT passthru

- 4. Online system installation + commissioning

- TFC + ECS hardware and software

- TELL40s and clock distribution/recovery

- Event Builder + online network

#### 5. Sub-detectors commissioning with global online system

- ETA beginning of 2020

- With reduced resources in FARM then towards 2021 with full resources

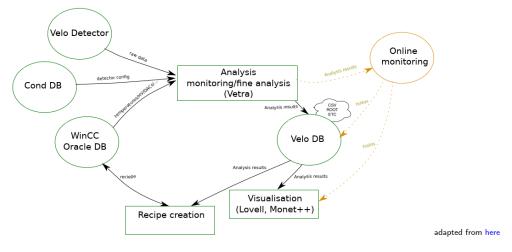

# Online Data Monitoring (data quality)

The monitoring of the LHCb detector should be considered a broader and important task/activity than it has been up to now.

One shifter is entirely dedicated to "monitor" the detector: the tools should make his/her work easy and should be adequate to the task Monitoring system will be the rock on which our future detector will rely on: not many chances to go back and fix an "alignment bug"

Monitoring system is an absolutely essential tools for commissioning and it should not be a burden on the experts.

Work on global monitoring system is going to pick up momentum from now on

- from diagrams on a paper to real implementations

- commissioning of monitoring system to happen with commissioning of detector

- ightarrow Thinking about solutions and implementations should start now

- o Online RTA collaboration fundamental here

- Use local commissioning setups to "build up" features

- Coordination by Patrick Robbe, second monitoring workshop currently scheduled for 11<sup>th</sup> October 2019: <u>https://indico.cern.ch/event/849009/</u>

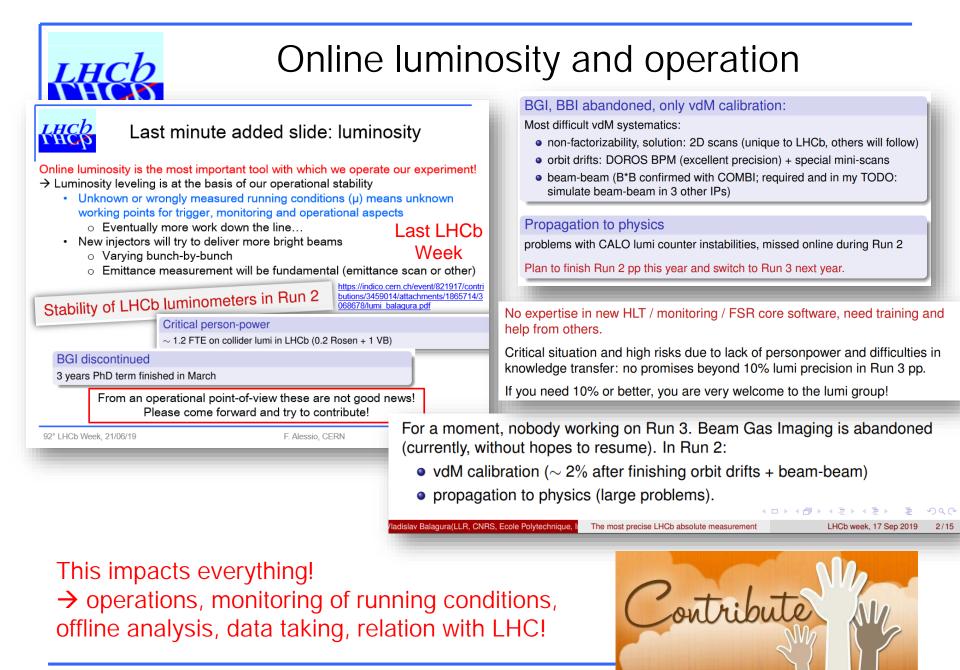

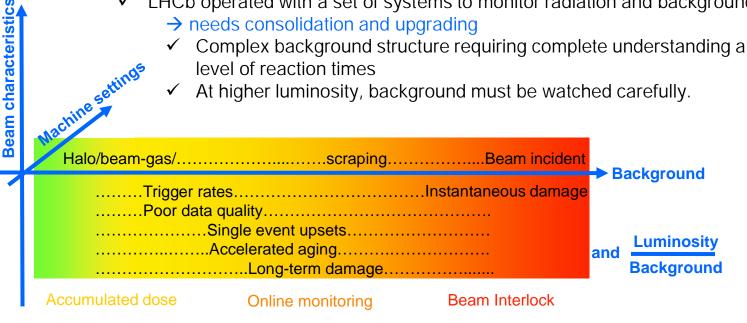

# Online luminosity and beam monitoring

From Run3, beam and luminosity monitoring will become an important tool to evaluate the performance of our detector in the LHC environment

- High radiation levels for a long enough time can trigger a beam dump

- Background is the normal life around an accelerator but it can be unacceptably high such that it affects the quality of data

- If high, it can also decrease the expected life of the detectors

- ✓ LHCb operated with a set of systems to monitor radiation and background in Run 1&2

- $\rightarrow$  needs consolidation and upgrading

- Complex background structure requiring complete understanding and widely different

- level of reaction times

- At higher luminosity, background must be watched carefully.

# Online luminosity and beam monitoring

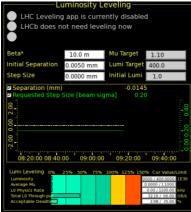

- 1. Online luminosity determination

- This is absolutely fundamental.

- Today, we use activity in the calorimeter to infer the mu

- ✓ Use the zero-bin (no activity), then  $mu = -log(fraction_ncalo)$

- ✓ But after the upgrade, no L0 trigger (+ zero-bin depleted)

- We need to find a strategy to measure mu

- ✓ We need a live counter: Leveling is a *real-time* application as well

- updated regularly and within a few seconds

- ✓ Cannot rely 100% on just HLT events

- because the luminosity determination should also be independent from running the DAQ → heavy machinery !

- But it should be integrated in it in order to cross calibrate various sources

- ✓ Ideas developing regarding an LHCb "*dedicated luminometer*"

- as a flexible system that can be used also for other applications

- a lot of opportunities here for young scientists w/o a huge budget...

- Involve more people in the luminosity working group.

- ✓ Manpower there is very limited and will surely profit from additional help.

# <u>гнср</u>

# Online luminosity and beam monitoring

#### 2. Beam interlocks and beam monitoring

Today we use the BCM (beam conditions monitoring) and the BLS (beam loss scintillators) to monitor beam induced background

- Beam/background conditions must be watched at higher luminosities.

- ✓ Evaluate impact of bad vacuum, UFOs, bad machine conditions etc

- BCM worked beautifully during the entire Run1&2

- ✓ Interlocked when needed, always justified and followed up

- ightarrow In LS2: readout system replaced and consolidation on the sensors

- → On a longer term, need to start thinking of a new BCM to be deployed from Run4 and beyond

- ✓ HL-LHC will be a different pp environment

- ✓ 25ns readout, dump logic/thresholds, what technology? Couple with luminometer?

- ✓ Not needed for Run 3, but ideal to have it under test before end of Run3

- 3. LHC clock reception, distribution and monitoring

- LHC clock distribution won't change until LS3.

- ✓ But clock phase changes due to temperature dependent fibers

- What about adding timing information in the upgrade?

- ✓ Old system to monitor clock phase could profit from this additional piece of information. Beam timing must be monitored.

**BCM**

# LHCb is in a unique position

- ✓ We can literally "see" our IP

- ✓ We have bigger beams ( $b^* = 1.5m$  in Run3)

- ✓ We have SMOG(2)

- $\checkmark\,$  We have an innovative and creative attitude

- ✓ We have the handle of a huge upgrade → LHCb in the spotlight in Run3

We have some "free" space in front of the VELO

List of desiderata

- bunch-by-bunch quantities

- time information

- "live" beam shapes/emittance

- integration in upgraded DAQ

- automatic reports/monitoring

- correlations with other quantities (vacuum, mu, detectors...)

#### → Invite proposal of new detectors!

F. Alessio, Dernie already reviewed

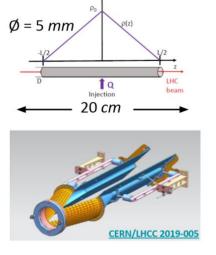

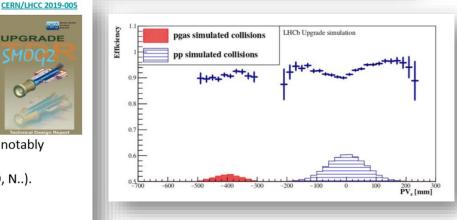

### SMOG2

UPGRADE

- The gas pressure follows a triangular profile.

- System composed of two retractable halves to follow the Velo closing procedure.

- Light and thin material, to keep low the material budget and appropriately coated to prevent electron clouds forming.

- Electrical connectivity ensured by the wake field suppressor.

- Cell installation approved for November 2019.

- Smog2: Upgrade of the fixed-target programme consisting in the installation of a confinement cell covering the [-500, -300] mm region.

- Cell installation approved for November 2019.

- In principle, excellent candidate for a super-early measurement: can we measure in pgas system with only beam1 stably circulating?

Gas density can be increased up of two orders of magnitude with the same gas flow of Smog.

- Gas pressure, and thus luminosity, can be precisely measured, notably reducing systematic uncertainties.

- With machine approval, more gas species can be injected (H, O, N..).

#### Unique FT physics program!

LHCb Upgrade Status, 01/10/2019

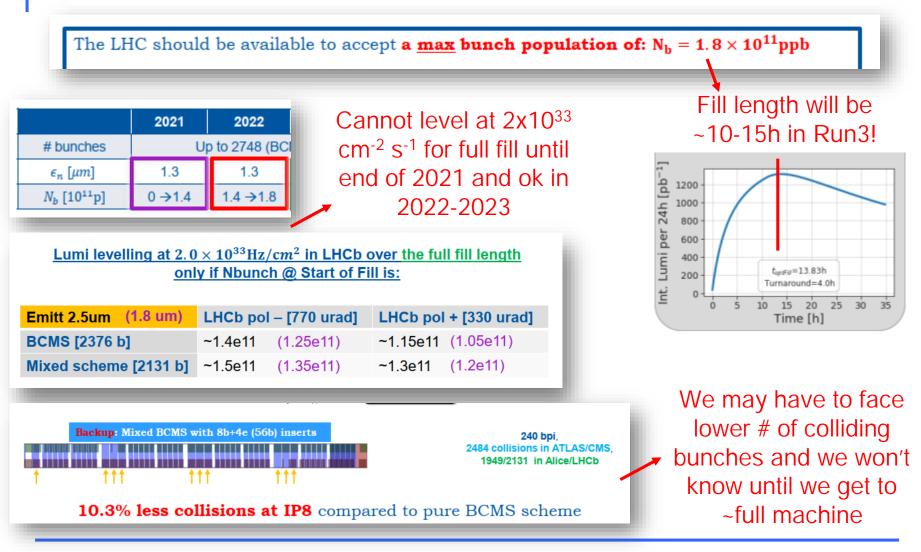

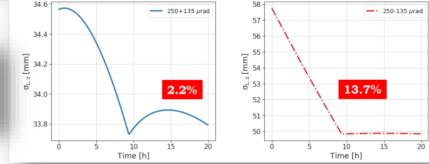

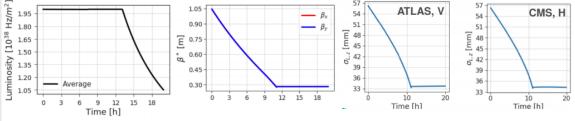

# **Luck** Run 3 running conditions requests to the LHC

For Run3, what beam parameters are we going to expect and what running conditions are we going to ask? We need to start thinking about it now!

- Levelling at 2x10<sup>33</sup> cm<sup>-2</sup> s<sup>-1</sup> throughout entire length of fill

→ Enough margin to do so in 2021 and 2022/2023

- 2. Maximize number of colliding bunches

- 3. Minimize crossing angle differences between magnet polarities

→ Add V x-angle and remove external H x-angle

- 4. Include new VELO aperture, investigate limitations on  $\beta^*$  reach

- 5. Energy stable throughout Run 3

- 6. Luminous region size (in z) above 37mm

- $\rightarrow$  If new crossing angle, bunch length leveling may not be needed

- 7. Mixed filling scheme ok if homogeneous pileup distribution among bunches

- → Many requests taken in considerations and accepted by LHC

- 2021 will be a commissioning year for the LHC as well

- 2022-2023 will be production year. 2024 is uncertain.

# Run 3 expectations: LHCb commissioning with beam

#### At the beginning of 2021, LHCb will have 90% of its detector new

- Need some early collisions to commission time alignment, initial scans, operational aspects, understand detector.

- ✓ Schedule early 450 GeV collisions (more than once)

- → Stable Beams & closing the (new) VELO @ 450 GeV would be highly appreciated

- $\rightarrow$  to cross check with LHC what the limit is

- ✓ Schedule early 2x2 bunches beam at ~7 TeV (more than once)

- $\rightarrow$  Also more than 2 bunches/beam, but no trains yet.

- TED shots may still be useful even if coming from opposite direction

- ✓ Commission the "mechanics" of time alignment

- $\checkmark$  Does not give final values  $\rightarrow$  need beam for that.

- $\rightarrow$  We could use/commission the new LHCb SMOG2 system for that

- → Can profit from simple circulating beams

- Need to schedule a full set of safety interlock commissioning with LHC

- ✓ According to installation/commissioning schedule, expect Q4 of 2020.

- ✓ New vacuum valve? Logic and connections to the BCM

#### Tight collaboration with EMTF (Early Measurement Task Force)

✓ Before "early" measurement, perform "early" commissioning ☺

# Conclusions

Installation is on schedule and absorbing delays where necessary

Sub-detectors local commissioning activities taking momentum

- SciFi, RICH, VELO and UT daily clients. Now also with CALO and MUON.

- Vertical slice ready w/ new PCIe40 cards being extensively used

- Firmware and software released in the first production versions + online commissioning

Strongly fostering a spirit of collaboration, sharing, inclusion and communication:

- We highly welcome the cooperation with sub-detector experts

- While keeping an eye on consistency and guidelines: do not repeat things twice!

Attention in covering all aspects of operations

- Data quality and detector monitoring

- Beam/background/online luminosity monitoring + interlocks

- Monitoring of beam conditions and online luminosity is fundamental for our success!

LHC being very cooperative in preparing the LHCb running conditions for Run3

LHCb Upmany apossibilities to contribute to the success of LHCb Upgrade 4/!

## Backup

# Global commissioning ultimate goal

The goal of 2020 should be to be able to take data with the vast majority of the upgraded devices included and using the global centralized system

- "cosmics" data taking over long periods of time

- remember: there is no hardware trigger, so seeing a "cosmics" event would be an interesting moment...

A et of milestones for this phase are being defined in collaboration with sub-detectors experts.

- (JIRA) Tasks generation

- Action lists and follow-up during regular commissioning meetings

- Coordination of parallel activities, sharing of resources

- Definition of data taking activities, conditions, modes

- Training of experts and non-experts

- Build a strong team of operational experts such that many can use the weapons at our disposal

# Commissioning tasks and follow-up

Set-up a JIRA project to follow-up commissioning activities https://its.cern.ch/jira/secure/RapidBoard.jspa?projectKey=LHCBUPGCOMM&rapidView=6465

- $\rightarrow$  Being setup over time as I get information/generate tasks

- Added more tasks recently and assigned tasks to users

- Integrate with other sub-detectors and their tasks/charts

- Also used as documentation and resources tracking

| O Add | ✓ O Delete ✓                                                                                            | Data 🕶                                                          |          |              |                        |       |                        |                                                   |                                                            |                                |                 |                                 |               |    |              | Jun | p to Gantt Bar Today          |

|-------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------|--------------|------------------------|-------|------------------------|---------------------------------------------------|------------------------------------------------------------|--------------------------------|-----------------|---------------------------------|---------------|----|--------------|-----|-------------------------------|

| # Î   |                                                                                                         |                                                                 |          |              |                        |       |                        | FY2018                                            |                                                            |                                |                 |                                 | FY2019        |    |              |     |                               |

| # T   | Project/Version/Issue                                                                                   | Assignee                                                        | Priorit  | y Start date | Finish date            | Perce | Due Date               | Q4                                                |                                                            | Q1                             | 0               | Q2                              |               | Q3 |              | Q4  |                               |

| 1     | ✓                                                                                                       |                                                                 |          |              |                        | -416  |                        |                                                   |                                                            |                                | 1               |                                 |               |    |              |     |                               |

| 1-1   | 👻 🗹 Run 3 running conditions                                                                            | 🧕 Federico Alessio                                              | Minor    | 20/Dec/18    | 31/Dec/19              | 4196  | 1/Jun/19               | Run 3 running conditions                          | -                                                          |                                |                 |                                 |               |    |              |     | Federico Alessio              |

| 1-1-1 | pp running conditions                                                                                   | 🚊 Federico Alessio                                              | Minor    | 20/Dec/18    | 31/Dec/19              | 50%   |                        | pp running conditions                             | -                                                          |                                |                 |                                 |               |    |              |     | Federico Alessio              |

| 1-1-2 | Luminous region size effects                                                                            | Vladimir Gligorov                                               | Mediur   | m 20/Dec/18  | 6/Mar/19               | 0%    | 6/Mar/19               | Luminous region size effects                      |                                                            |                                | Vladimir Gligor | rov                             |               |    |              |     |                               |

| 1-2   | UT commissioning                                                                                        | 🚊 Federico Alessio                                              | Minor    |              |                        | 0%    |                        |                                                   |                                                            | Federico Alessio               |                 |                                 |               |    |              |     |                               |

| 1-2-1 | Select PCIe40 cards and server                                                                          | Federico Alessio                                                | Minor    |              |                        |       | 1/Apr/19               | Select P                                          |                                                            | Federico Alessio               |                 | Ť                               |               |    |              |     |                               |

| 1-2-2 | Stave test                                                                                              | Mark Tobin                                                      | Minor    |              |                        | 0%    |                        |                                                   |                                                            | Mark Tobin                     |                 |                                 |               |    |              |     |                               |

| 1-3   | → RICH commissioning                                                                                    | Antonino Sergi                                                  | Minor    |              | 31/Dec/19              | 196   |                        |                                                   | RICH commissioning                                         |                                | 4               |                                 |               |    |              |     | Antonino Sergi                |

| 1-3-1 | Select PCIe40 cards and server                                                                          | Paolo Durante                                                   | Minor    |              | 15/Feb/19              | 30%   | 15/Feb/19              | Select P                                          | PCIe40 cards and server                                    | Paolo Dura                     | inte            |                                 |               |    |              |     |                               |

| 1-3-2 | Column test                                                                                             | Antonino Sergi                                                  | Minor    |              | 31/Dec/19              | 0%    |                        |                                                   | Column test                                                |                                | 4               |                                 |               |    |              |     | Antonino Sergi                |

| 1-4   | ✓ SciFi commissioning                                                                                   | Niels Tuning                                                    | Minor    |              | 30/Sep/19              | 0%    |                        |                                                   | SciFi commissioning                                        |                                | 4               | +                               |               |    | Niels Tuning | E   |                               |

| 1-4-1 | Select PCIe40 cards and server                                                                          | Fecusico Alessio                                                | Minor    | 4/Feb/19     |                        |       | 1/Apr/19               | Select P                                          |                                                            | Federico Alessio               | -               |                                 |               |    |              |     |                               |

| 1-4-2 | C-frame test                                                                                            | Niels Tuning                                                    | Minor    | 4/Feb/19     | 30/Sep/19              | 0%    |                        |                                                   | C-frame test                                               |                                |                 |                                 |               |    | Niels Tuni   | ing |                               |

| 1-5   | Vorking PCIe40 firmware                                                                                 | Guillaume Vouters                                               | Critical |              | 22/Feb/19              | 0%    |                        |                                                   | Vorking PCIe40 firmware                                    | Guillaur                       | me Vouters      | -                               |               |    |              |     |                               |

| 1-5-1 | TFC over SFP+ Interface and PON                                                                         | Mauricio Feo                                                    | Major    | 4/Feb/19     |                        |       | 1/May/19               |                                                   |                                                            | Mauricio Feo Guillaume Vouters |                 |                                 |               |    |              |     |                               |

| 1-5-2 | Include fix for clock path in XCVRs Define sub-detector partitions                                      | <ul> <li>Guillaume Vouters</li> <li>Federico Alessio</li> </ul> | Critical |              |                        | 0%    | 22/Feb/19<br>28/Feb/19 |                                                   | x for clock path in XCVRs<br>Define sub-detector partition |                                |                 |                                 |               |    |              |     |                               |

| 1-6   | <ul> <li>Define sub-detector partitions</li> <li>Follow-up of the production and delivery of</li> </ul> |                                                                 | Minor    |              |                        | 0%    | 28/Feb/19              |                                                   |                                                            | ns • Federico Aless            | 4               |                                 |               |    |              |     | Record to Gas                 |

| 1-7   | VELO commissioning                                                                                      | Victor Coco                                                     | Minor    |              | 31/Dec/19              | 0%    |                        | Follow-up of the production and delivery of the p | VELO commissioning                                         |                                | -               |                                 |               |    |              |     | Renaud Le Gac                 |

| 1-8   | Lab test                                                                                                | Victor Coco     Karol Hennessy                                  | Minor    |              | 31/Dec/19<br>31/Dec/19 | 0%    |                        |                                                   | VELO commissioning                                         |                                | -               |                                 |               |    |              |     | Victor Coco<br>Karol Hennessy |

| 1-8-2 | PCIe40 card in a MiniDAO server                                                                         | Paolo Durante                                                   | Minor    |              | 31/Dec/19              | 010   | 1/Apr/19               | B-0 - 44                                          |                                                            | Paolo Durante                  | 1               | <b>T</b>                        |               |    |              |     | Karol Hennessy                |

| 1-8-2 | MUON commissioning                                                                                      | Wander Baldini                                                  | Minor    |              | 31/Dec/19              | 01    | 1/Apt/19               | PC184U C                                          | MUON commissionine                                         | Paolo Durante                  | 4               |                                 |               |    |              |     | Wander Baldini                |

| 1-9-1 | Cavern test                                                                                             | Federico Alessio                                                | Minor    |              | 31/Dec/19              | 0%    |                        |                                                   | Cavern test                                                |                                | -               |                                 |               |    |              |     | Federico Alessio              |

| 1-9-1 | Select PCIe40 cards                                                                                     | Federico Alessio                                                | Minor    |              | 31/Dec/19              | 0%    | 1/May/19               |                                                   | Select PCIe40 cards                                        | Endorico Aleccio               | 1               | <b>T</b>                        |               |    |              |     | Pedenico Alessio              |

| 1.92  |                                                                                                         | Pederico Alessio                                                | MITO     | 4/760/19     |                        | 010   | innayi is              |                                                   | Jelett PCIew tarts                                         | Pedelico Alessio               |                 |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        | Y Sederico Alessio ad                             |                                                            | 45 /5-b (40                    | 0.50 414        |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        | <ul> <li>Federico Alessio ac</li> </ul>           | uded a commer                                              | 10 - 15/Feb/19                 | 9.50 AIVI       |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        |                                                   |                                                            |                                |                 |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        | Three PCIe40 cards gi                             | ven to RICH:                                               |                                |                 |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        |                                                   |                                                            |                                |                 |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        | #004 – to be used as                              | TFC master, into                                           | cik                            |                 |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        |                                                   |                                                            |                                |                 |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        | #010, #018 – to be us                             | ed as TELL40s,                                             | extclk(custom)                 | ).              |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        |                                                   |                                                            |                                |                 |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        | Installed in server Sup                           | erMicro #6588                                              | 009. Ibrichpcie                | 240-00 (use     | er Ibrich). Location 153/R-104, | lab 153/R-208 | 3. |              |     |                               |

|       |                                                                                                         |                                                                 |          |              |                        |       |                        |                                                   |                                                            |                                |                 |                                 |               |    |              |     |                               |

|       |                                                                                                         |                                                                 | 0        |              | 04/                    | 4.0   | 0040                   | Given also three USB                              | cables and two                                             | clock SMA ca                   | bles.           |                                 |               |    |              | = 0 |                               |