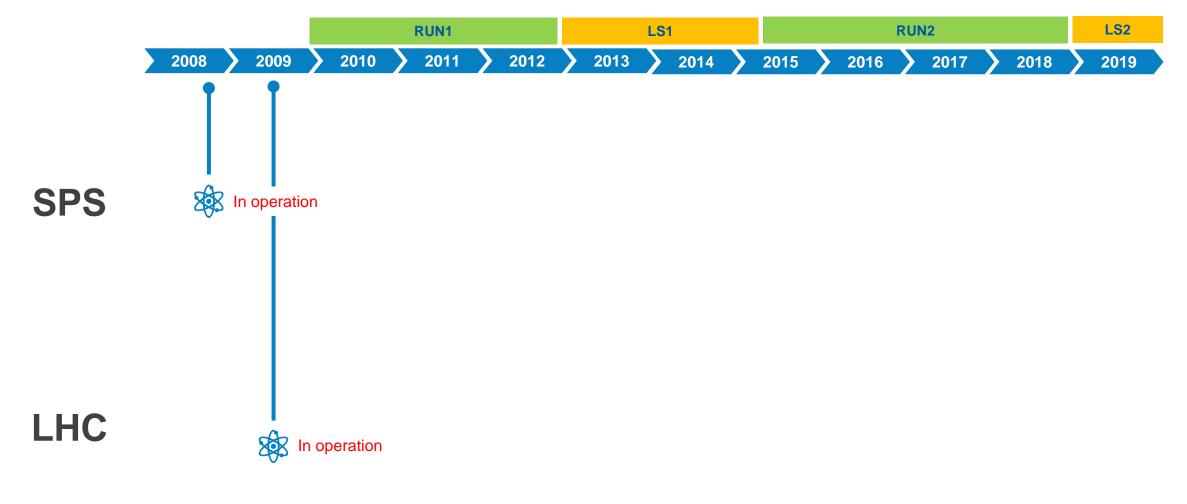

# Overview of the present SMP system

I. Romera Ramírez on behalf of TE-MPE-MI

21 June 2019 - Special MPP-SMP2 meeting

- SMP layout

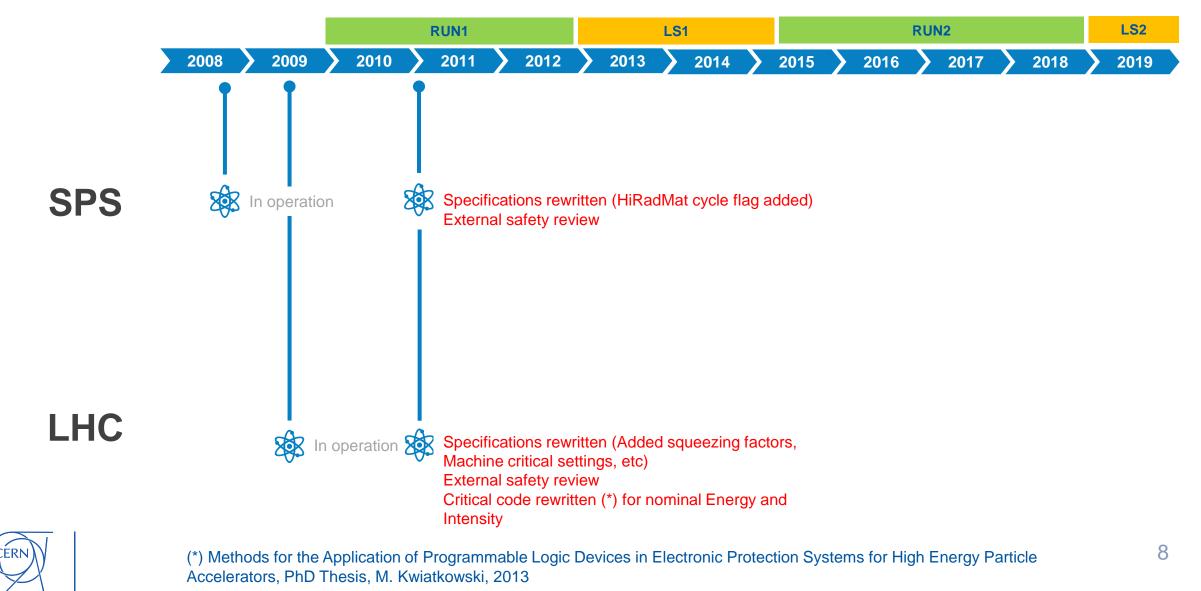

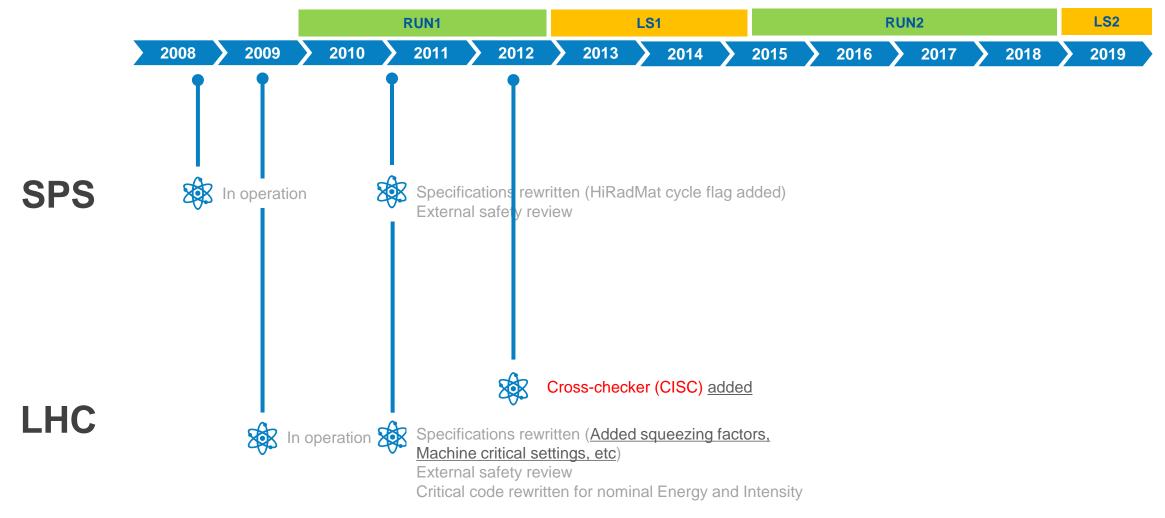

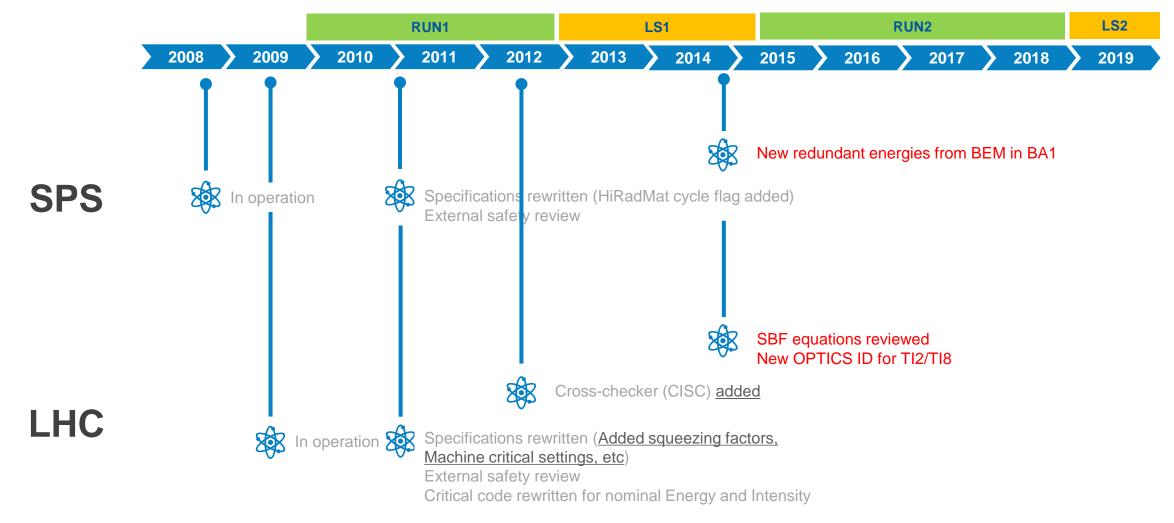

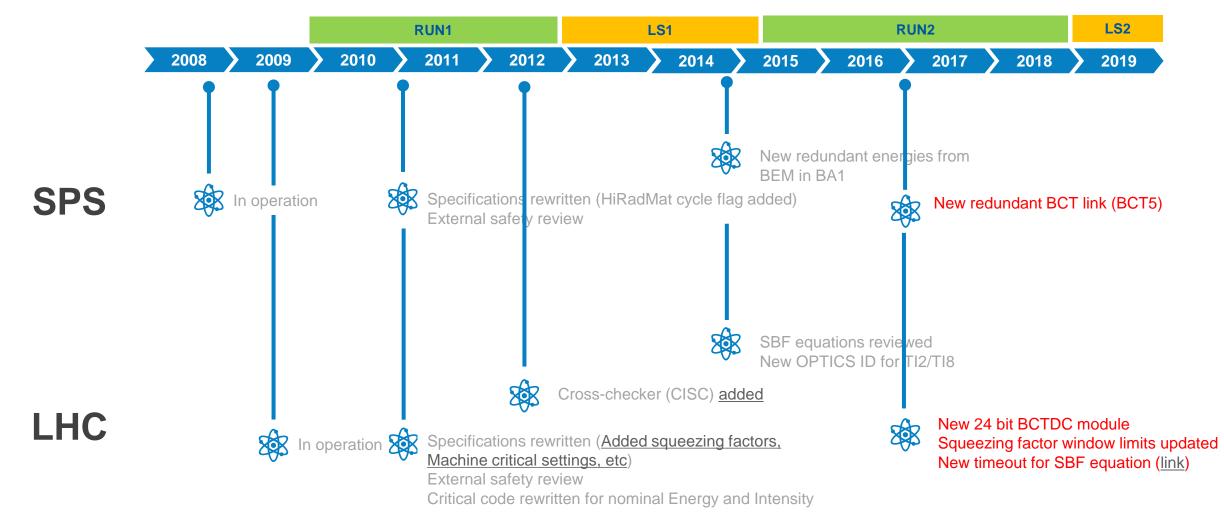

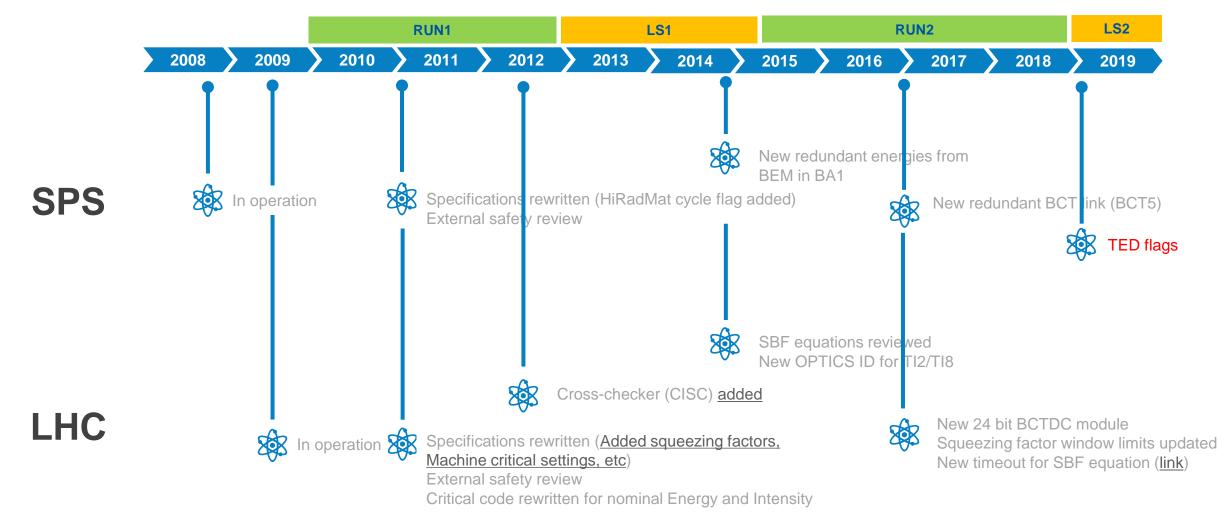

- Evolution of the system since deployment

- Dependability in RUN1 and RUN2

- Motivation to upgrade

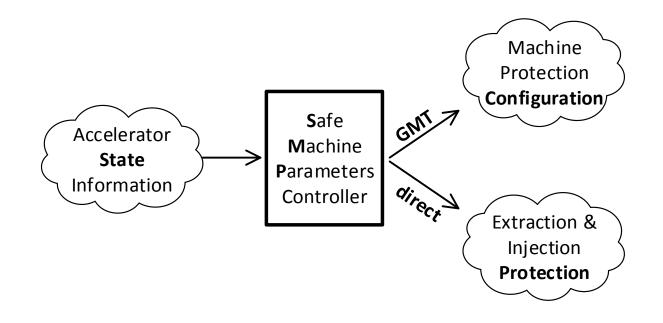

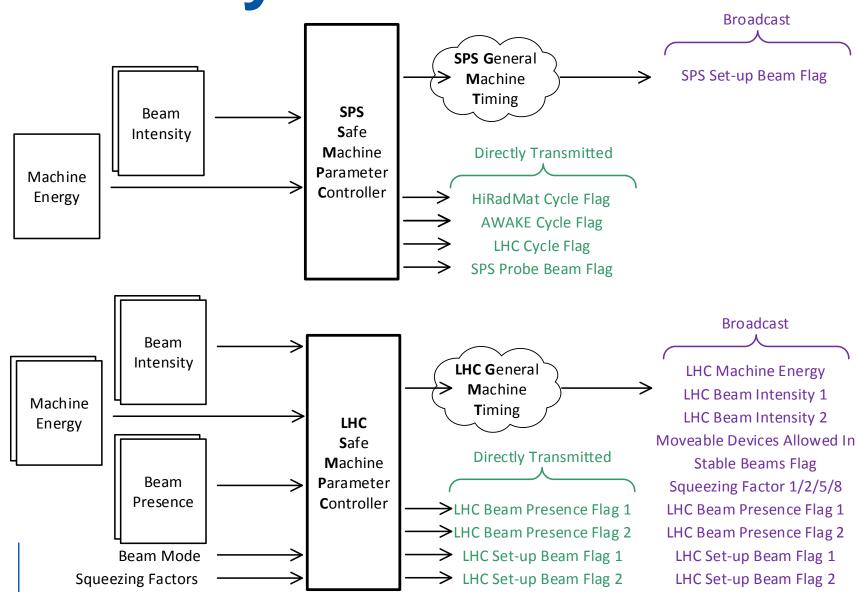

# **SMP Layout**

#### Fast, safe and reliable

# **SMP Layout**

CERN

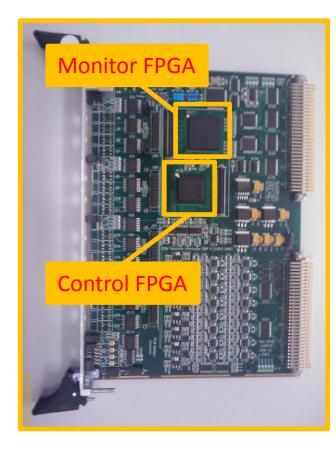

#### Hardware

- Hardware based on VMEbus

- Physical separation of critical / monitoring

- Redundant implementation for high safety

- Common HW design for all SMP boards (CISR, CISG, CISA and CISC)

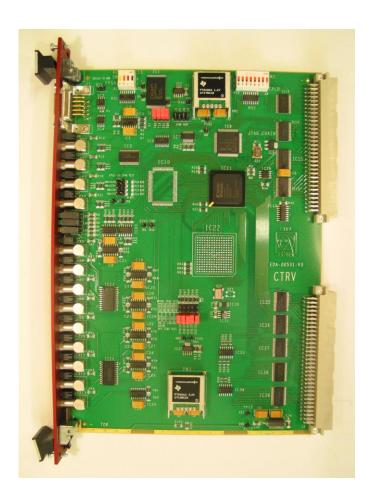

### Hardware to receive SMP flags

- CISV is used to decode LHC-SMP flags distributed over the GMT

- CISV based on standard CTRV (BE-CO) with dedicated firmware maintained by TE-MPE

- **44 CISV boards in operation** (BIS, BLM, MKI, TCD, ATLAS, ALICE, CMS and LHCb)

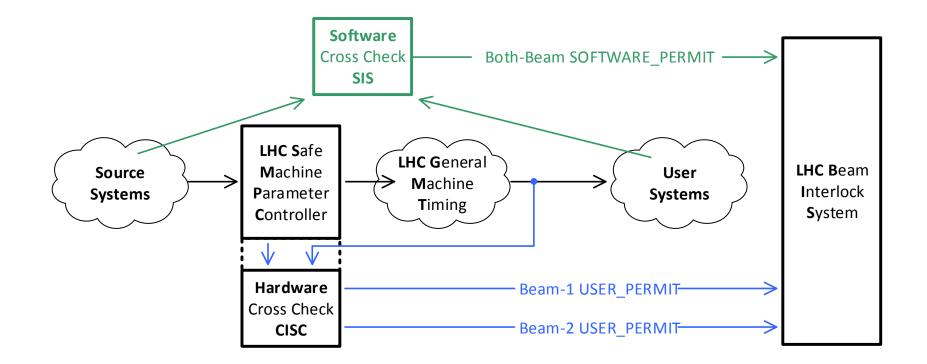

- A hardware cross-check (CISC) ensures that no discrepancies are observed between SMP and GMT

#### LHC: Cross-checker

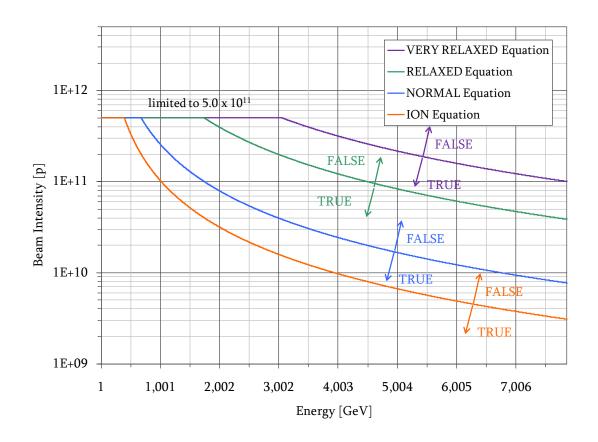

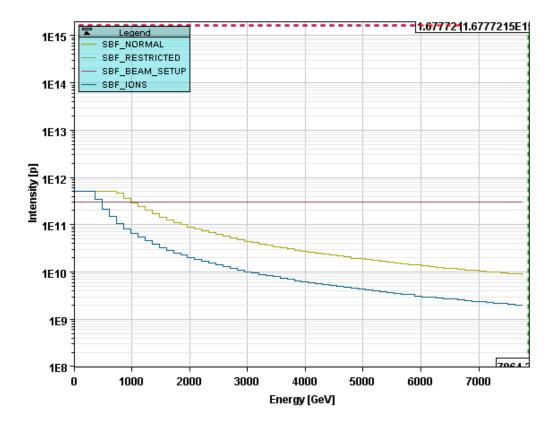

# **LHC: SBF equations**

SBF equations in RUN1

SBF equations in RUN2

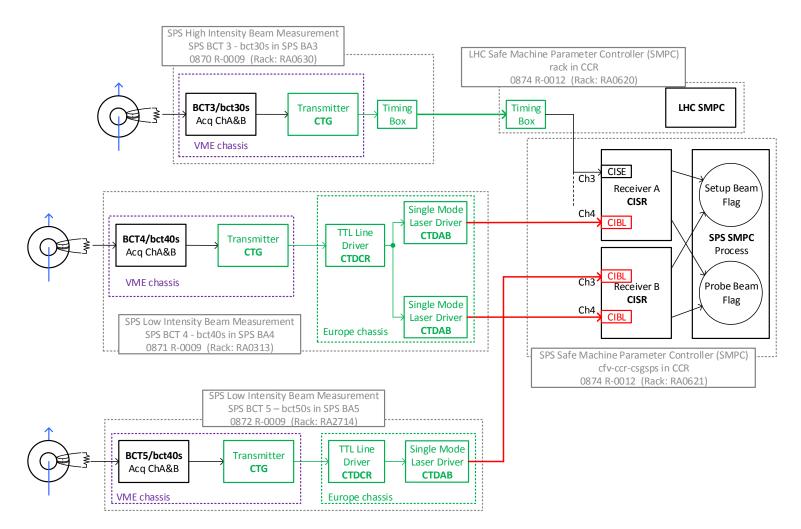

#### **SPS: Layout of BCTDCs since 2017**

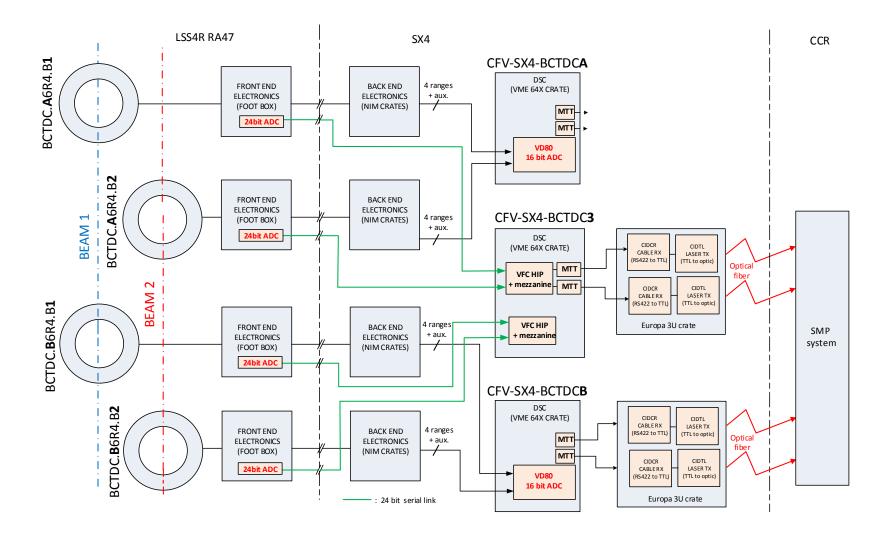

#### LHC: Layout of BCTDCs since 2017

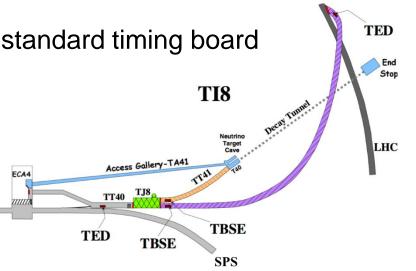

# **SPS: TED flag**

- TEDs will not be able to withstand a full 25 ns LIU batch consisting of 288b

- New machine protection strategy with LHC beams after LS2 (SPS-OTH-ES-0001)

- The maximum intensity to be extracted with TED in beam  $\leq$  3.34 x 10<sup>13</sup> protons

- Logic:

SPS\_TBF = true when (SPS\_INTENSITY  $\leq 3.5 \times 10e13$ )

else SPS\_TBF = false

- SPS\_TBF transmitted over the GMT and received via a standard timing board (CTR)

- 4 ELMA 3U VME chassis to be installed

# **Dependability in RUN1 and RUN2**

- 2010 March Beam dump triggered by SBF B1-A going erroneously false for 100 ms (<u>MPP link</u>), which led to the replacement of the external SBF threshold board by internal ROM in the FPGA. Fixed!

- 2010 April Availability issues due to Beam Presence Flag oscillating. Intensity close to the threshold (<u>MPP link</u>). Not an SMP fault, BCT responsible for the flag generation. SMP retransmission only. BPF filter implemented on SMP.

- 2012 March Beam dump due to SBF B2 going false. Could not confirm the cause but hypothesis is that BCT B2 sent spurious high intensity value

- 2018 February Issues with transmission of SMP flags to GMT during HWC. Faulty cable, switched to spare cable

- 2018 July Redundant power supplies from laser transceivers (CIBF) preventively replaced to avoid availability issues

# Motivation to upgrade

#### Obsolescence

- Discontinuity of critical electronic components Xilinx Spartan 2 / 3

- **Full occupancy** of FPGA logic cells no space for new features

- Aging of the present system -> support until end of HL-LHC

- Implementation of new requirements

- Transmission of Energy and Intensity in the SPS

- Transmission of bunch intensity in both SPS and LHC?

- Implementation of TED flags in LS2 required optimization

See Raffaello's talk

#### Conclusions

- Dependability of the present SMP system was extremely good during the RUN1 and RUN2, in particular after the major firmware upgrade in 2012

- The broadcast of mission critical flags over the GMT was proven to be adequate and reliable, thanks to the implementation of a hardware crosschecker

- An upgrade of the system is needed to guarantee the long-term maintenance (including implementation of new requirements) and to follow the BIS developments

# Thank you for your attention!