#### Microelectronic technologies for HEP Instrumentation

A. Marchioro CERN – Dept. PH 1211 Geneva 23 SWITZERLAND Alessandro.Marchioro@cern.ch

### Question

- Why is microelectronics so important for building detectors for particle physics?

- 1. Because it allows more compact detectors

- 2. Because it allows cheaper detectors

- 3. Because it allows more "intelligent" detectors

- 4. Because it allows more "sensitive" detectors

- 5. Because it allows more "precise<sup>(\*)</sup>" detectors

- 6. All of the above

<sup>(\*):</sup> space, time, energy

# Mythology on "Sensitivity"

#### Commercial cameras FWC

|              | ~ ~ ~ ~ ~ | ~~~~~  |

|--------------|-----------|--------|

| Canon 5D     | CMOS      | 80,000 |

| Canon 1DMII  | CMOS      | 79,900 |

| Canon 1DMIII | CMOS      | 70,200 |

| Canon 5DIII  | CMOS      | 68,900 |

| Canon 5D II  | CMOS      | 65,700 |

| Nikon D3     | CMOS      | 65,600 |

| Canon 1D IV  | CMOS      | 55,600 |

| Canon 30D    | CMOS      | 51,400 |

| Canon 20D    | CMOS      | 51,400 |

| Canon 20Da   | CMOS      | 51,400 |

| Canon 300D   | CMOS      | 45,500 |

| Canon 10D    | CMOS      | 44,200 |

| Canon 40D    | CMOS      | 43,400 |

| Canon 350D   | CMOS      | 43,000 |

| Nikon D300   | CMOS      | 42,000 |

| YM-3170A     | CMOS      | 35,000 |

| Canon 50D    | CMOS      | 27,300 |

| Canon 7D     | CMOS      | 24,800 |

| Canon 60D    | CMOS      | 24,800 |

| MT9D131      | CMOS      | 17,000 |

|              |           |        |

#### IEDM 2019: Samsung 64MP Sensor with 0.8um Dual CG Pixel

December 27, 2019 By Vladimir Koifman Leave a Comment

Image Sensors World Go to the original article...

Samsung IEDM 2019 paper "A 0.8 µm Smart Dual Conversion Gain Pixel for 64 Megapixels CMOS Image Sensor with 12k e- Full-Well Capacitance and Low Dark Noise" by Donghyuk Park, Seung-Wook Lee, Jinhwa Han, Dongyoung Jang, Heesang Kwon, Seungwon Cha, Mihye Kim, Haewon Lee, Sungho Suh, Woong Joo, Yunki Lee, Seungjoo Nah, Heegeun Jeong, Bumsuk Kim, Sangil Jung, Jesuk Lee, Yitae Kim, Chang-Rok Moon, and Yongin Park presents the company's latest generation sensor:

"A 0.8 µm-pitch 64 megapixels ultra high resolution CMOS image sensor has been demonstrated for mobile applications for the first time. Full-well capacity (FWC) of 6k e- was achieved in 0.8 µm pixels as the best in the world, and the advanced color filter (CF) isolation technology was introduced to overcome sensitivity degradation. Dual conversion gain (CG) technology was also first applied to mobile applications to improve the FWC performance of Tetracell up to 12k e-. In addition, highly refined deep trench isolation (DTI) and photodiode design significantly improved dark noise characteristics."

from: https://image-sensors-world.blogspot.com/2019/10/iedm-2019-sony-presents-48mp-all-pixel.html

AM - ISOTDAQ - 2020

# Topics

- Motivations

- What is microelectronics ?

- Trends and upcoming limitations

- What can you do with microelectronics ?

- Take home message

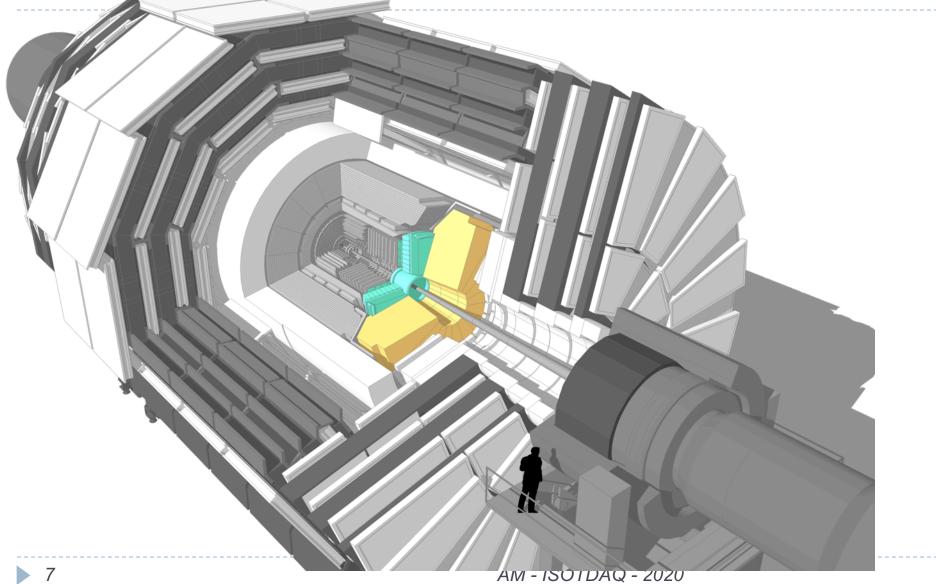

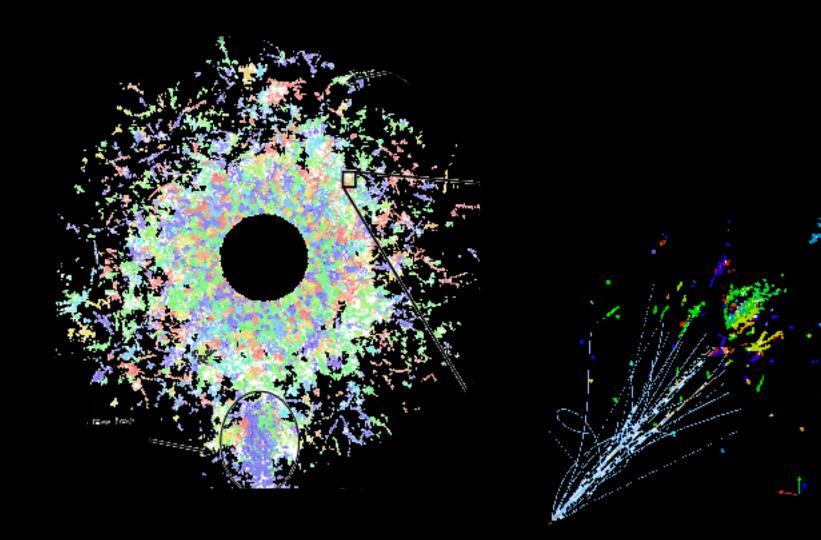

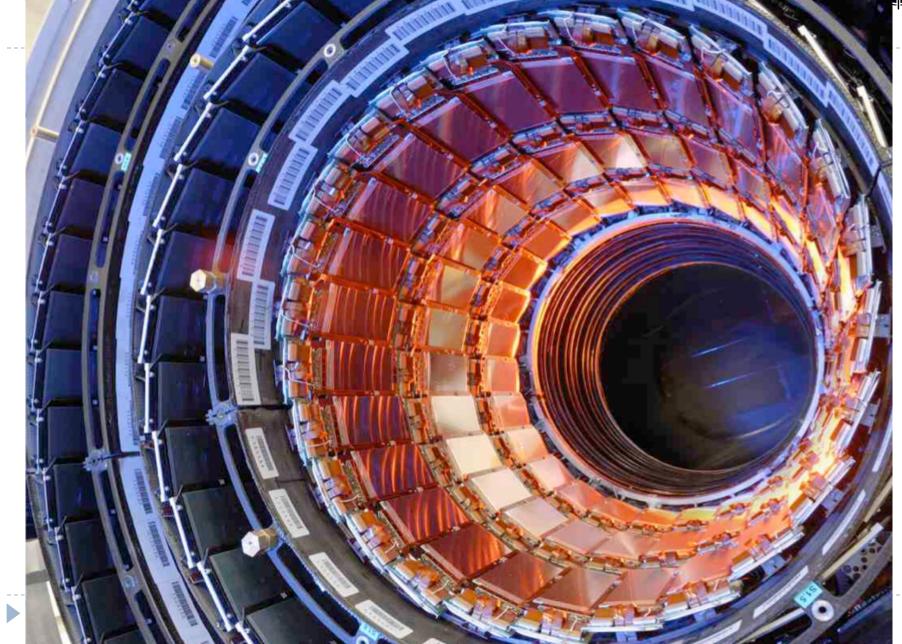

# This detector contains ~1,000,000 eustom made integrated circuits of about 20 types, some of them collecting signals consisting of a few thousand electrons

# Motivations and Trends in HEP

- Generation 0.1 (1980's) of chips for experiments where essentially integrated custom amplifiers for sensing detector signals

- The LHC 1.0 generation (late '90s) are full multichannel systems to cover large surfaces of silicon detectors and/or large number of calorimeter channels

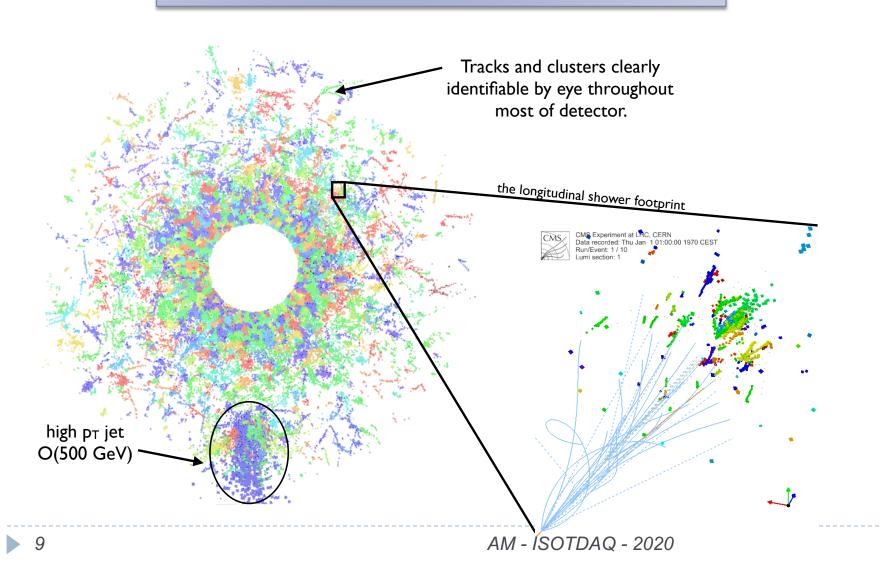

- Pixels and strip electronics are essentially position sensitive detector with little if any high level discrimination capabilities

- Next generation:

- Larger areas at lower cost

- Much improved functionality (meaningful data out, not just DN)

- Digital can help analog (like in so many commercial devices)

- E.g.: simplify tedious calibration and stability monitoring tasks

- ► Embedded processing: digital filtering, particle discrimination, cluster reduction ...

- Energy and/or momentum (vector)

- □ Timing

- Unique digital functionality

- Example: Associative Memories for Fast track recognition

- Full channel digital signal processing (but physicists need to be educated...)

#### **Microelectronics in HEP**

# **Microelectronics in HEP**

#### Key Parameters:

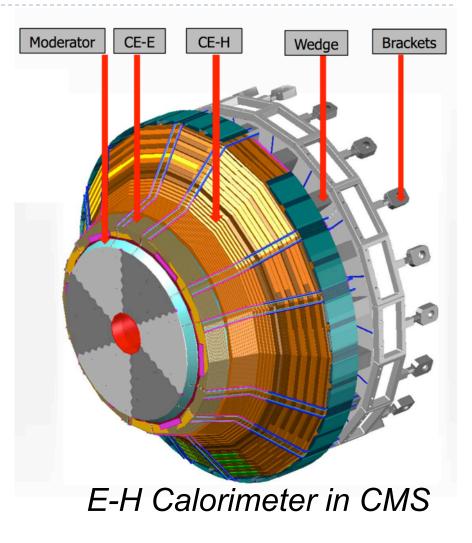

- CMS-HGCAL covers  $1.5 < \eta < 3.0$

- Full system maintained at -30°C

- ~600m<sup>2</sup> of silicon sensors

- ~500m<sup>2</sup> of scintillators

- 6M Si channels, 100K custom chips:

- 0.5 / 1.1 cm<sup>2</sup> cell size

- ~27000 Si modules

- 30 x 6 10<sup>6</sup> x 40 10<sup>6</sup> = 7.2 10<sup>15</sup> bits/sec

- ~16 bit dynamic range

- 220 KW

## **Electronic Camera**

#### Simulation of HL-LHC pileup events in CMS

#### **Electronic Camera**

### Extra wishes

#### What is microelectronics?

And why is digital important

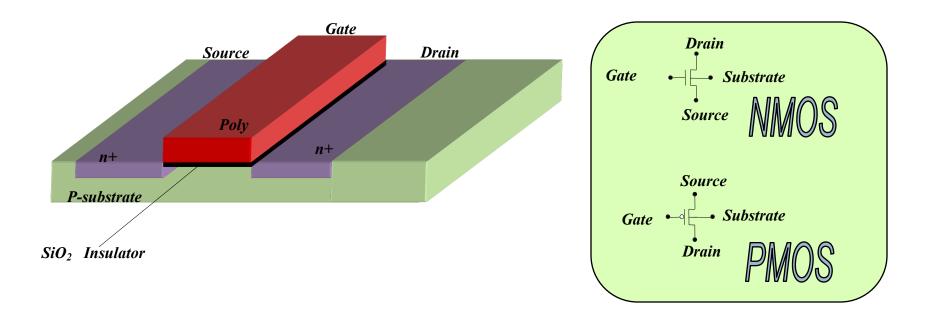

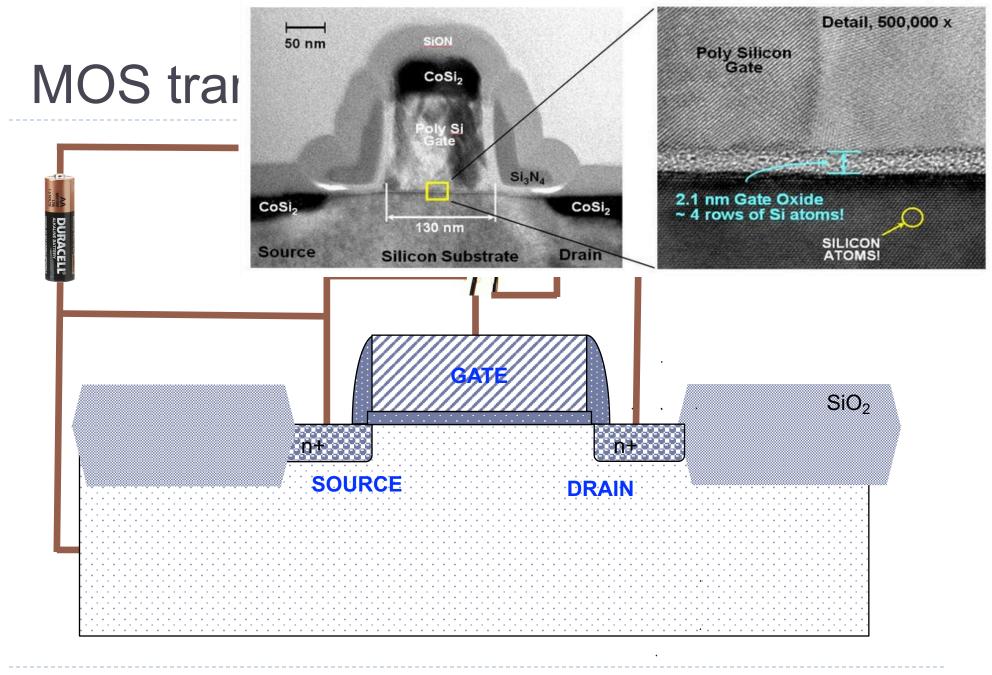

# What is microelectronics?

Combination of two factors

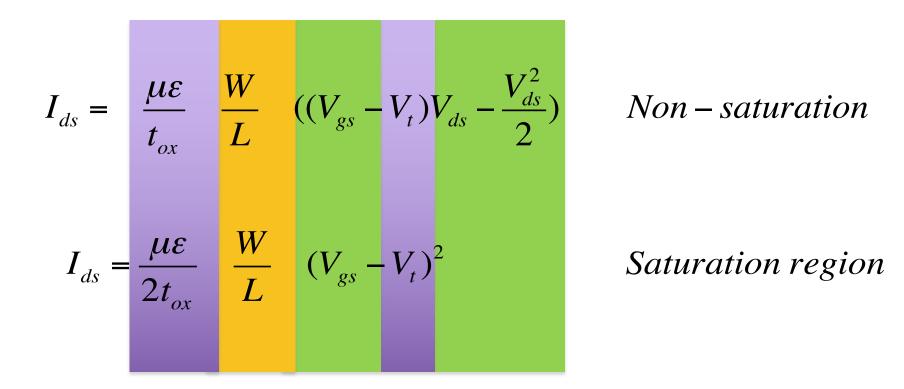

#### Technology

- Capability to "print" on a piece of silicon of about 1 cm<sup>2</sup> some 10<sup>9</sup>-10<sup>11</sup> transistors (working mostly as "switches") of size < 10 nm, each one of which has to work perfectly for 10+ years</p>

- repeat the above for ~100M pieces

- ... and then sell them for O(10\$) / pc.

#### • Tools

Capability to manage the design and the fabrication of these extremely complex systems-on-chip designed by teams of 100+ engineers

#### What do we want from a transistor anyway? (sorry analog engineers...)

- A transistor (a digital transistor) is a device that "should" have the following characteristics:

- works as a switch (on or off), if bi-directional it is even better

- htree terminals: an input, an output, a control

- makes a "sharp" transition between the two states (open or closed) in a time as short as possible (i.e. carry charge quickly through it)

- no leakage current when off (I<sub>on</sub>/I<sub>off</sub> >(>) 10<sup>6</sup>)

- ... while delivering high current when on (drive strongly the load),

I<sub>on,min</sub> ~ 1mA/um

- the control terminal induces a transition between the two states with a voltage drive ( $V_{tr}$ ) as small as possible: P =  $\frac{1}{2}$  C V<sub>dd</sub><sup>2</sup> (today V<sub>tr</sub> ~ 1/3 V<sub>dd</sub>)

- the control terminal should not be influenced by input/output terminal(s)

- be physically small (otherwise other "parasitics" ruin the party)

- must have complementary type (i.e. a second type which is turned on when the first is turned off using the same "control").

- "Good analog" characteristics are desirable but by far not necessary or even important for the the majority of applications.

- In fact modern deep-submicron devices have "horrible" analog characteristics and analog designers have a very hard time to achieve what was "easy" 20 years ago

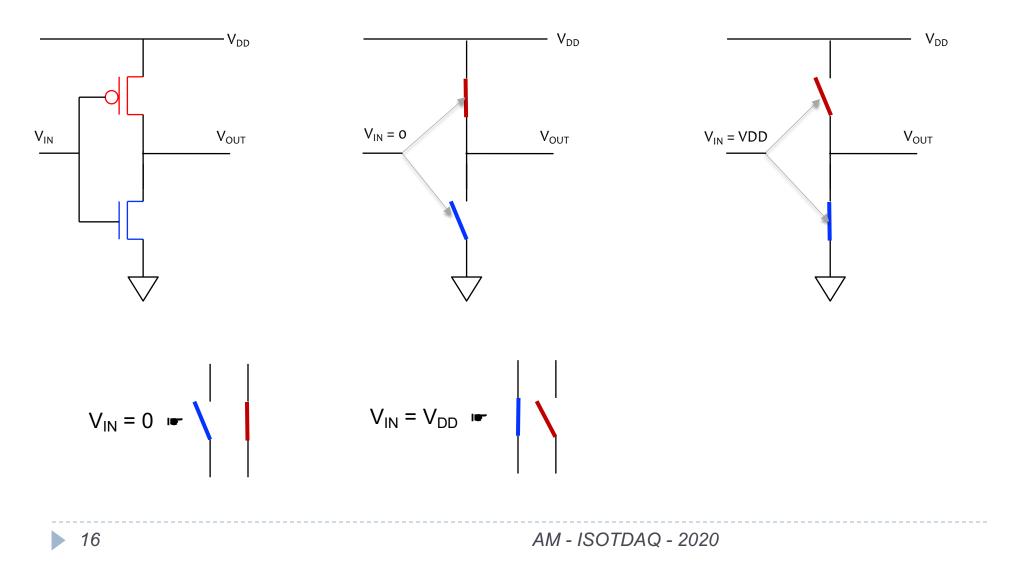

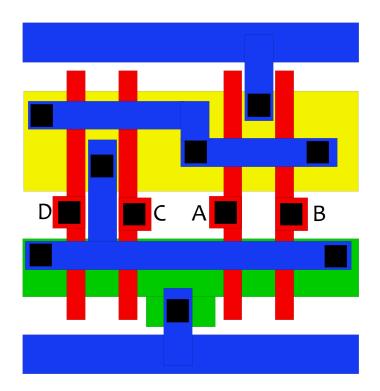

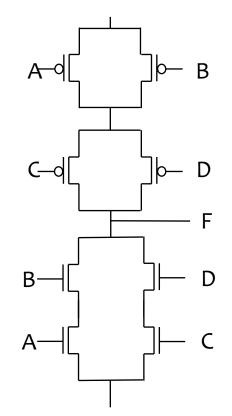

### Simple Inverter Gate

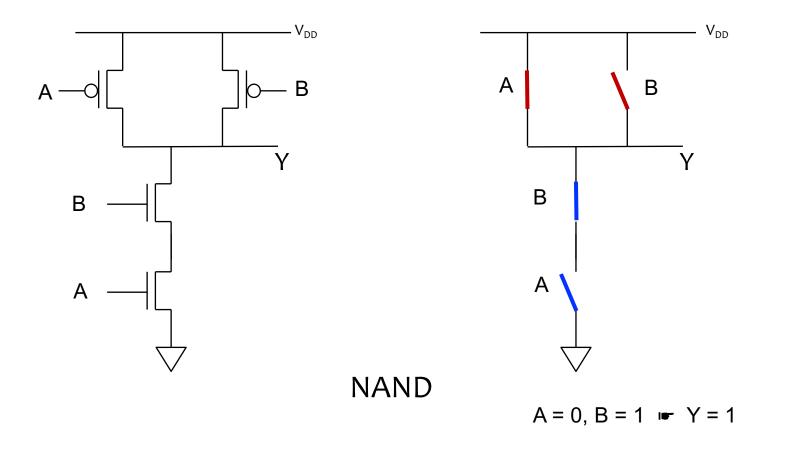

## Simple NAND Gate

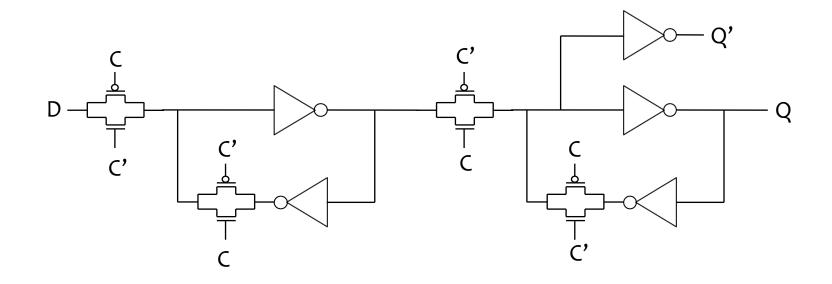

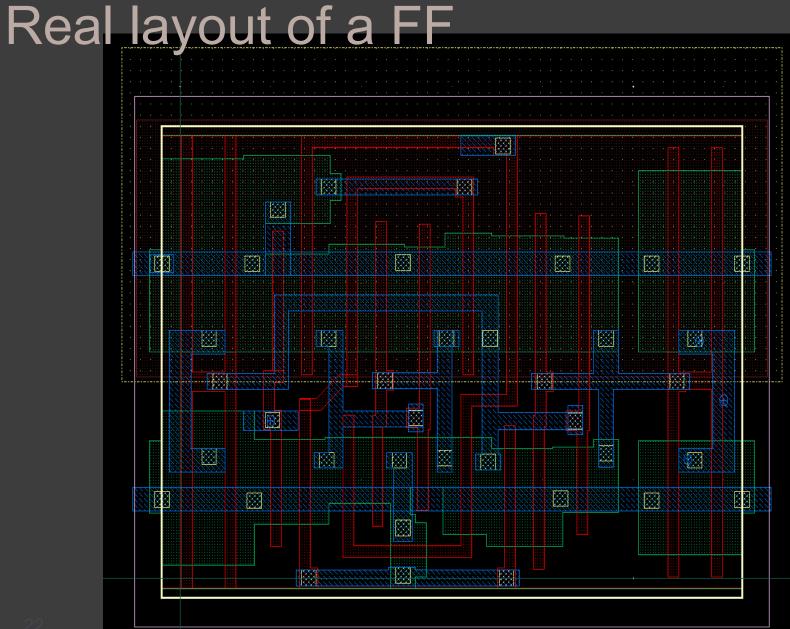

#### **Flip-Flop Memory Element**

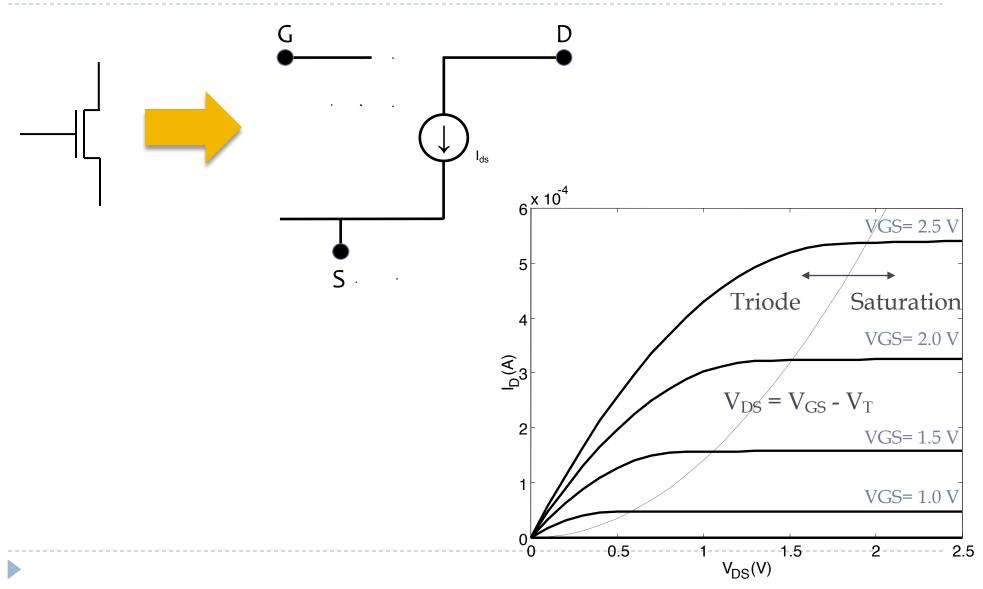

#### **MOS transistors**

## Simplified layout of a logic gate

### MOS (very) simple model

### **MOS Transistor equations**

Manufacturing parameters can't be changed on a giver perchology cuit behavior

Photogra

#### Technology Behind Samsung's \$116 Billion Bid for Chip Supremacy

By Sohee Kim

25

December 23, 2019, 1:50 AM GMT+1

|  | Custom cl | hips are the | future that | Samsung wa | ants to profit fro | m |

|--|-----------|--------------|-------------|------------|--------------------|---|

|--|-----------|--------------|-------------|------------|--------------------|---|

► Laying the foundation for expanding its semiconductor empire

LIVE ON BLOOMBERG

Watch Live TV >

Listen to Live Radio >

Bloomberg Television

How one Taiwanese firm uses unrivalled technology to dominate the world's chip-making industry

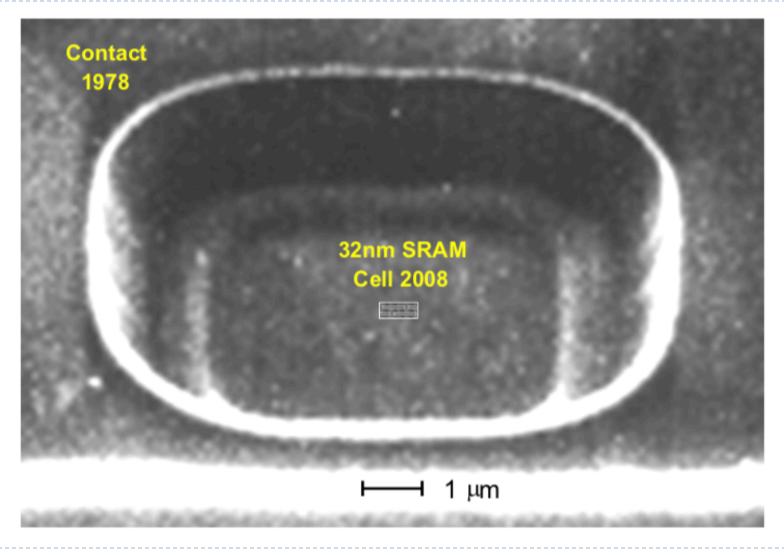

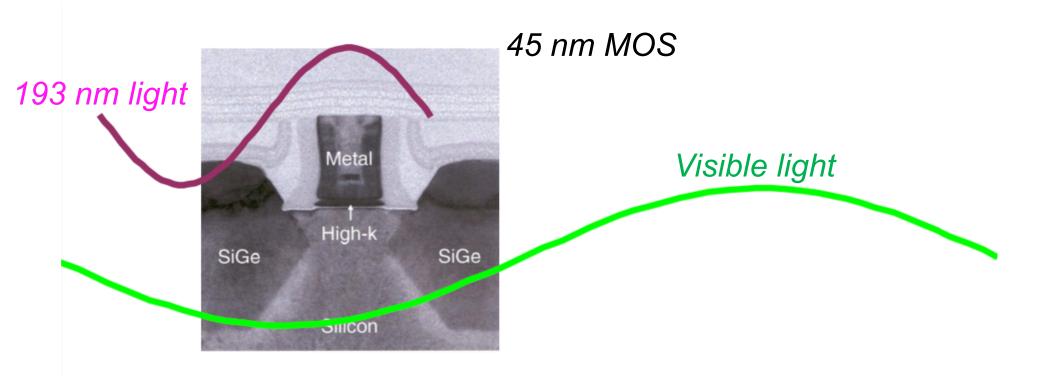

# One of the difficulties: Lithography

# Lithography (2)

# Lithography (3)

# Lithography (4)

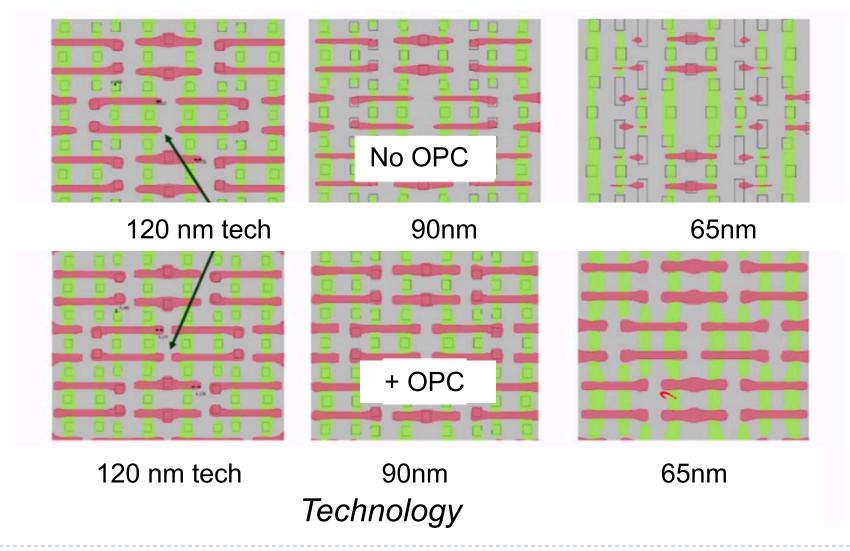

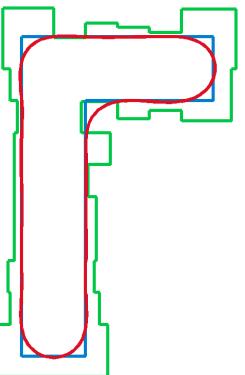

Optical Proximity Correction Techniques (Computational Lithography)

# Lithography (5)

65 nm-WIDE - 0.57  $\mu m^2$

45nm – WIDE w/ patterning enhancement 0.346 μm<sup>2</sup>

90nm – TALL 1.0 μm²

AM - ISOTDAQ - 2020

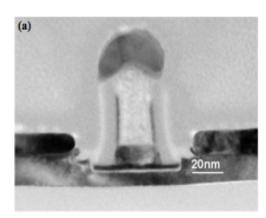

#### Some advanced devices

20 nm FDSOI from ST

22 nm TriGate from Intel

28 nm planar from TSMC

31

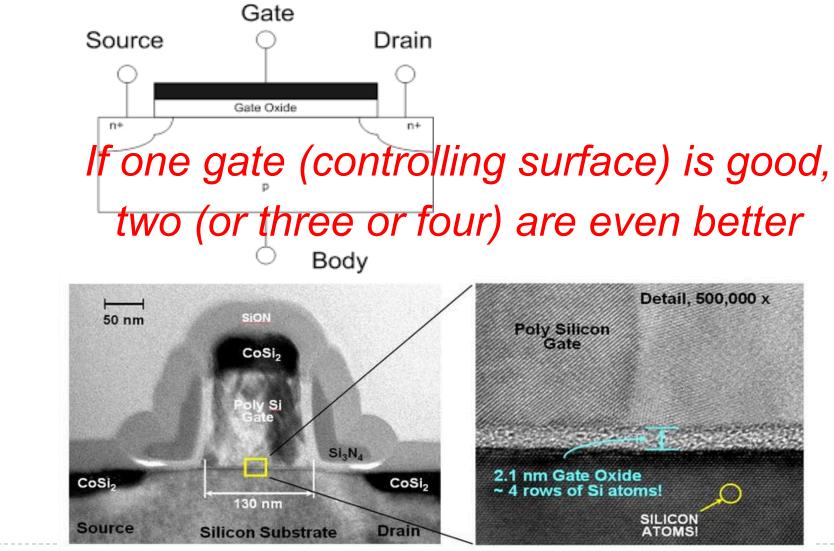

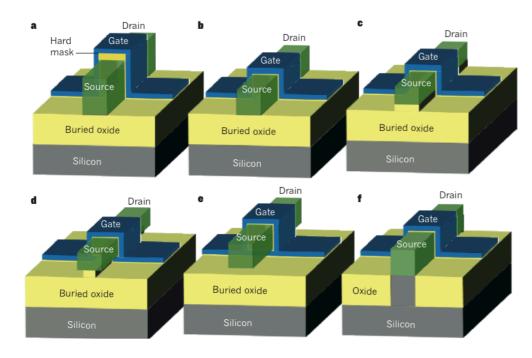

## Multi-gate devices

AM - ISOTDAQ - 2020

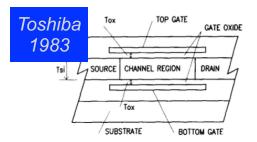

#### CALCULATED THRESHOLD-VOLTAGE CHARACTERISTICS OF AN XMOS TRANSISTOR HAVING AN ADDITIONAL BOTTOM GATE

(Received 30 May 1983; in revised form 24 August 1983)

Fig. 1. Schematic cross-sectional structure of an XMOS transistor having an additional bottom gate which is symmetrically placed to a top gate with a channel region between them. "X" originates from Greek capital letter of xi as this structure resembles its shape.

Electronic Device Division. Electrotechnical Laboratory, Sakura-mura. Ibaraki, 305. Japan

33

T. SEKIGAWA and Υ. ΗΛΥΛ5ΗΙ

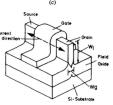

Digh Hisamoto, Member, IEEE, Toru Kaga, Member, IEEE, and Eiji Takeda, Senior Member, IEEE

is required. Moreover, it is evident that these structures Abstract-A fully depleted lean channel transistor (DELTA) with its gate incorporated into a new vertical ultra-thin SOI are difficult to contact to the substrate, and thus suffer from structure is presented. In the deep-submicrometer region, se-lective oxidation produces and isolates an ultra-thin SOI MOSa substrate floating effect. FET that has high crystalline quality, as good as that of con-ventional bulk single-crystal devices. Experiments and threedimensional simulations have shown that this new gate structure has effective channel control, and that the vertical ultrathin SOI structure provides superior device characteristics: reduction in short-channel effects, minimized subthreshold swing, and high transconductance. Hitachi 1989

-Si3Ne

Si-Sub

(a)

(d) g. 1. (a)-(c) Process flow of selective oxidation. (d) Schematic cross section of DELTA.

2320

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 47, NO. 12, DECEMBER 2000

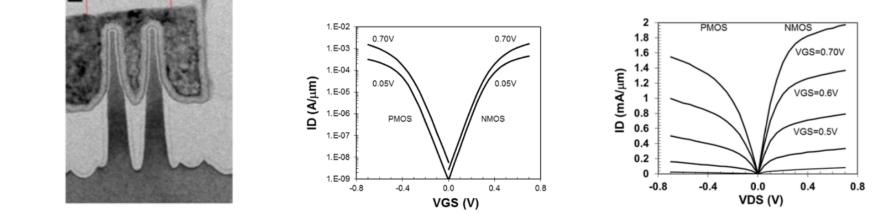

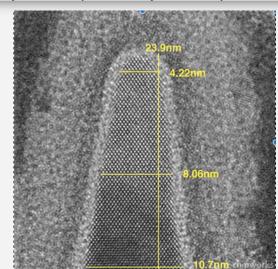

#### FinFET—A Self-Aligned Double-Gate MOSFET Scalable to 20 nm

Digh Hisamoto, Member, IEEE, Wen-Chin Lee, Jakub Kedzierski, Hideki Takeuchi, Kazuya Asano, Member, IEEE, Charles Kuo, Erik Anderson, Tsu-Jae King, Jeffrey Bokor, Fellow, IEEE, and Chenming Hu, Fellow, IEEE

Abstract-MOSFETs with gate length down to 17 nm are reported. To suppress the short channel effect, a novel self-aligned double-gate MOSFET, FinFET, is proposed. By using boron-doped Si0.4 Ge0.6 as a gate material, the desired threshold voltage was achieved for the ultrathin body device. The quasiplanar nature of this new variant of the vertical double-gate MOSFETs can be fabricated relatively easily using the conventional planar MOSFET process technologies.

Berkely

2000

Index Terms-Fully depleted SOI, MOSFET, poly SiGe, shortchannel effect.

I. INTRODUCTION

O DEVELOP sub-50-nm MOSFETs, the double-gate Fig. 1. FinFET typical layout and schematic cross sectional structures. structure has been widely studied. This is because

AM - ISOTDAQ - 2020

Figure 1: Schematic views of the double-gate SOI MOSFET's.

## Multi-gate devices

- Intel: Tri-gate

- TSMC, GF, Samsung: Finfets

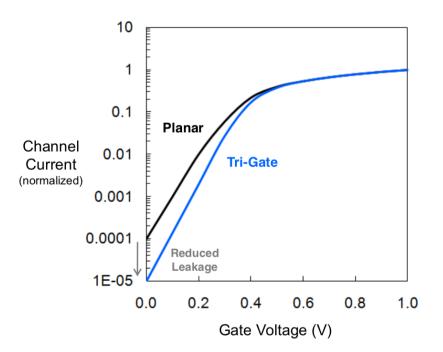

## Subthreshold slope improvement

**Transistor Operation**

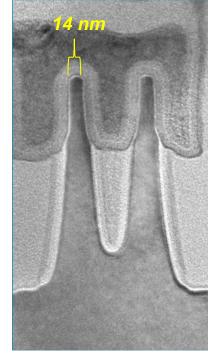

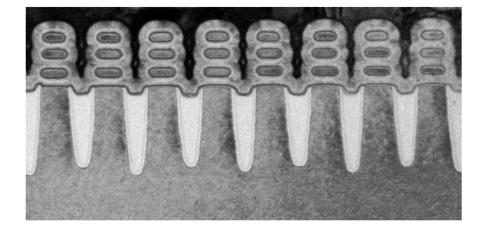

#### 10 nm Finfet

36

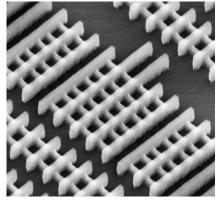

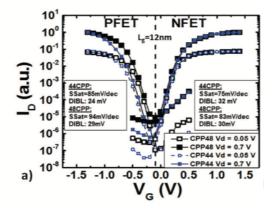

### State of the Art examples: FINFETs

Source: TSMC

AM - ISOTDAQ - 2020

Source: Intel

# Typical FinFET dimensions

#### From the ITRS 2011 report

| Year of Production          | 2013 | 2015 | 2017 | 2019 | 2021 | 2023 | 2025 | 2028 |

|-----------------------------|------|------|------|------|------|------|------|------|

| FinFET Fin Width (new) (nm) | 7.6  | 7.2  | 6.8  | 6.4  | 6.1  | 5.7  | 5.4  | 5.0  |

#### FINFET++ = GateAllAround (GAA)

39

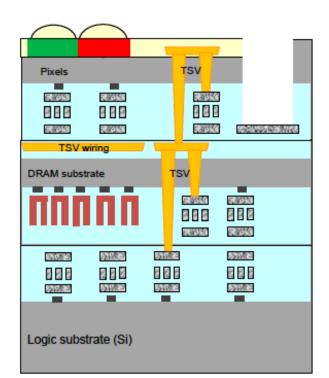

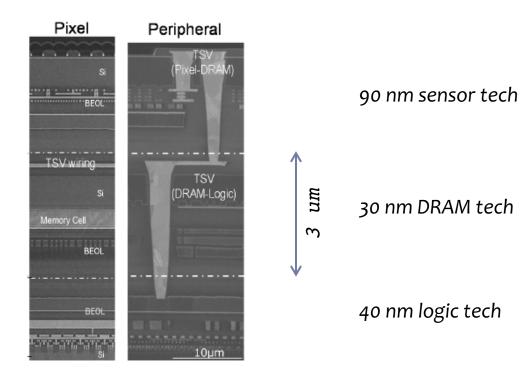

### 3D technology

How to consume less energy in computation

#### Less energy per computation

- Power consumption in digital circuits is determined by three factors:

- 1. The energy necessary to charge/discharge the input of the next level of logic and the interconnecting wire

- 2. The energy wasted by the switching device because of simultaneous conductance of the NMOS and PMOS devices during a transition

- 3. The energy wasted by leakage currents through the transistors (the switches are unfortunately not *"ideal"*) even in static conditions

$$P = \frac{1}{2} C V_{dd}^2 \alpha f + I_{leak} V_{dd} + \Delta \tau_{sw} I_{sc} V_{dd}$$

- *V<sub>dd</sub>*: *supply voltage*

- *α*: *activity factor*

- C: load capacitance

- *f*: *switching frequency*

- *I*<sub>leak</sub>: leakage current

- *I<sub>sc</sub>*: *short circuit current*

- $\Delta \tau_{sw}$ : fraction of time in sc mode

# Improving in energy saving

- Make devices smaller:

- C decreases

- ... but up to a point as the interconnect C becomes rapidly dominant and actually starts to increase

- V<sub>dd</sub> decreases

- ... but also up to a point, as threshold voltage behavior is limited by intrinsic physics and not by technology

- Something drastic is required to save energy!

# Any better transistor?

Today's devices make transitions around their threshold voltages which are determined by some fundamental physics related to the Boltzmann constant. Such devices require at least an input voltage change of 60 mV to increase their current by a factor of 10.

Devices with "very steep" transition regions between the OFF and the ON states are being researched, among these:

- 1. "Ferroelectric" (negative capacitance) transistors

- 2. Tunnel transistors

- 3. ...

If available in the coming years these would lead to supply voltages in the 100-200 mV region and a power saving of about one order of magnitude

# Who is more important: Transistors or wires?

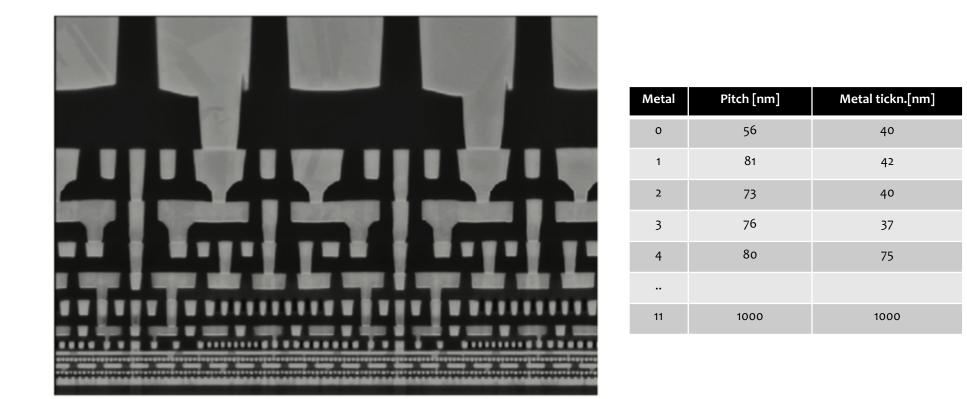

#### A 14 nm FINFET process metal stack

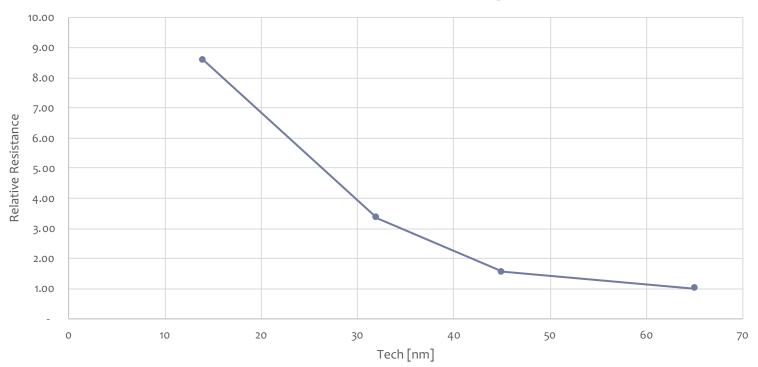

# Wire resistance in "classical" scaling

Resistance for Classic M1 scaling

*AM - ISOTDAQ - 2020*

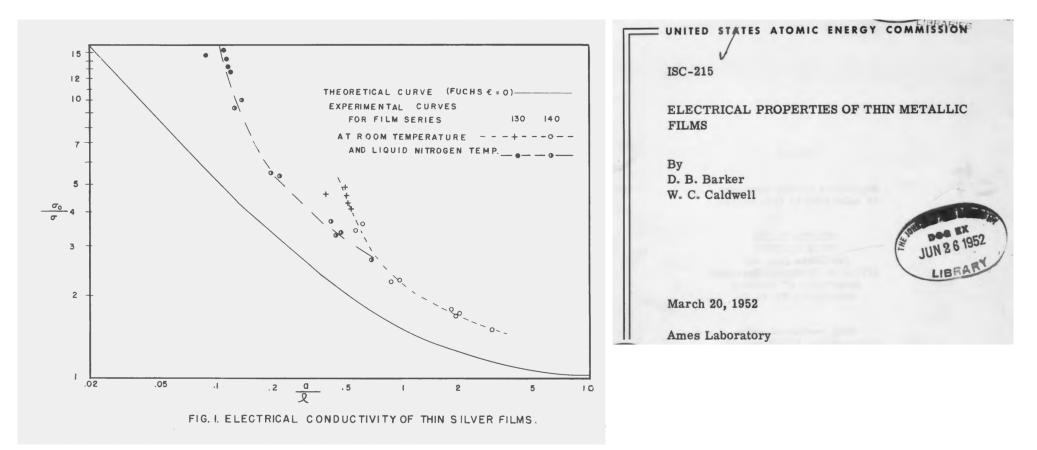

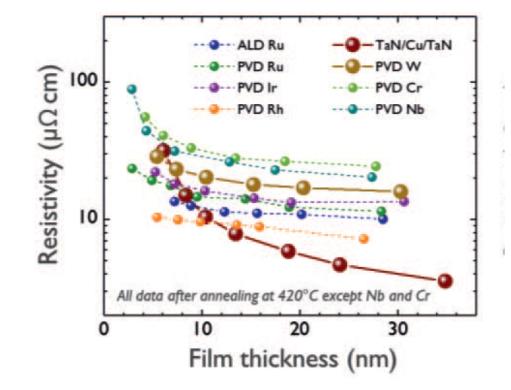

#### Ultra-scaled metals

# Ultra-scaled metals (2)

# Summary on technologies

- Moore's Law worked for more than 50 years with spectacular results

- But fundamental limitations are being encountered in many areas

- Thinness of materials

- Leakage currents

- Resistances (and Line Edge Roughness)

- Complexity of fabrication

- Physics:

- □ Random dopants distribution

- □ ...

- ...

- Cost of fabrication

- Another factor of 10 possible with 'brute force scaling'?

- Hard to bet, but most likely not possible

- Fundamental research is nevertheless very active to develop new materials that allow switches to be built through new phenomena

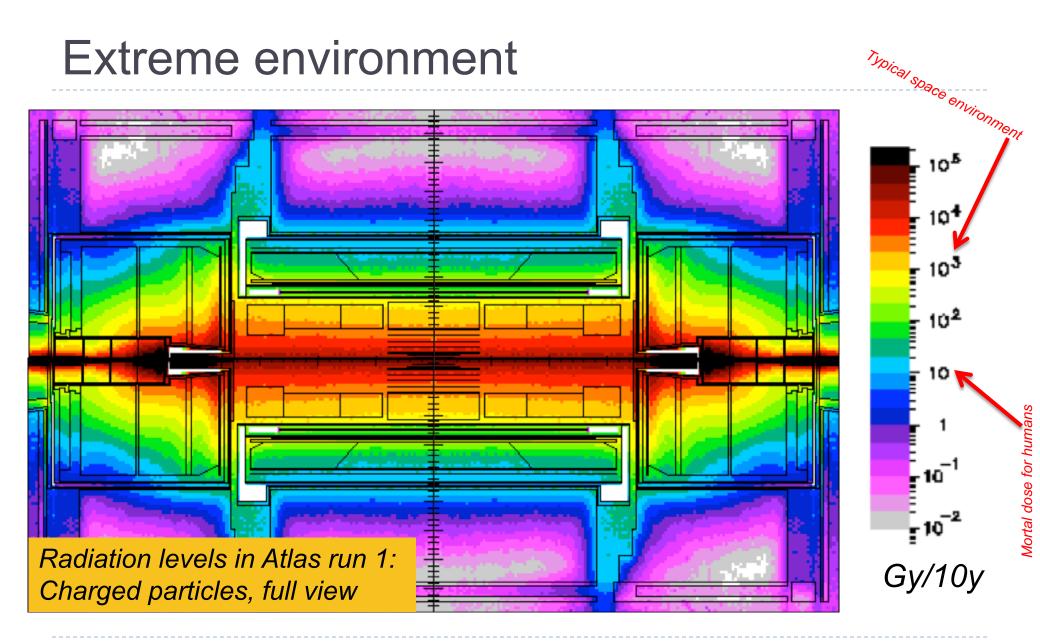

#### Basics on Radiation effects in CMOS

A "Bonus" or a "Miracle" ?

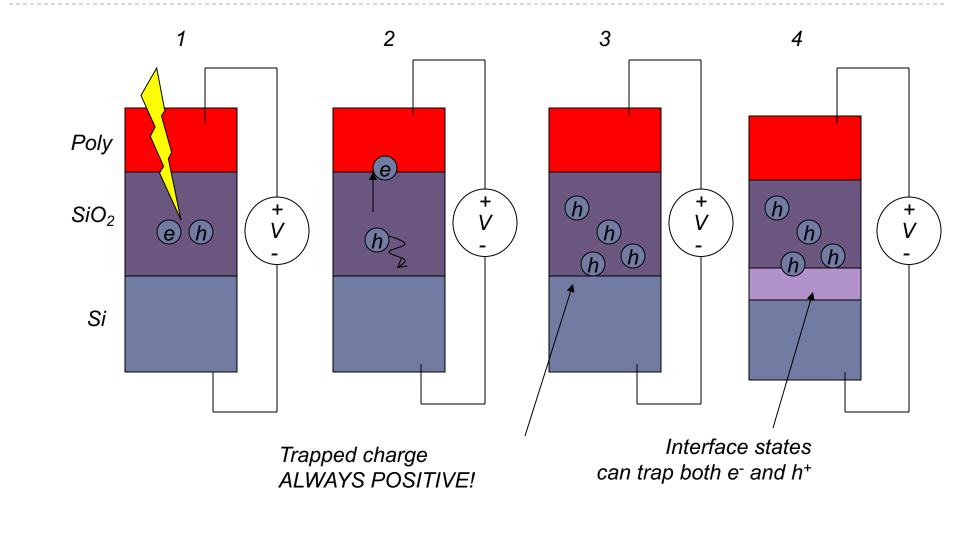

#### Ionizing particles in oxides (simple version)

# Consequences of trapped charge

- Charges on gate oxides:

- Threshold Voltage of NMOS becomes lower

- NMOS Devices are more difficult (or impossible) to turn off

- Threshold Voltage shift (and therefore matching between devices) depends on biasing conditions!

- Leakage current increases

- Threshold Voltage of PMOS becomes higher

- Devices are more difficult to turn on

- Leakage decreases but drive current decreases too

- Threshold Voltage shift (and therefore matching between devices) depends on biasing conditions!

- Charges in field oxides

- Field transistors:

- If field oxide gets heavily charged parasitic transistors can be formed "between" otherwise isolated diffusion areas (i.e. normally isolated regions such as sources and drains of different devices) causing very significant problems.

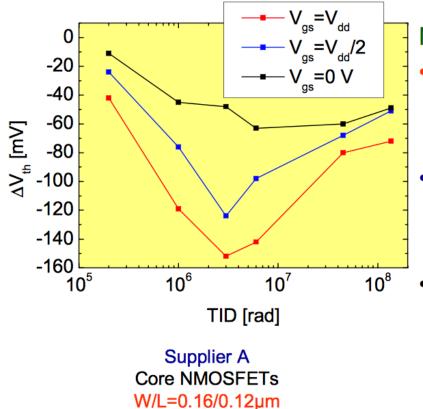

### Bias dependence of $\Delta V_{th}$

Minimum-Size NMOSFETs Worst condition:  $-V_{gs} = V_{dd}$  $-\Delta V_{\text{th.max}}$ =-150 mV Intermediate condition •  $-V_{gs} = V_{dd}/2$  $-\Delta V_{\text{th max}}$ =-120 mV **Best condition** •  $-V_{qs} = 0 V$  $- \Delta V_{\text{th.max}}$ =-60mV

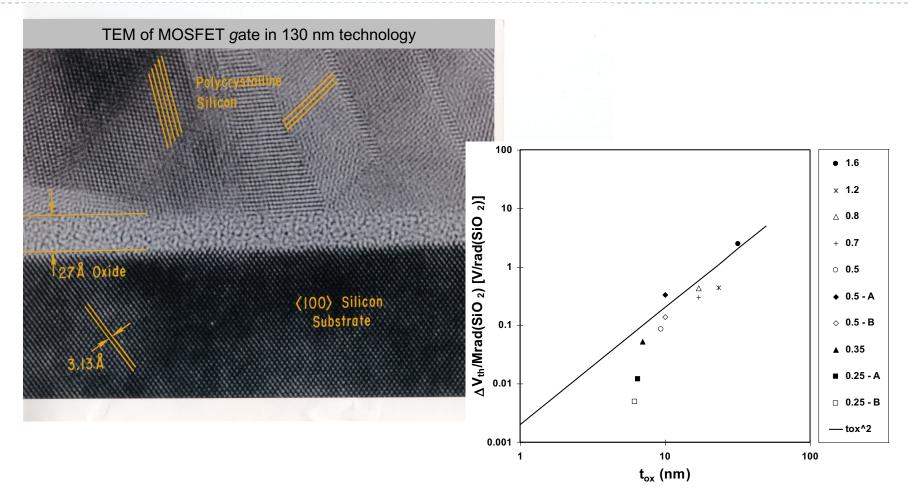

#### Charge trapped in gate oxides: DSM helps!

N.S. Saks et al., IEEE TNS, Dec. 1984 and Dec. 1986

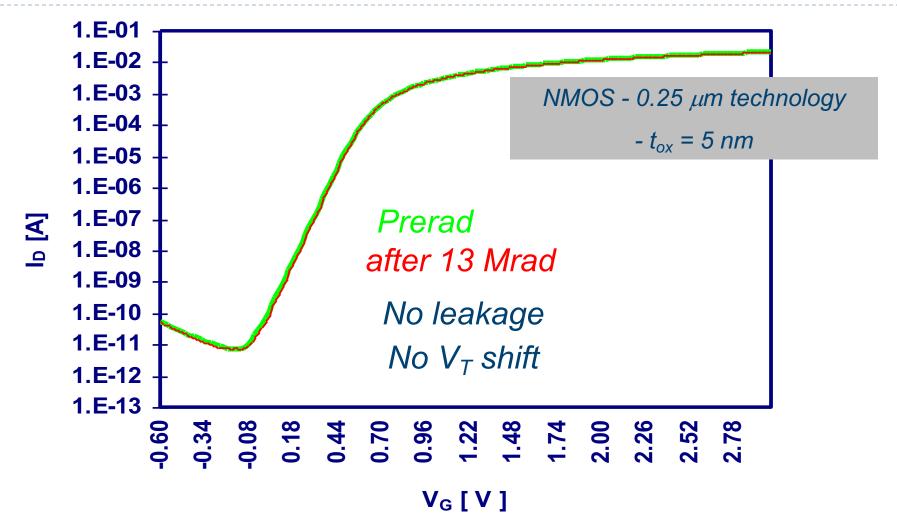

#### More modern tech, with ELT

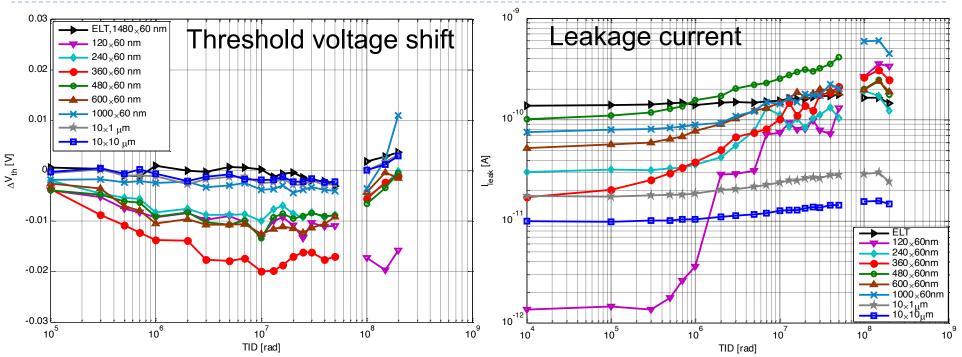

### Irradiation of 65nm technology

- Up to ~20mV shift for 200 Mrad

- Some rebound effect visible for narrow devices

- in 130nm: was 150mV

- At high doses Vth shift is positive for wide devices, negative for narrow devices

- STI edge oxide traps considerable charge (RINCE)

- Subtreshold slope does not change significantly

Less than 10 × increase in leakage for wide devices (W > 360nm)

Narrow devices have up to 2.5 orders of magnitude increase

- In 130nm:

- All devices are peaking at ~100nA

- Narrow devices increase leakage by 3 orders of magnitude

- ▶ I<sub>leak</sub> is ~1nA @136 Mrad

A. Marchioro / CERN

# Short summary on rad effects in CMOS<sup>(\*)</sup>

- "Fortunately" commercial CMOS introduced "thin-oxide" gates at the time when LHC instruments were being designed for the 1-100 MRad regime.

- If the CMOS development had been late by say 10 years, none knows what would have happened to LHC experiments.

(\*) Valid up to ~100 MRad, beyond this point matters become again complicated

#### Lesson learned

If you are working on a project for post-LHC HEP (and your experiment is very ambitious with radiation levels), beware of radiation effects, as another lucky coincidence may not be on the books!

#### Conclusions

- Powerful technologies and tools are here today, you have to invent how to use them to create new instruments.

- Introduction of local computation (i.e. intelligence) needs two essential ingredients:

- Low power microelectronics engineering (i.e. a commercial technology)

- and imagination (i.e. YOU)

- If you are at this school, you have already developed a sense of gratification and pleasure by "creating"

- new systems (for system designers)

- programs (if you mainly use "computers")

- new logic functionality (FPGA designers).

- ASIC design can add a new dimension of "creativity" to your bag of tools.