## **Trends in Electronic Packaging Technology**

Thomas Fritzsch, Fraunhofer IZM, Berlin

The Tenth International Workshop on Semiconductor Pixel Detectors for Particles and Imaging

## **Electronic Packaging**

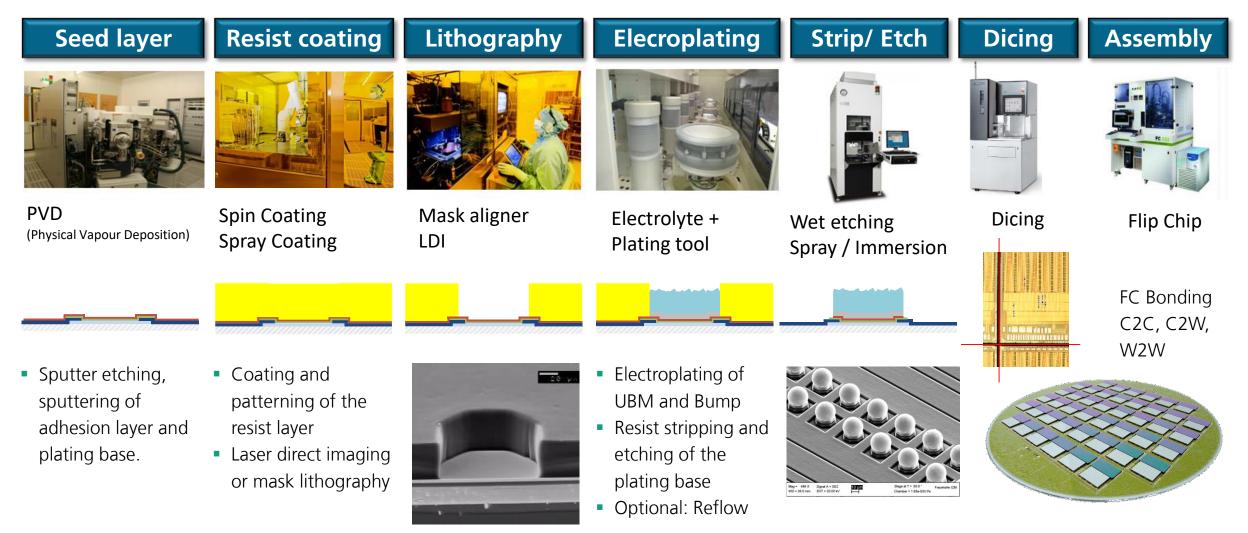

## Wafer Level Packaging: Micro Bumping and Hybridization Process

General process flow

## Outline

- Status Hybrid Pixel Detectors

- > New Developments

- > Trends in Advanced Electronic Packaging

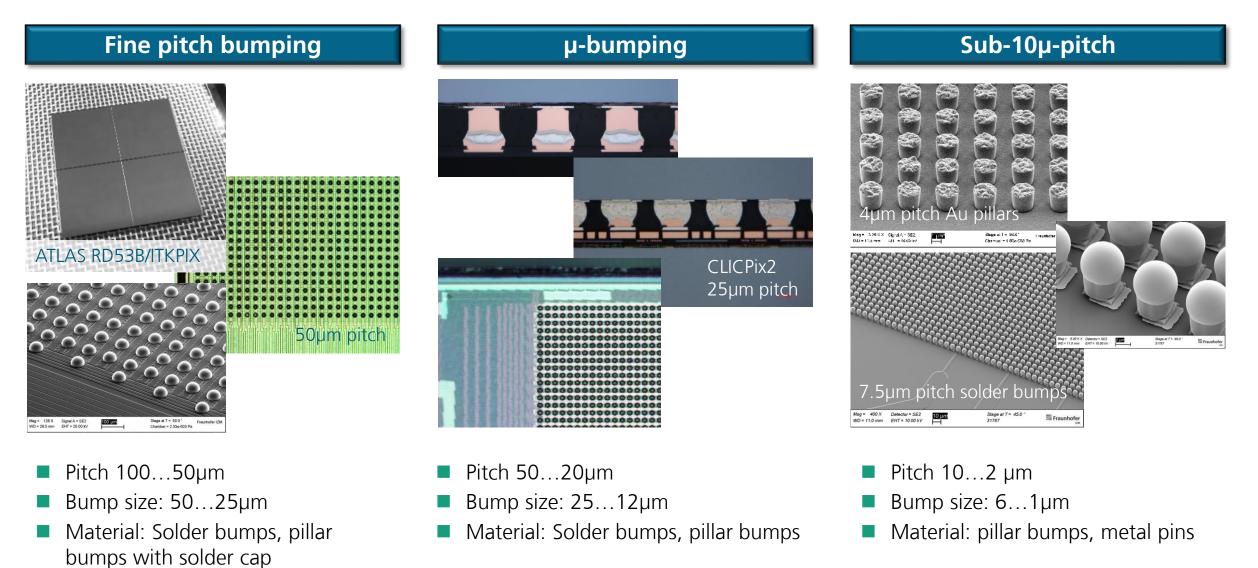

## **Flip Chip Assembly Parameter - Interconnection Pitch**

Pixel 2022 - The 10th International Workshop on Semiconductor Pixel Detectors for Particles and Imaging

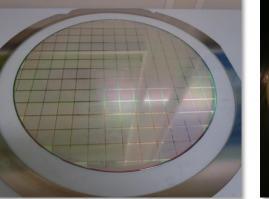

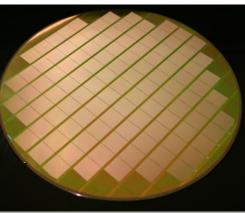

## **Process Line Parameter – Wafer Size**

#### 300mm (12")

- 65nm technology

- ATLAS ITKPix/CMS CROC/ TIMEPIX4

- pitch 50x50 µm<sup>2</sup>, ~20 Mio.

bumps/w (RD53B)

- thin wafer handling ( $\leq 150\mu$ m)

- 3D TSV processing

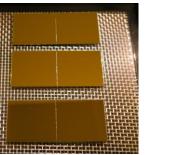

#### 200mm (8")

- 180/130/65 nm technology

- Readout: ATLAS FE-I4, MEDIPIX3, TIMEPIX3, ePIX10k,...

- Sensor: CMOS, DMAPS

- pitch 55x55 µm<sup>2</sup>, ~6 Mio. Bumps/w (MEDIPIX3)

- thin wafer handling ( $\leq 100 \mu m$ )

- 3D TSV process

#### 150mm / 100mm (6" / 4")

- Planar, 3D sensor technology

- Bumping/UBM deposition process: electroplating, e-less (NiAu), PVD

- Thin Wafer Handling: 150μm ... 50μm

#### 4"/ 3" III-V-compound semiconductor

■ GaAs, CdTe, CdZnTe, InGaAs

#### Single chip

- 65nm/28nm readout chips from MPW

- diced sensor (i.e. 3D diamond)

TIMESPOT ASIC with 3D diamond sensor, both chips processed at single die level

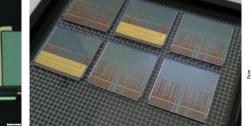

300mm RD53B/ITKPix ROIC wafer with solder bumps

200mm MEDIPIX3 Wafer with solder bumps

14

18

21

25

3

6

24

27

29

2

5

9

12

16

28

28

4

4

11

15

19

28

28

150mm FBK planar sensor wafer, 150µm thickness

## **Fabrication Volume: Production Level**

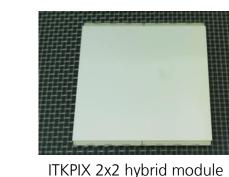

CERN ATLAS/CMS ITK Pixel Detector Upgrade

- ITK detector upgrades using hybrid modules with 50x50µm<sup>2</sup> bumping pitch

- Assembly of 1-chip, 2x1-chip and 2x2-chip hybrid modules:

- 6" planar sensors: 100µm, 150µm thickness

- 4"/6" 3D sensor wafer: 250µm thickness

- 8" CMOS sensor wafer: 150µm thickness

- Readout chip size:

- 300 mm RD53B (ITKPIX) wafer chip size ~21x20mm<sup>2</sup>; thickness 150µm

- 300 mm CROC wafer н. chip size ~22x19mm<sup>2</sup>; thickness 150µm

- ITK Detector Upgrade:

- i.e. ATLAS ITK Pixel: ~10,000 4-chip + 2,150 1-chip modules

CMS collaboration https://cms.cern/collaboration

CROC 2x1 hybrid modules

ITKPIX 2x2 hybrid module

ITKPIX 1x1 hybrid modules

CROC 2x2 hybrid modules

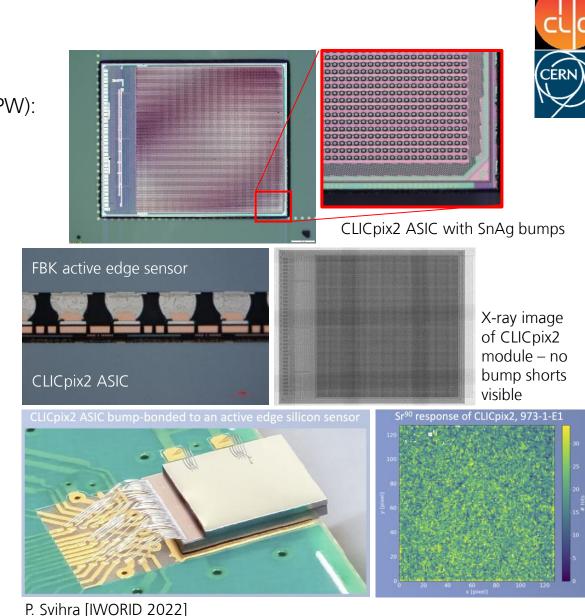

## **Fabrication Volume: Prototyping Level** CLICpix2 - 25µm Pitch Single Chip Bumping

- Single Chip bumping of individual die from multi-project wafer (MPW):

- Aligned chip bonding onto carrier wafer

- Bumping process using wafer level process line:

- PVD mask lithography electroplating of UBM/solder bump

- Removal from carrier

- Hybrid module:

- TSMC 65nm CLICpix2 ROC

- Bumping 128x128, 25µm pitch, bump size 12µm

- UBM on FBK active edge sensor:

- Thickness 50μm, 100μm and 130μm

- Connection yield up to 99,9%

- PCB assembly, wire bonding & test done at CERN

#### See also: P. Svihra et al. IWORID 2022

https://doi.org/10.48550/arXiv.2210.02132 arXiv:2210.02132v1 [physics.ins-det] 5 Oct 2022

## Outline

- Status Hybrid Pixel Detectors

- > New Developments

- Trends in Advanced Electronic Packaging

## Hybridization: New Interconnection Methodes for Sub-10µm Pitch

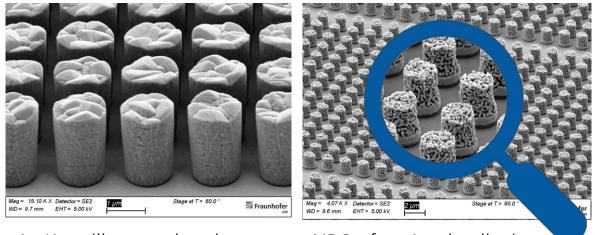

Nano-porous Gold-Pillar-Interconnects

#### Motivation:

- sponge-like metal for I/O bumps with superior compressible behavior

- Bump deformation in z-axis with less spreading in lateral x/y-direction featuring smallest bump space

- Applicability of reduced bonding parameters like temperature and force

#### Features:

- Electro-plating of Au/Ag pillars and de-alloying of Ag results in sponge like Au-bump (nano-porous-gold – NPG)

- Bump size ~2µm, bump pitch 4µm

Au/Ag pillars as plated

NPG after Ag-de-alloying

NPG  $\mu$ -bumps before and after thermo-compression bonding

## **Advanced Bonding Technologies**

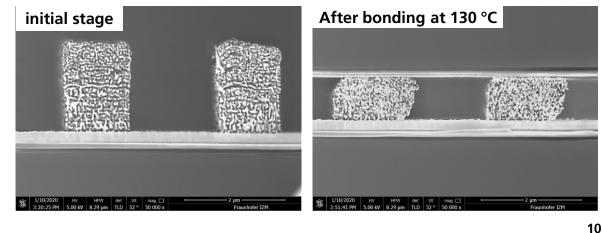

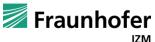

### Metal-Oxide-Hybrid-Bonding

#### **Motivation for DBI**<sup>®</sup>

- W2W , D2W, D2D

- Highest interconnect density: I/O pitch down to 1 µm

- High alignment accuracy

- No bumps, no intermetallics

- No gap no underfilling

- 3D chip stacking: memory chips, CMOS image sensors (CIS)

#### Process

- SiO2 passivation + Cu pads

- Surface planarization (CMP)

- Surface activation (plasma, chemicals)

- Room temperature bond

- Annealing 200 350°C

#### Challenges

- Particle free surface required

- Cu-Oxide surface roughness <1nm</p>

- Cu dishing  $\leq$  5nm

- Delicate die and wafer handling to avoid contamination and particles

- Processes licenced by XPERI/ADEIA:

- DBI-Ultra: D2W HB, DBI: W2W HB

- Zi-Bond: W2W DB

Pixel 2022 - The 10th International Workshop on Semiconductor Pixel Detectors for Particles and Imaging

## **Advanced Bonding Technologies**

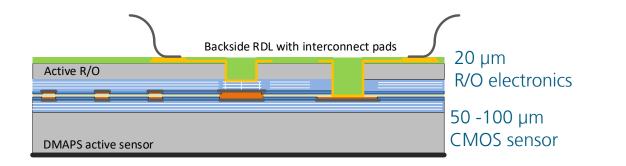

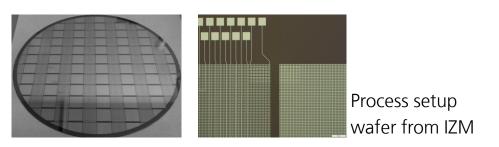

## AIDAinnova: Ultra Thin Hybrid Pixel Detectors

Task 6.4: Wafer to wafer bonding technique Slides: F. Huegging (Bonn), I. Gregor (DESY&Bonn), T. Fritzsch (IZM)

#### Features:

- R/O backside redistribution layer (RDL) with contact pads

- Thinned R/O wafer (i.e. TIMEPIX3) with backside via last interconnection

- Combined polymer metal bonding

- Thin DMAPS sensor with contact pads and backside processing

#### Tasks:

- Fabrication of technology development and characterization wafer by Fraunhofer IZM

- W2W bonding process development by Fraunhofer IZM

- TIMEPIX3 wafer provided by CERN MEDIPIX collaboration

- TIMEPIX3 adapted sensor design by University of Bonn

- 200mm sensor wafer fabricated by Lfoundry

TIMEPIX wafer from CERN

This project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No 101004761.

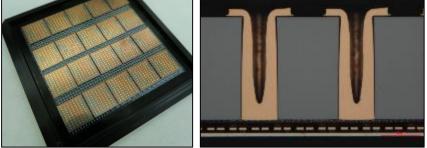

## **3D Integration Technologies**

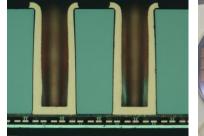

TSV in electronic readout chip wafer – TSV backside via last process

**ATLAS FE-I4**

## TSV Ø60µm, wafer thickness 80µm

ATLAS FE-I4 TSV single chip modules

[JINST 2022: https://doi.org/10.1088/1748-0221/17/01/C01029]

- TSV backside, via last process

- TSV connection to CMOS M1 layer landing pad

- Level 1 assembly: TSV readout chips flip chip bonded onto silicon sensor chip

- Level 2 assembly: module assembly onto PCB and functional test at project partner side: ATLAS/University of Bonn, MEDIPIX3/DESY

- Ongoing projects:

- TSV backside via last process in TIMEPIX4 wafer with CERN/MEDIPIX collaboration

Source scan: Sr90, 60s, 60V

- Current status: TSV metallization process ongoing

- MEDIPIX3 TSV projects with industry partners

TSV Ø40µm, wafer

[2017 JINST 12 C12042]

thickness 100µm

MEDIPIX3 TSV wafer view onto BS-RDL

PCB sample imaged with X-ray tube, Mo target, 51 kV

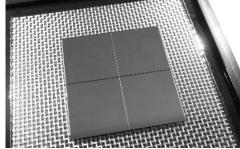

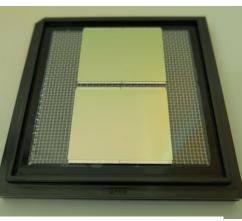

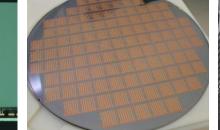

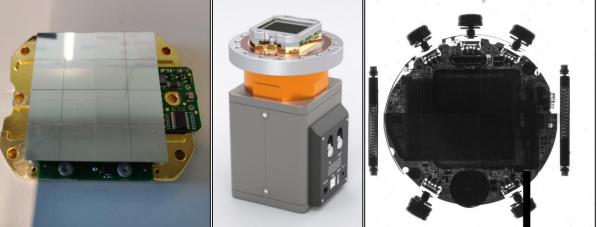

## **MEDIPIX3 TSV based 1MPix Electron Microscope Camera**

Project: Amsterdam Scientific Instruments – MEDIPIX3 TSV Process and Module Assembly

#### **Project Goal**

- Development and fabrication of MEDIPIX3 X-ray camera with TSV

- 1MPix gap-less camera image by combination of MEDIPIX TSV chips and edgeless silicon sensor chips

#### Contribution of the Fraunhofer IZM

- TSV backside via last process at IZM using MEDIPIX3 readout chip wafer

- Flip Chip Assembly onto Si-pixel sensor chips with SnAg bumps

- Level2-Assembly onto connector substrate

#### **ASI: 1MPix Electron Microscope Camera Features**

- 1024x1024 pixels full detector area (56 x 56mm<sup>2</sup>)

- 4x4 single MPX3 TSV modules assembled without gaps

- 300 µm edgeless silicon sensor (200 kV electron microscope)

- Fits on CF100 standard flange for mounting in a TEM

IZM

MEDIPIX3 chips after TSV process

1MPix camera assembled at ASI and x-ray test image of a watch

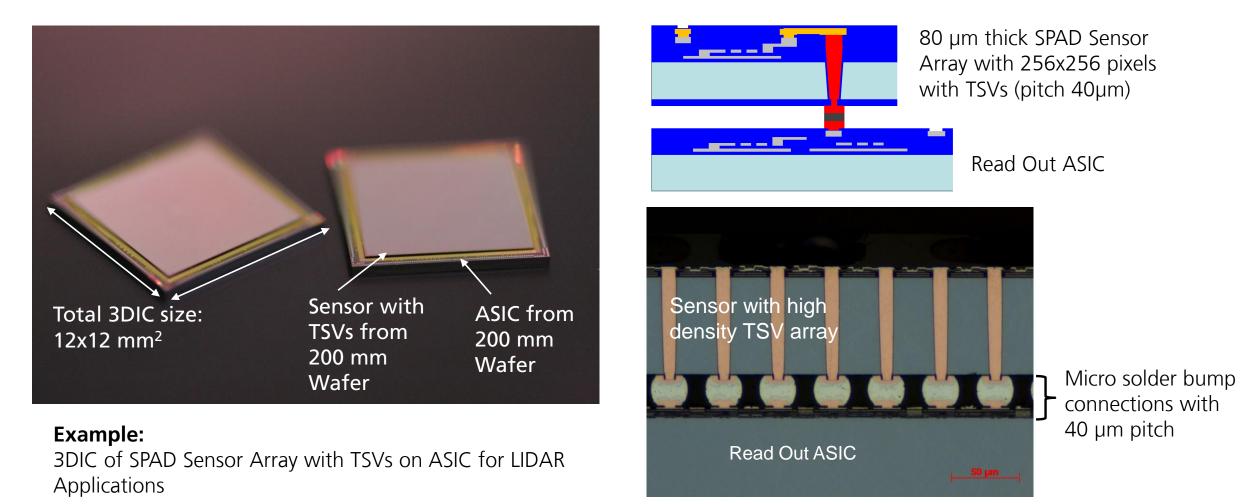

## **3D Integration Technologies**

TSV in SPAD sensor array – TSV frontside via last process

## Outline

- Status Hybrid Pixel Detectors

- > New Developments

- Trends in Advanced Electronic Packaging

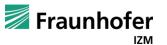

## **Advanced Electronic Packaging**

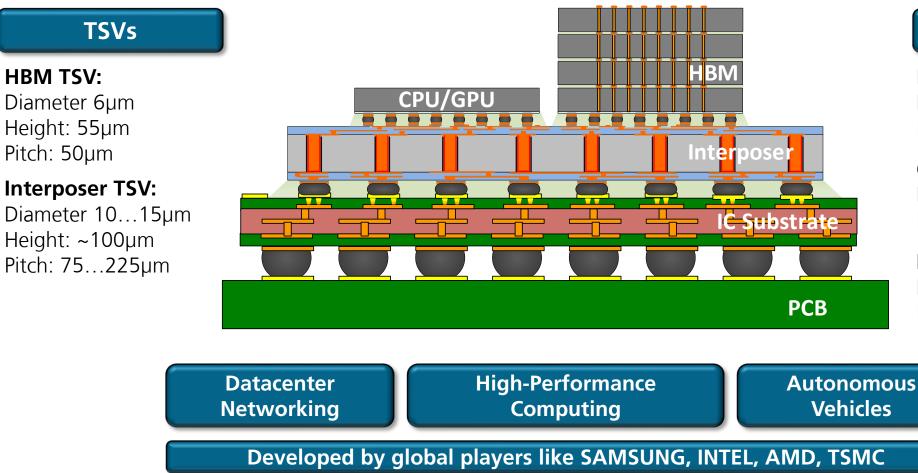

3D/2.5D Package for High-End Performance Applications

Interconnects

**HBM stack** Diameter 20µm Pitch 48µm

## CPU/GPU/HBM to Interposer

Diameter ~25µm Pitch 95µm

#### Interposer to IC substrate:

Diameter 100µm Pitch 200µm

Numbers according to High-End Performance Packaging: 3D/2.5D Integration 2022 | Report | www.yole.fr

17

Pixel 2022 - The 10th International Workshop on Semiconductor Pixel Detectors for Particles and Imaging

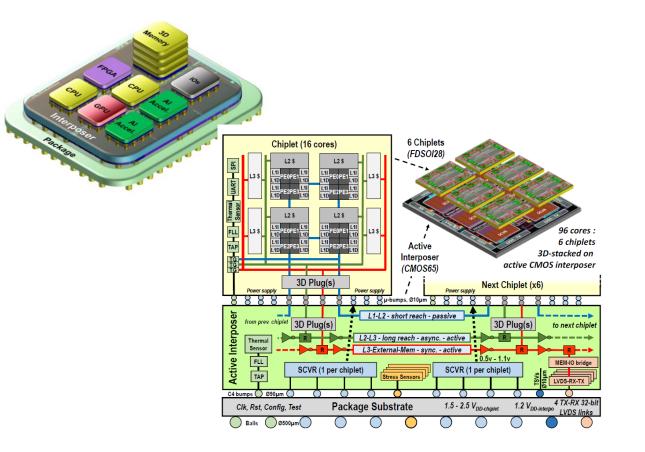

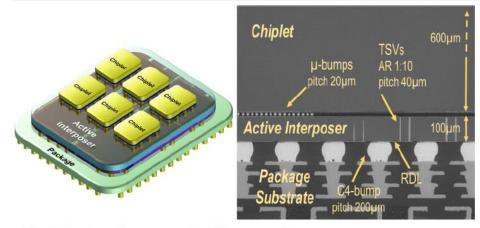

## **Advanced Electronic Packaging**

Processor Chiplet Assembly on Active Interposer

Pascal Vivet, Eric Guthmuller, Yvain Thonnart, Gaël Pillonnet, Cesar Fuguet, et al.. IntAct: A 96-Core Processor With Six Chiplets 3D-Stacked on an Active Interposer With Distributed Interconnects and Integrated Power Management. IEEE Journal of Solid-State Circuits, Institute of Electrical and Electronics Engineers, 2020, pp.1-1. 10.1109/JSSC.2020.3036341 . hal-03072959

Fig. 5. INTACT : from concept to 3D-cross section

TABLE I: INTACT MAIN CIRCUIT FEATURES AND 3D TECHNOLOGY DETAILS

| Chiplet technology     | FDSOI 28nm, 10 metals, 0.5V-1.3V+adaptive biasing                |

|------------------------|------------------------------------------------------------------|

| Chiplet area           | $4.0 \text{ mm x} 5.6 \text{ mm} = 22.4 \text{ mm}^2$            |

| Chiplet complexity     | 395 Million transistors, 18 transistors/µm <sup>2</sup> density  |

| Interposer tech.       | CMOS 65nm bulk, 7 metals, MIM option, 1.2V                       |

| Interposer area        | $13.05 \text{ mm} \ge 15.16 \text{ mm} = 197.8 \text{ mm}^2$     |

| Interposer complexity  | 15 Million transistors, 0.08 transistors/µm <sup>2</sup> density |

| 3D technology          | Face2Face, Die2Die assembly onto active interposer               |

| µ-bump technology      | Ø10µm, pitch 20µm                                                |

| #µ-bumps               | 150 000 (20k signals + 120k powers + 10k dummies)                |

| Inter-chiplet distance | 800µm                                                            |

| TSV technology         | TSV middle, Ø10µm, height 100µm, pitch 40µm                      |

| #TSV                   | 14 000 TSV (2 000 signals + 12 000 power supply)                 |

| Backside RDL           | 10µm width, 20µm pitch                                           |

| C4-bumps               | Ø90µm, pitch 200µm, 4,600 bumps                                  |

| Flipchip package       | BGA 39 x 39, 40mm x 40mm, 10 layers                              |

| Balls                  | Ø500µm, pitch 1mm, 1 517 balls                                   |

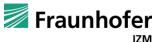

## **Advanced Electronic Packaging**

#### Photonic Integration Technology

#### Empowering Photonic Interconnects for Data Center and NGC

Tolga Tekin, Fraunhofer IZM EPIC Meeting on CMOS Compatible Integrated Photonics at imec Leuven, Belgium, 7-8 September 2022.

- High data rate communication using Photonic IC (PIC)

- Drivers in Industry: next generation computing cloud, edge, node HPC

- Electrical and optical integration on silicon photonic interposer and PIC

- Optical off-chip interconnection for chip-to-chip communication: low-latency, high-bandwidth, high density, low power

- Massive switching beyond 400 Gb/s with new developed Serializer/Deserializer circuits and optical links

- How to enable mass-manufacturing of datacom photonics products? – lower cost, lower power consumption, higher reliability

## **Summary**

- Current hybridizaton projects cover the range from 300mm wafer to single chip processing: requires a high level of flexibility in your process line

- Requested module numbers from several thousand to only one prototype: requires capabilities for volume production and process slots for R&D projects

- Interconnection pitch one benchmark for flip chip product developments: interconnection pitch reduction from 50µm pitch to sub-10µm pitch

- New developments in bonding technologies and integration: cover C2C, C2W and W2W bonding, 3D integration and chip stacking

- Advanced packaging developments ongoing for high preformance computing: 3D/2.5D system in package, chiplet integration, silicon photonics integration, qubit-chip packaging

Fraunhofer Institute for Reliability and Microintegration IZM

# Thank you for your attention!

Thomas Fritzsch Fraunhofer IZM Berlin Department WLSI Phone +49 30 46403 681 thomas.fritzsch@izm.fraunhofer.de

Fraunhofer Institute for Reliability and Microintegration IZM

# Backup

Thomas Fritzsch Fraunhofer IZM Berlin Department WLSI Phone +49 30 46403 681 thomas.fritzsch@izm.fraunhofer.de

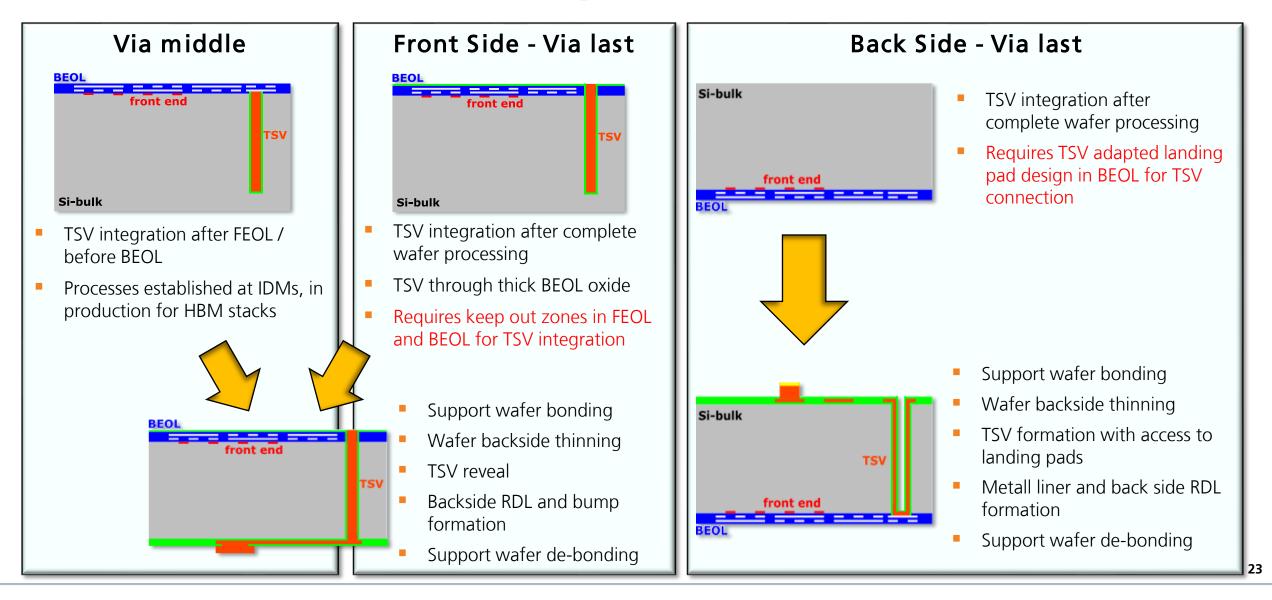

## **TSV Integration Schemes**

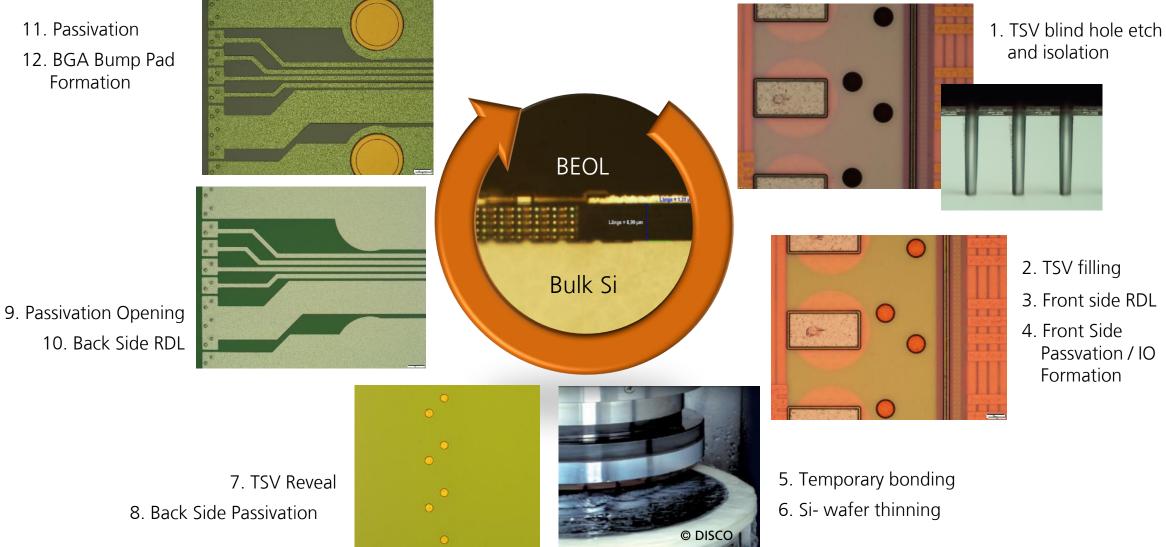

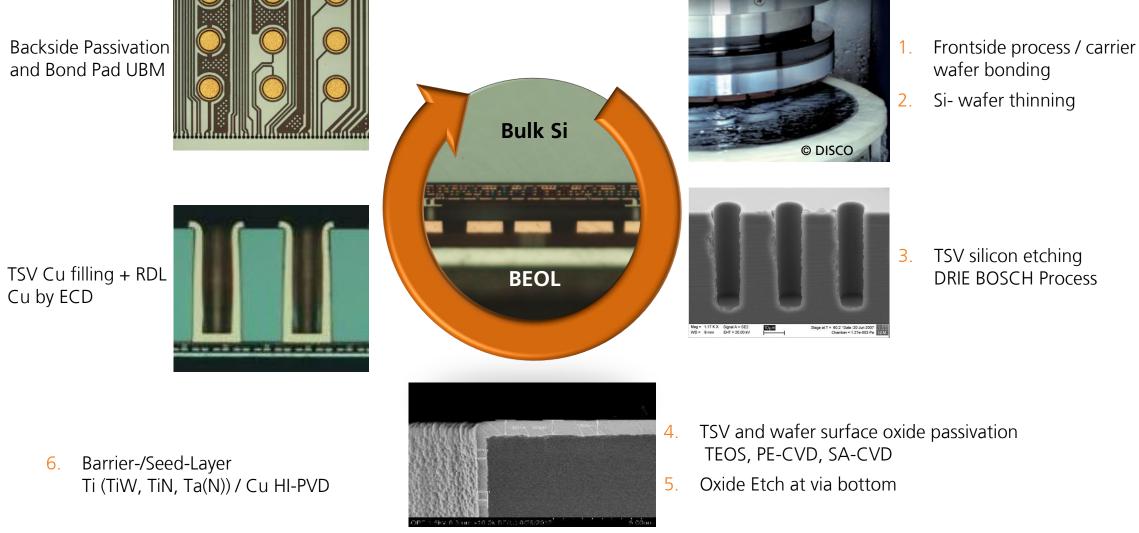

## Basic Process Steps of TSV Formation – Back Side Via Last

**Backside Passivation** 8. and Bond Pad UBM

Cu by ECD

6.

7.

## **Basic Process Steps of TSV Formation – TSV Frontside – Via Last**

11. Passivation 12. BGA Bump Pad Formation