# Innovative digital architecture

for low power-consumption MAPS

<sup>1</sup> University of Padua - department of physics and astronomy "G. Galilei" - via F. Marzolo, 8, 35131 - Padua, Italy <sup>2</sup> Italian National Institute of Nuclear Physics (INFN) - Section of Padua - via F. Marzolo, 8, 35131 - Padua, Italy <sup>3</sup> Italian National Institute of Nuclear Physics (INFN) - Section of Turin - via P.Giuria, 1, 10125 - Turin, Italy

Istituto Nazionale di Fisica Nucleare Sezione di Padova

### HASH architecture idea

In MAPS, depending on the operating conditions, a significant part of the power consumption may be used to communicate the hit pixel address to the periphery. A common solution employs a bus shared among the pixels belonging to the same physical column, where each pixel writes its address, in a radix-of-two basis. This approach, and its variations, are an example of early encoding, where the pixel transmits its complete address. This approach is usually not directly scalable, as the number of communication lines and their topology depend on the matrix size.

A theoretical alternative would be to directly connect each pixel to periphery through a one-hot line. This way, the periphery must reconstruct the pixel position by looking at the physical position of the wire brining the hit information. Such an ideal arrangement would allow for simpler pixels, and easier addressing (for reset and configuration). It can be thought as address writing in radix-of-N, instead the standard radix-of-two. We refer to this approach as late encoding. Clearly, this approach is impractical, as modern MAPS pixel density makes it impossible to route all the metal lines such an architecture would require.

An hybrid approach may use something in between, exploiting **projections**: if there are some **lines shared between pixels**, the address can be communicated through single bits and be reconstructed in the periphery. This algorithm is lossy; depending on the number of projections, reconstructions might be wrong. By adding more projections, the number of wrong cases drops.

Early encoding

## Mathematical justification

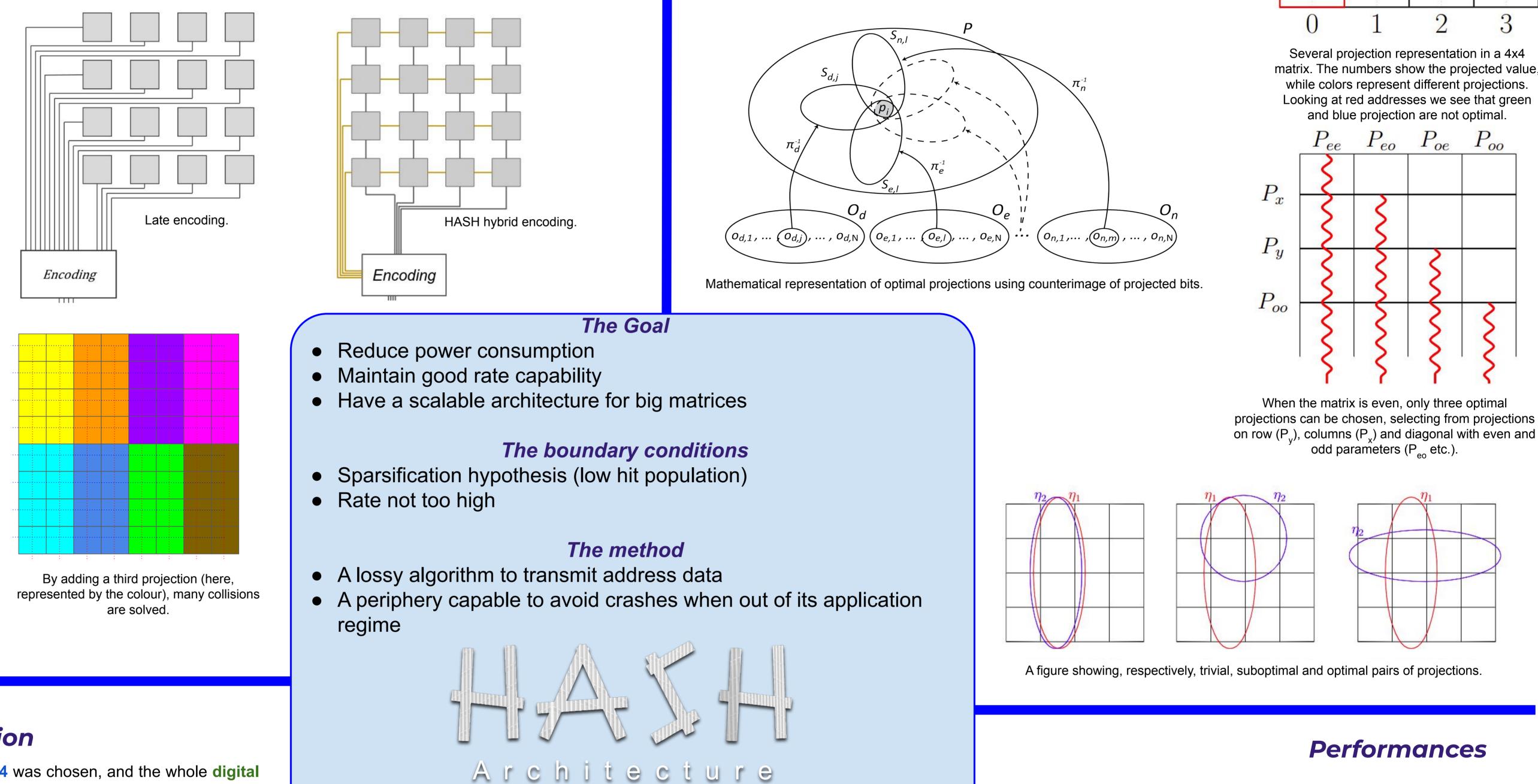

A thorough preliminary study has been done to find the **best projections** to use for this purpose.

A formalism has been created, electing the projections that maximize the reconstruction capability by looking at the couterimage of the projected bits.

Pairs of projections are ranked as:

- **Optimal** when a single hit is always reconstructed correctly by using only these two projections;

- Suboptimal when it is possible to make a mistake trying to reconstruct a single hit;

- Trivial when the two projections provide the very same information.

| 2 | 2 | 1 | 2 | 2 | 2 | 3 | 2 | 0 |

|---|---|---|---|---|---|---|---|---|

| 3 | 0 | 3 | 1 | 0 | 2 | 1 | 3 | 2 |

| 2 | 0 | 2 | 0 | 3 | 0 | 0 | 0 | 1 |

| 2 | 0 | 2 | 1 | 3 | 2 | 0 | 3 | 1 |

| 1 | 2 | 3 | 2 | 0 | 2 | 1 | 2 | 2 |

| T | 0 | 1 | 1 | 2 | 2 | 3 | 3 | 0 |

| 0 | 0 | 0 | 0 | 1 | 0 | 2 | 0 | 3 |

|   | 0 | 0 | 1 | 1 | 2 | 2 | 3 | 3 |

|   | 0 |   | 1 |   | 2 |   | 3 |   |

Several projection representation in a 4x4 matrix. The numbers show the projected value,

Several Monte Carlo simulations were run to validate this

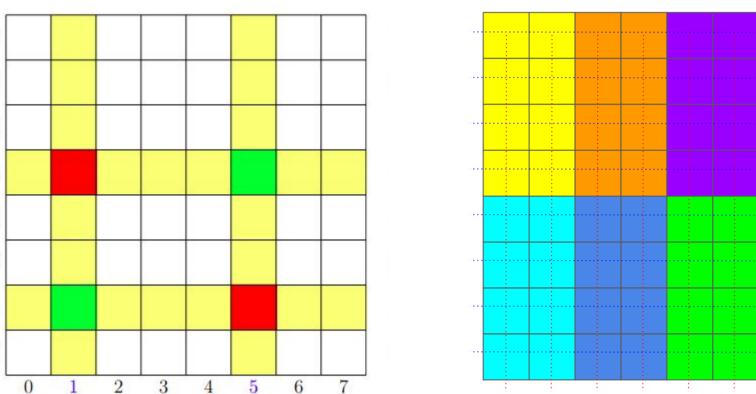

If 2 projections are used wrong reconstructions are relatively likely (here, 2 hits in green are reconstructed together with two mistakes in red using only the 2 projections along x and y axis).

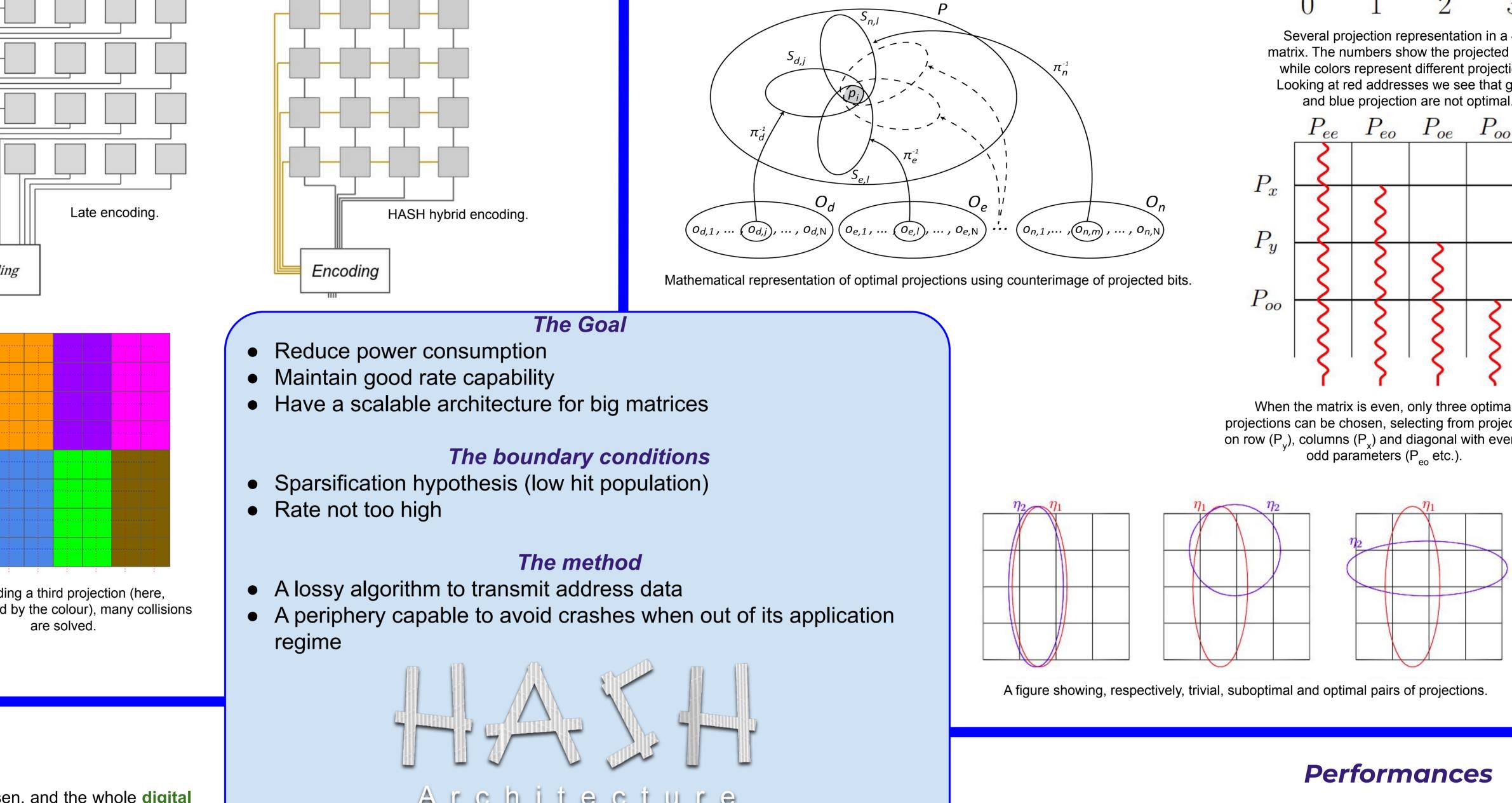

#### **Device implementation**

A fixed number of projection equal to 4 was chosen, and the whole digital architecture was developed, simulated and verified in system-verilog.

A "smart" pixel layout has been developed, so that the pixel layout (gates and metals) is in fact identical for each pixel in the matrix, making it easy to generate large area sensors. The only elements changing from pixel to pixel is in fact a fixed layout set of vias, which are programmatically enabled (via is actually present) or disabled (via is omitted) to determine the pixel function in the matrix.

For the place and route phase, an **automatic routing algorithm** has been integrated with the standard placement tools (Synopsis): for each pixel the algorithms determines the correct vias setting accordingly to its position in the matrix, so to automatically implement the hash-code generating architecture across the whole matrix.

The periphery was completely developed, simulated, and tested for various possible faults. In the current implementation, all addresses are tested, and wrong addresses give an empty signal accordingly.

Many further flavours (e.g. without address testing, with self-reset, or with **possible fake hits** are envisioned and can be created by changing only slightly the current implementation.

#### The Solution

- Scalable architecture can easily be built arbitrarily large

- Rate capability demonstrated by using pessimistic time constraints

- Simple pixels low power consumed

- Its implementation can change depending on physical constraints (add projections)

- Theorized in different flavours:

- In-pixel memory

- Clustering algorithm

- Loss prone but faster

#### The future

The architecture has been thoroughly studied by using Monte Carlo simulations. The rate performances are good for many scientific applications (space physics, also some high energy physics). Power consumption estimation is promising. We foresee to complete place and route and a tentative silicon run.

architecture:

- In an idealized condition, the reconstruction capability, changing the number and the type of projections;

- In a real physical condition, using RTL simulation environment, the digital logic was validated and issues were sought;

- In a replicated condition, using ad-hoc developed C++ software, high statistics was simulated to compute the efficiency of the device in various conditions and various flavours.

From a **power point of view**, pixels are **extremely simple**, hash propagation is not power hungry (a hashing line consumes ~ twice a normal communication line) and periphery can be adapted depending on spatial, power and speed constraints.

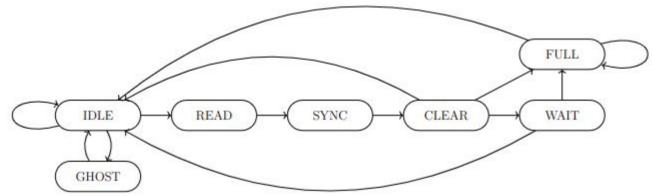

The automata of the periphery readout and reset machine in the current implementation. This flavour is hyper safe and reliable, prevents any digital collision, but could be further optimized in terms of speed.

| ) | Matrix                                                                                                                                   | Pixel<br>pitch | Aspect<br>ratio | Hash line<br>speed | Data line<br>speed |  |  |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|--------------------|--------------------|--|--|--|

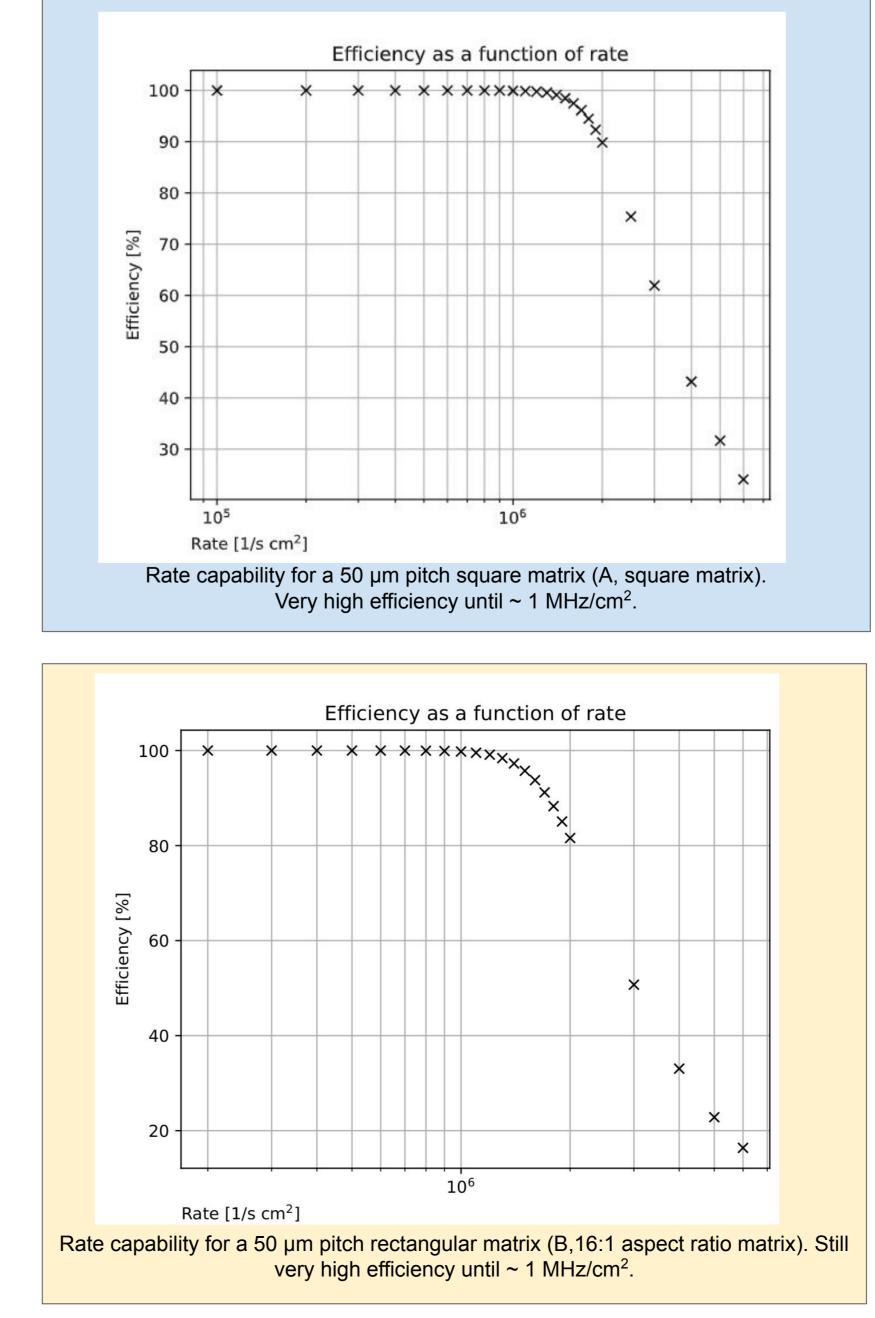

|   | A                                                                                                                                        | 50 µm          | 512x512         | 26 ns/cm           | 7 ns/cm            |  |  |  |

|   | В                                                                                                                                        | 50 µm          | 128x2048        | 10 ns/cm           | 7 ns/cm            |  |  |  |

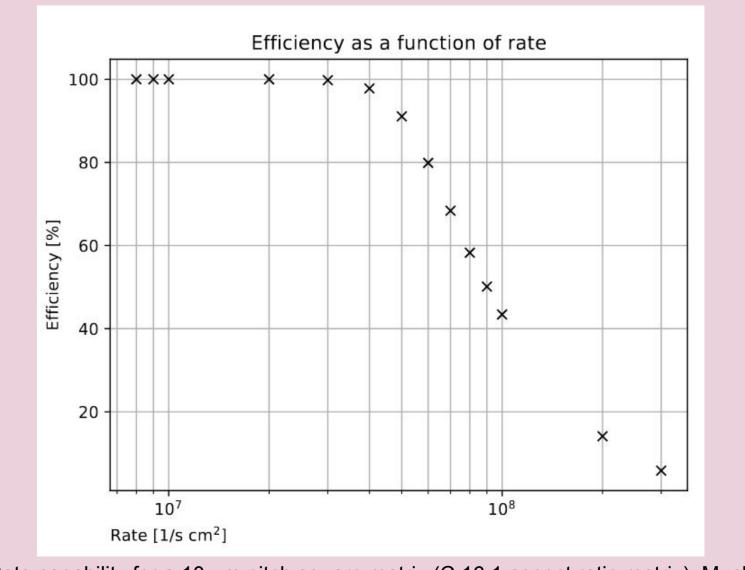

|   | С                                                                                                                                        | 10 µm          | 128x2048        | 26 ns/cm           | 7 ns/cm            |  |  |  |

|   | Three matrices, with different aspect ratio and pixel size,<br>are foreseen. Line speed deduced from technological<br>libraries (110 nm) |                |                 |                    |                    |  |  |  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                                         |                                                         |                                                     |                                                                             |

|-------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------------|

| Hash projections in<br>current<br>implementation      | Guide for<br>connection of P <sub>x</sub><br>projection | Guide for<br>connection of P <sub>y</sub><br>projection | Guide for<br>connection of a<br>diagonal projection | In most diagonal<br>bits, a peculiar<br>operation, named<br>hook, is needed |

#### Hits per frame

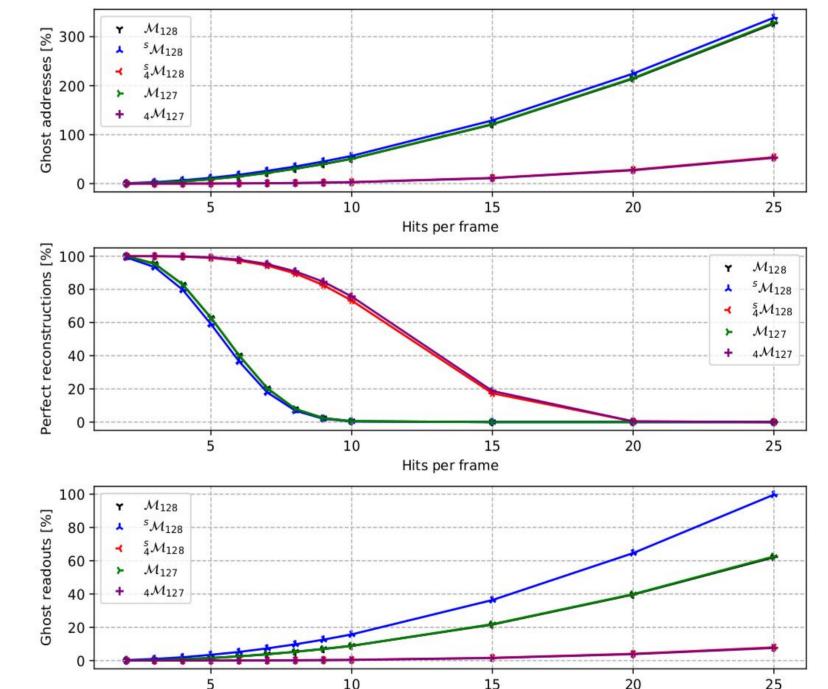

Mathematically, the performance of a set of projections can be computed by looking at the percentage of wrong addresses (first plot), the percentage of perfect reconstruction (second plot) and the percentage of ghost readout when address are evacuated (third plot). Here five different matrices, with slightly different sizes, three or four projections and suboptimal sets of projections.

Rate capability for a 10 µm pitch square matrix (C,16:1 aspect ratio matrix). Much higher rate capability.