Optimization of a 65 nm CMOS imaging technology for monolithic sensors for high energy physics

### CERN EP R&D WP1.2 Monolithic Pixel Detectors

Many contributors, see next page

CÈRN

R&D

FP

# Optimization of a 65 nm CMOS imaging technology for monolithic sensors for high energy physics

University and INFN Torino: F. Benotto, S. Beole, C. Ferrero U. Savino, S.

Perciballi, F. Prino, A. Turcato **University and INFN Bari**: G. De Robertis, F. Loddo

University and INFN Catania: P. La Rocca, A. Triffiro

University and INFN Cagliari: D. Marras, , V. Sarritzu, G. Usai

University of Salerno and Bologna: R. Ricci

University and INFN Trieste: M. Antonelli, R. Baccomi, M. Buckland, P.

Camerini, G. Contin, S. Rashevski A. Villani

**CPPM**: P. Barrillon, M. Barbero, D. Fougeron, A. Habib, P. Pangaud

IPHC: J. Baudot, G. Bertolone, A. Besson, S. Bugiel, C. Colledani, A. Dorokhov,

Z. El Bitar, X. Fang, M. Goffe, C. Hu, K. Jaaskelainen, F. Morel, H. Pham, S. Senyukov, J. Soudier, I. Valin, Y. Wu (also with USTC)

**NIKHEF**: R. Russo, V. Gromov, D. Gajanana, A. Yelkenci, A. Grelli, R. Kluit, J. Sonneveld, A. Vitkovskiy

**Heidelberg University**: P. Becht, S. Masciocchi, M.W. Menzel, H.K. Soltveit, A. Yuncu, J. Stachel

Munster University: A. Andronic, N. Tiltmann

Prague University: A. Isakov, A. Kotliarov, F. Krizek

STFC (RAL): S. Matthew, I. Sedgwick

Birmingham University: L. Gonella

**Technical University Munich**: L. Lautner, I. Sanna (also with CERN), L. Fabiette

**Technical University Vienna**: J. Hasenbichler (also with CERN) **DESY:** K. Hansen, C. Reckleben, S. Spannagel Strong synergy with ALICE ITS3 upgrade

Yonsei University: Y. Kwon, G.H. Hong CCNU: Wenjing Deng (also with CERN) EPFL: E. Charbon, F.Piro (also with CERN) SLAC & Stanford U: M.D. Vassilev, C. Vernieri

**CERN:**, G. Aglieri Rinella, W. Bialas, G. Borghello, R. Ballabriga, J. Braach, E. Buschmann, M. Campbell, F. Carnesecchi, L. Cecconi, D. Dannheim, K. Dort, Joao de Melo, W. Deng (also with CCNU), A. Di Mauro, A. Dorda Martin, P. Dorosz, J. Hasenbichler (also with TU Vienna), H. Hillemans, A. Junique, I. Kremastiotis, A. Kluge, G. Kucharska, T. Kugathasan, P. Leitao, M. Mager, P. Martinengo, M. Munker, L. Musa, F. Piro, K. Rebane, F. Reidt, I. Sanna (also with TU Munich), <u>W. Snoeys</u>, P. Svihra, M. Suljic, G. Termo, J. B. Van Beelen

**TPSCo:** M. Suzuki, **Tower Semiconductor:** A. Fenigstein, and **Etesian Semiconductor:** A. Haim, E. Toledano

### EP RD WP1.2 on monolithic CMOS sensors

#### Long term goal: develop CMOS sensors in sub 100nm technologies

• Synergy with development of the stitched sensor in the ALICE ITS3 upgrade (see Lukas Lautner's presentation)

#### First technology selected: TPSCo 65 nm CMOS imaging technology

- TPSCo (joint venture TJ & Panasonic): several 65 nm flavors: high density logic, RF, and imaging (ISC)

- ISC preferred: 2D stitching experience, special sensor features, different starting materials, lower defect densities, etc

- Initially 5 metal layers, now 7 metals

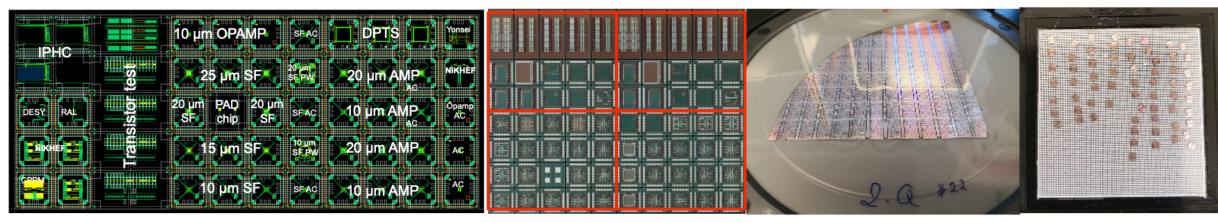

First submission: Multi Layer per Reticle MLR1

- Significant contribution from outside groups (from ALICE but not only) to design and test (!), also financially

- Many test chips of 1.5 x 1.5 cm<sup>2</sup> or twice that size.

- How to optimize sensor integrated with complex in-pixel circuitry ?

- GDS submitted Dec 1, 2020, released for manufacturing end of Feb 2021, chips ready to test, Sept, 2021

20221215 | Pixel 2022 | Monolithic Sensor Development

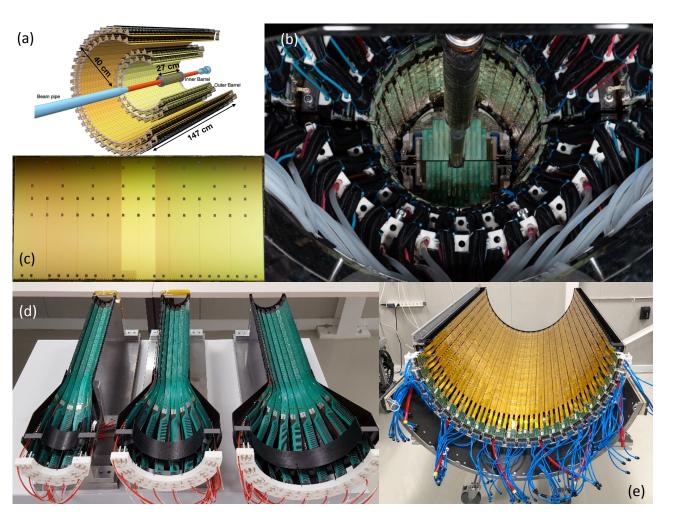

# State of the art: ALICE Inner Tracking System 2 : $10 \text{ m}^2$ with 3x1.5 cm<sup>2</sup> ALPIDE chips

TowerJazz 180 nm imaging CMOS technology, development 2012-2016

#### ALPIDE CHIP

- 512 x 1024 pixels of 28 x 28 μm<sup>2</sup>

- Full CMOS in the pixel (deep pwell)

- 40 nW front end, sparse readout

- Matrix 6 mW/cm<sup>2</sup>, up to 40 mW/cm<sup>2</sup> including periphery

- Standard process: sensitive epitaxial layer not depleted

### Taking data

# ALICE Pb-Pb 5.36 TeV

A AND A A

ALE MAIN MARKED ADALAS

A CONTRACTOR OF A CONTRACTOR

LHC22s period 18<sup>th</sup> November 2022 16:52:47.893

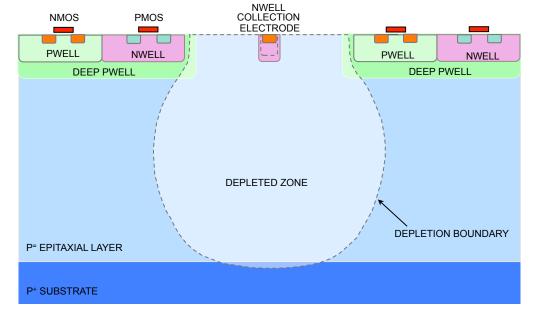

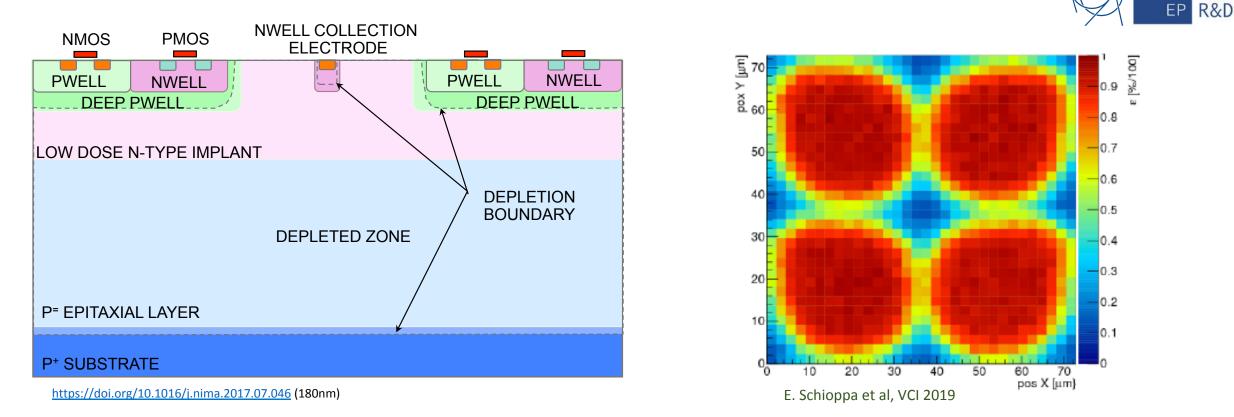

### The need for sensor optimization to obtain full depletion

Signal charge is collected from the non-depleted layer, diffusion dominated and prone to trapping after irradiation

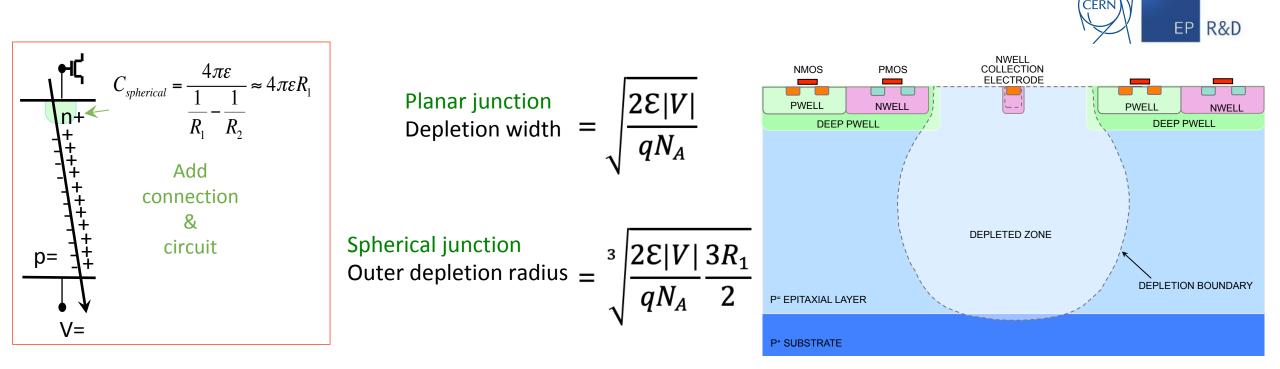

#### Planar vs spherical junction

- Planar junction: depletion thickness proportional to square root of reverse bias.

- Spherical junction : depletion thickness proportional only to *cubic root* of reverse bias, inner radius R1 to be kept small for low capacitance

- Deep pwell and substrate limit extension of the depletion layer -> see next slide

### Sensor optimization: influence of the resistivity of the epitaxial layer

For thinner epitaxial layers, higher resistivity does not help for further depletion due to the proximity of the substrate

Depletion constrained by the substrate and surrounding pwells

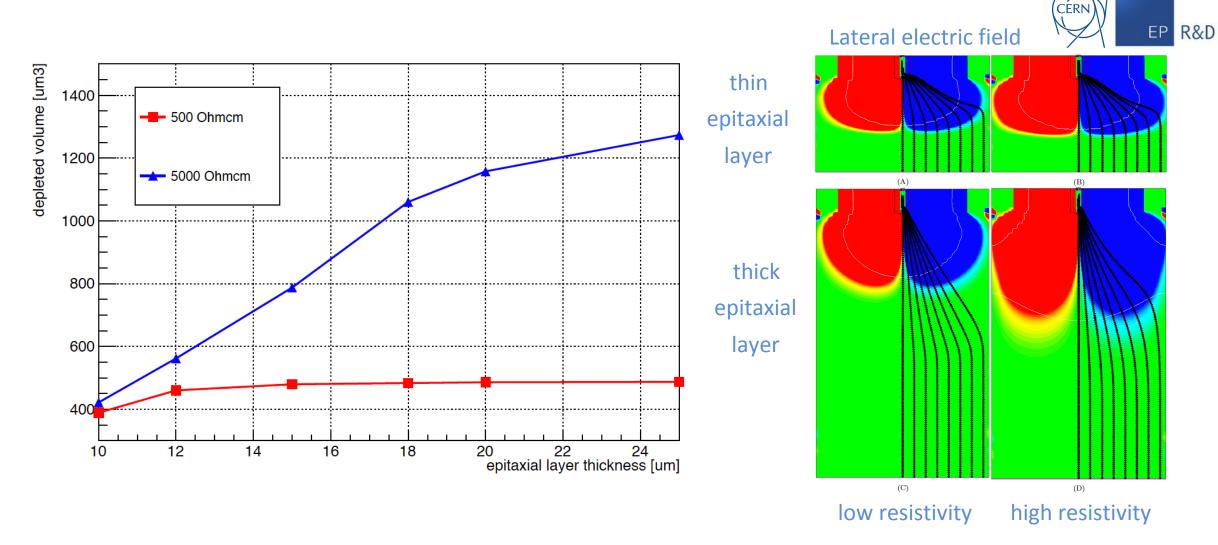

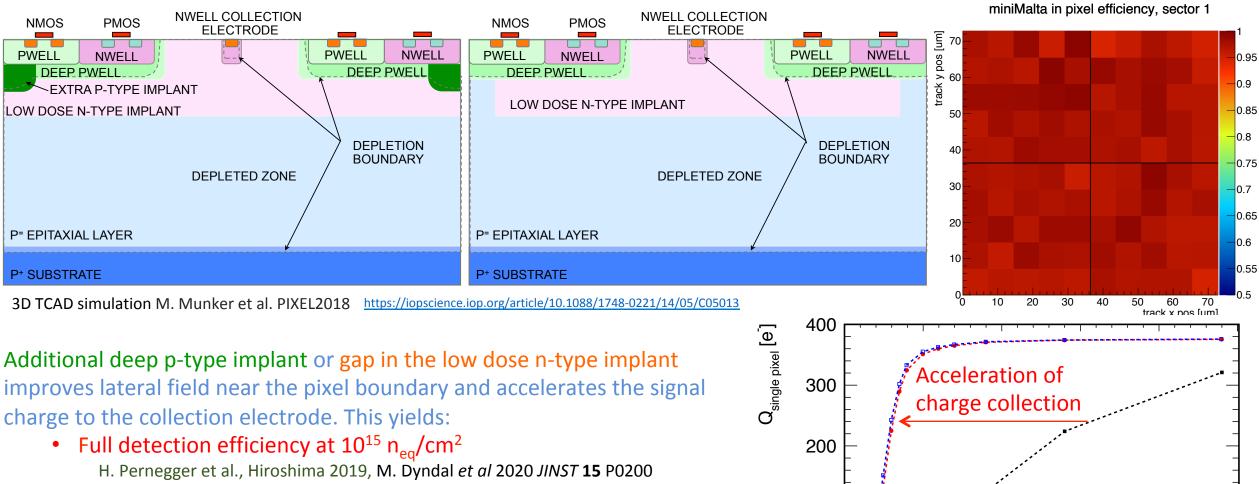

#### Sensor optimization: create planar junction using deep low dose n-type implant CÈRN

TowerJazz 180nm imaging CMOS technology

- Side development in ALICE: move junction away from the collection electrode to create a planar junction and deplete the epitaxial layer

- add deep low dose n-type implant -> radiation tolerance improved by an order of magnitude.

- After interest from ATLAS: MALTA/TJ MONOPIX development (Bonn, CPPM, IRFU and CERN)

- However, efficiency loss at ~ 10<sup>15</sup> 1 MeV n<sub>eq</sub>/cm<sup>2</sup> on the pixel edges and corners due to a too weak lateral field ٠

### Sensor optimization: improvement of the lateral field

TowerJazz 180 nm imaging CMOS technology

CERN EP R&D

- more operating margin even before irradiation

- better sensor timing

100

5

10

Time [ns] 10

25

**Modified process**

Gap in n-layer

15

Additional implant

20

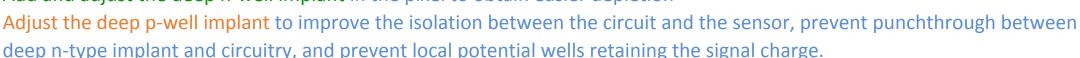

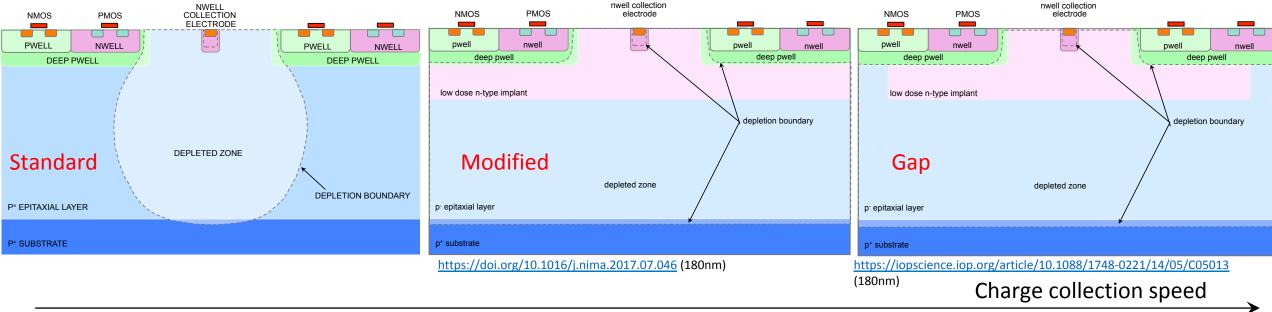

# Moving to 65 nm: apply same principles as in 180 nm

- Process optimization: more needed/beneficial in 65 nm due to a thinner epitaxial layer

- Add and adjust the deep n-well implant in the pixel to obtain easier depletion

- 4 process splits, 3 wafers each: moving gradually from default to optimized process

- Split 1: default process

- Split 2: first deep pwell adjustment to prevent punchthrough

- Split 3: first deep pwell adjustment + deep nwell adjustment

- Split 4: optimized process: first deep pwell adjustment + deep nwell adjustment + second deep pwell adjustment against

local potential wells

- 3 main pixel designs implemented in all process splits

CERN

EP

R&D

### Sensor optimization: Mitigate local potential wells related to the in-pixel circuitry

Simulation for MIPS:

Increasing the margin for punchthrough was not sufficient to eliminate potential wells under the deep pwell.

Lower lateral field for the modified version without gap enhances the effect of these potential wells and illustrates best the improvement

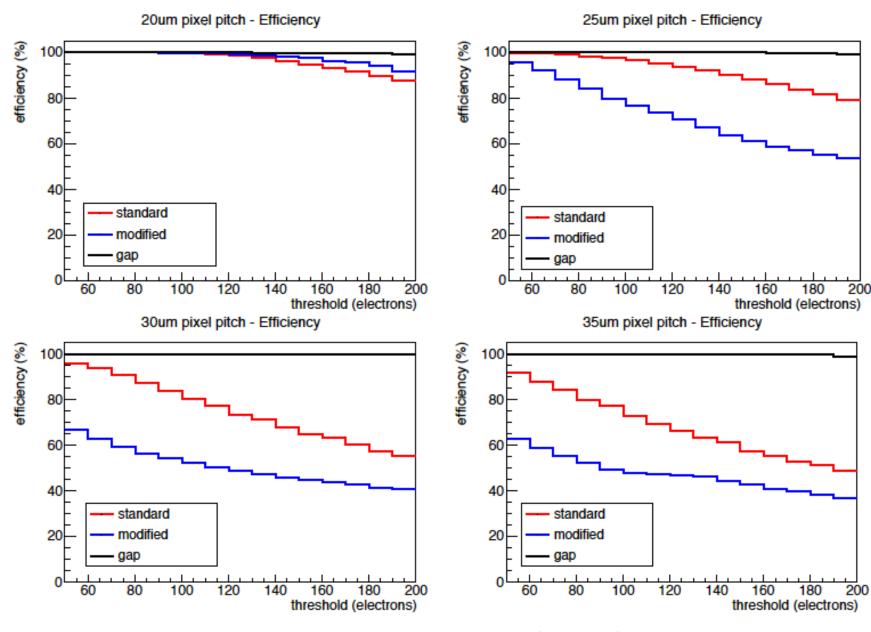

### Different pixel flavors at larger pixel pitches

Simulations by J. Hasenbichler for MIPS

Charge sharing reduces the signal in a single pixel and reduces efficiency especially for larger thresholds.

Only the gap concentrates charge sufficiently to remain efficient for large pixel pitches

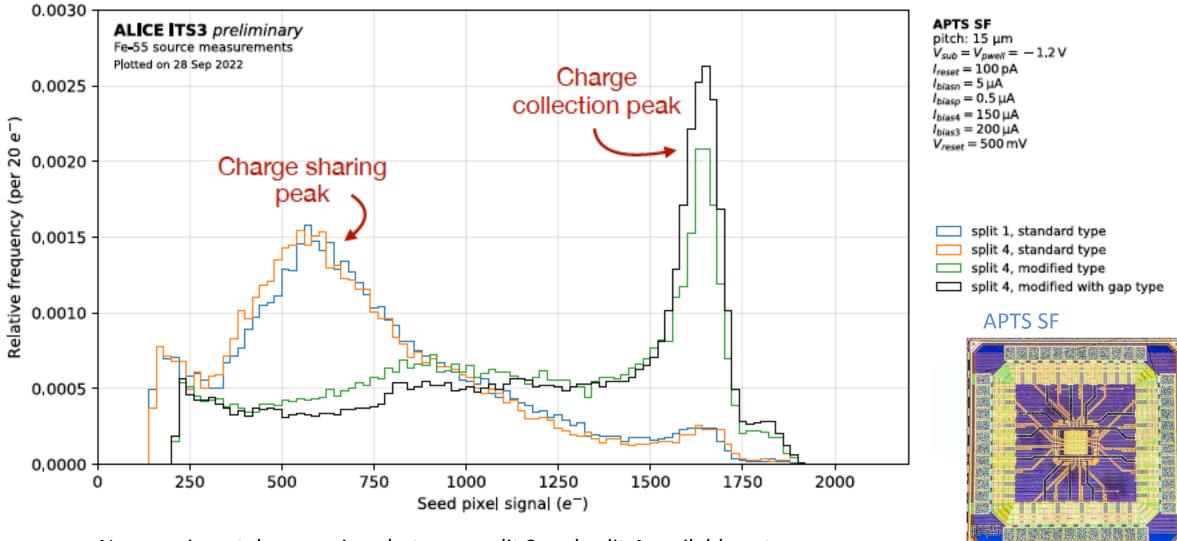

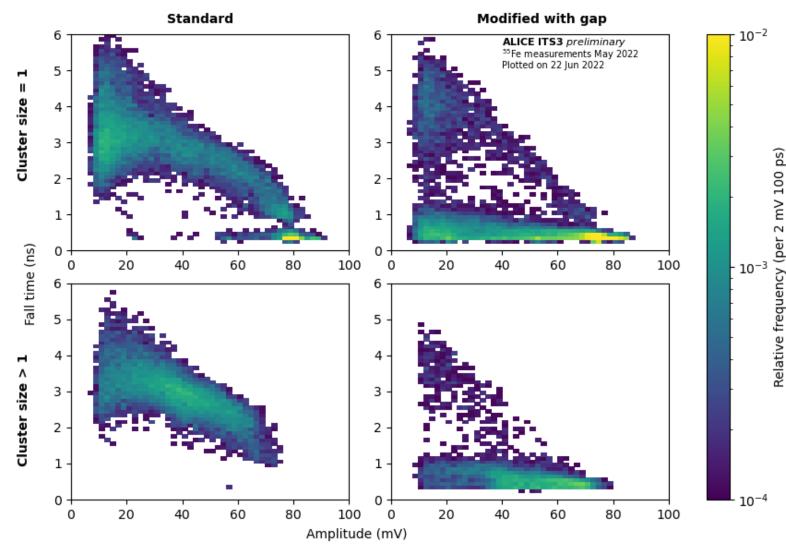

# <sup>55</sup>Fe measurements confirm influence on charge sharing

#### See also: I. Sanna IEEE NSS 2022

No experimental comparison between split 3 and split 4 available yet.

CÉRN

R&D

EP

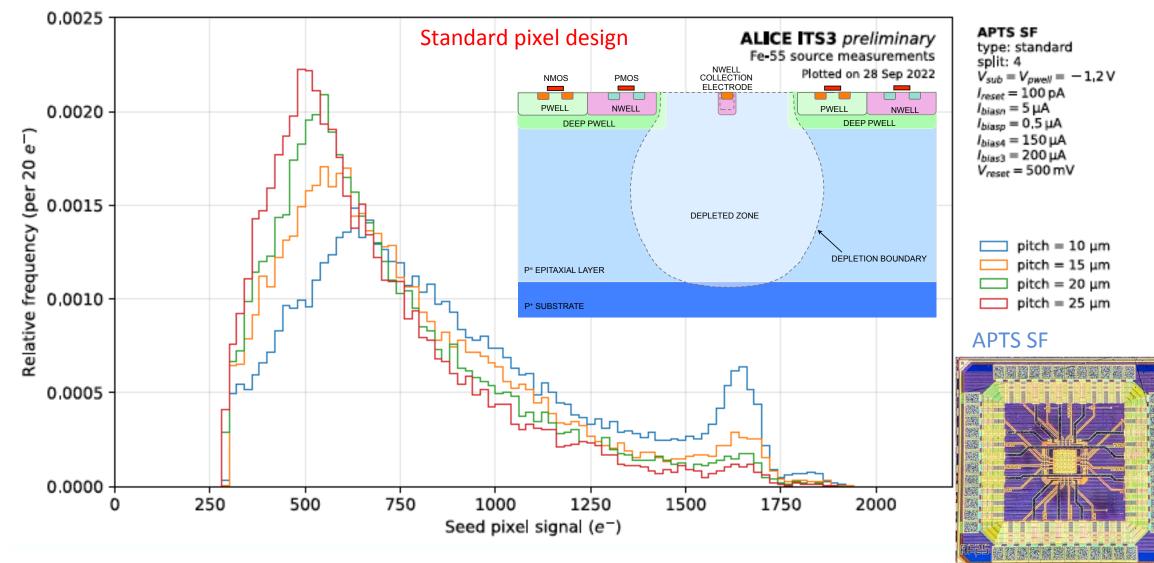

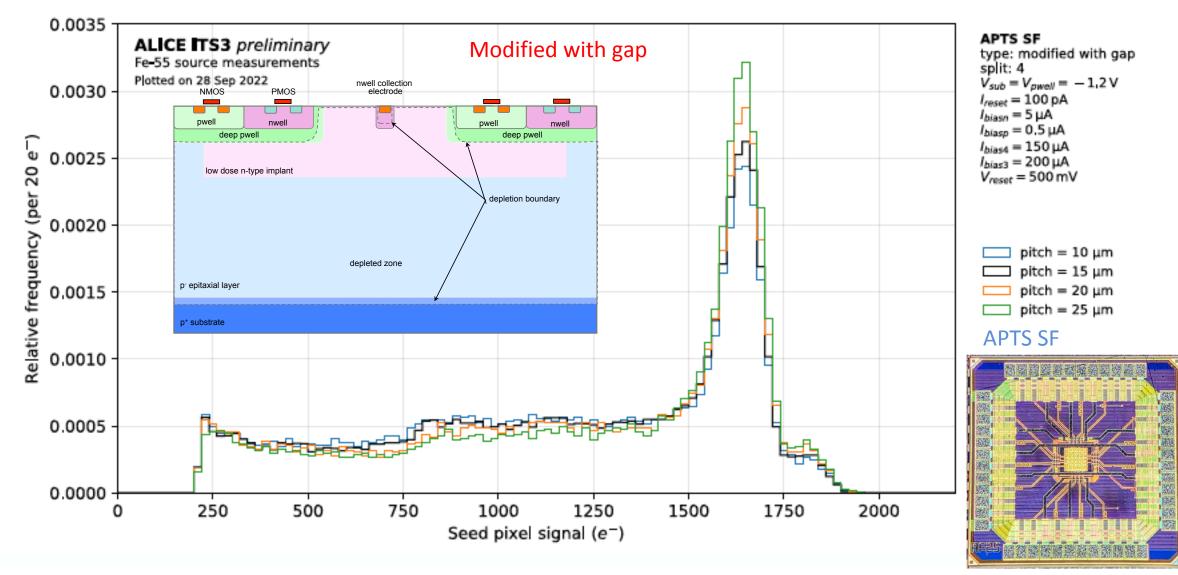

# Pitch dependence for different variants

See also: I. Sanna IEEE NSS 2022

# Pitch dependence for different variants

See also: I. Sanna IEEE NSS 2022

### <sup>55</sup>Fe measurements on Analog Pixel Test Structure Opamp

APTS OPAMP pitch: 10 um version: modified with gap split: 4 (opt.)  $l_{blasp} = 10 \text{ uA}$   $l_{blash} = 75 \text{ uA}$   $l_{blash} = 2.5 \text{ mA}$   $l_{blash} = 2.5 \text{ mA}$   $l_{reset} = 100 \text{ pA}$   $V_{reset} = 350 \text{ mV}$   $V_{casp} = 300 \text{ mV}$   $V_{casp} = 750 \text{ mV}$   $V_{pwel} = V_{sub} = -4 \text{ V}$ T = ambient

Clusters of various sizes show distinct time and charge distributions

Illustrates the impact of the pixel design and process modifications on the charge collection

Sensor timing is at present under study, in 180nm better than 150 ps\*, first indications this may improve in 65 nm.

\*Fastpix :<u>https://www.mdpi.com/2410-390X/6/1/13</u> J. Braach, E. Buschmann, D. Dannheim et al.

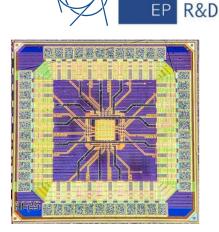

## Detection efficiency/Fake hits

- Fully efficient sensor, analog front end, digital readout chain in 15 x 15  $\mu$ m<sup>2</sup> pixel (DPTS) including sensor optimization

- Large operating margin before irradiation

- After 1E15 n<sub>eq</sub>/cm<sup>2</sup> efficiency > 99% maintained at room temperature

- Higher fluencies under investigation

#### (see also Lukas Lautner's presentation)

R&D

DPTS

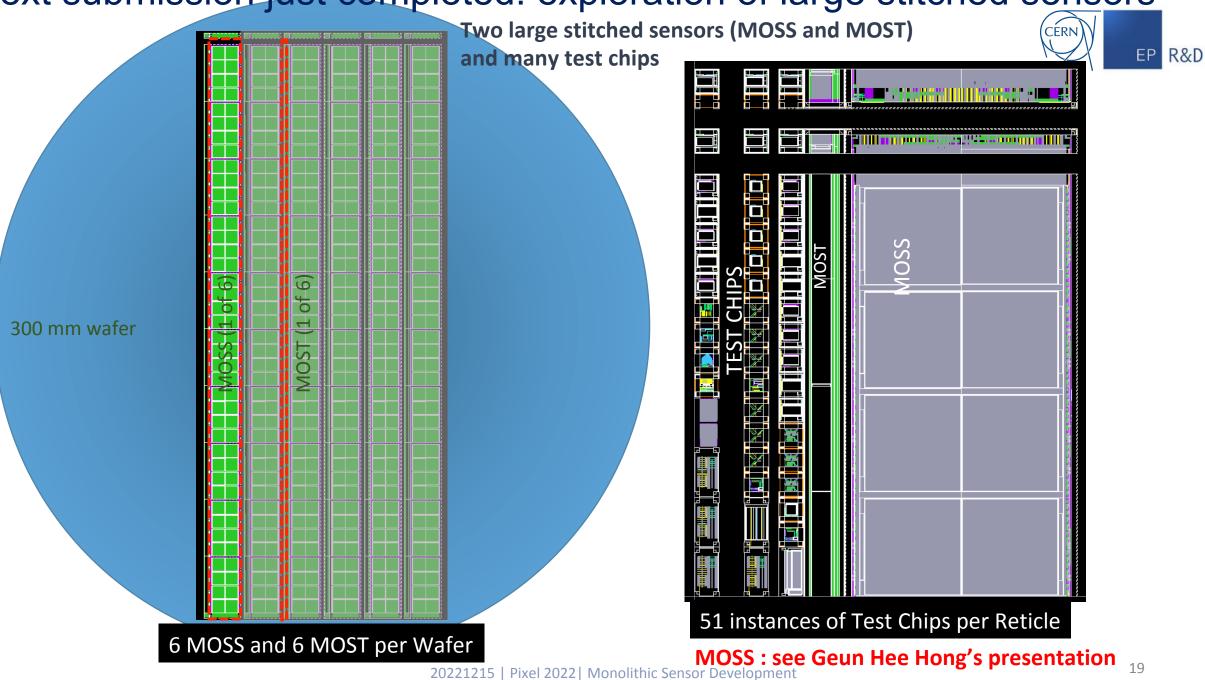

### Next submission just completed: exploration of large stitched sensors

# SUMMARY AND OUTLOOK

#### First technology selected in WP1.2 is the TPSCo 65 nm CMOS imaging technology

- Fully efficient optimized sensor, analog front end, digital readout chain in 15 x 15  $\mu$ m<sup>2</sup> pixel (DPTS)

- Sensor optimization following general principles now also proven in 65 nm

- More margin before irradiation, better time resolution and radiation tolerance

- Technology specific special transistors and sensor structures still to be exploited

#### **Radiation effects**

- Circuit radiation tolerance TID in line with other 65 nm technologies\*

- Sensor radiation tolerance NIEL:

- ~ 99% efficiency after 1e15  $n_{eq}/cm^2$  at room temperature

- higher fluencies to be investigated, also at lower temperature

- Single event upset cross-section according to expectations

#### Building knowledge about this technology for general interest

- Very significant contribution from the ALICE experiment

- Towards full technology validation for our applications ٠

#### Next submission Stitched Engineering Run ER1

- Learning about stitching and continue learning about the technology

- \*P. Barrillon et al, A. Dorda et al. Twepp 2022

20221215 | Pixel 2022 | Monolithic Sensor Development

20

# THANK YOU TO ALL CONTRIBUTING PEOPLE, GROUPS AND INSITUTES

# SPARE

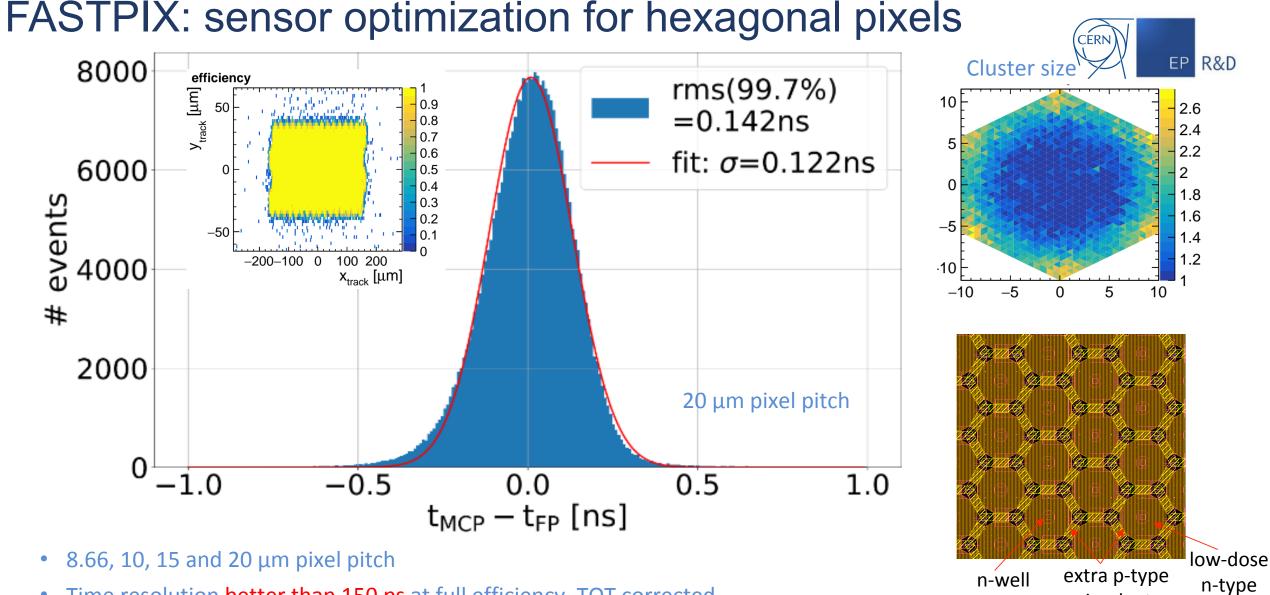

• Time resolution better than 150 ps at full efficiency, TOT corrected

#### https://www.mdpi.com/2410-390X/6/1/13

FASTPIX started as an ATTRACT project funded by the EC Grant Agreement 777222, with INFN, Ritsumeikan U. and CERN

J. Braach, E. Buschmann, D. Dannheim, K. Dort, T. Kugathasan, M. Munker, M. Vicente 20221215 | Pixel 2022 | Monolithic Sensor Development

implant

implant

electrode