The Tenth International Workshop on Semiconductor Pixel Detectors for Particles and Imaging

La Fonda Hotel | Santa Fe, New Mexico, USA

# TimeSPOT ASIC developments for 4D pixel readout

Electronics for high-rate precision-timing Sensors. A system perspective

#### Adriano Lai,

INFN Cagliari

For the TimeSPOT team

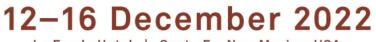

# **CMOS 28-nm for pixels with timing capabilities**

The toughest constraint against speed is power budget, based on state-of-the-art capabilities in cooling system techniques (micro-channelling CO<sub>2</sub>).

Other systems (e.g. CMS/ATLAS with hermetic structure) have harder constraints (< 1 W/cm<sup>2</sup>)

# **TimeSPOT ASIC developments**

## Purpose and scope

- I. Explore the capabilities and technical pitfalls of CMOS 28-nm, which has been chosen as the successor of 65 nm for future HEP developments

- 2. Concentrate first on pixel performance addressing the questions:

- What can be integrated in a pixel  $\approx$  50x50  $\mu$ m<sup>2</sup>?

- Referenced to a target  $\sigma_t \approx 30 \text{ ps} (\sigma_{FE} \oplus \sigma_{TDC})$ , what is the minimum power required ?

- What is the maximum sustainable rate/pixel or is it possible to integrate 1 TDC per pixel?

- What would be the best TDC resolution and its power consumption?

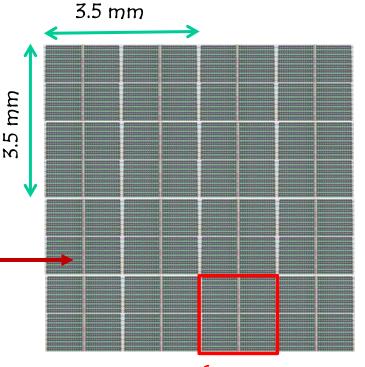

- 3. Design and produce the largest possible chip, compatibly with budget (32x32 pixels was the choice)

- 4. Drop the requirement about high data bandwidth, which needs specific additional developments (as Silicon Photonics)

2 submissions made: Timespoto (single test-cells) and Timespot1 (complete matrix)

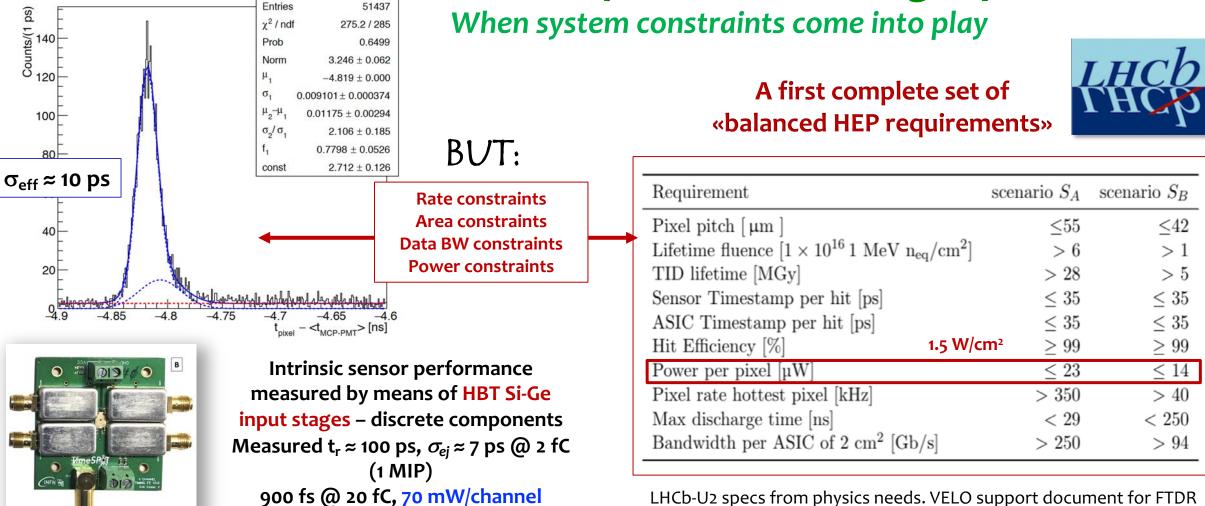

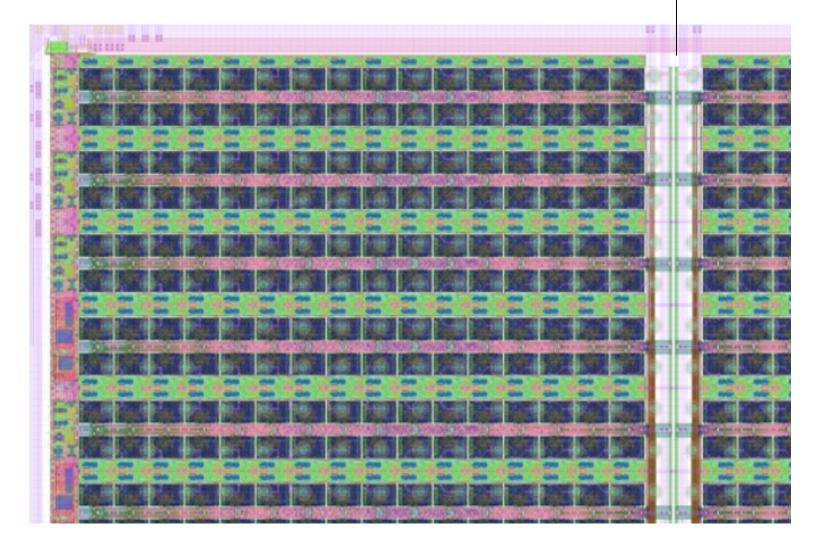

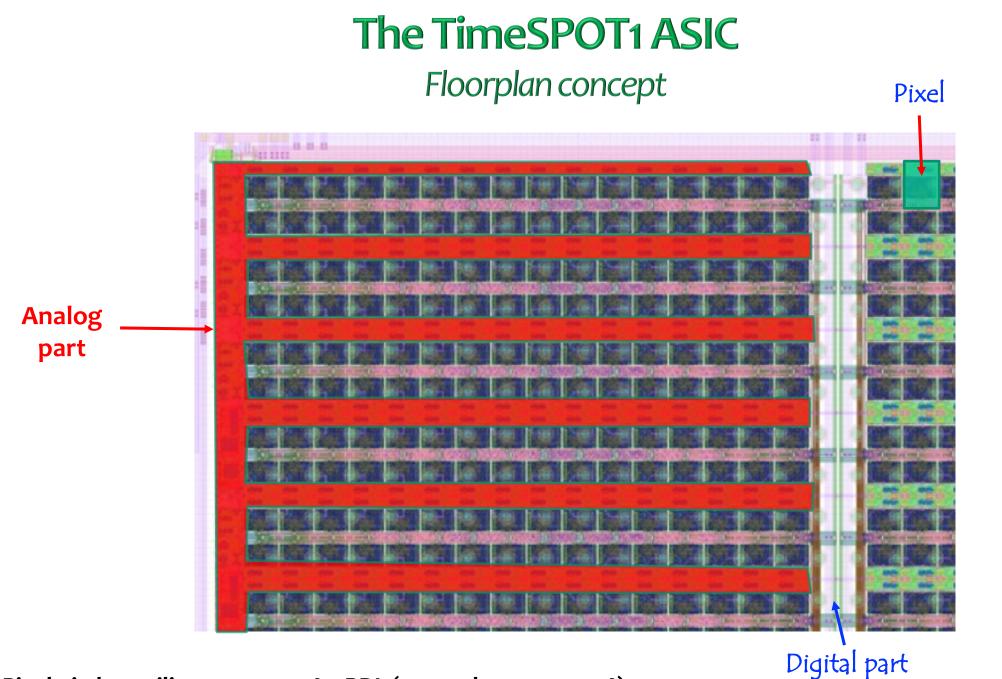

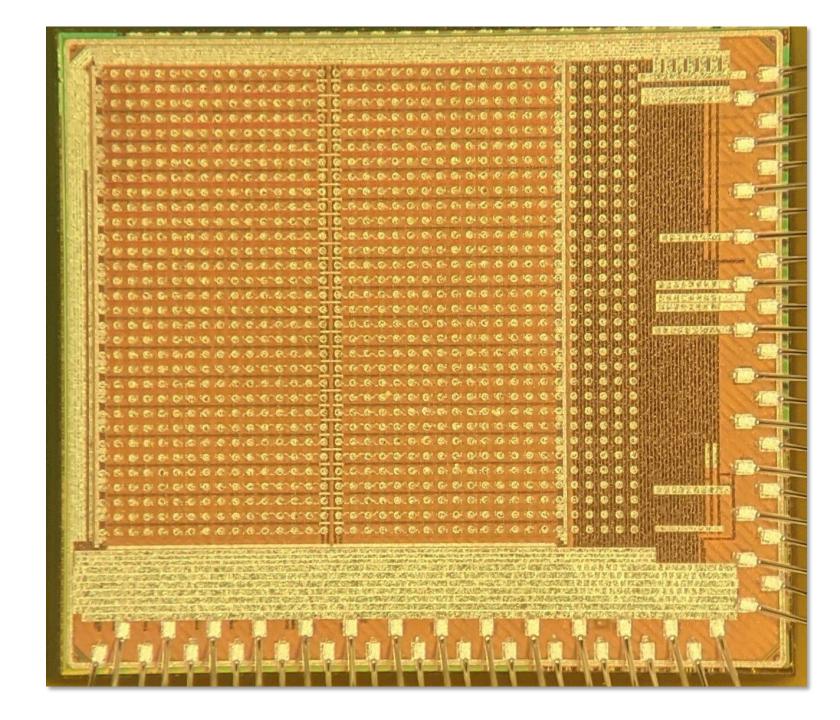

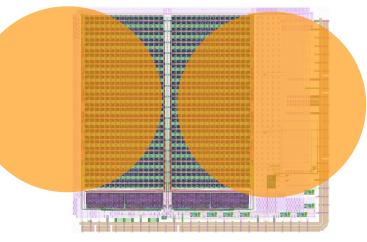

# **Timespot1 ASIC** 28-nm CMOS

- Reduced size (1024 pixels, 6 mm<sup>2</sup>)

- HPC flavour

- Complete set of functionalities for pixel readout

- Slow read-out (demo-test purpose)

INFN Cagliari, Milano, (Pavia), Torino **640 MHz master clock**

- Digital row: 16x2 TDC

- + Controls, Conf. registers, I<sup>2</sup>C I/F

- Analog row (16x2 AFE)

- Analog (service) column. Each contains:

- 1 Band-Gap circuit (Pavia)

- $5x \Sigma \Delta$  DACs (producing analog levels used by pixels)

- Programmable bias cell (for power consumption)

- bias replicas with source followers.

- 4x Read Out Trees

- 8x LVDS driver (Pavia) (each @1.28 Gbps)

# **The TimeSPOT1 ASIC**

Floorplan concept

Every 16 pixels 80 µm are gained (40 µm per side) and used for inter-connectivity

Pixel pitch on silicon 50x55  $\mu$ m<sup>2</sup> + RDL (sensor has 55x55  $\mu$ m<sup>2</sup>)

Pixel pitch on silicon 50x55  $\mu$ m<sup>2</sup> + RDL (sensor has 55x55  $\mu$ m<sup>2</sup>)

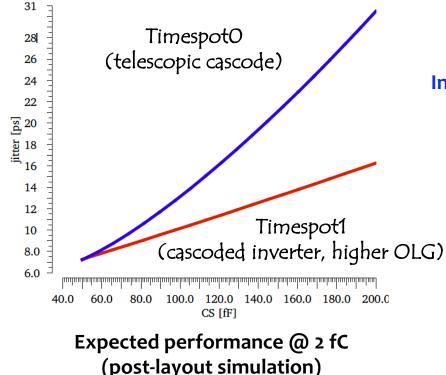

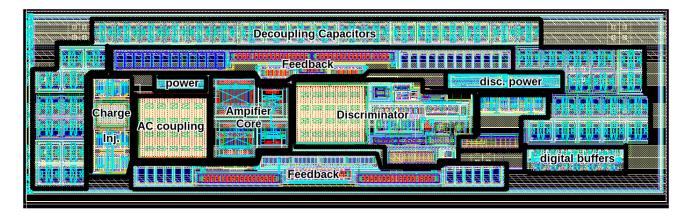

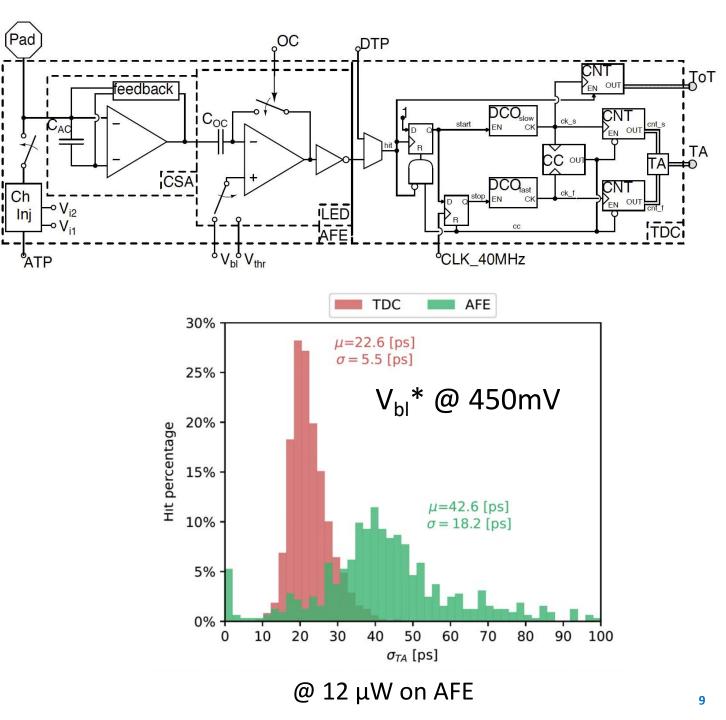

# **Timespot1: Analog Front End**

Inverter core amplifier with double Krummenacher FB

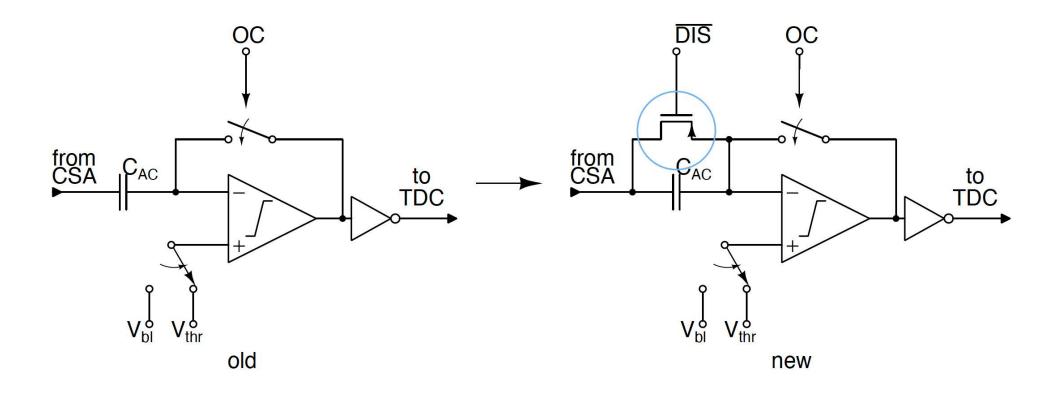

Leading Edge Discriminator with Discrete-time Offset-Compensation for threshold uniformity OC procedure: 250 ns every ≤800 µs (it causes dead time)

Programmable power from 2.5 to 32  $\mu$ W/channel

Inverter-based Charge Sensitive Amplifier (CSA) with DC current compensation.

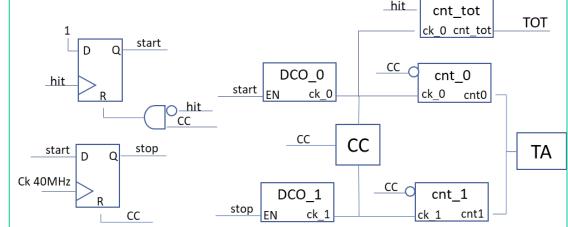

### **Timespot1: TDC**

Fully digital design, standard-cell based

12-16<sup>th</sup> December 2022 High resolution, "low" To maximize sustainable rate, 1 TDC consumption TDC start per pixel channel has been based on 2 DCOs and a integrated hit Vernier architecture start hit CC Santa Fe NM, Max input rate = 3 MHz/pixel Max conversion time 300 ns stop start 23 bits output word (ToA + ToT)  $TA = (cnt_0 - 1) T_0 - 1$ ToT resolution  $\approx 1$  ns Ck 40MHz  $-(cnt_1-1)T_1$ stop CC Expected power per rate 2022 200.0 180.0 clk 40 MHz Pixel 160.0 signal 140.0 TOT Lai – 120.0 Å The TDC gives the phase of the 100.0 signal wrt the 40MHz BX clock 80.0 TimeSPOT ASIC 38 µW @ 350 kHz The TDC and the counter use the 60.0 (LHCb max rate) 40.0 **Could be split among** same DCO-generated Clk (~1 GHz) more channels (?) 4 levels of Vernier precision ( $\Delta f$  in 20.0 DCOs) can be programmed. 0.0 2000 1000 3000 4000 Typical LSB 12 ps Hit Rate [kHz]

# Pixel architecture & characterization

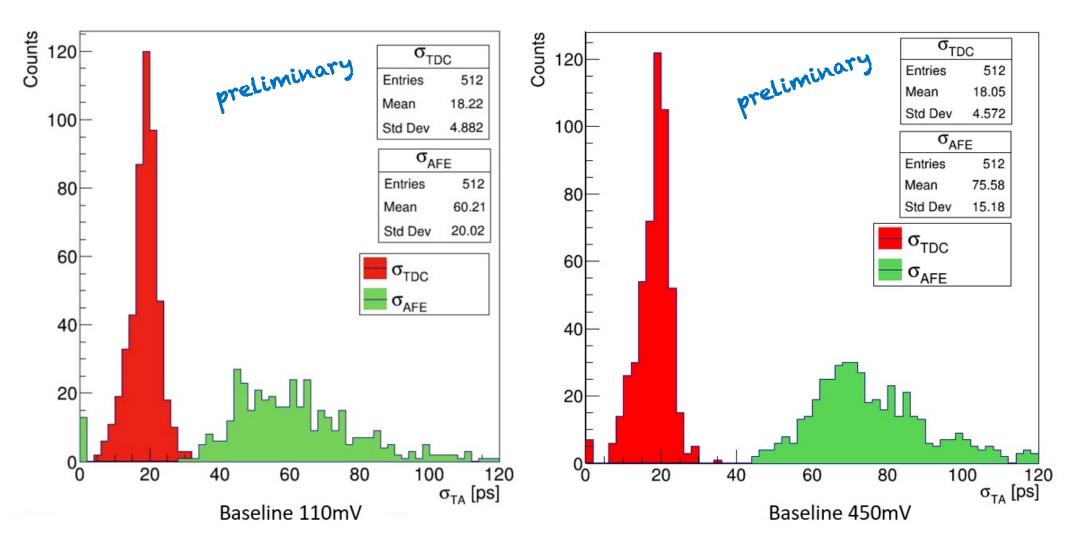

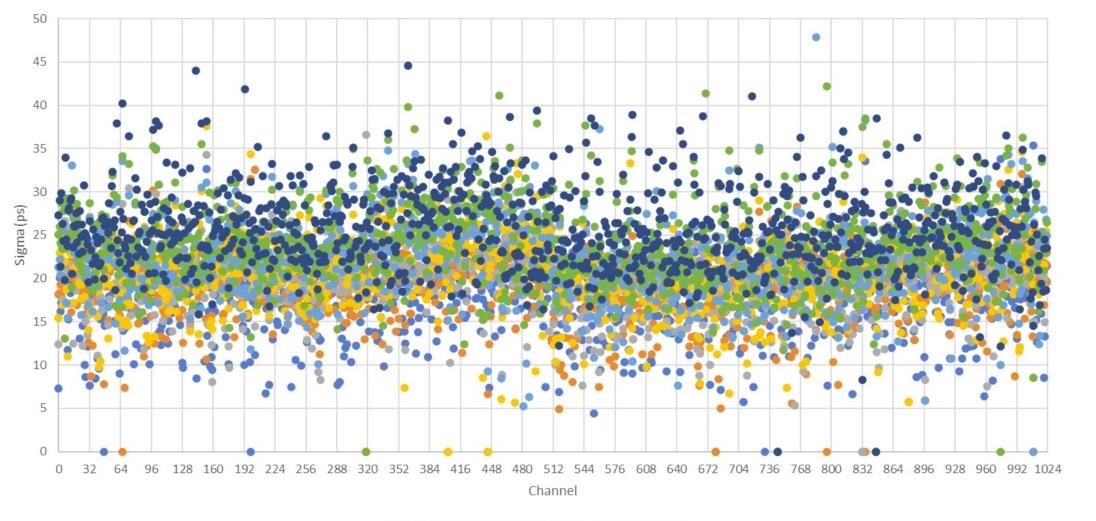

Time resolution (no sensor)

- The TDC has a typical σ<sub>t</sub> ≈ 20 ps, with a dispersion around 5 ps and is limited by the system clock jitter. As a consequence, no improvements are visible when increasing the Vernier precision

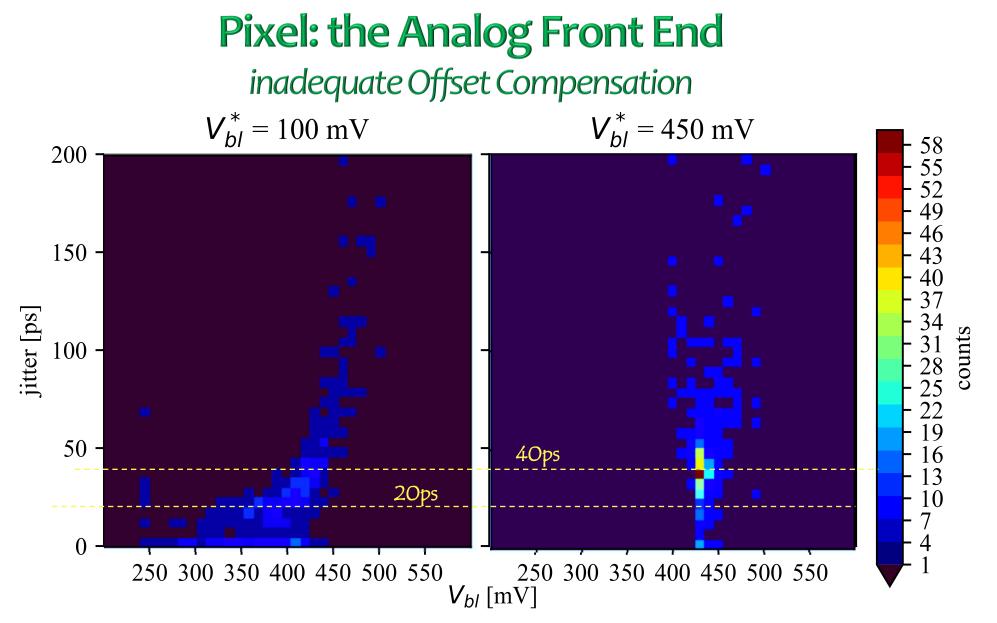

- The AFE  $\sigma_t$  is intrinsically below 20 ps but an identified bug in the Offset Compensation of the LE discriminator spoils  $\sigma_t$  in most of the channels (see next slide).

- In general, issues which are extrinsic to circuit design limit the very good resolution at the pixel level (clock distribution, OC bug). The pixel circuit design appears adequate to system requirements.

- When V<sub>bl</sub> is set at low values, in most of the channels, the OC circuit fails to charge the memory capacitance C<sub>OC</sub>.

- The discriminator is forced to work at high voltages, where it is band-limited

- The timing performance is heavily degraded

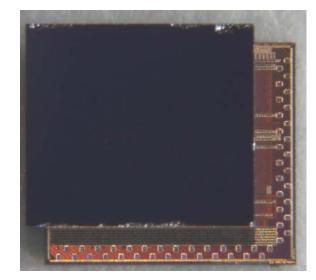

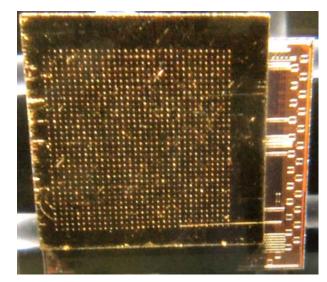

#### Timespot1 on 3D-trench silicon matrix

#### Timespot1 on 3D-column diamond matrix

# **Hybridized devices** with 3D sensors

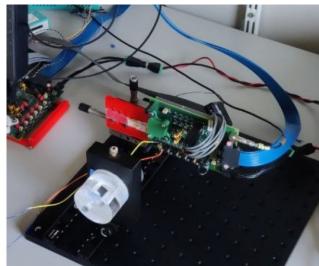

The test-bench PCB (named TSPOT1) operates also as a tracking station in the demonstrator

# **Hybridized devices** Cagliari test bench and ongoing tests

- The system is completed by a low-jitter clock distributing board and an aggregation board (Mezzanine), which hosts up to 8 boards/layers.

- The Mezzanine is connected onto a KC705 performing DAQ functionalities (up to 10 Gbps)

- Hybrids are being tested by internal pulsing system and beta radiactive source

- Subsequently they will be characterized under IR synchrounous laser setup in the lab

- Test beam is foreseen next spring at SPS (up to 8 stations, silicon and diamond hybrids)

Mezzanine (max 8 tracking layers/DUT) and KC705 FPGA readout board

Clock

distribution

board

Si5341

2 DUT on 2 TSPOT1 PCB

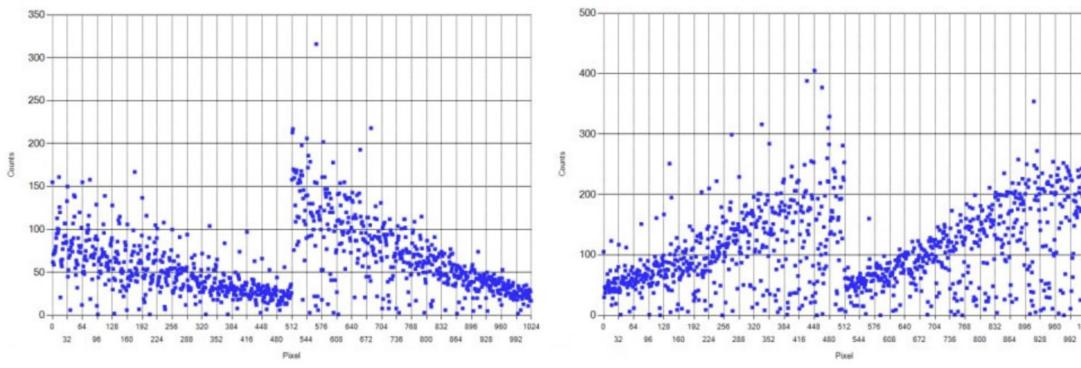

# Hybridized device under <sup>90</sup>Sr source

#### Off-centered <sup>90</sup>Sr source

# **Hybridized devices**

time resolution (2 fC pulses, sensors connected)

Same behaviour with slight worsening of timing performance. Performance is dominated by the discriminator

# **Conclusions and Outlook**

- At the pixel level, the Timespot1 ASIC shows an intrinsic timing performance around 20 ps, both on the AFE and TDC stages at a reasonably low consumption (≈ 12 µW on the AFE stage)

- 2. Leaving apart the (amendable) OC-bug, true limitations are due to global issues as clock jitter and power distribution (such as geographical disuniformities, dispersion of values, instabilities when power is increased)

- . As expected, verification methods at the full ASIC level are crucial in this technology

#### **FUTURE:**

- A test beam with up to 8 tracking station is in preparation for Spring 2023

- We are already working (**IGNITE** project) at the next version of the ASIC, with corrected features, fast readout (by integrated photonics), radiation hardening features and larger area (64x64 or 128x128 pixel matrix).

- The **IGNITE** ASIC aims at addressing the full requirements for 4D-tracking. Discussions on specs are ongoing in the present months. Many «users» interested (LHCb, HIKE, CMS-PPS, CMS-Endcap, ATLAS-AFP)

(modified)Timespot1 Matrix (32x32)

- Future advancement → minor tweaks on the current architecture could lead to a resolution better than 30 ps.

- Improve core discriminator.

- Implement a reset transistor.

- Improve the threshold setting switch.

● Sig7 ● Sig6 ● Sig5 ● Sig4 ● Sig3 ● Sig2 ● Sig1

Distribution of sigmas depending on channel position and pulse phase (1 to 7)

#### Res=3 - All pixels - Test Point=All - Points 100

S. Cadeddu, INFN Cagliari