Ivan Berdalovic (ESR8, CERN)

# DESIGN AND CHARACTERISATION OF RADIATION-HARD MONOLITHIC SENSORS IN TOWERJAZZ 180 NM CMOS

European Commission

16/09/2019

## Outline

- Introduction

- The ATLAS High-Luminosity upgrade

- CMOS pixel sensors

- Sensors in the TowerJazz 180 nm technology

- The MALTA pixel sensor

- Analogue front-end design

- Measurements of front-end performance

- MALTA asynchronous readout architecture

- Architecture timing measurements

- Lab tests and testbeam results

- The miniMALTA prototype

- New features and measurements

- Outlook and conclusion

### Introduction

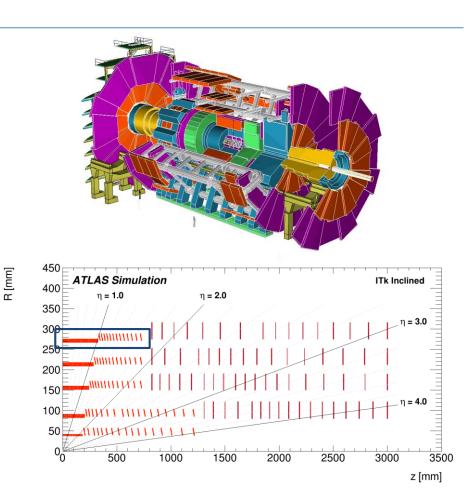

- The ATLAS experiment will undergo a major upgrade for the High-Luminosity LHC phase

- CMOS pixel sensors were considered for the outermost layer of the ITk pixel detector

- Requirements for layer 4:

- High efficiency (>97 %)

- Fast timing (<25 ns bunch crossing time)</li>

- High hit rate capability (hit rate ~2 MHz/mm<sup>2</sup>)

- Low power consumption (<0.5 W/cm<sup>2</sup>)

- Radiation tolerance (1.5x10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> NIEL and 80 Mrad TID)

- SEU robustness

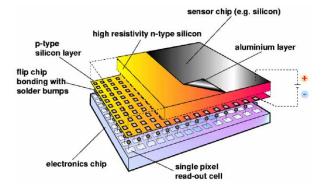

## Hybrid vs. CMOS pixel detectors

• Hybrid pixel detectors

- Used in the majority of present systems

- Sensor and readout on separate chips can be optimised separately (different materials, high sensor bias voltages)

- Fast charge collection, good radiation tolerance

- Complex and costly assembly due to fine-pitch bump bonding

CMOS monolithic pixel sensors

- Sensor and readout integrated into the same silicon die (large or small collection electrode)

- High granularity, low power consumption, significant reduction in material budget

- No bump-bonding: easy integration, lower cost

- Recent progress in radiation hardness

### 16/09/2019

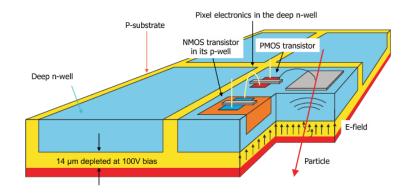

### Sensors in the TowerJazz 180 nm technology

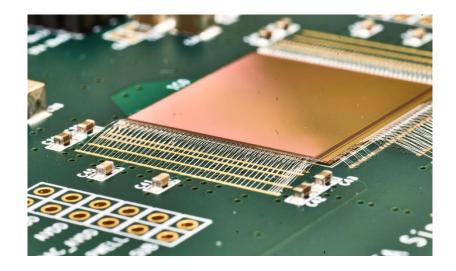

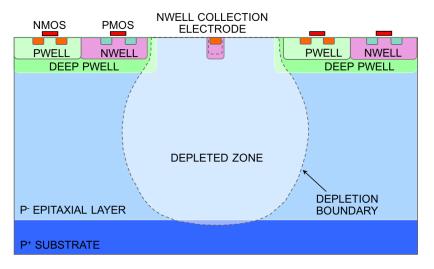

- Small collection electrode design with high resistivity (> 1 kΩ cm) p-type epitaxial layer (25 μm thick → MIP charge ~1500 e<sup>-</sup>)

- Deep p-well shielding n-well to allow full CMOS

- **Reverse bias** (~6 V) to further reduce input capacitance and increase depletion volume

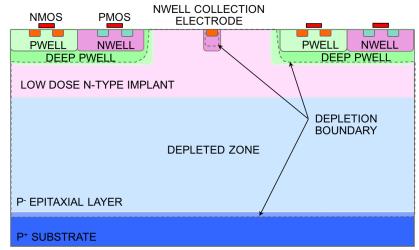

- Modified process adding a planar n-type layer to improve depletion under the deep p-well near the pixel edges

- A fully depleted epitaxial layer results in faster charge collection and **better radiation tolerance**

- No circuit or layout changes required

W. Snoeys et al. https://doi.org/10.1016/j.nima.2017.07.046

### 16/09/2019

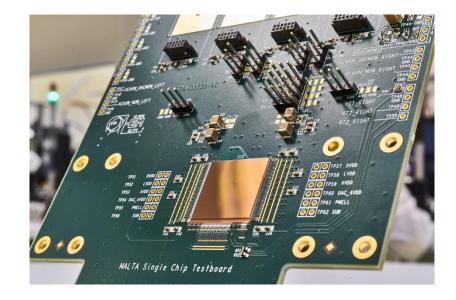

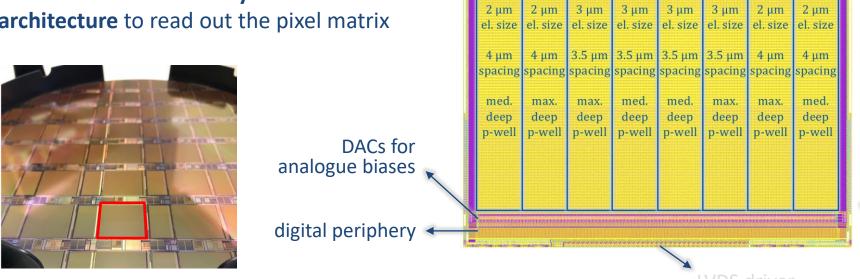

## MALTA pixel sensor

- The 512x512 pixel matrix divided into 8 sectors with slight differences in electrode size, spacing and reset mechanism

- Design based on a low-power analogue front-end and a novel asynchronous architecture to read out the pixel matrix

SO

diode

reset

**S1**

diode

reset

S2

diode

reset

\$3

diode

reset

**S4**

**PMOS**

reset

**S5**

PMOS

reset

**S6**

**PMOS**

reset

\$7

**PMOS**

reset

18.6 mm

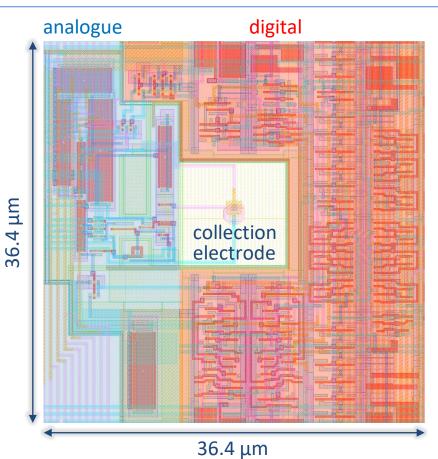

## The MALTA pixel

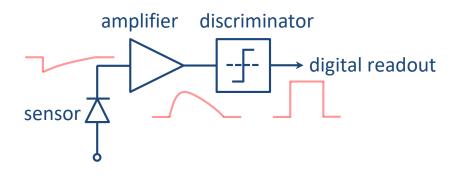

Sensor and analogue front-end (shaperamplifier and discriminator) shielded from digital part to minimise crosstalk

## Analogue front-end design

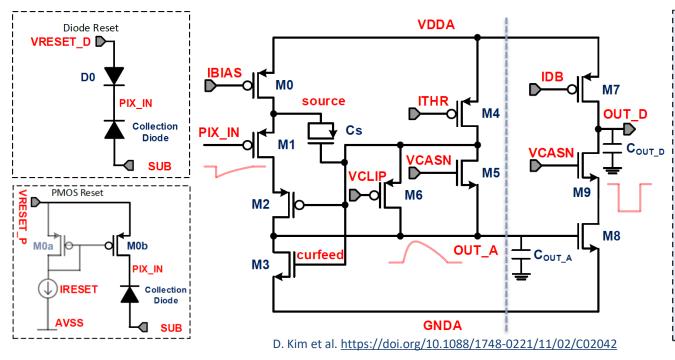

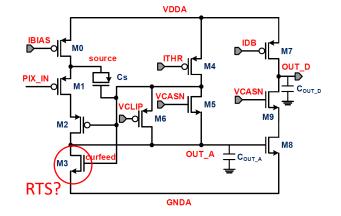

- Fast, low power, low noise amplifier based on a previous design for the ALICE upgrade (shaping time ~25 ns, power <1 μW/pixel)</li>

- Designed for a threshold of ~200 e<sup>-</sup> with a simulated ENC noise of <10 e<sup>-</sup> and RMS channelto-channel threshold variation of ~10 e<sup>-</sup>

- Input node reset using either a diode or a PMOS

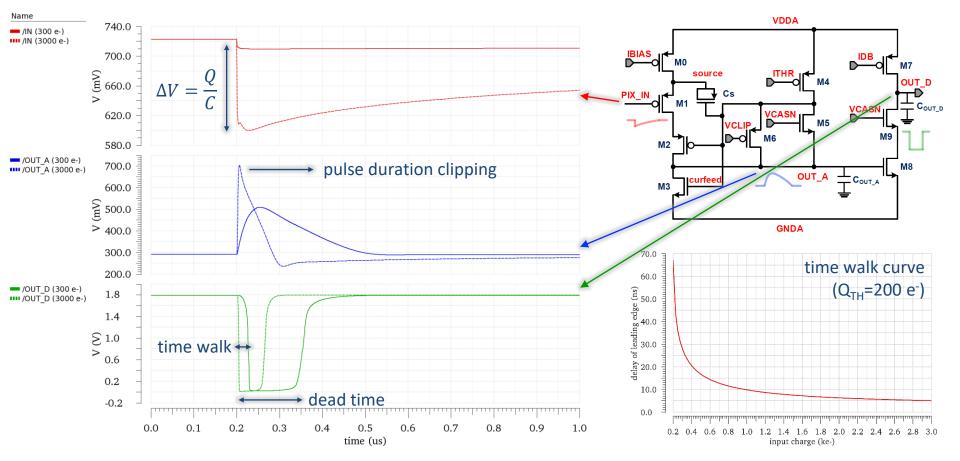

- M1 acts as a source follower, amplification caused by transfer of charge from C<sub>s</sub> to C<sub>OUT\_A</sub> (C<sub>s</sub> >> C<sub>OUT\_A</sub>)

- M3-M5 form a lowfrequency feedback to stabilise OUT\_A

- M6 clips the analogue pulse for high input charges

- M7-M9 form a simple discriminator

### 16/09/2019

## Analogue front-end timing optimisation

## Analogue front-end timing measurements

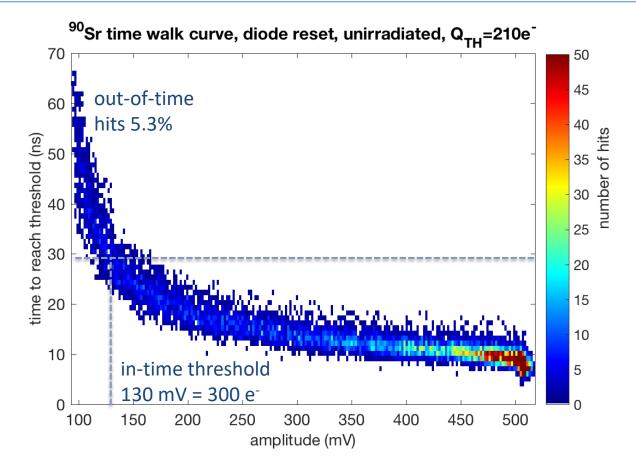

- Time walk measurement performed with a <sup>90</sup>Sr source using special pixels to monitor the analogue output

- With a threshold of 210 e<sup>-</sup> the in-time threshold is

300 e<sup>-</sup> (20% of MIP charge)

- Out-of-time hits mostly due to charge sharing (measurement done on a single pixel)

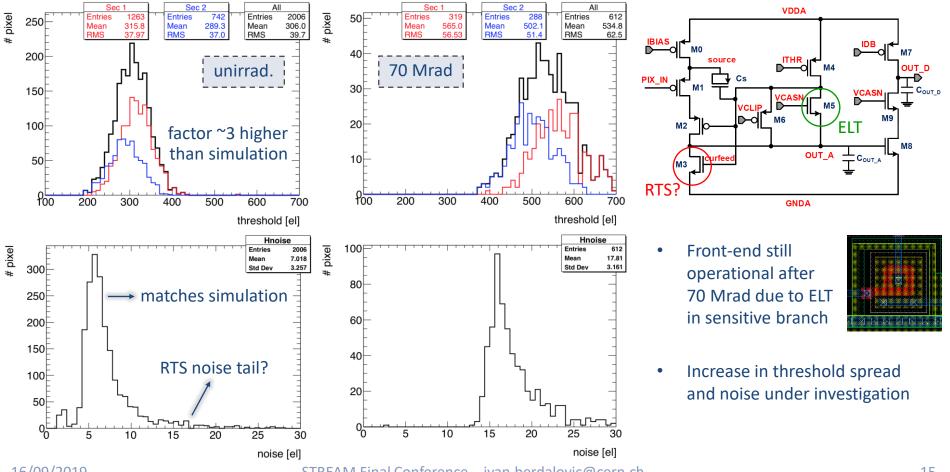

## Front-end response before and after irradiation

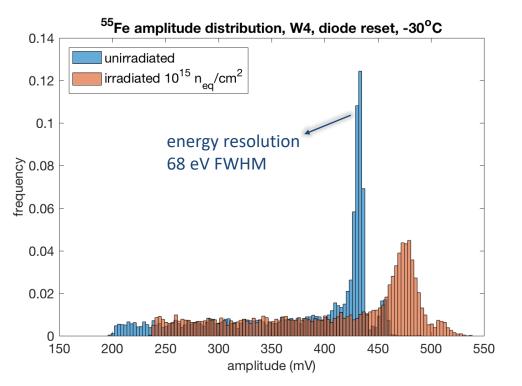

- MALTA chips irradiated with neutrons up to 10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup> (with a background TID of 1 Mrad)

- Monitoring pixels also used to study sensor and front-end response to <sup>55</sup>Fe source before and after irradiation

- Characteristic  $K_{\alpha}$  and  $K_{\beta}$  peaks of the source clearly visible even after irradiation

- Irradiated front-end shows a slightly higher signal due to decreasing input capacitance, as well as an increase in noise

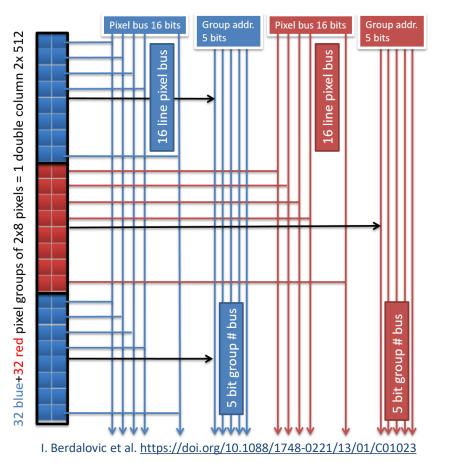

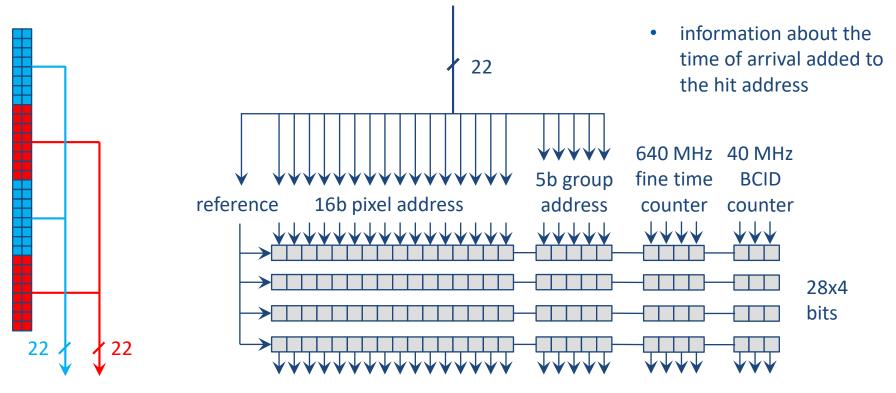

## MALTA asynchronous readout architecture

- Front-end discriminator outputs are injected into double-column digital logic generating a short pulse (0.5-2 ns)

- Data is transmitted **asynchronously** over high speed buses without clock distribution over the active matrix to **save power**

- 2 independent buses serve alternating 2x8 pixel groups (one bus for the red groups and another for the blue groups)

- 22 bits per bus: reference (1b) + pixel pattern (16b) + group address (5b)

- In-pixel logic includes hit arbitration in case of simultaneous hits within one 2x8 group

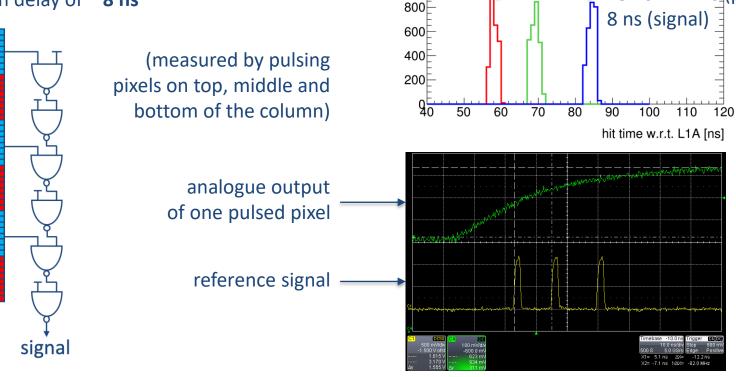

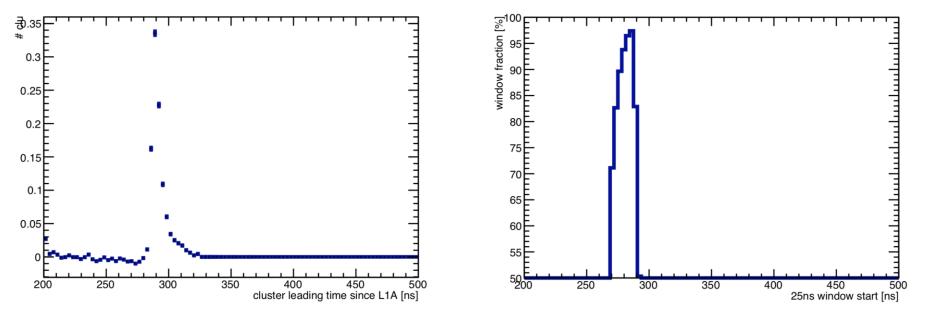

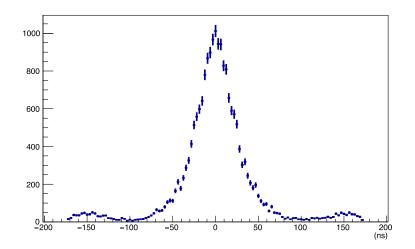

### Asynchronous readout architecture – measurements

Hit signals from the pixels are buffered and arrive at the end-of-column with a maximum propagation delay of ~8 ns

counts

1200

1000

pulse

STREAM Final Conference - ivan.berdalovic@cern.ch

25 ns = 17 ns (pulse) +

### Front-end and readout timing measurements

Time walk can also be obtained by measuring the delay of digital output signals with respect to a fast trigger (scintillator)  In-time efficiency for leading signals in clusters reaches 98% with a 300 e<sup>-</sup> threshold (no correction for the 8 ns propagation delay down the column)

STREAM Final Conference – ivan.berdalovic@cern.ch

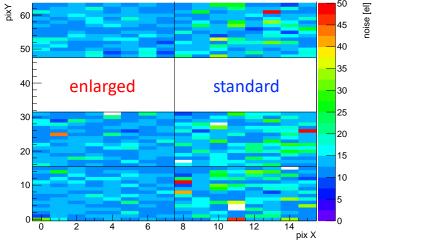

### Threshold dispersion and noise before and after TID

16/09/2019

STREAM Final Conference – ivan.berdalovic@cern.ch

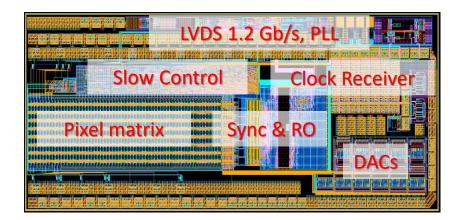

## The miniMALTA prototype

- The next small prototype after MALTA, contains:

- A 64x16 pixel matrix with the same designs as MALTA, but enlarged transistor to fix RTS noise

- A block to synchronise signals at the periphery

- A priority encoder readout and serialiser to send the data out at 1.2 Gb/s

- A new modular DAC design (Francesco)

- Process modifications for improved efficiency after irradiation (Roberto)

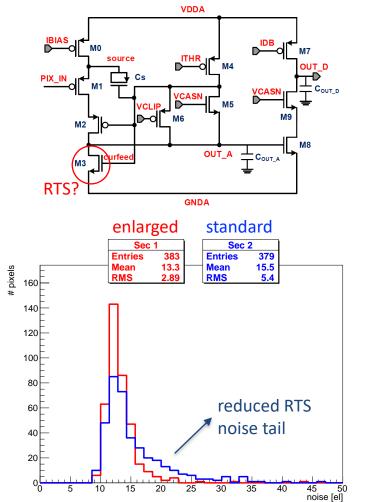

## Front-end design changes

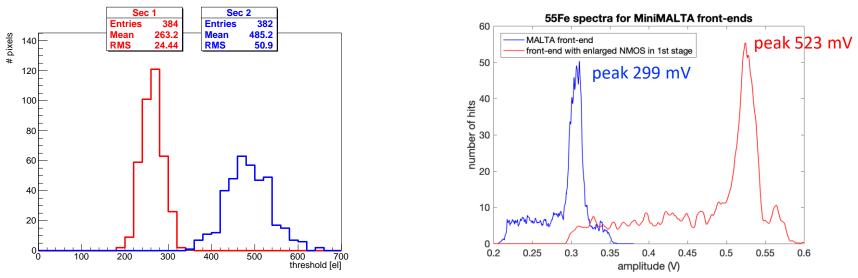

- Two sectors with different front-end designs: one with enlarged M3 and one with the same front-end as MALTA

- Noise distributions after irradiation show a significant reduction in RTS noise with enlarged M3

## Front-end design changes

- A larger length of M3 means lower output conductance on OUT<sub>A</sub>, leading to a higher gain (about 30% in simulation)

- In measurements, the gain and threshold difference is around a factor of 1.7, allowing lower thresholds to be achieved more easily

## Synchronisation in miniMALTA

• Hits at the output of the MALTA double column stored asynchronously into FIFO RAM memory and read out synchronously

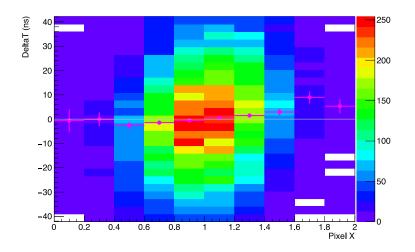

### Measurements on the synchronisation block

- Functionality already proven by reading out the correct address data in threshold scans and beam tests

- Timing information stored in the synchronisation memories tested with a 320 MHz fast clock (resolution of ~3 ns)

- Example distribution of timing difference between hits in horizontal clusters of 2 pixels (close to 0 near the pixel borders, < 50 ns towards the pixel centres)</li>

## **Conclusion and outlook**

- The MALTA CMOS pixel sensor was developed in view of the ATLAS High-Luminosity upgrade

- The large pixel matrix implements a fast, low-power analogue front-end and a novel asynchronous readout architecture

- The chip has been extensively characterised in lab measurements and testbeam, and shows good results in terms of front-end performance and readout capability

- The miniMALTA prototype includes front-end improvements and a synchronisation block at the chip periphery, all of which are tested and proven to work

- Designs in TowerJazz 180 nm continue towards large-scale pixel detector chips with asynchronous and synchronous architectures (MALTA V2, TJ Monopix V2)

### Thank you for your attention!

## **QUESTIONS?**