#### Progress and Advances in Serial Powering of Silicon Modules for the ATLAS Tracker Upgrade

John Matheson

**Rutherford Appleton Laboratory**

On behalf of the SP Community

Thanks to Martin Gibson (RAL), Richard Holt (RAL), Dave Lynn (BNL), Peter Phillips (RAL) and Giulio Villani (RAL)

# Outline

- powering issues for the ATLAS strip tracker upgrade

- the serially powered (SP) detector stave

- shunt regulator options

- protection against chain failure

- current source developments

- the SP stavelet program

- SP stavelet test results

- summary and conclusions

# The present SCT

- 4088 Detector Modules

- 3.2M channels

- Independent Powering

- 4088 cable chains

- 22 PS racks

- 4 crates / rack

- 48 LV and 48 HV channels/crate

- Overall efficiency ~40%

- Cable R => voltage drops

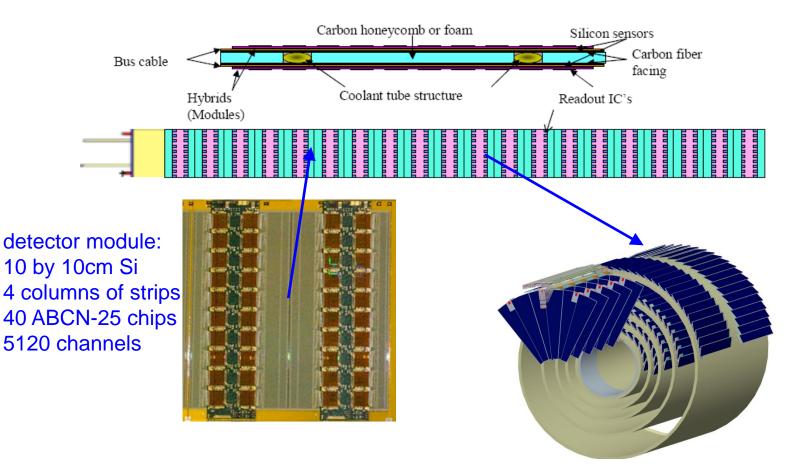

#### current SCT module design

**Barrel Modules**

Forward Modules

Upgrade Tracker: need 34 M channels to cope with increased luminosity

# Upgrade strip tracker: Stave and Petal Concept

detector staves arranged into barrels detector petals arranged into discs

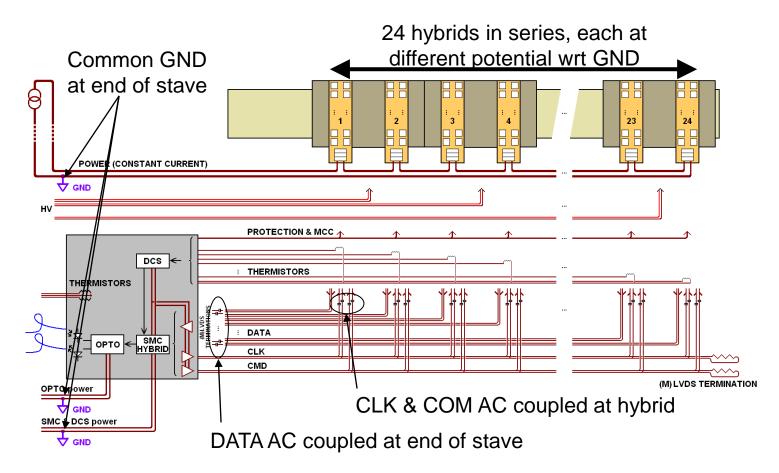

#### **Serially Powered Stave Architecture**

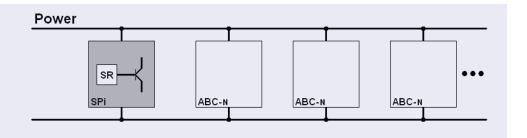

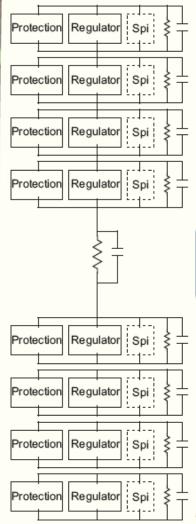

staves carry 12 detectors, 24 readout hybrids per side each hybrid carries 20 ABCN ROICs each module must carry a shunt regulator to keep supply V constant powering by DC-DC converter is a competing/complementary option currently prototyping 4 module "Stavelets"

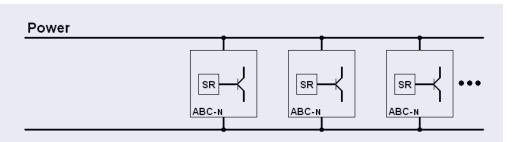

# Shunt Regulator Architectures with ABCN-25

#### • Hybrid with Shunt "W"

- Use each ABCN-25 integrated shunt regulator

- Use each ABCN-25 integrated shunt transistor(s)

#### • Hybrid with Shunt "M"

- Use one external shunt regulator

- Use each ABCN-25 integrated shunt transistor(s)

- Two (redundant) shunt transistors, 140mA each

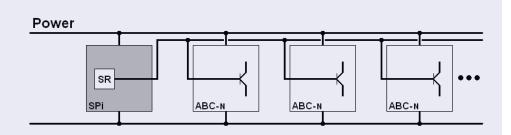

#### • Hybrid with SPi (or similar)

- Use one external shunt regulator

- Use one external power transistor

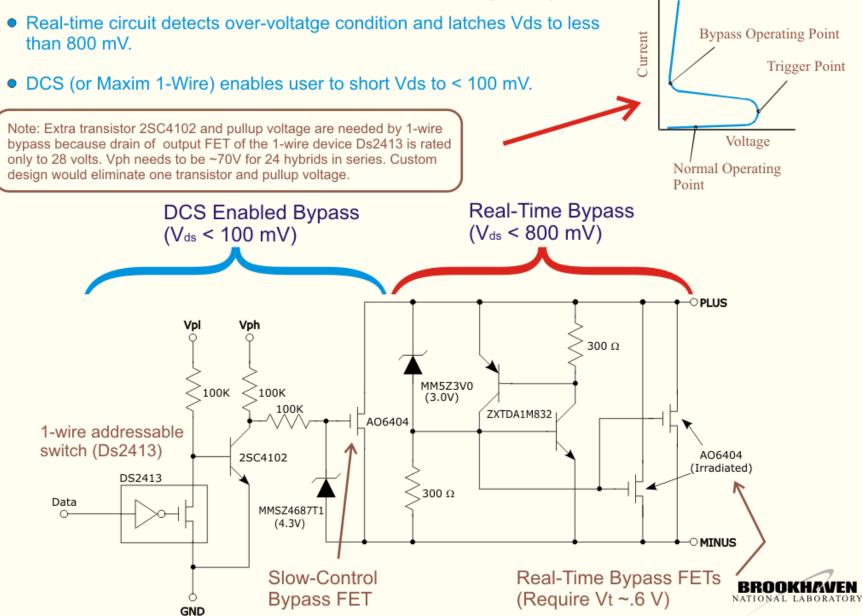

## Protection of SP against faults

- What happens if a module fails open circuit?

- What happens if a module becomes a noise generator?

- How to turn modules on/off?

We could provide a system to "short out" each module under control of DCS

- Voltage across shorted module should be small

- Area of components and number of control lines must be small

- Protection circuit must draw minimal power when module active

- Automatic over voltage protection is desirable

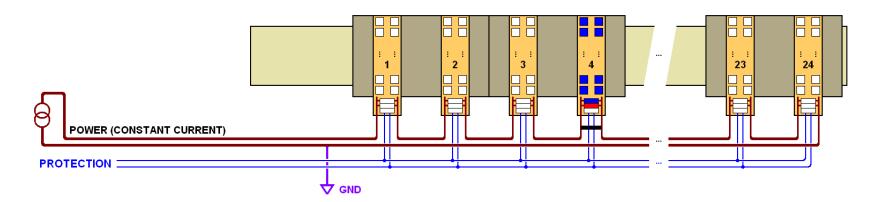

#### Power Protection Board(PPB) Circuit

## PPB system test studies

SP System Test Board

#### Protection Circuit- Protoype I

#### **Regulator Board**

#### System Test Board

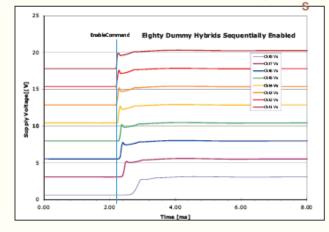

•Mimics 8 hybrids + 8 virtual hybrids

•16 x 2.5 V = 40 volt operation •Test real-time circuits; allows 1wire controlled "open circuits" in variety of "hybrid" locations •Test multiple 1-wire bypass circuits

•Mimics clock dependent variable module current loads for noise tests •SPi chip compatible

Study power-up issues

Note: Thermal issues limit current to 2.5 Amps

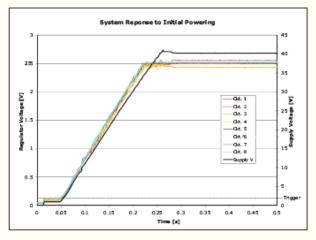

## PPB system test results

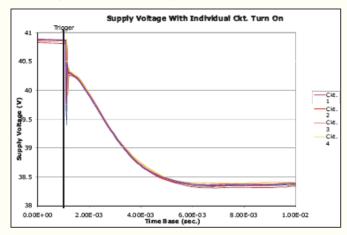

Simultaneous Power-Up

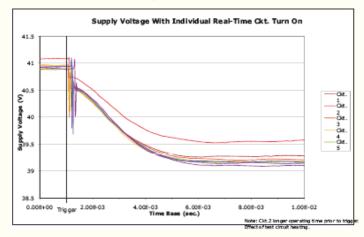

Change in Supply Voltage When Hybrid is DCS Bypassed

#### Sequential Power-Up Via 1-Wire Bypass Disable

Change in Supply Voltage When Real-Time Bypass is Enabled

System Tests all show protection circuit behaves as expected in a serial chain of dummy hybrids.

More details in power working group session

## **Programmable Constant Current source**

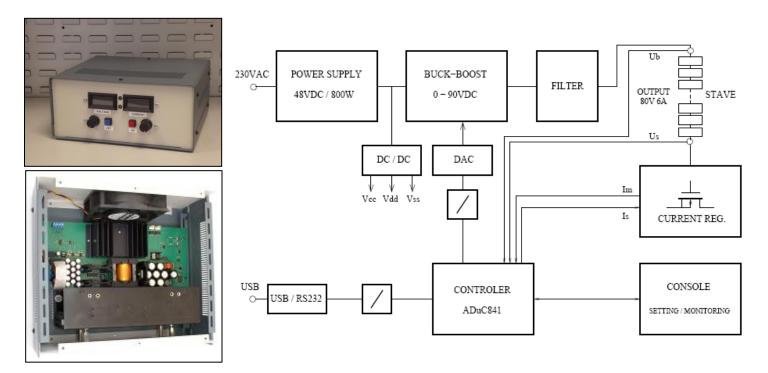

- programmable current source has been prototyped (J.Stastny, ASCR)

- specifically designed for stave09 (ABCN-25), output up to 80V at 6A

- current setting resolution 2mA

- isolated USB interface

- overvoltage protection

- it should work well also for ABCN-13

- now under test with stavelets at RAL

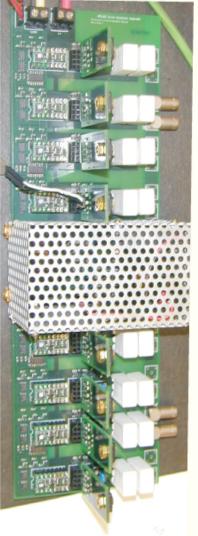

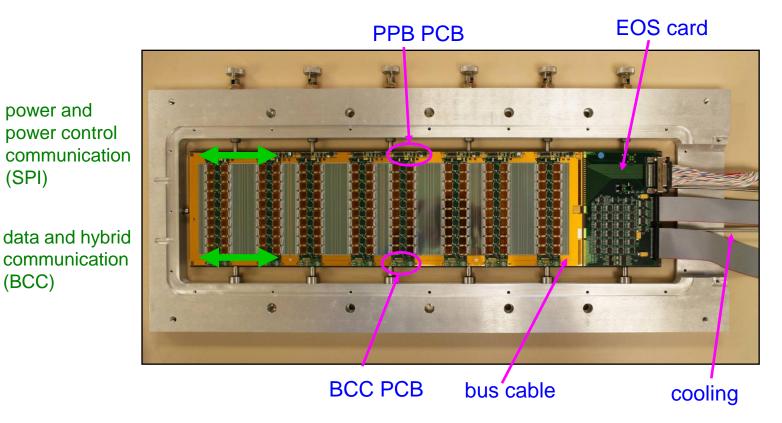

# The Stavelet with ABCN-25 readout

Allows comparison of: Different power configurations, Different bus cable designs, Different grounding and shielding concepts

Stavelets allow option choices for later stave construction

One built, second under costruction at RAL

PPB carries protection and power plugin

# **Power Protection board (PPB) and plugins**

# **PPB** dual redundant distributed shunt plugin SPI plugin PPB provided by BNL, implements protection scheme and power connectivity Hybrid contains basic control circuit for distributed shunt – used for stavelet tests

Plug in boards will be used for testing other powering schemes – coming soon !

serial power interface chip (SPI) Fermilab

so far

#### Stavelet GAIN @2fC, JS CS II@5A Run 1108 Scan 3 After Trimming, reading all hybrids simultaneously, column 1 strip order corrected. Gain (Hybrid 6 Column 0) Gain (Hybrid 4 Column 0) Gain (Hybrid 2 Column 0) Gain (Hybrid 0 Column 0) h\_gain\_0\_0 ries 1280 en 639.3 1280 1280 1280 635.4 130 130 130 130 120 S 120 Gain 120 5 120 110 110 110 100 100 100 100 105 mV/fC 108 mV/fC 106 mV/fC 108 mV/fC 80 E 70 🗄 60 E 1200 Channel 1200 Channel 1200 1200 Channel Channel Gain (Hybrid 6 Column 1) h\_gain\_6\_1 Gain (Hybrid 4 Column 1) h cain 4 1 Gain (Hybrid 2 Column 1) h\_gain\_2\_1 Gain (Hybrid 0 Column 1) h\_gain\_0\_1 1280 640.1 1280 1280 638.3 369.6 1280 Entries la en 130 130 E 130 130 120 E .<u>5</u> 120 E ⊑ 120 E .⊆ 120 E 100 8 100 100 90 E 90 106 mV/fC 108 mV/fC 107 mV/fC 108 mV/fC 80 E 70Ē 60 60 1200 1200 Channel Channe Channel Channel h\_gain\_7\_4 h\_gain\_1\_0 Gain (Hybrid 5 Column 0) h\_gain\_5\_0 Gain (Hybrid 3 Column 0) h\_gain\_3\_0 Gain (Hybrid 7 Column 0) Gain (Hybrid 1 Column 0) 1280 636.1 1280 1280 639.9 369.3 Entrie 128 140 638.6 370.4 - 140 636.1 369.2 130 E 130 130 130 120 - 120 E .5 120 -<u>5</u> 120 100 104 mV/fC 107 mV/fC 107 mV/fC 107 mV/fC 80 Ē юE 1200 Channel Channel Channel Channel h gain 7 1 h\_gain\_5\_1 h gain 3 1 h\_gain\_1\_1 Gain (Hybrid 7 Column 1) Gain (Hybrid 5 Column 1) Gain (Hybrid 3 Column 1) Gain (Hybrid 1 Column 1) 1280 1280 639.6 370.3 128 Entries 1280 637.9 370.6 \$35.9 637.4 369.7 Mean RMS 130 Ē 130 E 130 120 120 ≣ 120 E 120 121 110 100 100 100 90 F 90 F 107 mV/fC 105 mV/fC 106 mV/fC 106 mV//C 80 E 80 80 E 70 Ē 70 60 E 60 Anomalous Cal Line 50 E 1200 1200 1200 1200 Channe Channe Channel Channe

Tacillies Council

14

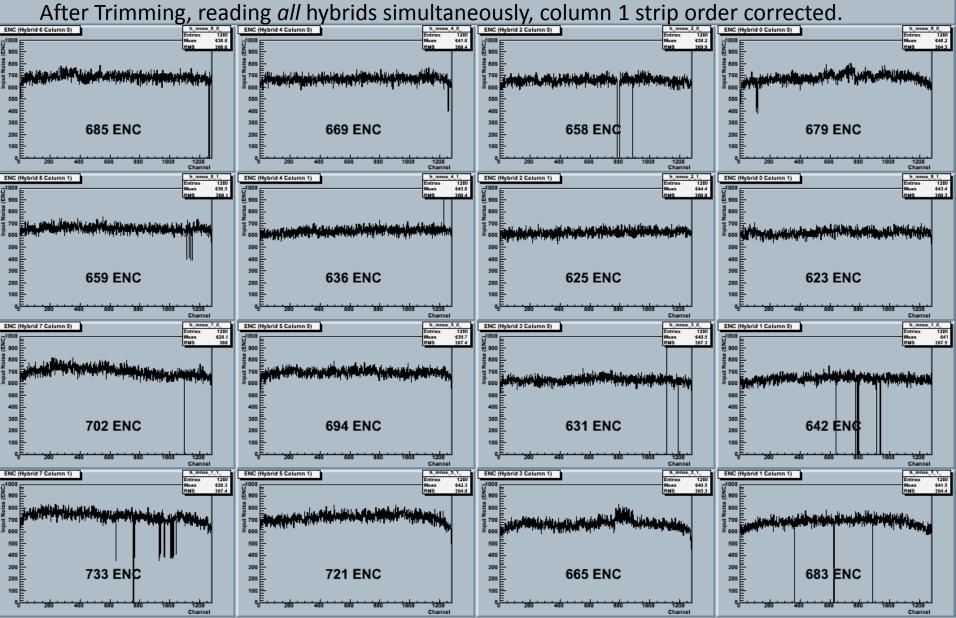

# Stavelet ENC @2fC, JS CS II@5A

Run 1108 Scan 3

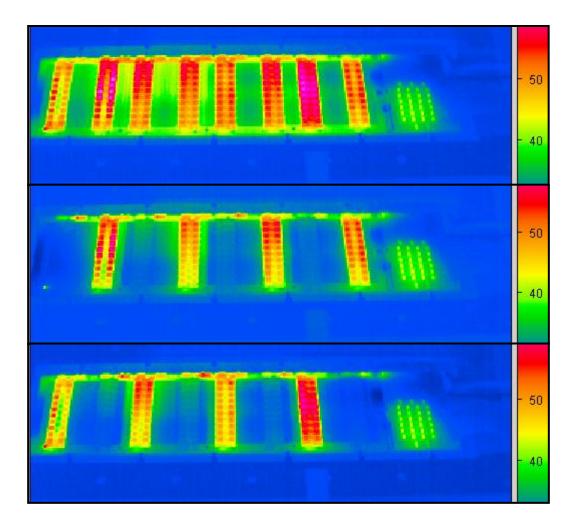

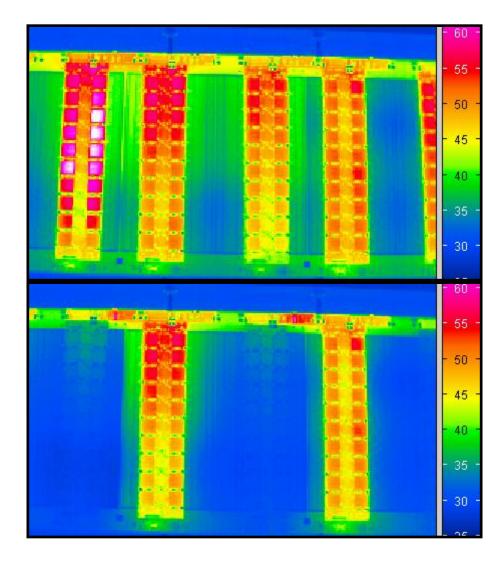

#### Thermal images of stavelet in operation

#### All hybrids on

22.7V 5.09A

# Slow control disables odd hybrids

12.7V 5.09A

Slow control disables even hybrids

## Thermal images of slow control bypass in operation

0.5 W

slow control bypass on: P = VI =100mV \* 5A = 0.5W

thermal images show slow control bypass working as expected

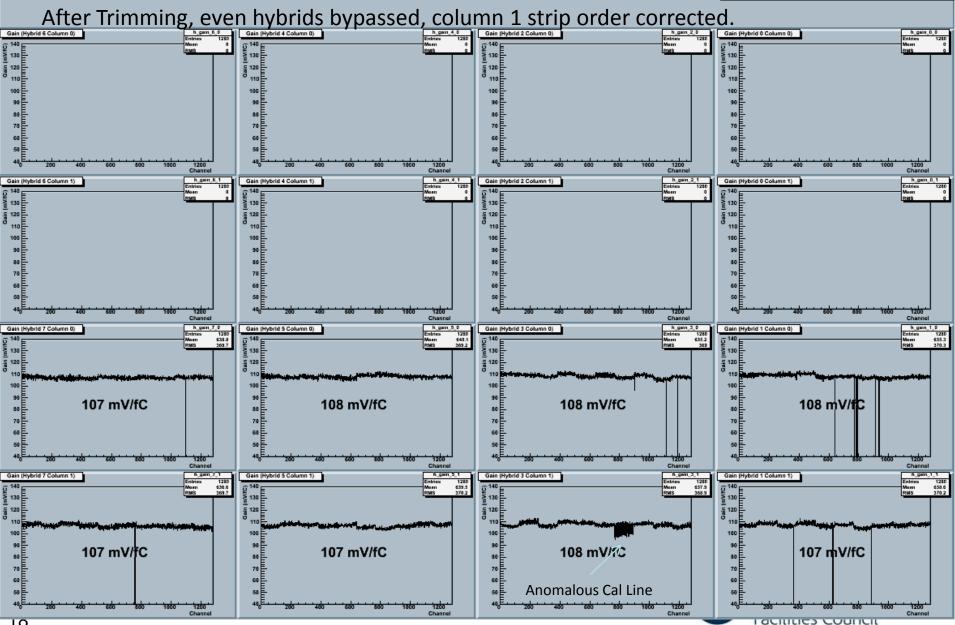

#### Stavelet GAIN @2fC, JS CS II@5A

#### Run 1113 Scan 3

10

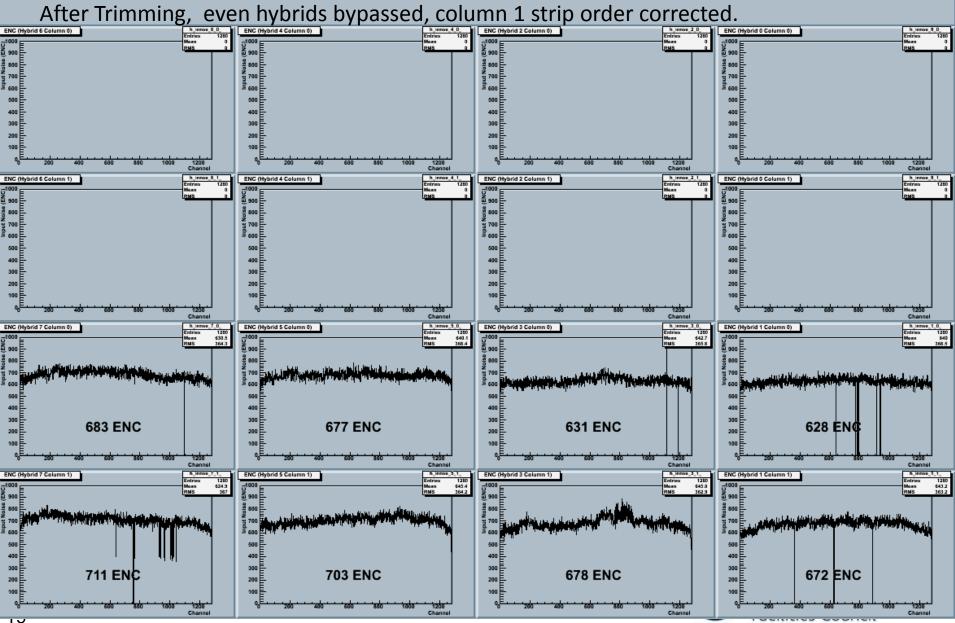

#### Stavelet ENC @2fC, JS CS II@5A

Run 1113 Scan 3

## Summary and Next Steps

- Progress continues with Serial powering for the tracker Upgrade

- ABCn-25 chips contain custom SP components

- A protection system has been implemented using COTS components

- The protection system also implements slow control of powering

- A custom current source has been prototyped

- The first test stavelet has been built

- Stavelet working well so far, no excess noise. Modules can be turned on and off independently. Studies continue.

- Stavelets will allow refinement of architecture for a full SP stave prototype

- A modified stavelet is being designed (R.Wastie et al.) to allow DC-DC tests (with G.Blanchot, F.Faccio) and will be built asap

# Spare slides

# Power Requirements with Modern Process Technologies

|                   |                                |                       |                        |                                                                                   | Power per 128 channel chip         | per channel |

|-------------------|--------------------------------|-----------------------|------------------------|-----------------------------------------------------------------------------------|------------------------------------|-------------|

| In ATLAS SCT      | ABCD<br>(0.8µm, biCMOS)        | Digital:<br>Analogue: | 4.0 volts<br>3.5 volts |                                                                                   | => 4.0 x 35 + 3.5 x 74<br>= 399 mW | 3.1 mW      |

| Present Prototype | <b>ABCN25</b><br>(0.25μm CMOS) | Digital:<br>Analogue: | 2.5 volts<br>2.2 volts | 1 1 1 1 1 77                                                                      |                                    | 2.3 mW      |

| Proposed          | ABCN13<br>(0.13μm CMOS)        | Digital:<br>Analogue: |                        | <ul><li>**51 mA per chip (estimate)</li><li>**16 mA per chip (estimate)</li></ul> | => 0.9 x 51 + 1.2 x 16<br>= 65 mW  | 0.5 mW      |

ABCN25: Vdig > Vana Idig >> Iana

If we generate Vana from Vdig using LR:

- 27mA \* 0.3V = 8.1mW per chip

- 3% of chip power

ABCN13: Vana > Vdig Idig >> Iana If we generate Vdig from Vana using LR:

- 95mA \* 0.3V = 28.5mW per chip

- 44% of chip power

-

• Can we do better than this? Of course...

\*\* Power Estimates for an ABCN in 130nm Technology, Mitch Newcomer, Atlas Tracking Upgrade workshop, NIKHEF, November 2008 http://indico.cern.ch/getFile.py/access?contribId=16&sessionId=8&resId=0&materialId=slides&confId=32084

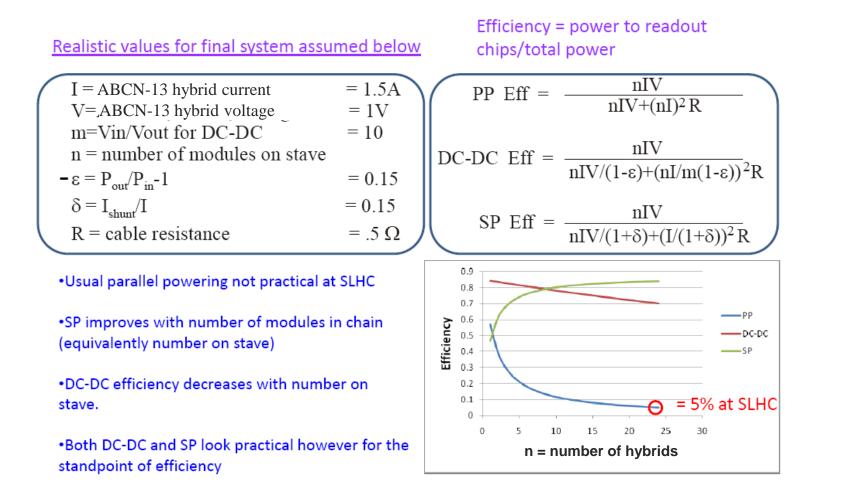

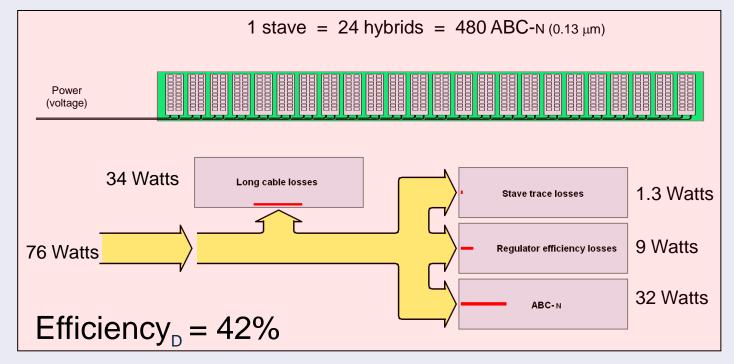

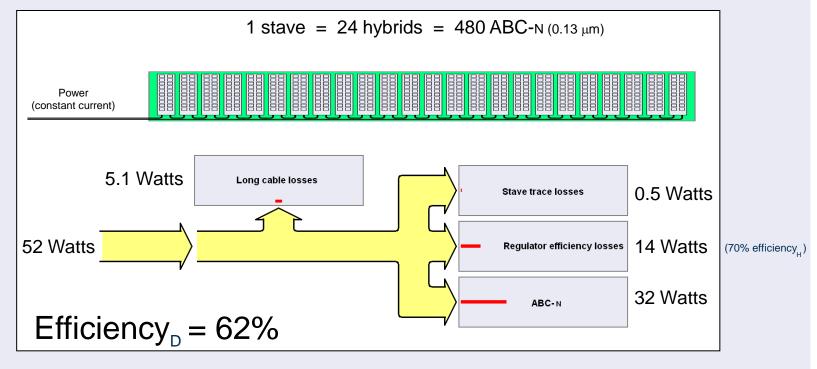

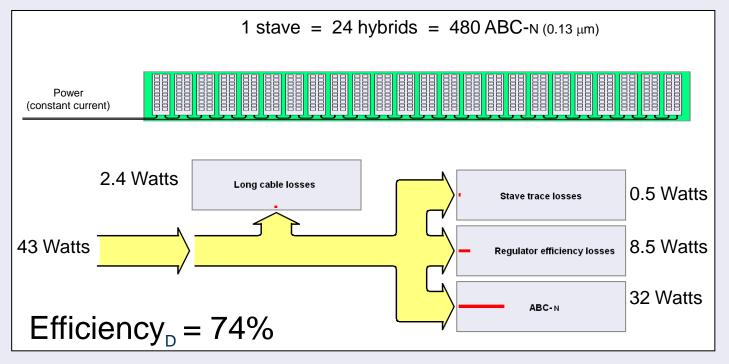

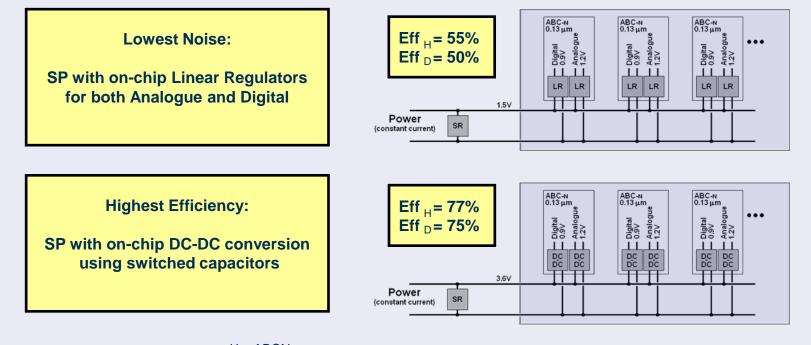

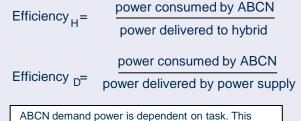

#### **Power Efficiency Comparison of Different Options**

these numbers for ABCN-13, i.e. next ASIC generation

# **Detector power efficiency**

#### Two-stage DC-DC powering (78% hybrid efficiency)

| Cables assumed to be 2 ohms total for each power line pair  |  |

|-------------------------------------------------------------|--|

| Regulator power = (1/eff - 1) x ABC power                   |  |

| Stave supply current = (32 + 9)watts / 10volts<br>= 4.1amps |  |

Numbers rounded

# **Detector power efficiency**

#### Serial powering a stave, (no DC-DC version)

| Cables assumed to be 2 ohms total for each power line pair           |

|----------------------------------------------------------------------|

| Regulator power = $(1/eff_{H} - 1) \times ABC$ power                 |

| Stave supply current = (32 + 14)watts / (1.2volts x 24)<br>= 1.6amps |

Numbers rounded

# **Detector power efficiency**

Serial powering a stave, (higher voltage, with DC-DC version)

Cables assumed to be 2 ohms total for each power line pair Regulator power =  $(1/eff_{H} - 1) \times ABC$  power Stave supply current = (32 + 8.5)watts / (1.6volts x 24) = 1.1amps

Numbers rounded

# Two possible future SP implementations

ABCN demand power is dependent on task. This will normally mean a shunt regulator will dissipate some power to maintain voltage under all conditions.

Some assumptions: Cable resistance 2 ohms for each line pair, SR = 85%, low current DC-DC = 90%, high current DC-DC = 85% Bus cable traces 7.5mm wide, 18 micron Cu chip power is that projected for 130nm ABCn

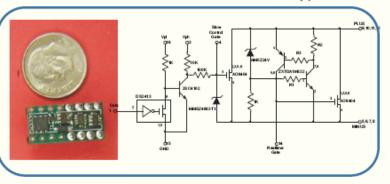

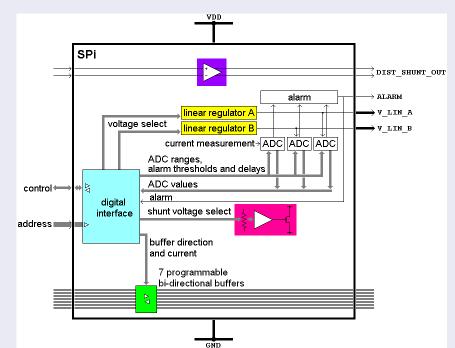

## The SPI chip – a serial power test bed

# **SPi (Serial Power Interface):** Shunt regulator schemes **Data communication Power management Monitoring/alarms Designed by** Marcel Trimpl (FNL) Mitch Newcomer (U Penn)

2.7 mm

nm ↑

- flip chip, bump bonded

- 144 pads (68 I/O, 76 power)

- Sub-set used for each application

# Serial Powering system design

# **Current Source ver.2 specifications:**

Input Voltage Input Frequency **Input Power** Output Current range **Output Current Setting Resolution Output Current Settling Time** Voltage Compliance Voltage Resolution Output Current Ripple ( $P_k$ - $P_k$ ) Control Mechanical Dimensions (W x D x H) 90 - 264 VAC 47 - 63 Hz 800 W (max) 0 - 6 A2 mA< 2 ms0 - 80 V25 mV 10 mA (estimated max) Manual / Remote(USB) 305 x 280 x 133 mm

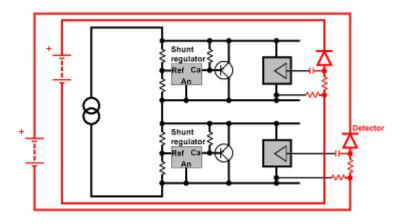

# Serial Powering and HV

Standard HV powering: one HV per hybrid

Alternative HV powering: one HV supply per 2 hybrids

Shunt

Shunt

÷

regulator

regulato

- Serial Powering is compatible with the use of a single HV supply for several modules

- Each sensor is dynamically connected to current source ground through output impedances of the chain of shunt regulators

- Low shunt output impedance is crucial to achieve good 'grounding' and reduce noise

Detector

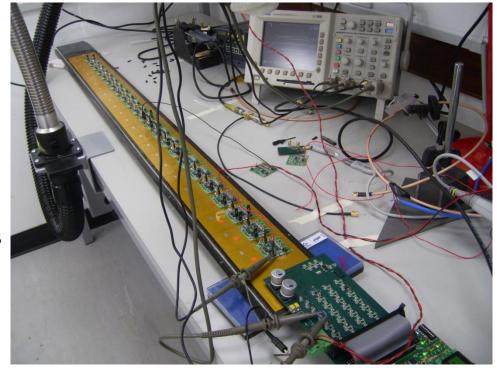

#### AC coupled data transmission - prototype bus tape

Whether we use SP or not, need to minimize number of signal traces in stave => multi-drop

Test stave at Oxford

Cu/kapton + Al screen layer

Send "TTC" data from FPGA  $\rightarrow$  24 dummy hybrids with receiver/drivers

Loopback data on dummy hybrids  $\rightarrow$  FPGA  $\rightarrow$  BERT.

Measure BERT for balanced and unbalanced data, parallel and serial powering

Balanced code works fine. M-LVDS + Serial powering + balanced code ok, ie no errors found in 3 locations tested (3,12 and 24).

Science & Technology Facilities Council

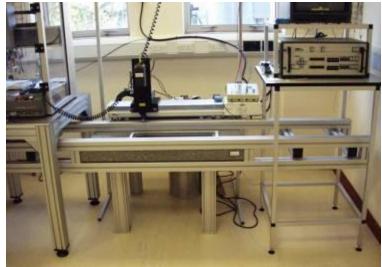

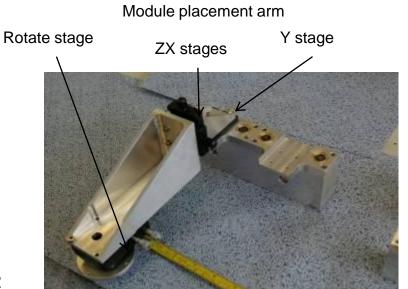

#### **Stavelet construction at RAL**

#### Module placement area

Glue pattern trials (left - on test board , right – on test bus cable)

Stavelet test box

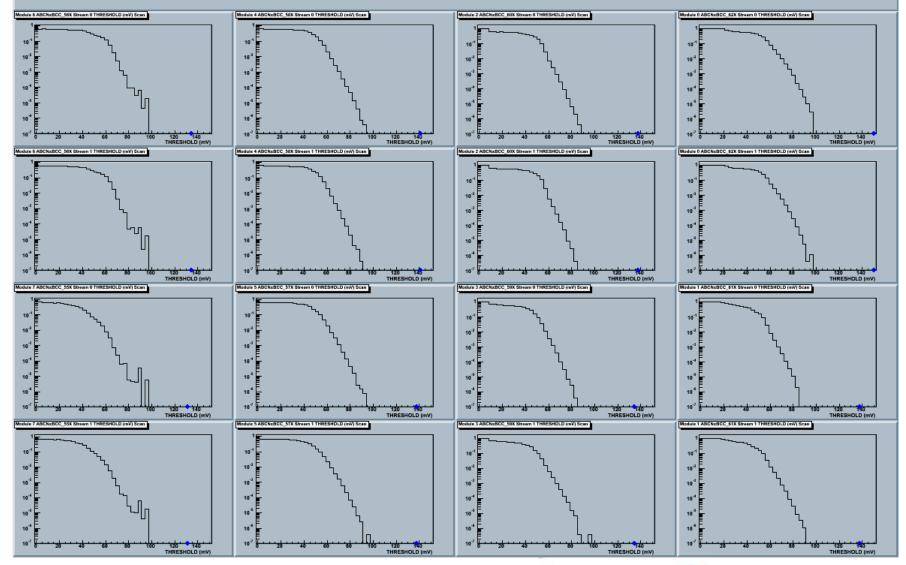

#### Run 1108 Scan 6 (log)

# Hybrid powering

Hybrids are designed for two powering schemes:

- 1. Parallel power, which could be provided by DCDC converters

- 2. Shunt regulation, using the distributed shunt regulators integrated within the ABCN-25s

- Required for serial powering Mshunt is the default scheme

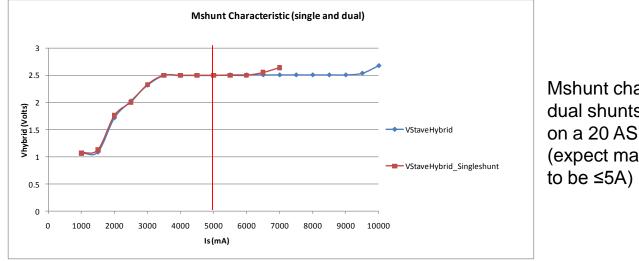

Mshunt characteristic for single and dual shunts enabled per ABCN-25 on a 20 ASIC hybrid (expect max. Hybrid shunted current to be ≤5A)

Single Shunt transistor enabled per ABCN-25 (20 x shunt transistors) Shunt regulates Vhybrid to 2.5V at  $I_s$ >3.5A and diverges at  $I_s$ <6.5A (*cf*  $I_{hybrid}$  + $I_{smax}$  (3.6 + (20 x 0.14))) = 6.4A

Dual Shunt transistors enabled per ABCN-25 (40 x shunt transistors) Shunt regulates Vhybrid to 2.5V at  $I_s$ >3.5A and diverges at I<9.5A (*cf*  $I_{hybrid}$  + $I_{smax}$  (3)