# Development of a beam test telescope based on the Alibava readout system

Marco-Hernández R.<sup>1</sup>, On behalf of the ALIBAVA Collaboration<sup>2</sup>

mounted on a rotary stage. Two scintillators and PMTs placed in the outermost XYT

The front-end includes the following parts

planes for triggering purposes

- <sup>1</sup> Instituto de Física Corpuscular, CSIC-Universidad de Valencia, Valencia, Spain.

- <sup>2</sup> Department of Physics, Oliver Lodge Laboratory, University of Liverpool, Liverpool, UK.

- Instituto de Microelectrónica de Barcelona, IMB-CNM, CSIC, Barcelona, Spain.

- Instituto de Física Corpuscular (IFIC), CSIC-Universidad de Valencia, Valencia, Spain.

#### Introduction

- A telescope is a tracking system used to measure the spatial

- resolution performance when developing new detectors. The system is intended for working in a beam test environment

# The system is interided to working if a beam test environment. The system will be used to carry out both analogue charge collection and spatial resolution measurements. The system is designed to be with different types of microstrip or pixel silicon detectors.

The telescope has a front-end part, a readout part and a DAQ

**DUT Board**

Two Beetle ASICs (256 channels) for the readout of either strip or fanout pixel silicor

required. Fast control (LVDS) and Slow control (I2C) shared by the Beetle chips. There is a temperature sensor attached to the backplane via the copper chuck. Independent HV DC level for blaising the sensors. Trigger circuit from the detector backplane signal if a self-triggering mode is required. - Charge amplifier stage: analogue trigger pulse. - Constant fraction discriminator: digital trigger pulse.

The DUT can be mounted on a rotary stage controlled manually or by software: possibility of varying the angle between the DUT and the particle track. The DUT is childed with a Peltier element.

detectors of different types. Buffer stage for the Beetle chips analogue outputs. Optional equalization if long cables are

software

reauired.

Time iitter of 60 ns.

USB temperature controller

Air fans for the heat sink of the Peltier element

LV DC Supply System

L Sector Sufer harman

HCEC NELOW

TRUNCATION OF

Block diagram of the DUT board

Although in the base unit designed there is a provision for just one plane, up to twelve DUT boards can be read out by the tele scope

- System architecture

- The readout part of the system is composed of the following items Four XY measurement and trigger planes, perpendicular to the particle track, where XYT boards are located. Detector under test (DUT) attached to a chilled DUT board, An Alibava mother board connected to each XYT or DUT board.

- A master board which collects the data and distributes the control signals (trigger, clock and reset) to the Alibava mother boards

- The master board is connected to the DAQ software via Ethernet. The boards are placed in a crate with a standard PC-like power supply

Readout part of the telescope

The boards are placed in a crate with a standard PC-like power supply and a power distribution board.

XYT Board

The XYT board measures the track space points using two silicon strip detectors mounted Different strip detectors (p-in-n and n-in-p) with a thickness of 300 µm are used for robust amplitudes and charge sharing. Either 80 µm pitch detectors or 40 µm pitch detectors with intermediate strips (for more spatial resolution) can be used.

The coordinate measurements are carried out with two Beetle ASICs (256 channels). Buffer stage for the Beetle chips analogue outputs. Optional equalization if long cables are

Fast control (LVDS) and Slow control (I2C) shared by the Beetle chips. The XYT board can also trigger on the particle tracks in the beam test using a trigger circuit

There is also a driver for the rotary stage attached to the crate

#### **Beetle ASIC**

- ASIC Beetle: readout chip developed at ASIC laboratory of the University of Heidelberg.

- 128 input channels with charge amplifiers and shapers Front-end output signal:  $V_p = kQ$ .  $T_p \sim 25$  ns.

- This output is sampled into the analogue pipeline (128x187 cells) with the frequency of the Beetle chip clock (40 MHz).

- Analogue pipeline latency fixed of 128 CLK cycles (3.2

- Analogue multiplexed readout: 16 bits header + 128

- Analogue multiplexed readout: to bits neader + 128 analogue channels 25 ns wide. Charge injector on each channel for calibration purposes Fast control (LVDS) signals for clock, trigger, reset and readout detection. Slow control (I2C) for chip configuration.

| s. | The trigger circuit produces analogue and digital There is a CPLD connected to the trigger circuit. and to the Master board.     For synchronization of the trigger signal to a c     For delaying and implementing coincidence w |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                                                                                                                                   |

| ıt |                                                                                                                                                                                                                                   |

trigger pulses with a time jitter of 60 ns. It is also connected to other XYT boards

#### Alibava Mother Board

DUT board picture

- A modified Alibava mother board is used to readout and to control each XYT/DUT board. The board works using a common trigger and clock signals as well as an common event reset signal as inputs. The board has a Xilinx Spartan 3 FPGA clocked at 40 MHz with an on-board oscillator. There is also a SDRAM (266 Mb) for temporary acquisition data storage. Beetle ASICs analogue data are processed and digitized by a signal conditioning block and two ADCs. Fast control and Slow control signals for the Beetle ASICs are generated directly by the FPGA. The former board trigger inputs are used for the common input signals (clock, trigger and event reset). The TDC on board (600 ps resolution) is used to have a time stamp of each input trigger; no synchronization required between common clock and trigger. The data collected by each Alibava board are sent to the a Master board: local data/address bus with a custom digital protocol.

protocol. - The former USB controller replaced by a digital connector and a readout bus terminator for the communication with the Master board. The board has its own supply system (DC-DC converters and LDC regulators) from a 5V DC input: required Alibava board supply levels and XYT/DUT board supply levels generated from this level.

LIP

ed in the

BEETLE CONFIGURATION

DATA

DATA

GIN

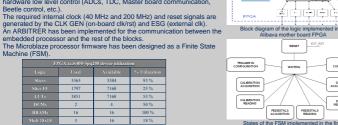

- The logic implemented in the FPGA is a combination of custom digital blocks and an embedded system. A CFSM controls the different blocks depending on the current state of the

- system. The CFSM and SDRAM CONTROL have been implemented with a Microblaze embedded processor (32 bits RISC). The custom digital blocks have been described in VHDL. They perform the hardware low level control (ADCs, TDC, Master board communication,

- Power supply

- The power distribution for the system is carrie out by means of a standard PC power supply which supplies +5V and +12V.

- - There is a power distribution board connected to the power supply to fan-out these levels to:

- Alibava boards. Master board. PMTs.

- DUT rotation stage

- Air coolers for the Peltier element of the DUT.

- The XYT boards and the DUT board are powered from the Alibava boards.

- The detectors of the XYT boards and the DUT board are powered with dedicated power supplies since they control we can be a control to solve the solv

- require HV and current sensing.

- Master board: Xilinx development board connected to the patch board

## System status

- are part of the system is produced and The hardw

- tested separately. 5 XYT boards. 2 DUT boards. 10 Alibava boards. 2 Master boards. 2 Naster boards. 2 Power distribution boards . 2 power distribution boards . Cabling. The Alibava FPGA logic and firmware has been redesigned and tested. The Master board FPGA logic has been designed and tested

- tested. The DAQ software is being developed based on the Alibava DAQ software. The track based alignment software is being developed. Next steps: Software tests. .

- .

- Software tests. System integration and commissioning.

- XYT board block diagra **Master Board**

- The Master board is implemented with a Spartan 3E Xilinx development board and a custom patch board. The board distributes the common clock, trigger and event reset signals to the Albava boards through the patch board. The trigger signal generated by the telescope can come from the XYT boards for the WMTS. The patch board provides the connections and circuitry required to process these signals. The Master board mergers the data streams coming up to sixteen Alibava boards: the patch board need for connecting the data/dtress bus cable to the Master board using a decoder for addressing each Alibava board. A test channel has been implemented for testing in a standalone mode a XYT or DUT board. The board also performs the communication with the DAC software via 100M Ethemet: an Ethemet controller implemented in the FPGA.

- Ethernet controller implemented in the FPGA. The board is a communication bridge. It

- addresses and collects data from the corresponding Alibava board. It sends these data in the corresponding Ethernet frames New functions can be added to the Master

- board by implementing new digital logic in the FPGA.

### Software

- Main characteristics Control the telescope hardware by raw Ethernet communication for configuration, calibration and data

- communication for configuration, campration and usual acquisition. User interface with the system (GUI). Generation of information (output file). The software also processes the raw data acquired by the Alibava boards to obtain data with physical the Alloava boards to obtain data with physical meaning. The DAQ software has been designed using two levels. - Low level implements the communication between the software and the Master board by raw Ethernet and the low level data processing. - High level includes the GUI and the output file

generation. The software has been designed using C++ language. Operating system compatibility: Linux. Track based alignment software has also been developed for the data obtained with the DAQ software.