# The Design for Test Architecture in Digital Section of the ATLAS FE-I4 Chip

Vladimir Zivkovic

National Institute for Subatomic Physics (NIKHEF)

Amsterdam, the Netherlands

Topical Workshop on Electronics for Particle Physics (TWEPP) 2010 Aachen, September 22

#### **Outline**

- Introduction

- Implementation of the Design-for-Test (DfT) Architecture in FE-I4

- Test Development Flow

- Method evaluation benchmarking

- Conclusion and further challenges

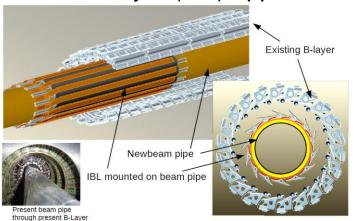

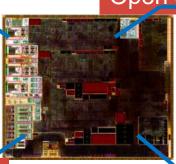

## FE-I4 Chip

#### Insertable B-Layer (IBL) Application

| Pixel array size                                                                                                                                                                     | 80x336                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| Pixel size                                                                                                                                                                           | 50x250 mm <sup>2</sup>                                |

| Maximum charge                                                                                                                                                                       | 100 000 e <sup>-</sup>                                |

| Hit trigger association resolution                                                                                                                                                   | 25 ns                                                 |

| Same pixel two-hit discrimination (time)                                                                                                                                             | 400 ns                                                |

| Tuned threshold dispersion                                                                                                                                                           | < 100 e <sup>-</sup>                                  |

| Charge resolution                                                                                                                                                                    | 4 bits                                                |

| ADC method                                                                                                                                                                           | TOT                                                   |

| Radiation tolerance                                                                                                                                                                  | 250 MRad                                              |

| Operating temperature range                                                                                                                                                          | -40° C to 60° C                                       |

| Average hit rate with < 1% data loss                                                                                                                                                 | 400 MHz/cm <sup>2</sup>                               |

| Average filt rate with < 170 data 1033                                                                                                                                               | 400 WII 12/CITI                                       |

| Readout initiation                                                                                                                                                                   | Trigger command                                       |

| •                                                                                                                                                                                    |                                                       |

| Readout initiation                                                                                                                                                                   | Trigger command                                       |

| Readout initiation  Max number of consecutive triggers                                                                                                                               | Trigger command 16                                    |

| Readout initiation  Max number of consecutive triggers  Trigger latency (max)                                                                                                        | Trigger command 16 6.4 μs                             |

| Readout initiation  Max number of consecutive triggers  Trigger latency (max)  Maximum sustained trigger rate                                                                        | Trigger command 16 6.4 μs 200 KHz                     |

| Readout initiation  Max number of consecutive triggers  Trigger latency (max)  Maximum sustained trigger rate  External clock input (nominal)                                        | Trigger command 16 6.4 μs 200 KHz 40 MHz              |

| Readout initiation  Max number of consecutive triggers  Trigger latency (max)  Maximum sustained trigger rate  External clock input (nominal)  Single serial command input (nominal) | Trigger command  16  6.4 µs  200 KHz  40 MHz  40 Mb/s |

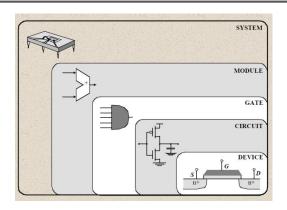

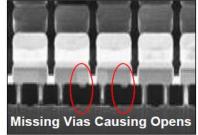

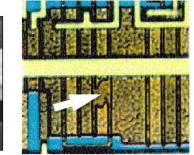

## Importance of IC Test

- IBL has raised concerns on large-volume product quality: yield has to be increased

- Complexity of State-of-the-Art ICs produced in deep submicron technology requires dedicated approach for test

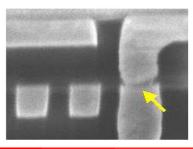

Transistor always ON

Physical Defect: An on-chip flaw introduced during fabrication or packaging of an individual ASIC that makes the device malfunctioning

Open circuit

Short circuit

Oxide pinholes

Times when the designers were able to write the procedures to distinguish between correct and faulty chips quickly, with ease and map them to tester platforms, are past long times ago

## Test development process in deepsubmicron technologies

Internal probing of ICs too costly

Rule of the game: Tester access to the Device Under Test (DUT) only possible through its primary I/O ports – the Design for Test (DfT) needed

Fact: Test is not any longer back-end process – the development and implementation begins during the design stage

Test Development and Test Vector Generation

22/09/2010

## Functional vs Structural Testing

- Functional testing verifies that a circuit fulfils the desired spec

- Functional testing not feasible for exhaustive tests

- An example: 32-bit adder requires 2<sup>65</sup> ≈ 3.7\*10<sup>19</sup> test vectors

- Structural test focuses rather on the circuit structure and can cover manufacturing defects that otherwise may not have been detected by functional testing

- Power or ground shorts

- Open interconnection on the die

Short-circuited drain or source of the transistor, caused by metal-spike

#### **Outline**

- Introduction

- Implementation of the DfT Architecture in FE-I4

- Test Development Flow

- Method evaluation benchmarking

- Conclusion and further challenges

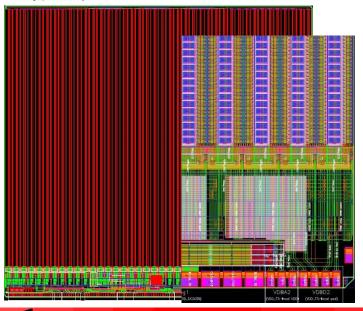

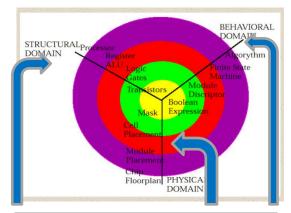

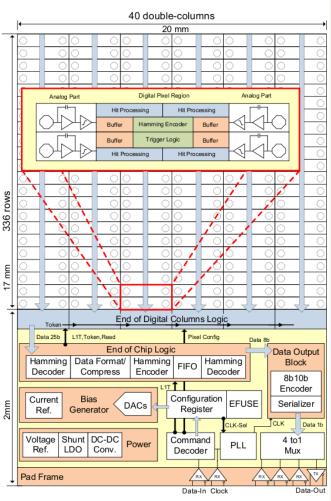

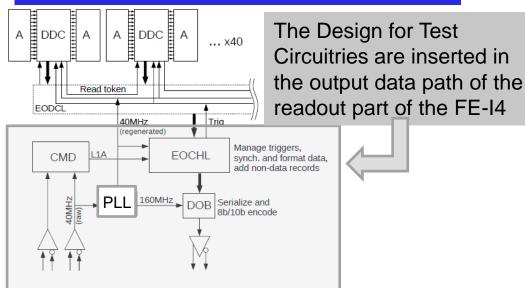

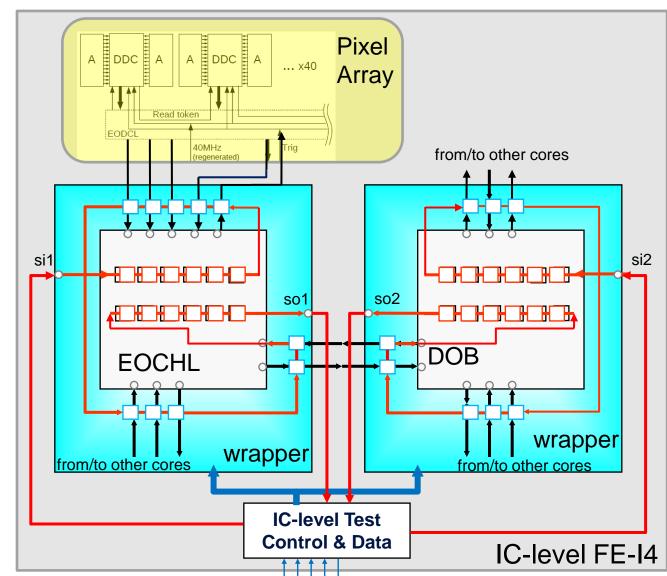

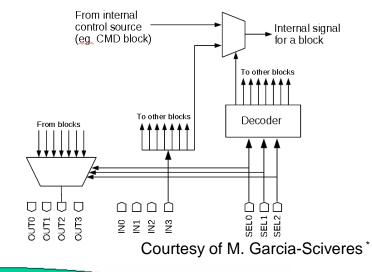

#### FE-I4 Architecture Overview

Courtesy of M. Barbero'

For the sake of SEU robustness, the design makes extensive use of triple redundancy, emphasizing further the internal test structures requirement

The DfT architectural choice: Full-scan Modular (Core-Based) test architecture

22/09/2010

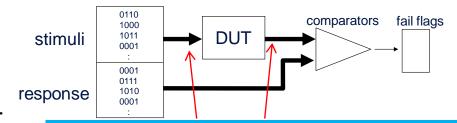

## Basics of digital structural testing

- Stimulus and response calculated by Automatic Test Pattern Generator (ATPG) based on fault models

- Applied on the whole device or in a divideand-conquer fashion, individually on the embedded modules (cores)

Access to internal terminals of the embedded modules (cores) through design for test (DfT) is necessary

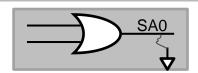

Stuck-at Fault Model: A logical model representing the effects of a physical defect

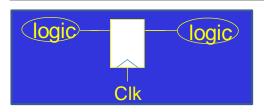

Handling sequential designs: full-scan concept

Most of the commercials Automatic Test Pattern Generator (ATPG) based on stuck-at fault model (D-algorithm)

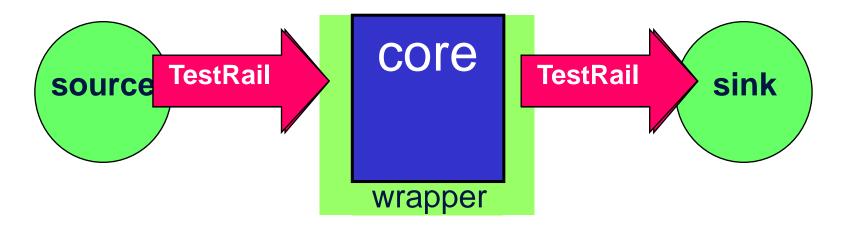

## Core-Based Test concept

- 1. Test Pattern Source and Sink

- 2. Test Access Mechanism (TAM)

- 3. Core Test Wrapper

[ Zorian, Marinissen, Dey - ITC'98 ]

### Core-Based Test in FE-I4

#### **Mandatory**

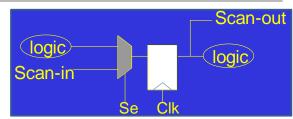

- Internal scan chain insertion

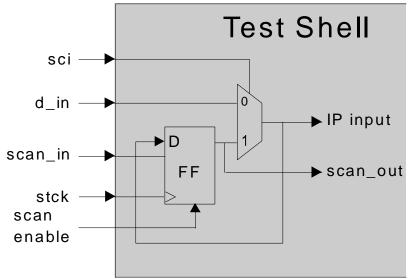

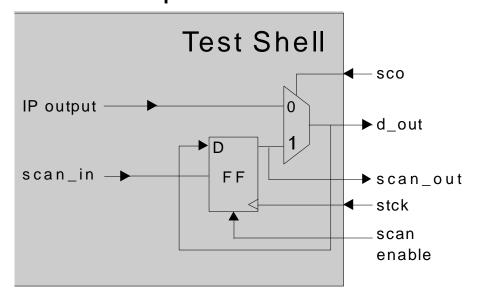

- Wrapper cells providing function access and test controllability + observability at IP's data terminals

- TestRail access to wrapper cells ('surround chains') and IP flip flops ('scan chains')

- SEU proof

22/09/2010

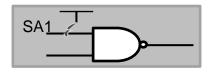

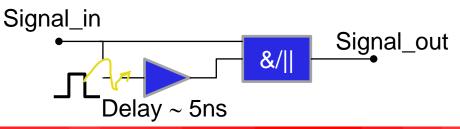

## Wrapper cells in the nutshell

#### Input isolation

Note: Only the combinatorial inputs require isolation

Deglitcher cells implemented on scan enable, test mode and reset signals

#### Output isolation

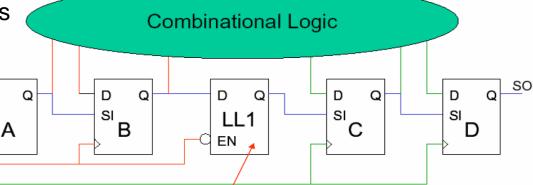

## IC-level control and consequences on core internal DfT

- Cores will be scan-tested independently,

i.e. in isolation of each other

- Top-level test control (scan enable, test mode selection) routed to each of the cores

- No more than one scan chain per core

Additional challenge for multiple-clock cores: most aggressive DfT insertion strategy with lockup latches

SI

Clk1 Clk2

Lockup latch inserted on the clock domain boundary

#### **Outline**

- Introduction

- Implementation of the DfT Architecture in FE-I4

- Test Development Flow

- Method evaluation benchmarking

- Conclusion and further challenges

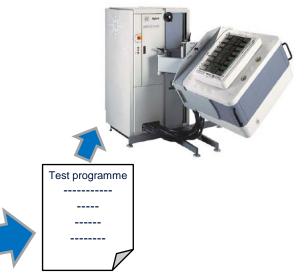

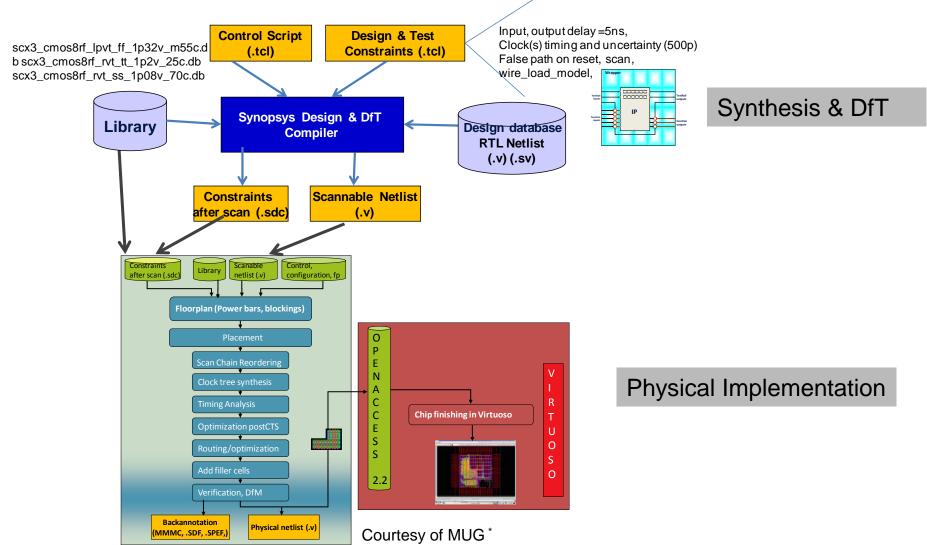

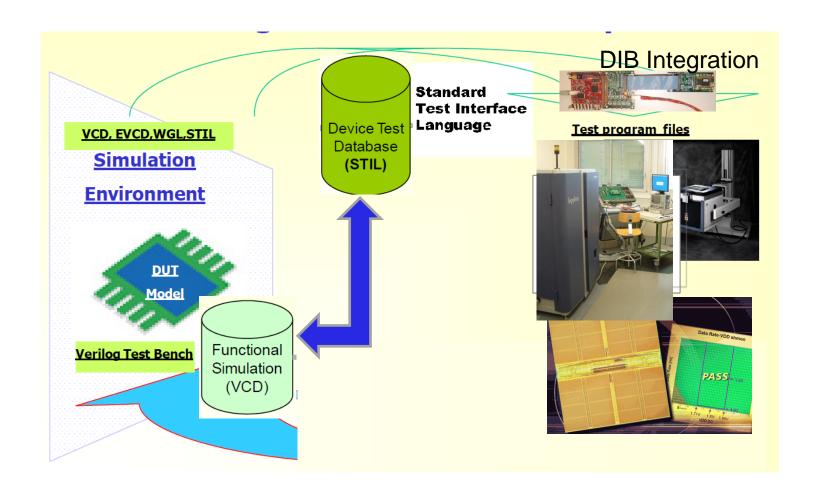

## DfT generation: Two-pass mapped flow

## ATPG & Test Assembly

Generate the test patterns

Generate the test bench for the simulation with both stimuli and response with timing and wave information

Assemble the test patterns of the IP(s) into the test vectors running at the

tester platform DfT **Physical ATPG Protocols** netlist constraints TetraMax test **Timing** lib **ATPG** WaveForm { Pin = inputs; Drive = NR, tdel; test WaveForm · Pin = rzClocks; bench Drive = RZ. t1. t2: WaveForm { XXX XXX Pin = outputs; STIL Expect = SB, t1, t2; vectors **NCsim**

#### Test execution

#### **Outline**

- Introduction

- Implementation of the DfT Architecture in FE-I4

- Test Development Flow

- Method evaluation benchmarking

- Conclusion and further challenges

## Reports

- End of Chip Logic (EOCHL) Core

- Total faults105980

- Fault coverage 90.83%

- Number of patterns 231 (3192 bit-stream wide, each)

- DfT area overhead ~ 8 % relative, < 0.1% absolute</li>

- Data Output Block (DOB) Core

- Total faults2183

- Fault coverage 78.67%

- Number of patterns26

| Test Cost (time) = $\sum_{i=1}^{Nc}$ | $\int_{1}^{\infty} \left( \left[ \frac{f f_{i}}{nsc_{i}} \right] \right)$ | $\left  \mathbf{q}_{i} + 1 \right  \neq p_{i}$ | $\frac{1}{ftck_{i}}$ |

|--------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|----------------------|

|--------------------------------------|---------------------------------------------------------------------------|------------------------------------------------|----------------------|

| Nc   | nr of modules        |

|------|----------------------|

| ff   | nr of flip-flops     |

| nsc  | nr os scan-chains    |

| p    | nr of patterns       |

| ftck | Test clock frequency |

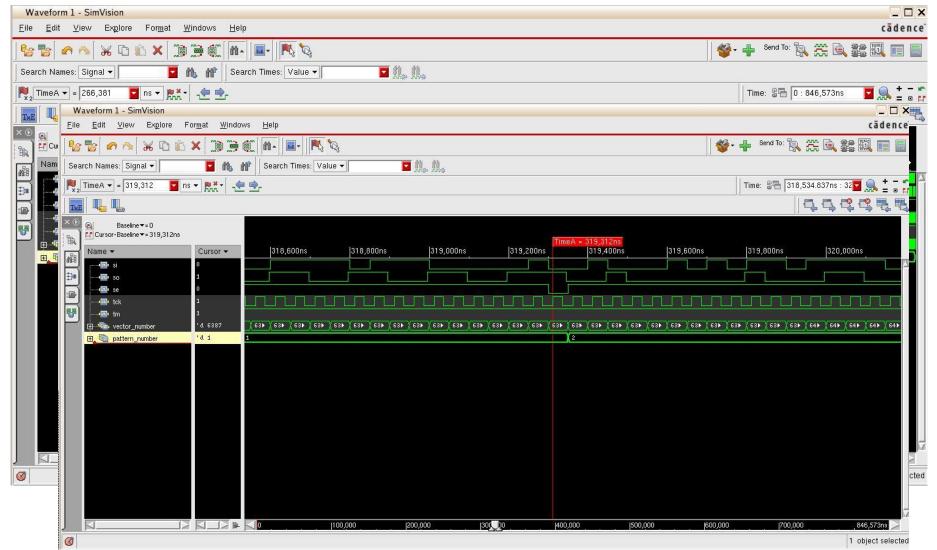

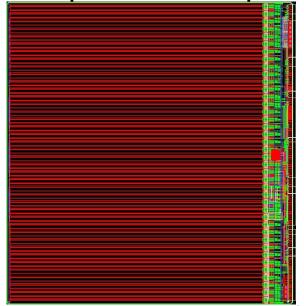

## Simulation charts (EOCHL core)

#### Conclusion

- The test infrastructure in digital portion of ATLAS FEI4 IC is in place for production test

- The fault coverage figures are sufficiently high for this type of application

- Minimal area overhead, while the performance penalties are virtually none

- Reusability of the method

- Compliant to the industrial standards

## Future challenges

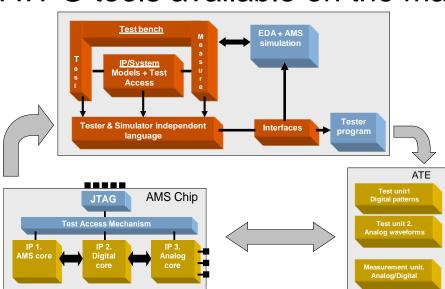

- Implementing the DfT in a digital portion only may not be sufficient – analog mixed-signal dedicated test approach needed

- Probability of the random defect landing on a random location leads to unpredictable quality levels

Gaining in importance with smaller feature size

## Future challenges (II)

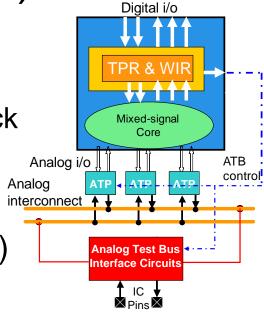

- Apply Analog Mixed-Signal DfT/BIST

- E.g. analog/mixed-signal test bus and/or digitally controlled patterns to test AMS block

Automate the AMS Test Development (no analog ATPG tools available on the market)

22/09/2010

## Acknowledgement

- Maurice Garcia-Sciveres, the project leader of FEI4

- Jan-David Schipper, Ruud Kluit, Nikhef institute

- The other members of FEI4 team, A. Mekkaoui, M. Barbero, R. Beccherle, D. Gnani, T. Hemperek, M. Karagounis, M. Menouni, D. Fougeron, F. Gensolen, V.Gromov, A. Kruth, G. Darbo, J. Fleury, J-C. Clemens, S. Dube, D. Elledge, A. Rozanov, D. Arutinov, F. Jensen