# High speed data transfer with FPGAs and QSFP+ modules

R. Ammendola<sup>(a)</sup>, A. Biagioni<sup>(b)</sup>, G. Chiodi<sup>(b)</sup>, O. Frezza<sup>(b)</sup>, A.Lonardo<sup>(b)</sup>, F. Lo Cicero<sup>(b)</sup>, R. Lunadei<sup>(b)</sup>, D. Rossetti<sup>(b)</sup>, A. Salamon<sup>(a)</sup>, G. Salina<sup>(a)</sup>, F. Simula<sup>(b)</sup>, L. Tosoratto<sup>(b)</sup>, P. Vicini<sup>(b)</sup>

(a) I NFN Sezione di Roma Tor Vergata (b) I NFN Sezione di Roma

Aachen, Germany, 20-24 September 2010

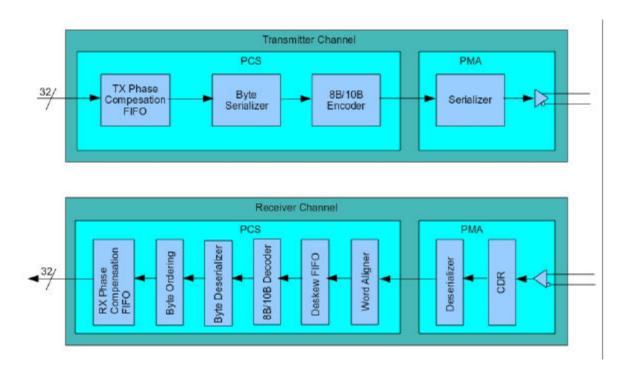

### High speed serializer/deserializer

- •Stratix IV GX embedded Altera transceivers

- •Full duplex ser/des

- •Data rates from 600 Mbps to 8.5 Gbps

- •Single or dual data rate

- •8b/10b enconding with clock data recovery

- •Channel bonding (up to 8x)

- •Programmable pre-emphasys and equalization

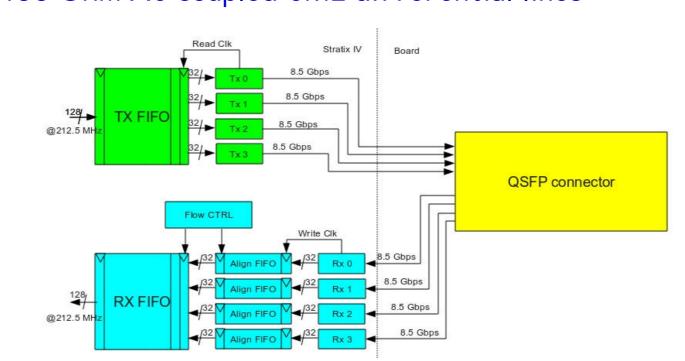

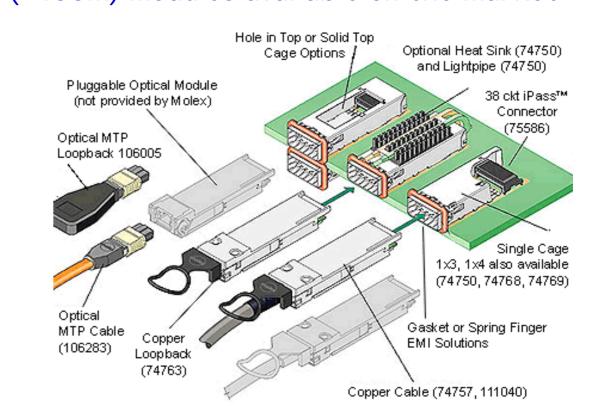

### **QSFP+** standard

- •SFP+ (Small Form Pluggable) electrical and mechanical standard for point-to-point links over copper or optical fibers with data rate up to 10 Gbps

- •QSFP+ (Quad SFP+) hot-pluggable transceiver with 4 transmit and 4 receive channels

- Aggregated bandwidth up to 40 Gbps per direction

- •High speed data rate, high-density and low-power applications

- •Passive copper (< 5m), active copper (< 15m) and active optical (< 100m) modules available on the market

- •100 Ohm AC coupled CML differential lines

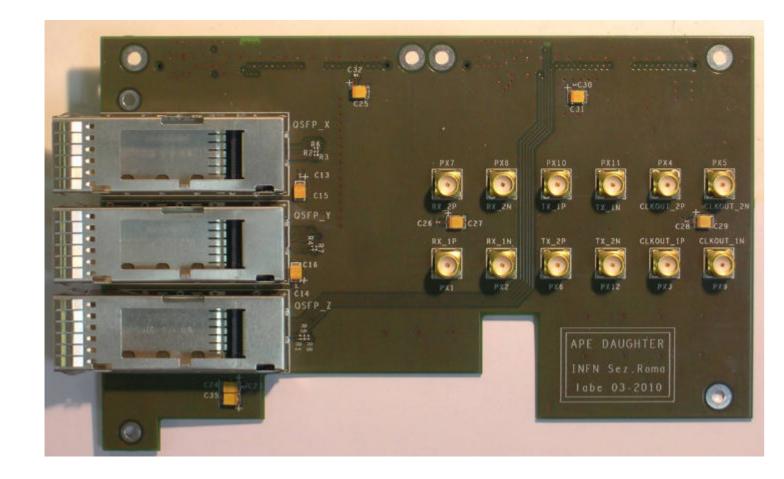

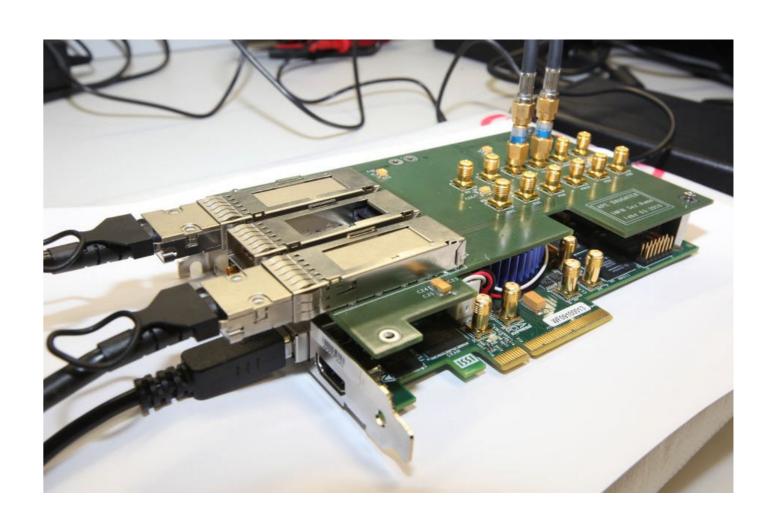

## Test system

- •Altera Stratix IV GX 230 development kit

- •230k Logic Elements, 24 serializers / deserializers •PCI - Express gen 2

- •Custom mezzanine (designed at LABE I NFN Roma)

- •3 QSFP+ connectors

- 2 high-speed Samtec connectors

- SMA test connectors

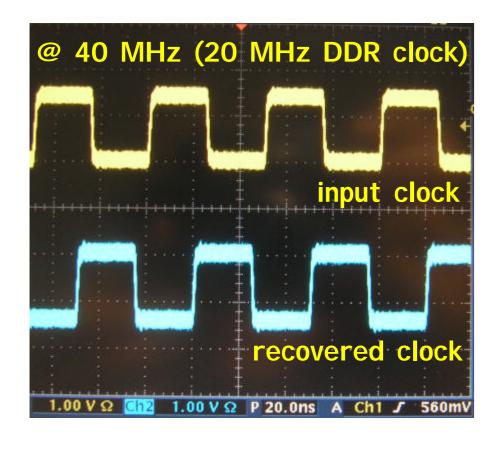

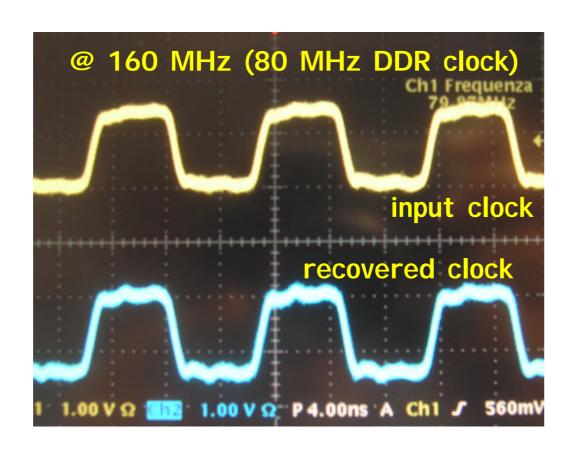

# Recovered clock

•Recovered clock stable and in phase up to 400 MHz (200 MHz DDR clock)

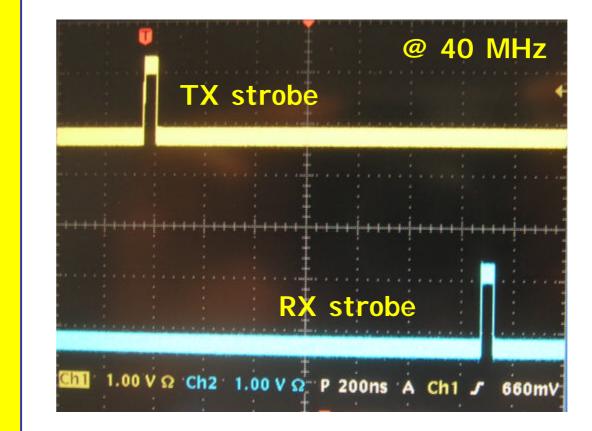

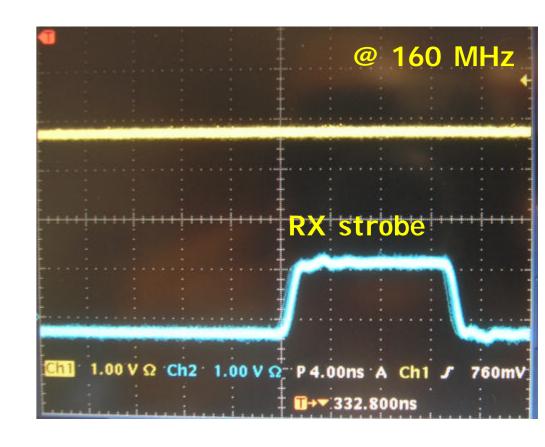

#### Latency

- Pseudorandom data stream

- Output strobe on a specific data word

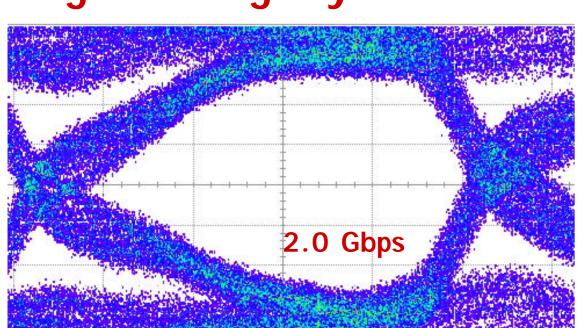

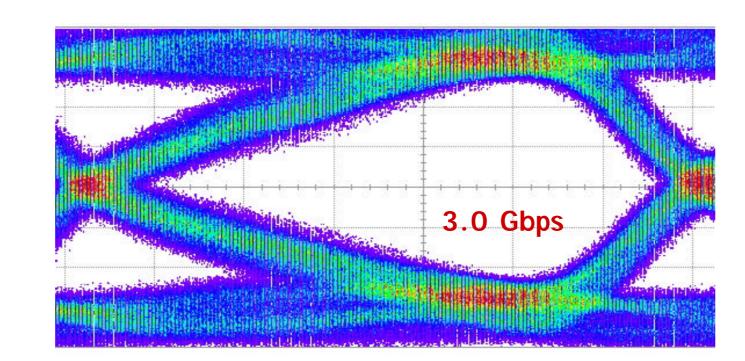

### Signal integrity

- •20 GHz sampling scope with external clock data recovery

- •2<sup>32</sup> pseudorandom data stream

- •Eye diagram at 2 and 3 Gbps (without pre-emphasys)

- Above 3 Gbps pre-emphasys needed (work ongoing!)

#### **Conclusions**

- •High speed embedded serdes mature and reliable technology with single line data rate up to 8.5 Gbps

- •QSFP+ emerging standard for high-density, low power applications high-data rate applications

- •Successfully tested up to 12 Gbps aggregated bandwidth

### References

- •http://apegate.roma1.infn.it/APE

- •http://www.altera.com/products/devices/stratix-

- fpgas/stratix-iv/transceivers/stxiv-transceivers.html •ftp://ftp.seagate.com/sff/SFF-8436.PDF