### CMS Pixel Detector with new Digital Readout Architecture PAUL SCHERRER INSTITUT PAUL SCHERRER INSTITUT

**Beat Meier** Chip Design Core Team Paul Scherrer Institut, 5232 Villigen, Switzerland

beat.meier@psi.ch

# New Readout Chip Design for Phase I Upgrade

### Abstract

The CMS pixel detector is planned to be upgraded in 2016 to a new one with a significantly reduced material budget. The new pixel system with more layers (4 for the barrel pixel) has to operate through the existing services at double the luminosity. Therefore a new readout scheme is implemented with a new pixel read out chip (ROC). A description of the ASIC modifications of the digital readout interface of the ROC is presented as well as the results and the performance of the physics based electronic simulations of a complete pixel module consisting of 16 pixel ROCs and a token bit manager chip.

### **Requirements for Phase I Upgrade**

- **R1** 4 layers for the pixel barrel detector instead of 3 3 layers for the forward detector instead of 2

- **R2** Reduction of material budget (Mechanical structure, cooling, Cabling)

- **R3** Design for double the luminosity  $(2 \cdot 10^{34} \text{ cm}^{-2} \text{ s}^{-1})$

### Module with new Readout Scheme

Data Buffers in Readout Chip (ROC)

### **Digital Readout**

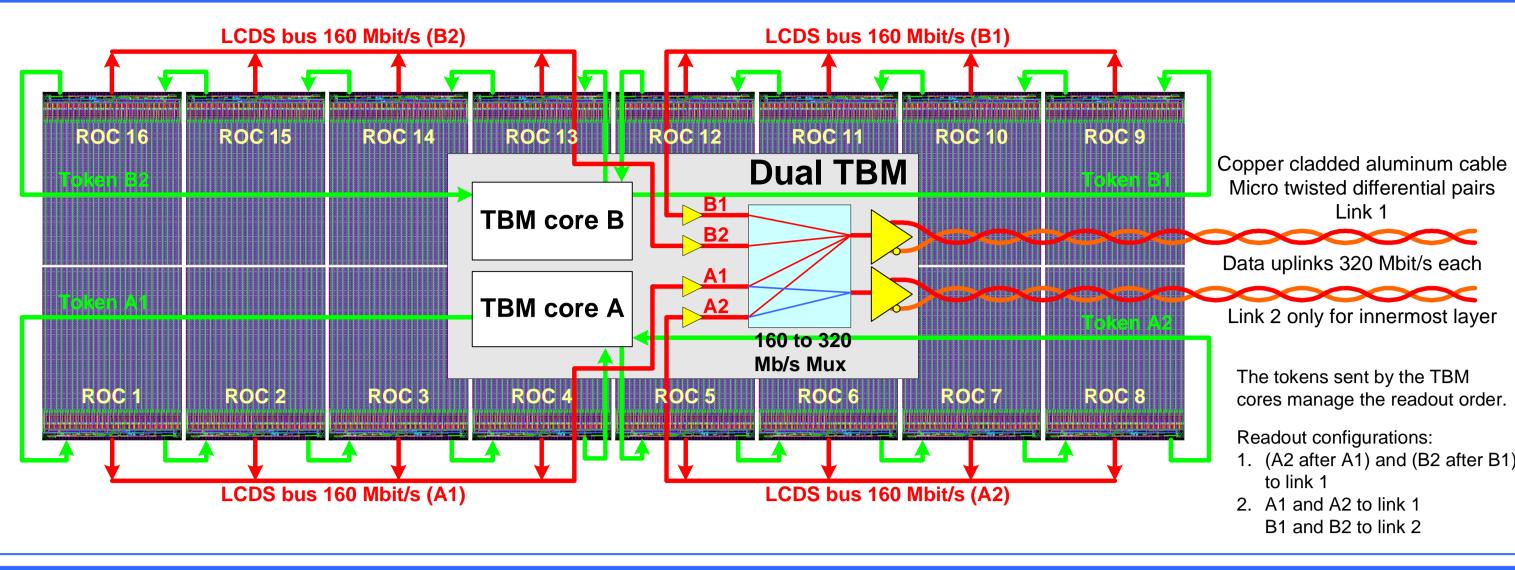

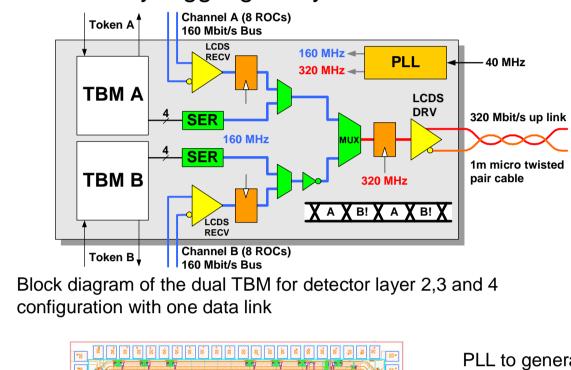

The new digital ROC readout is running at 160 Mb/s. Two serial data streams are recombined in the dual TBM chip to a single serial data stream at 320 Mb/s. Optimized drivers and receivers for LCDS (low current differential signal) are designed for very low power consumption.

| (0 X 1 X 1 X 1 X 1 X 1 X 1 X 1 X 1 X H X H                                                                                                                                               |                                                        |                                                                     | <br> <br>  <b>                                </b>         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------------------|

| ROC header                                                                                                                                                                               | double<br>column #                                     | pixel # (row)                                                       | pulse height                                               |

| repeated for each pixel hit                                                                                                                                                              |                                                        |                                                                     |                                                            |

| Proposed data format for the digital output of the ROC                                                                                                                                   |                                                        |                                                                     |                                                            |

| <ul> <li>The following new bl</li> <li>LCDS drivers and r</li> <li>PLL clock multiplier<br/>the serial data trans</li> <li>New control logic a</li> <li>8 bit ADC to digitize</li> </ul> | eceivers (<br>r to provide<br>sfer (desig<br>nd readou | design tested<br>e higher clock<br>ned and teste<br>t buffer FIFO ( | at 320 Mb/s)<br>frequencies for<br>d)<br>(dig. simulation) |

Schematic view of the present CMS Pixel detector consisting of 3 barrel layers and 2 forward disks on each side. For the phase I detector upgrade, 4 barrel layers and 3 forward disks on each side are intended.

### Limitations & Modifications

- 1.  $R3 \rightarrow L1$  trigger latency buffer overflows cause resets in double columns (dominating data loss)  $\rightarrow$  Increase number of data buffers in double columns

- 2.  $R3 \rightarrow Readout$  related dead-time at higher data volumes (blocked buffers in double columns)  $\rightarrow$  Additional readout buffer stage

- 3.  $R1 \rightarrow$  Higher module count with more layers and the same number of fibers → Digital readout and data link with 320 MBit/s

- 4.  $R2 \rightarrow Micro twisted pair cables for signals$

TRIGGER

TOKEN IN

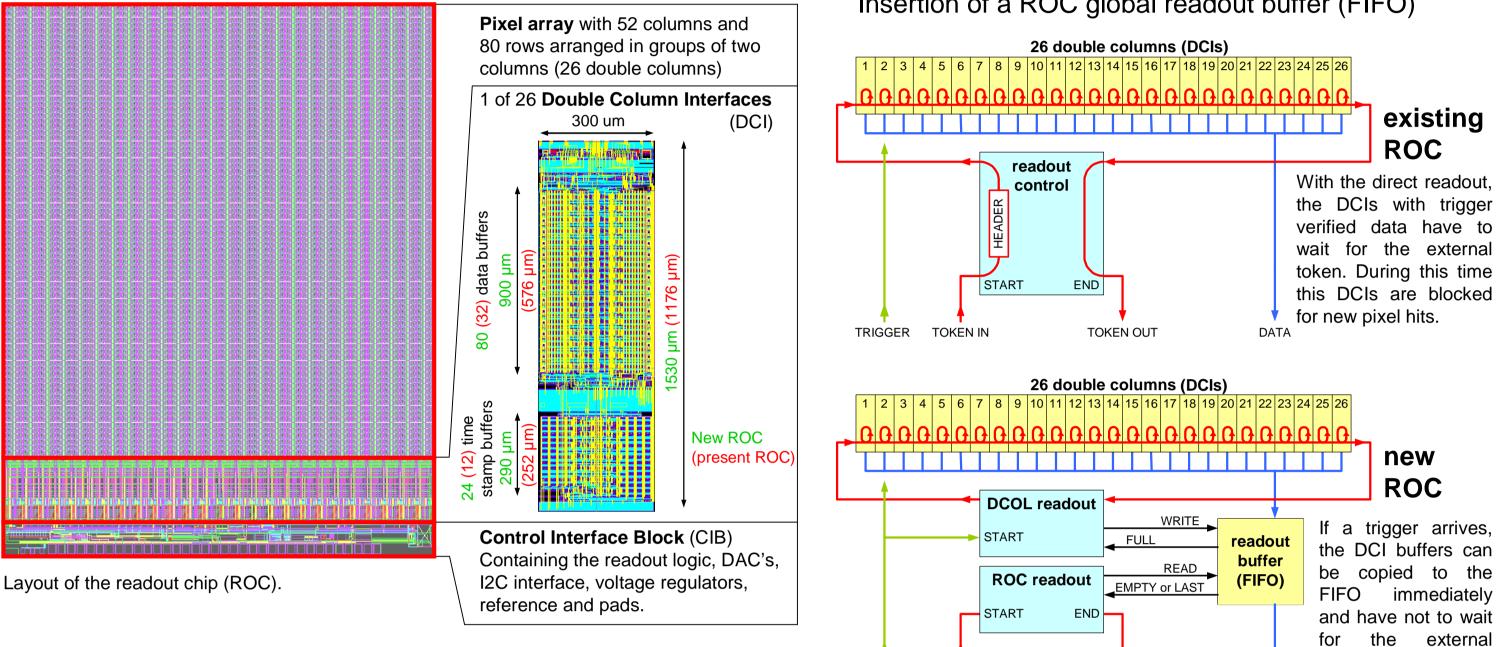

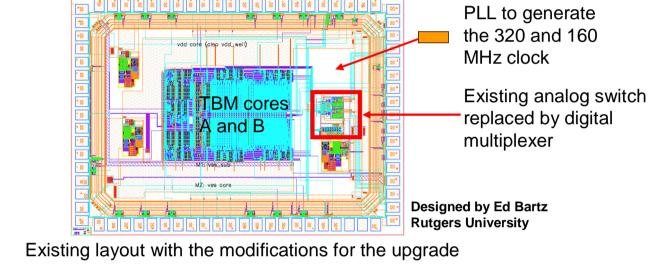

In the double column interface (DCI) more buffer cells have to be added. The bigger size can partially be compensated by smaller memory cells. The readout logic in the CIB will be replaced by a buffered, fully digital readout at 160 Mb/s. A PLL to provide the 160 MHz clock and a 8 bit ADC has to be added. The new readout buffer will be added between the DCI and the CIB. There are no modifications needed in the pixel array.

Insertion of a ROC global readout buffer (FIFO)

TOKEN OUT

buffers can be reduced significantly.

At double the luminosity an additional readout buffer

(FIFO) is needed to separate the double column

readout from the ROC readout. In this way, the

waiting time of the data in the double columns

## Dual Token Bit Manager (TBM)

existing

ROC

new

ROC

the

token.

DATA

immediately

externa

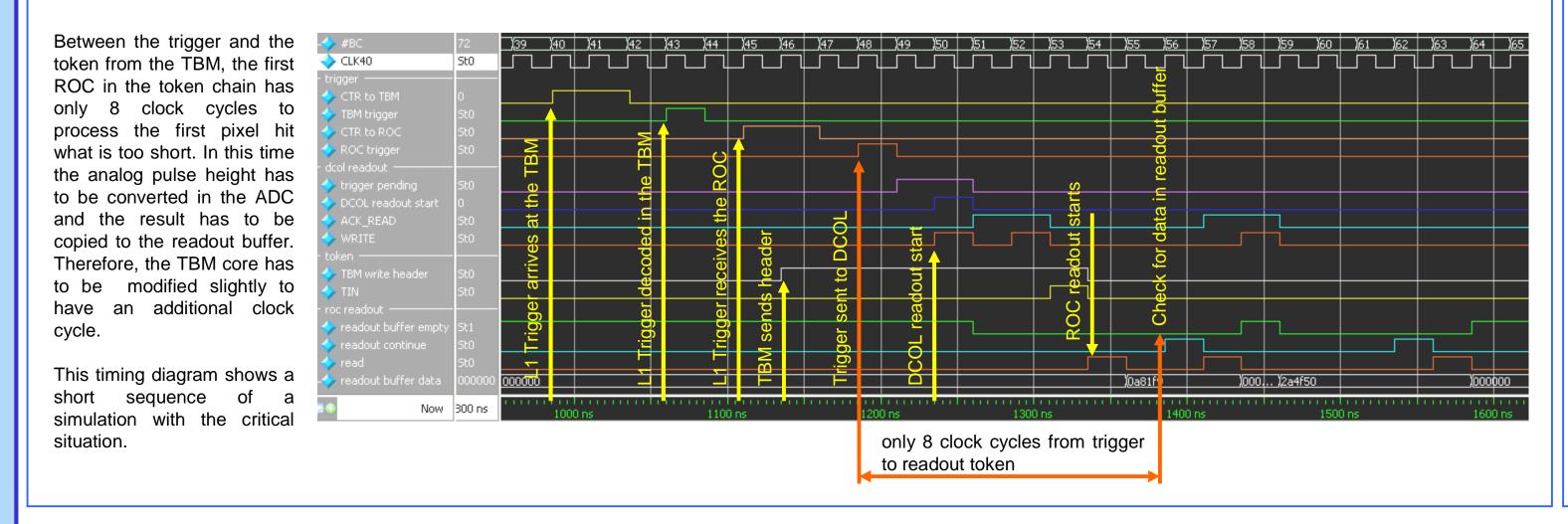

For the upgrade the existing TBM has to be changed. The two TBM cores that manage the ROC readout have to be redesigned slightly (see "Critical Trigger and Readout Timing"). The new data multiplexer refreshes the signals from the ROCs, adds the TBM header and trailer to the data stream and multiplexes two 160 Mb/s data streams together to 320 Mb/s by toggling bit by bit.

Timing diagram for detailed

## **Digital Simulation with Physics Data**

### Simulation Model

pxmod.v

### Introduction

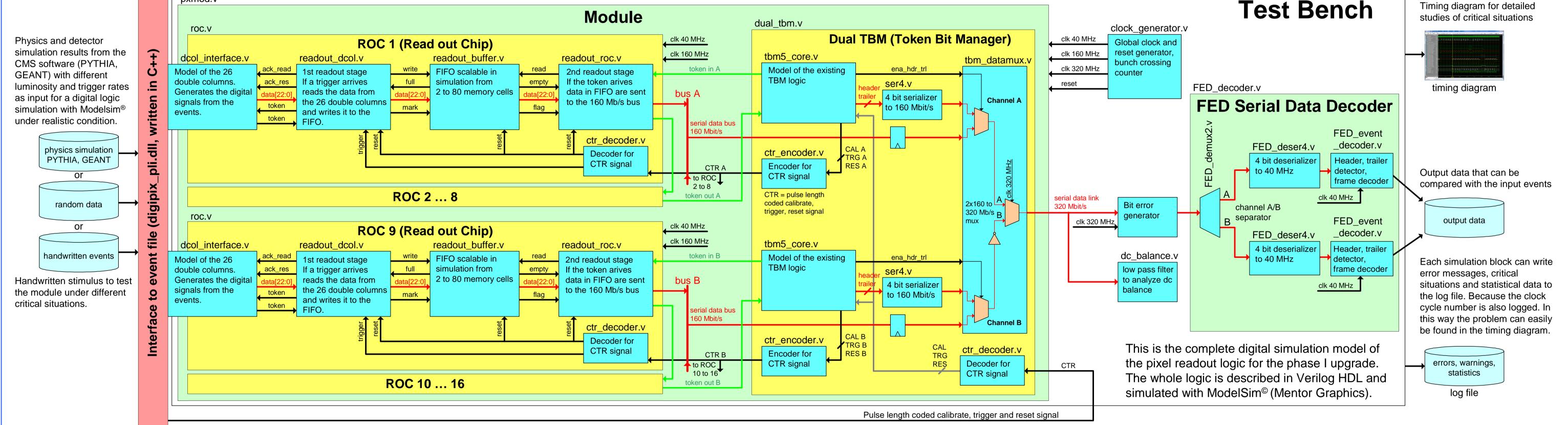

The goal of the overall simulation is to test the new ROC and TBM logic before doing the layout. This should be done under realistic conditions to cover all possible critical situations. In particle physics experiments a digital circuit should be able to cope with widely fluctuating data. To setup such a simulation, an interface program library for the digital simulator is written to access the physics data. In this way, it is possible to simulate over millions of clock cycles.

### **Simulation Performance**

### FPGA Implementation of Simulation Model

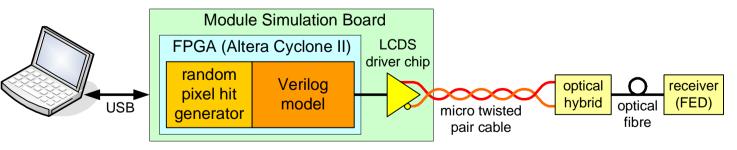

It is planned to implement the Verilog model of the module in an FPGA. The physics data file interface is replaced by a random pixel hit generator.

The Verilog model with a random pixel hit generator implemented in an FPGA. At the output a LCDS driver chip with the micro twisted pair cable, the optical link and the FED.

- Overall simulation of a whole module with 16 read out chips (ROC) and a TBM

- Clock cycle by cycle exact simulation (40 MHz, 160 MHz and 320 MHz) including serial data stream

- Each block can send messages to a log file

- Simulation speed: 70µs (2800 bunch crossings) per 1s

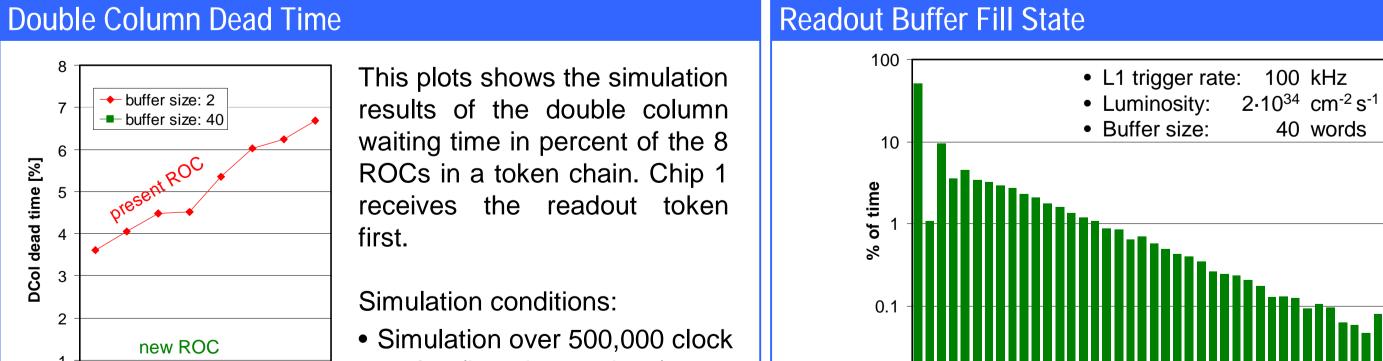

The red curve (read out buffer size 2) comes nearest to the existing pixel chip without a readout buffer. The green curve shows the improvement with a readout buffer of size 40.

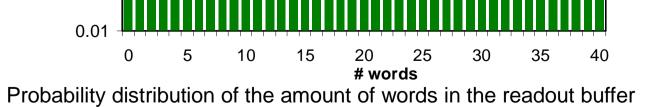

### Numbers of Data Words in the Readout Buffer

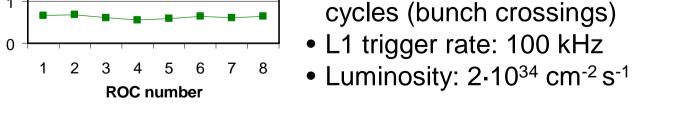

$\mathbf{O} = \mathbf{O} \mathbf{v} \mathbf{e} \mathbf{r} \mathbf{f} \mathbf{l} \mathbf{w}$ . ROC 1 a data sama da data Masta da Malanda da Matura dan ka ka kana ka ka ka ta ka ka ta ka ka ka ka ka ka Mala ROC 2 ROC 3 Level the Market and Market her wedle and Market Are supplied a liter to be a figure the formula with ROC 4 million Martin Ma ROC 5 Muchiller Miller Mc . March and American March and and a stranger and the meridian of the march and the march and the march and the meridian of the march and the ma ROC 6 Julia and many marked and the full with the full of the Andread and the second with the second and the se ROC 7 unorther the adding adding and the rate of the rate of the match and the the same whether the ROC 8 ulante Mulante with and and the second for the second the se • Simulation over 4 ms or 160,000 clock cycles • Simulation time: 60 s • L1 trigger rate: 100 kHz • Luminosity: 2-10<sup>34</sup> cm<sup>-2</sup> s<sup>-1</sup>

40 words (events)

Application of the FPGA pixel module:

- Test of cables, optical link with realistic data

- Test of FED decoding

overflows

• Development of new test board firmware

This tests do not need to wait for the complete chip and module prototype.

Module simulation board with FPGA, containing the module emulator and a CPU (NIOS II) with an USB interface to communicate with a PC. On the right side are the LCDS driver chips and micro twisted pair cables to the optical link.

### Critical Trigger to Readout Timing

Topical Workshop on Electronics for Particle Physics TWEPP, Aachen, September 2010

• Buffer size: