M. Bochenek<sup>1,2</sup>, W. Dąbrowski<sup>2</sup>, F. Faccio<sup>1</sup>, S. Michelis<sup>1</sup>

- I. CERN, Conseil Européen pour la Recherche Nucléaire

- 2. AGH, University of Science & Technology

Topical Workshop on Electronics for Particle Physics, TWEPP 2010

### Outline

- I. Powering schemes considered for upgraded ATLAS Inner Tracker

- 2. Switched capacitor step-down converter proposed for the DC-DC powering scheme

- A model of a simple step-down (2:1) converter and its practical implementation,

- Designs of the non-overlapping clock generator and buffers.

- 3. Switched capacitor voltage doubler proposed for the serial powering scheme

- A model of a simple voltage doubler and its practical implementation,

- Designs of the non-overlapping clock generator, level shifters and buffers.

Due to the fact that the IBM 0.13 µm submission was delayed, we have to wait for the results from the chips.

# I. Overview of the powering schemes considered for the upgraded ATLAS Inner Tracker

22/09/2010 3

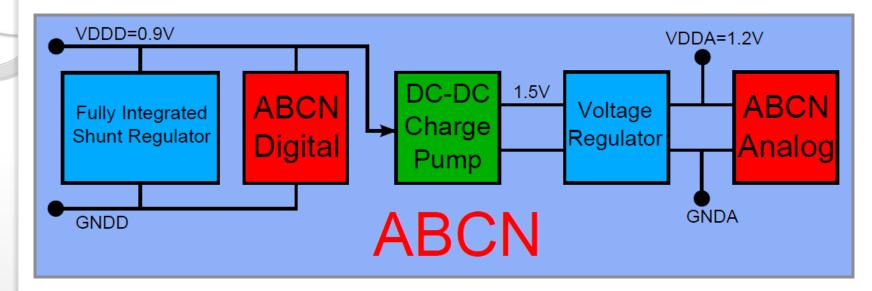

### Serial powering scheme

Good quality of analog and digital voltage:

- low output impedance of shunt regulator,

- possibility to use classical linear regulator  $\rightarrow$  good filtering efficiency.

No regulation on DC-DC, but the power consumption in the analog part is constant.

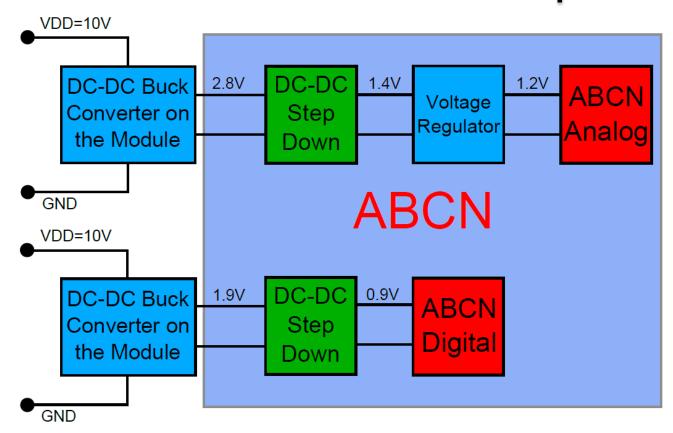

### DC-DC conversion technique

- A low-dropout voltage regulator in the "analog bus" is required.

- No regulation on the digital power line (required low impedance of DC-DC since the current consumption varies significantly in the digital part).

## 2. Switched capacitor step-down converter

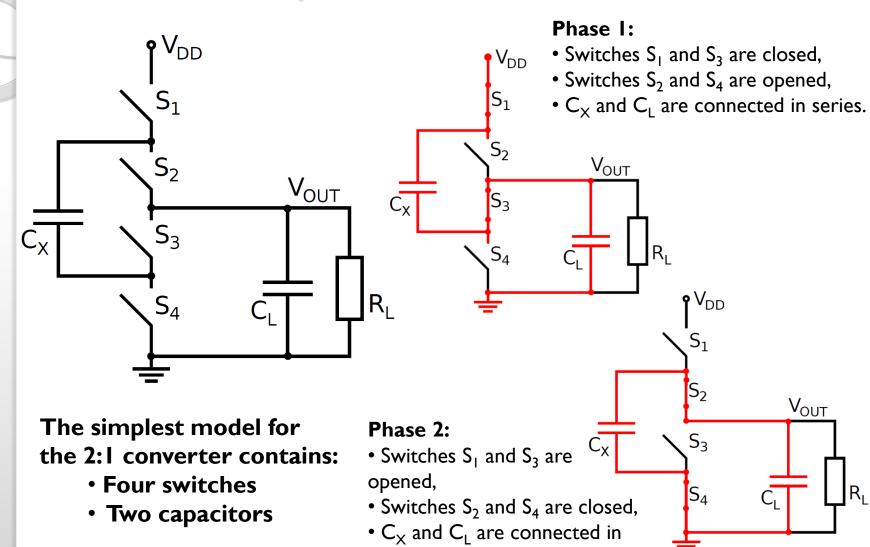

## A simple model of the step-down switched capacitor converter

parallel.

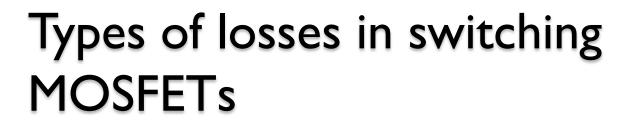

The optimization process is based on minimizing the contradictory types of losses in the switching MOSFETs

- Conduction losses (equal to:  $I^2 \cdot R$ ) therefore the total resistance between the source and drain during the "ON" state,  $R_{DS(on)}$  has to be as low as possible,

- Switching losses (equal to:  $\mathbf{t_s} \cdot \mathbf{V_{DS}} \cdot \mathbf{I} \cdot \mathbf{f}$ ) switching time, rise and fall time depend on the gate to drain capacitance  $C_{GD}$ , internal resistance of the driver and the  $V_{TH}$ ,

- Gate charge losses (equal to:  $\mathbf{f} \cdot \mathbf{Q}_{\mathbf{G}(\mathbf{TOT})} \cdot \mathbf{V}_{\mathbf{DRIVE}}$ ) are caused by charging up the gate capacitance and then dumping the charge to ground every cycle.

## Practical solution for the DC-DC step-down converter

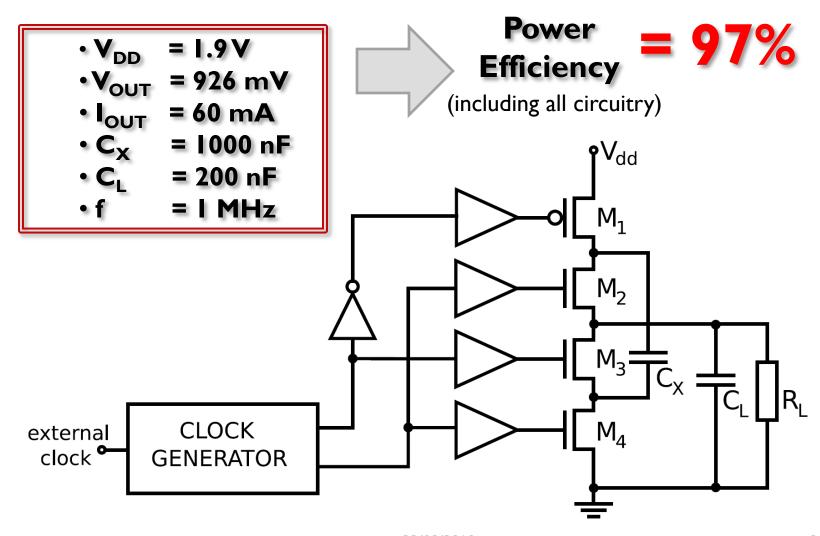

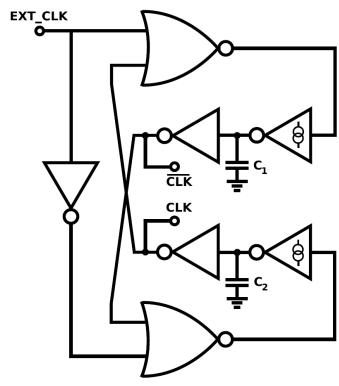

### Schematic diagram of the non-overlapping clock generator used in the step-down converter

2 x NOR gate

3 x inverter

2 x current starved inverter

$$C_1 = C_2 = 20 \text{ fF}$$

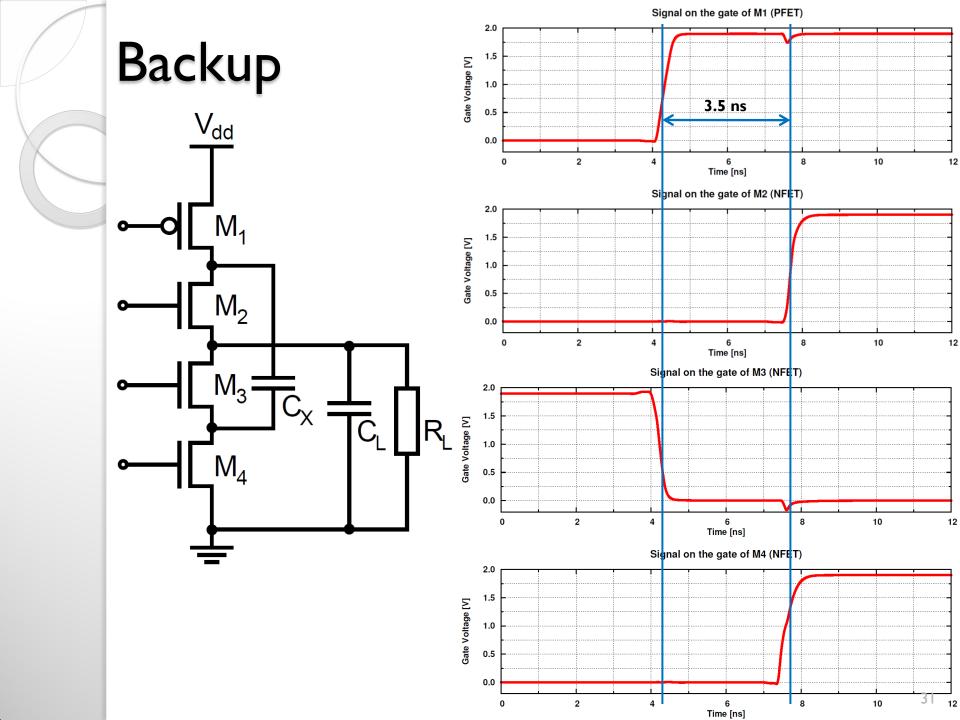

allows for a clock signal separation of 3.5ns

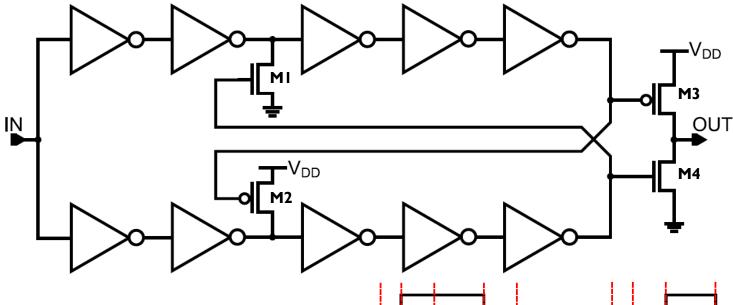

## Buffer used in the step-down converter

Two chains of scaled inverters with cross-coupled transistors MI and M2 allow to avoid the conduction current in the last inverter M3 / M4

This architecture of the buffer was used by S. Michelis in AMIS2

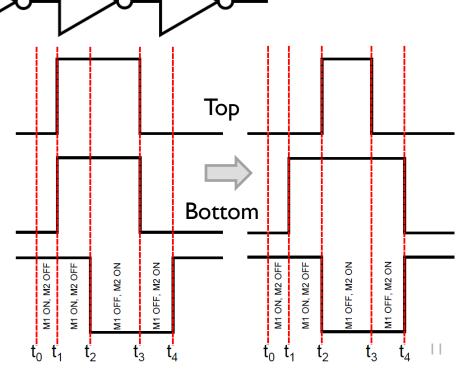

### Layout of the step-down converter

MI = 28.2 mm / 0.24  $\mu$ m, M2 = M3 = 18.0 mm / 0.30  $\mu$ m, M4 = 6.0 mm / 0.30  $\mu$ m

Total area =  $0.12 \text{ mm}^2$

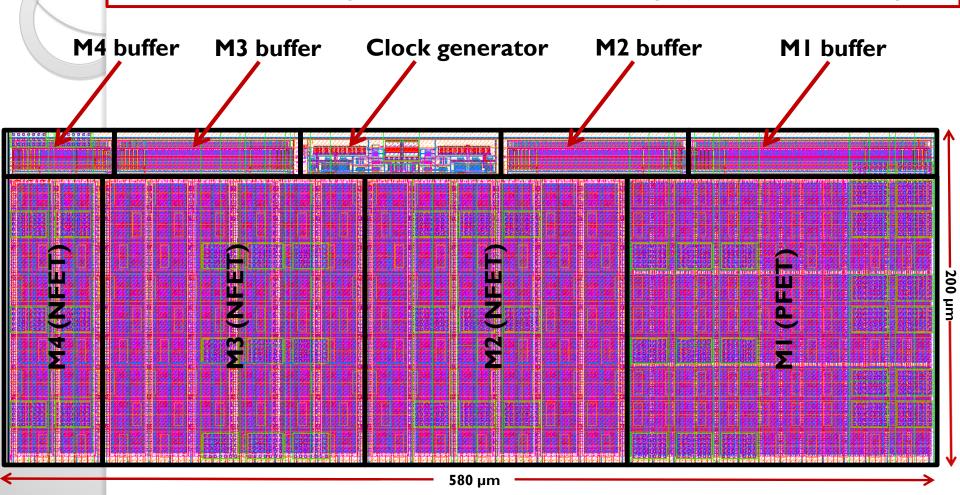

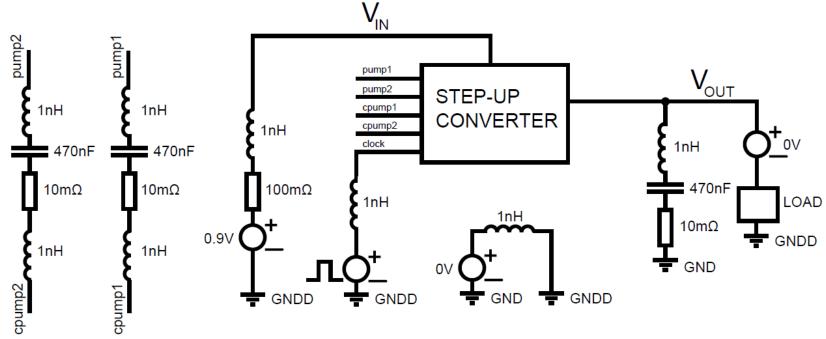

## Simulation cell for the transient analysis (including package components)

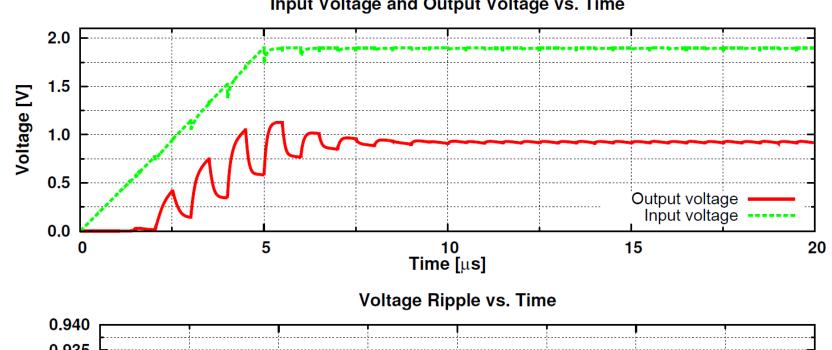

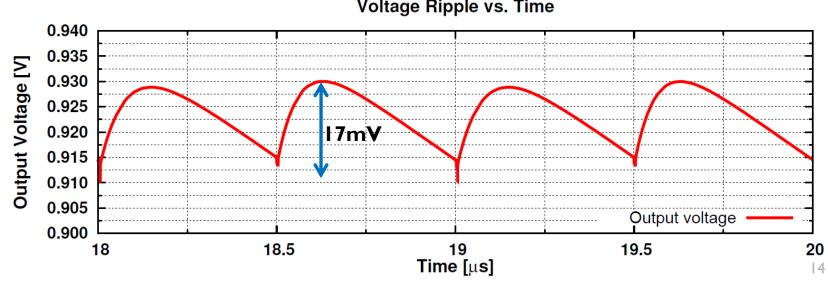

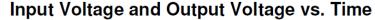

### Time response of the step-down converter (no wire bonds)

Input Voltage and Output Voltage vs. Time

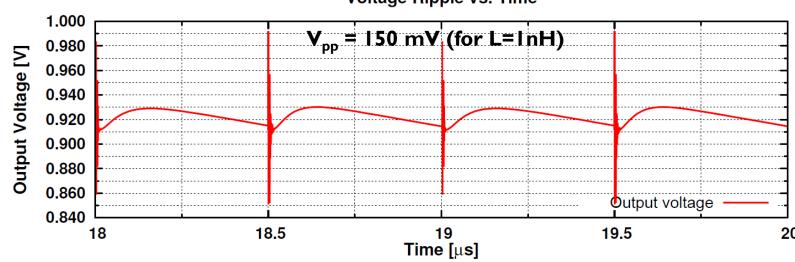

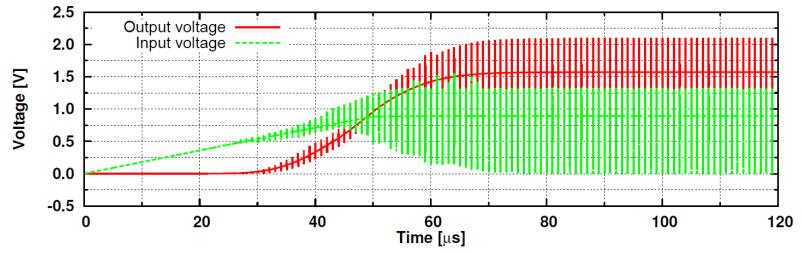

## Time response of the step-down (wire bond inductance included)

#### Voltage Ripple vs. Time

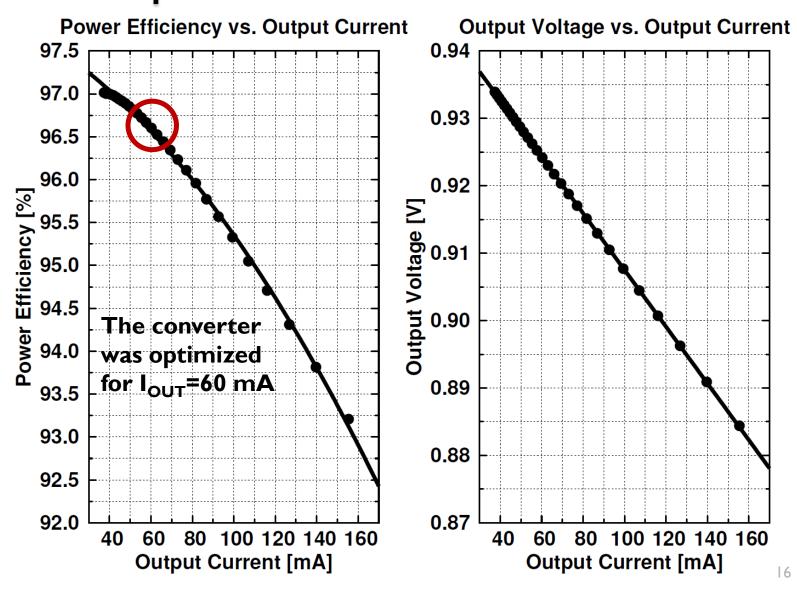

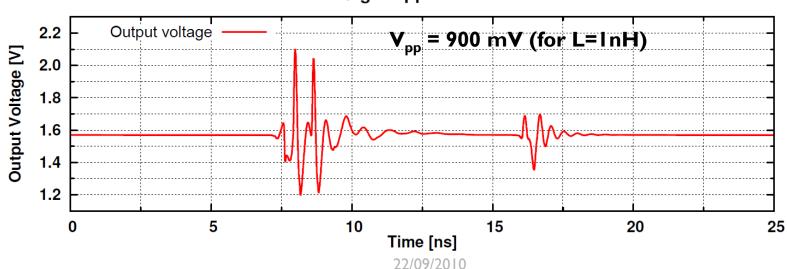

## Power efficiency and output voltage vs. output current

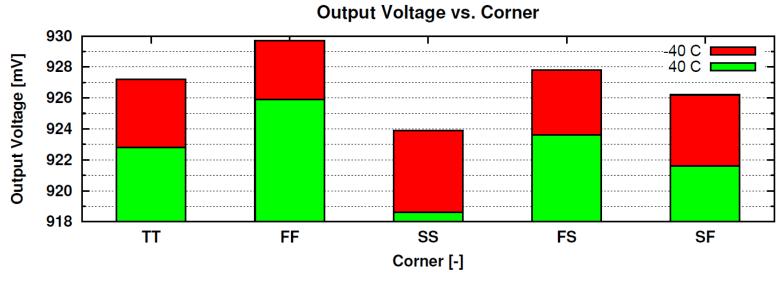

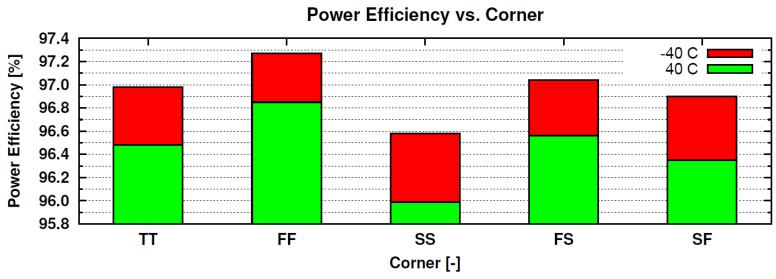

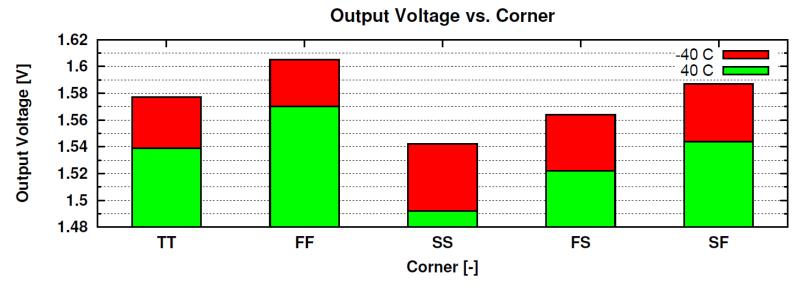

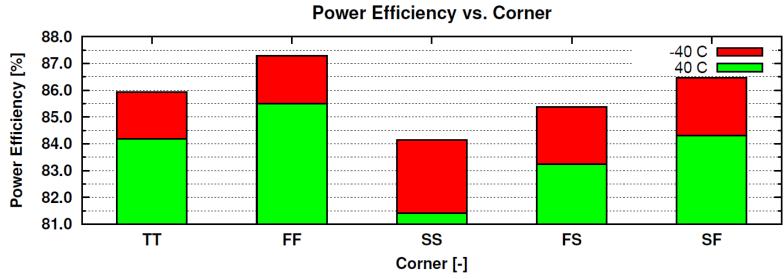

### Results from the corner analysis

## 2. Switched capacitor step-up converter

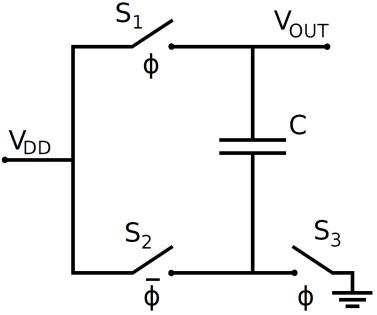

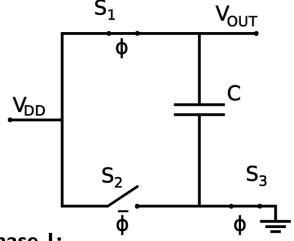

## A simple model of the step-up switched capacitor converter

- Three switches

- One capacitor

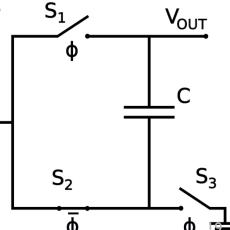

### Phase 2:

- Switches S<sub>1</sub> and S<sub>3</sub> are opened,

- Switch S<sub>2</sub> is closed,

- Bottom plate of the capacitor on  $V_{DD}$ , while the capacitor maintains its charge  $V_{DD}C$  (from the previous phase).

#### Phase I:

- Switches S<sub>1</sub> and S<sub>3</sub> are closed,

- Switch S<sub>2</sub> is opened,

- Capacitor is charged to the supply voltage  $V_{DD}$

$V_{DD}$

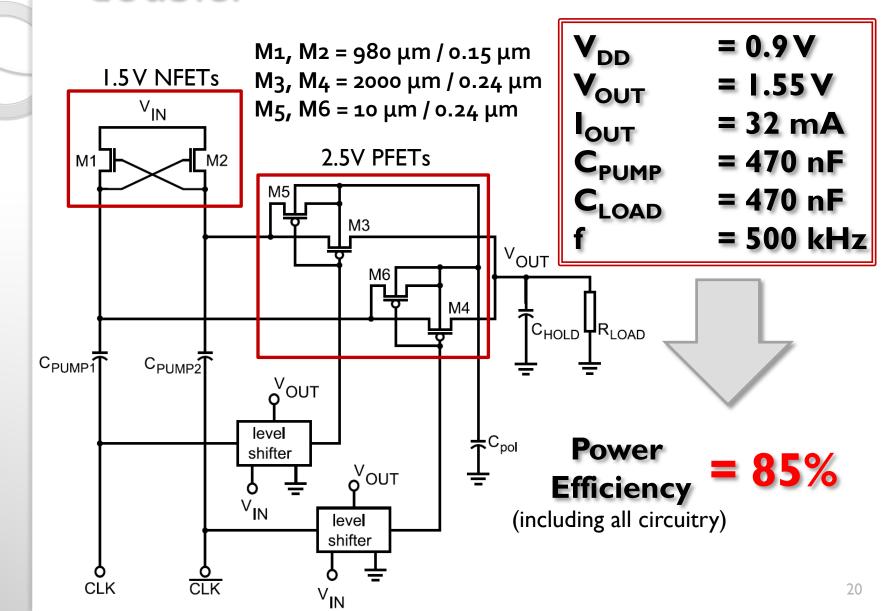

## Practical solution for the voltage doubler

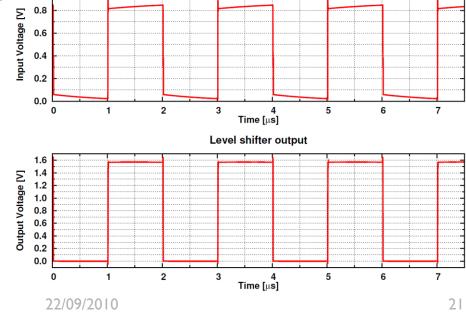

### Level shifter

Because of poor driving capability of used big PMOS serial switches two level shifters are needed

**V**OUT M5 M6  $\mathsf{CLK}_\mathsf{OUT}$ M1 CLKIN M2 M4

The level shifter requires two voltage supply domains: input voltage supply (0.9 V) and output supply (1.6 V) - taken from the output of the charge pump

Level shifter input

### Layout of the charge pump **Buffers Voltage Doubler** Level **Shifters** Clock **Generator Total area** $= 0.04 \text{ mm}^2$ 200 µm

## Simulation cell for the transient analysis (including package components)

22/09/2010 23

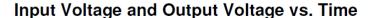

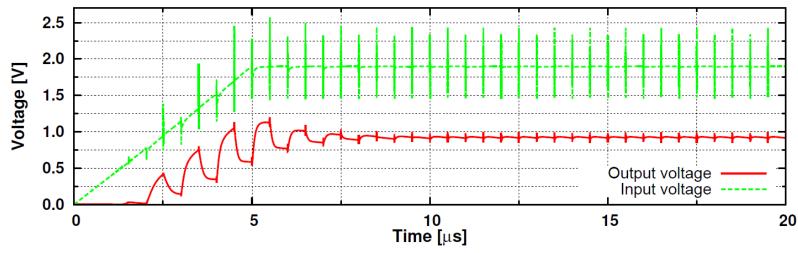

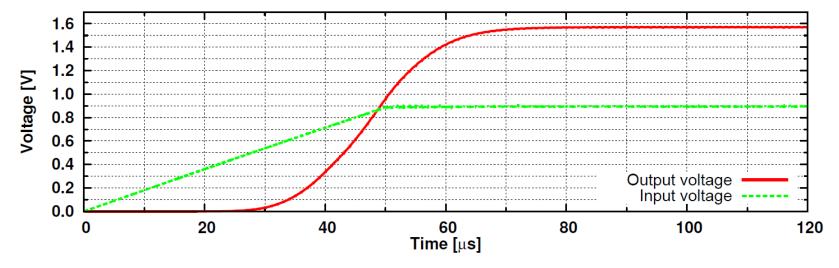

## Time response of the step-up converter (no wire bonds)

Input Voltage and Output Voltage vs. Time

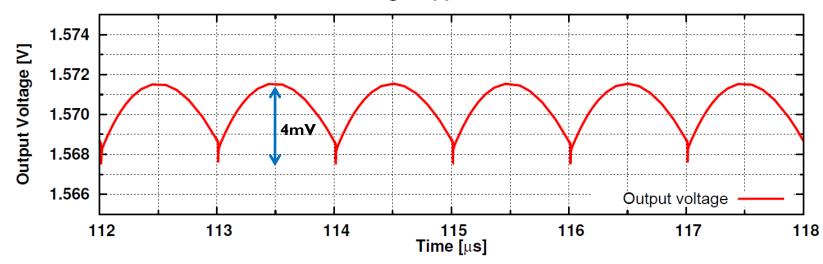

#### Voltage Ripples vs. Time

22/09/2010

24

## Time response of the step-up (wire bond inductance included)

#### Voltage Ripples vs. Time

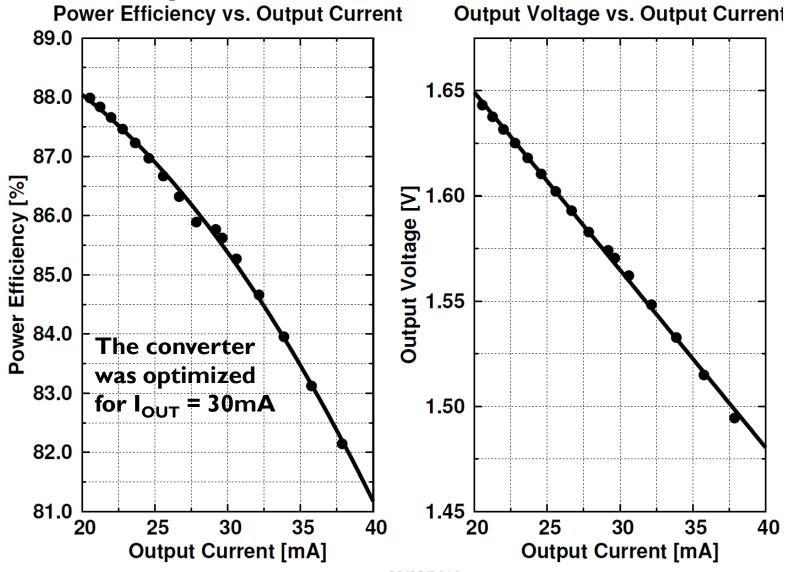

## Power efficiency and output voltage vs. output current

22/09/2010 26

### Results from the corner analysis

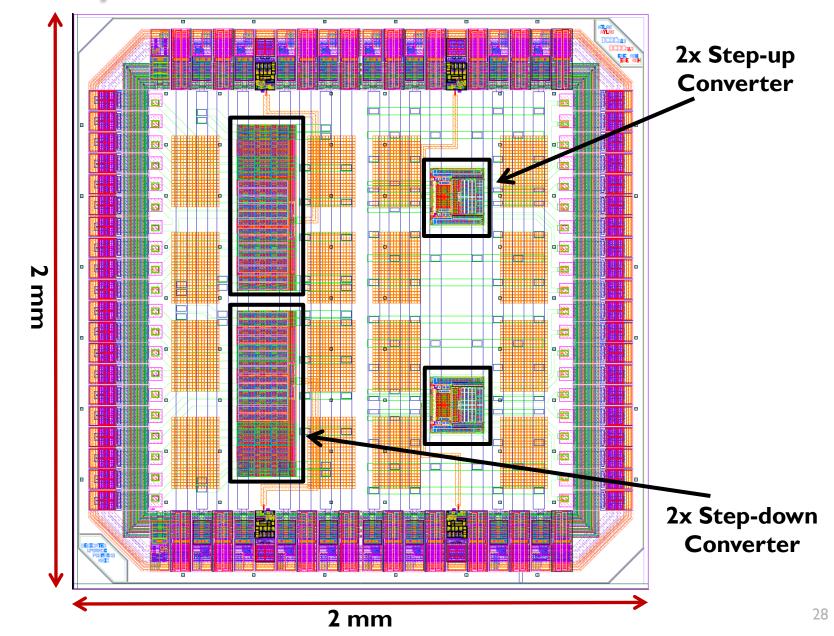

### Layout of the DCDC013

### Conclusions

- The results from the Spectre simulations are quite promising:

- $\eta$  = 97% for the step-down converter,

- $\eta = 85\%$  for the step-up converter.

- The inductance of the bond wires causes fast voltage spikes the padring was designed to reduce the influence of the bond wire inductance.

- Therefore, the use of the DC-DC converters mounted on the **separate chip** with **C4 pads** should be considered.

- The chip was submitted at the end of August 2010.

- The PCB board is now in production and will be ready before the arrival of the chips.

22/09/2010 2

### Thank you!

This research project has been supported by a Marie Curie Initial Training Network Fellowship of the European Community's & Seventh Framework Programme under contract number (PITN-GA-2008-211801-ACEOLE)