# ESS VMM3a news

#### **RD51** Collaboration Meeting

October 21st to 23rd

Dorothea Pfeiffer (ESS) Jerome Samarati (ESS) Richard Hall-Wilton (ESS)

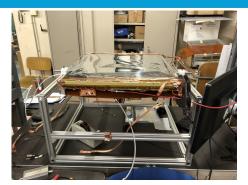

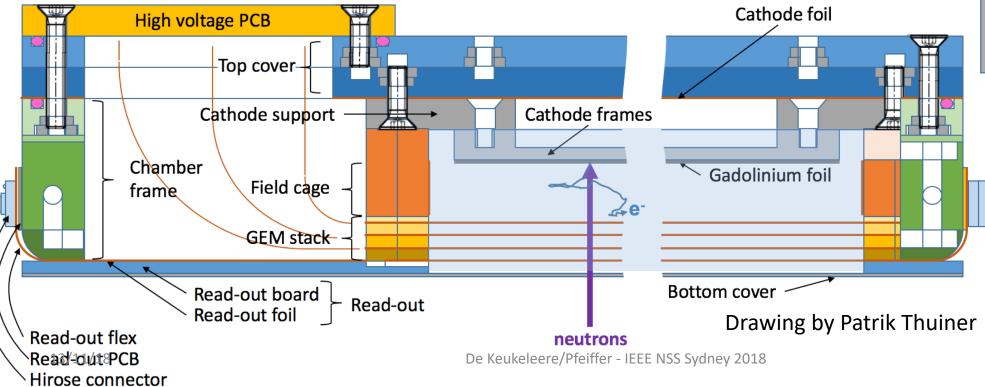

## VMM3a Gd-GEM for NMX

Edge

**GEM** with frame

and spacers

- Detector Demonstrator Zita

- 80 VMM3a per detector (5120 channels per detector)

- Will start tests with Xrays, neutrons and VMM3a (one detector quadrant) in October

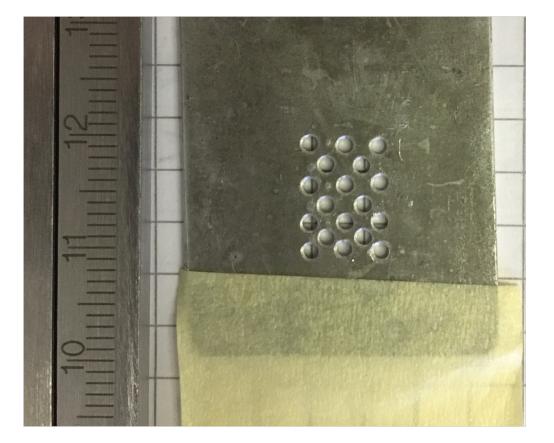

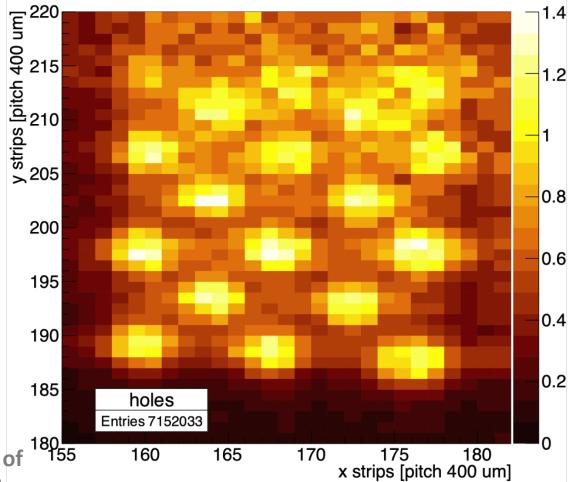

#### VMM3a NMX detector test at BNC July 2018

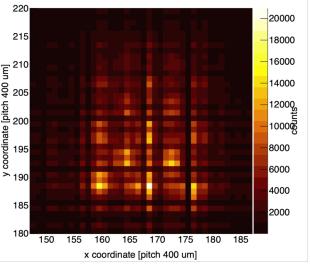

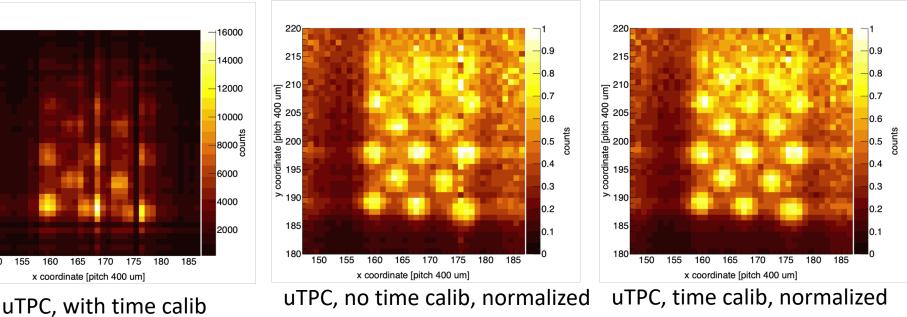

Cd mask, 1mm holes, normalized, time corrected

- Beam focused on lower three rows of Cd mask

- Clearly resolved holes with minimum separation (centre to centre) of about 2.0 mm horizontally, 1.6 mm vertically, and 1.3 mm diagonally

VMM delivering quality data from demonstrator

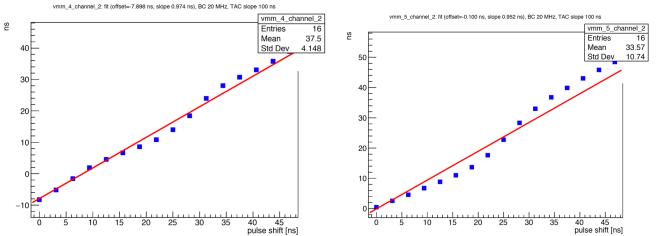

### NMX detector test at BNC July 2018 Time calibration and normalization

220

215

ੰਬੂ <sup>210</sup>

§ 205

<u>ā</u> 200

195

> 190

185

180

150

165

#### uTPC, no time calib

- For center-of-mass like algorithms, ADC calibration necessary

- For utpc like algorithms, also time calibration

- Both implemented in slow control, DAQ and reconstruction

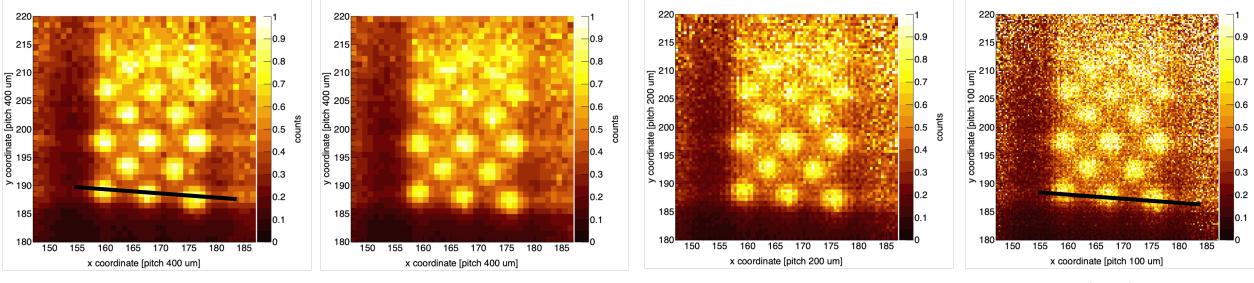

## NMX detector test at BNC July 2018 Improved analysis

EUROPEAN SPALLATION SOURCE

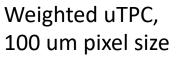

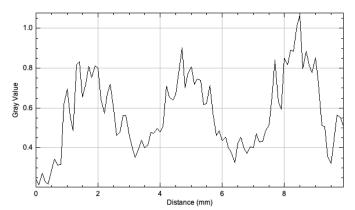

#### uTPC, 400 um pixel size

#### Weighted uTPC, 400 um pixel size

#### Weighted uTPC, 200 um pixel size

Ongoing work on algorithms and detector settings

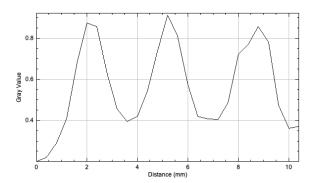

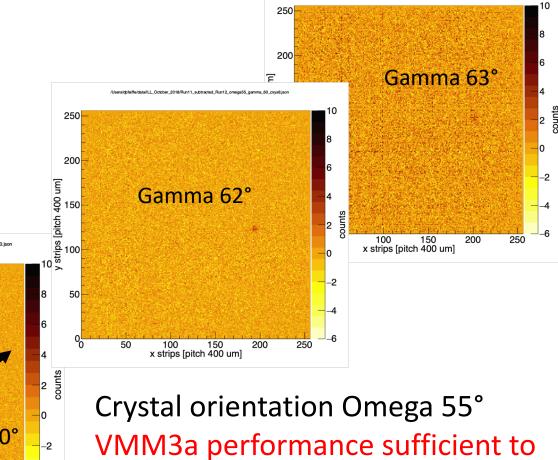

#### VMM3a NMX detector test at D16 at ILL October 2018

ers/dpfeiffe/data/ILL\_October\_2018/Run13\_omega5\_gamma\_63\_subtracted\_Run12\_cxys8.js

Crystal diffraction sample: Triose phosphate isomerase w/ 2-phosphoglycolate (2PG) inhibitor

resolve weak reflections

#### VMM3a Multiblade test at Utgard December 2018

EUROPEAN SPALLATION SOURCE

- Successful test of VMM3a hybrid with MB

- MB: Charge injection into:

- Wires (negative polarity, AC coupled)

- strips (positive polarity, DC coupled)

- Successfully read out with VMM3a via analog monitoring output and digital data in continuous mode

- Gain 1 mV/fC , 200 ns shaping time

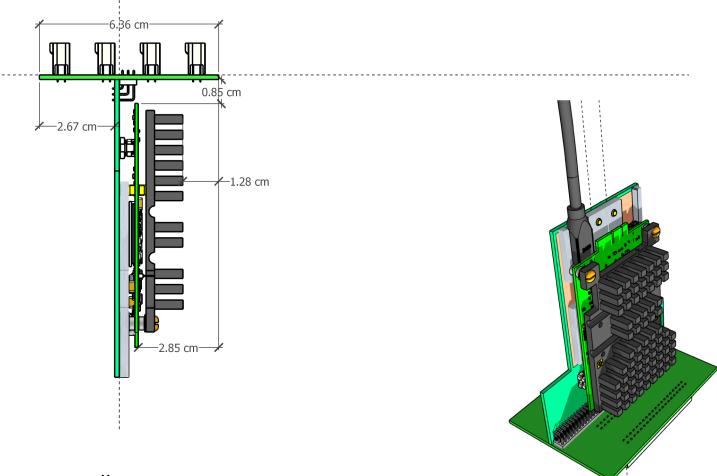

### Multiblade Adapter for RD51 VMM3a hybrid

Designed by Hans Muller

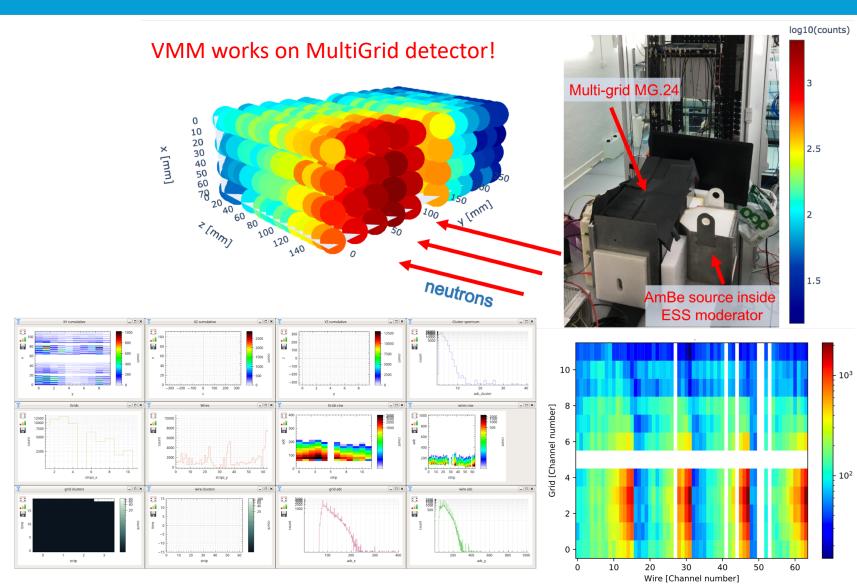

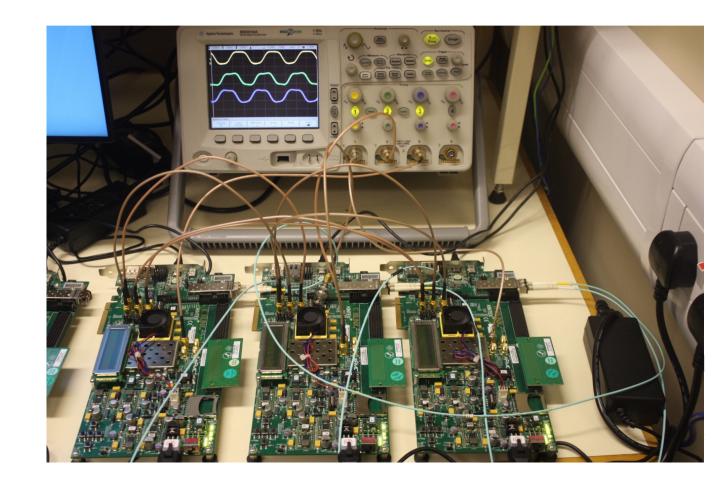

#### VMM3a Multigrid test at STF Summer 2019

- Started in May to test VMM3a together with Multigrid

- Huge team effort between detector group (Ramsey, Alex, Isabell, Doro) and DMSC (Morten, Martin)

- As expected, biggest challenges at the beginning: Mapping and noise

## VMM3a Multigrid test at STF Summer 2019

- Analog matching of VMM to MG succesful

- After solving mapping and noise issue, successful reconstruction of source position

- Wires and grids read out with VMM3a gain of 1mV/fC

- Optimization: Matching of detector gain to VMM3a gain to use full range of 10 bit ADC

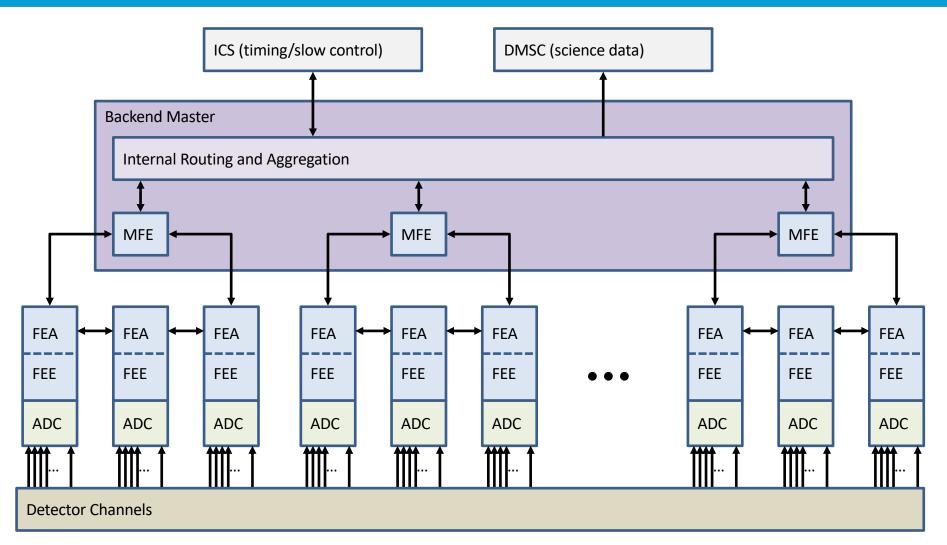

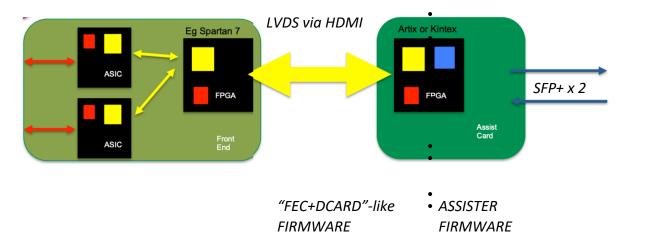

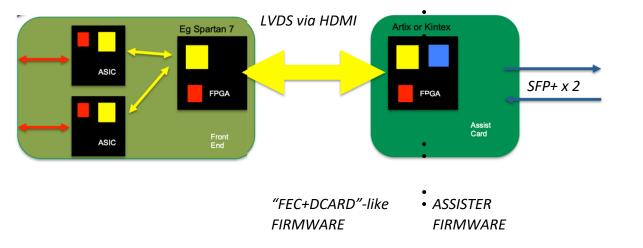

## Schematic drawing of ESS Readout

# Timing distribution in rings

- Front ends (FEA/FEE) connected to Master (MFE) via 8b/10b encoded SFP+ links.

- ESS clock used to generate these links

can be recovered and forwarded by each front end (similar concept to Synchronous Ethernet).

- The ESS timestamp can therefore be forwarded to all the front ends, forming a single distributed synchronous system.

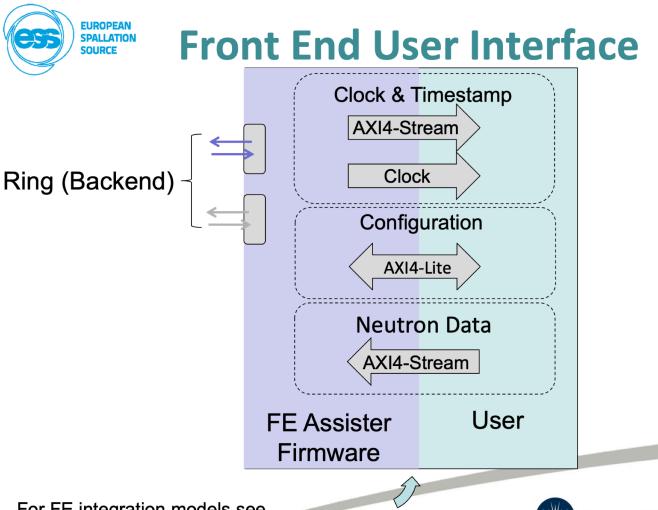

## FE user interface

- FEA (front end assister) firmware communicates with the ring/backend

- FEE (front end user firmware) communicates with frontend ASIC like VMM3a or ADC

- FEA and FEE part of firmware communicate via AXI4 streams

For FE integration models see BrightnESS Deliverable Report: D4.1 – Integration Plan for Detector Readout, Scott Kolya et.al. 2017

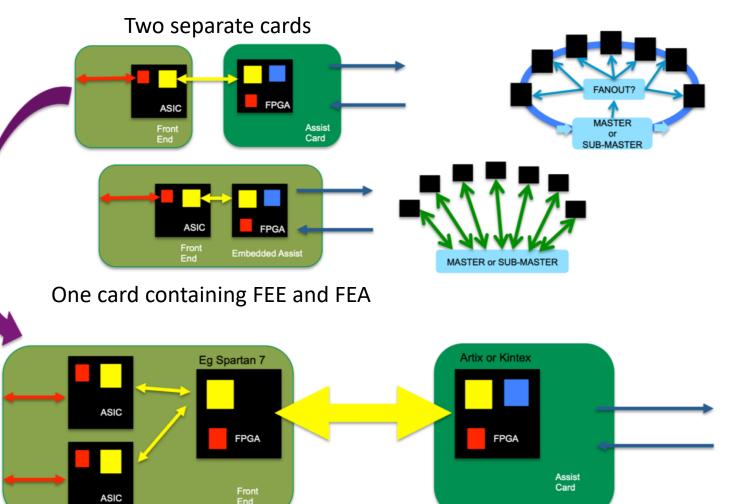

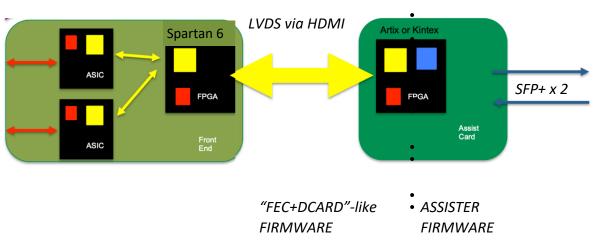

# Frontend (FEE) and assister (FEA): hardware and firmware modules

- Frontend FEE with firmware communicating with ASIC

- Frontend assister FEA with firmware to communicate with ring

- Could be in one FPGA and one card, or two FPGAs and two cards

- Advantages for two card solution: RD51 hybrid already exists, form factor of FEE card can stay small, heat dissipated on FEA card away from FEE

FEE card to communicate with ASIC

FEA card to communicate with ring

Step 1a (existing RD51 hybrid with Spartan6): Improve hybrid firmware, develop assister firmware

#### **Start immediately**

- Use existing RD51 VMM3a hybrid with Spartan 6

- RD51 hybrid firmware objectives:

- Support high rate operations

(part of general high rate optimizations of whole readout chain)

- Structure, clean up and document

- Use FPGA development board as assister platform

- Develop firmware for assister Artix7 FPGA

# Step 1b (use dedicated assister hardware):

.

#### Within the next six months

- Use dedicated assister hardware

- Assister layout for beam monitor readout already exists, can be modified for RD51 hybrid

# Step 1c (upgrade RD51 hybrid with Spartan7 or Artix7):

#### More longterm

- Explore options to upgrade RD51 hybrid to use Series 7 FPGA

- Have hybrid design modified by Alex

- Port firmware to Series 7 FPGA

# To be discussed, who would like to join

- Hans (RD51)

- Alex (SRS Technologies)

- Steven, Doro (ESS)

- Michael, students (Bonn)

- Chinese student funded by RD51/ESS

Team for changes

UNIVERSITÄT BONN

- Order for 56 hybrids out (46 for ESS, 10 for Bonn)

- Hybrids produced from one single wafer

- Outcome will determine yields and quality

- Yield said to be > 80%, but assume 50% for excellent quality

- Lower quality chips can be used for other purposes.

- We should allow for upgrades

- We should allow for spares ... these are always in short supply. x%? 50%? 100%? (not decided yet)

### ESS VMM3a expected numbers

- NMX: 5120 strips/detector: 240 VMM

- ESTIA: 2 VMM/cassette, 40 cassettes: 80 VMM (or twice for upgrade)

= 160 VMM

- FREIA: 2 VMM/cassette, 40 cassettes: 80 VMM

- CSPEC: <13000 grids, 5200 wires. 300 VMM

- TREX: 9000 grids, 8000 wires. 270 VMM

- Lab systems: ca. 100 VMM

- Total: 650? 25 or 50 wafers = 2500 or 5000 chips?

- How do we store extra wafers?

- Future:???: VOR: 16000 grids, 6000 wires. 350 VMM.