## Cost, Schedule and Risks

### Alexei N. Safonov, CMS Muon GEM Upgrade Coordinator GE2/1 TCR Review August 30, 2019

Alexei N. Safonov

CMS GE2/1 TCR

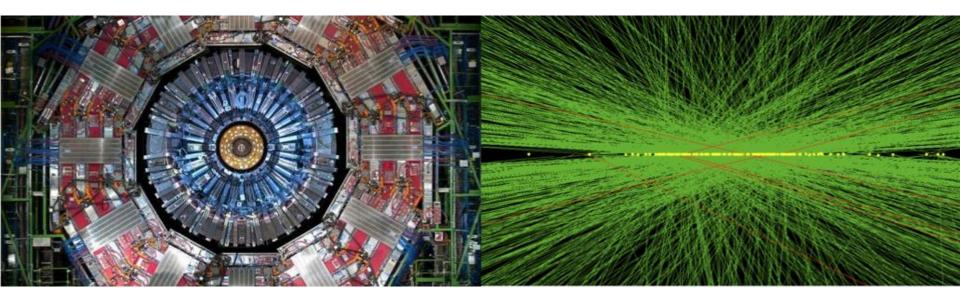

## CMS Muon Upgrade Scope

Alexei N. Safonov

CMS GE2/1 TCR

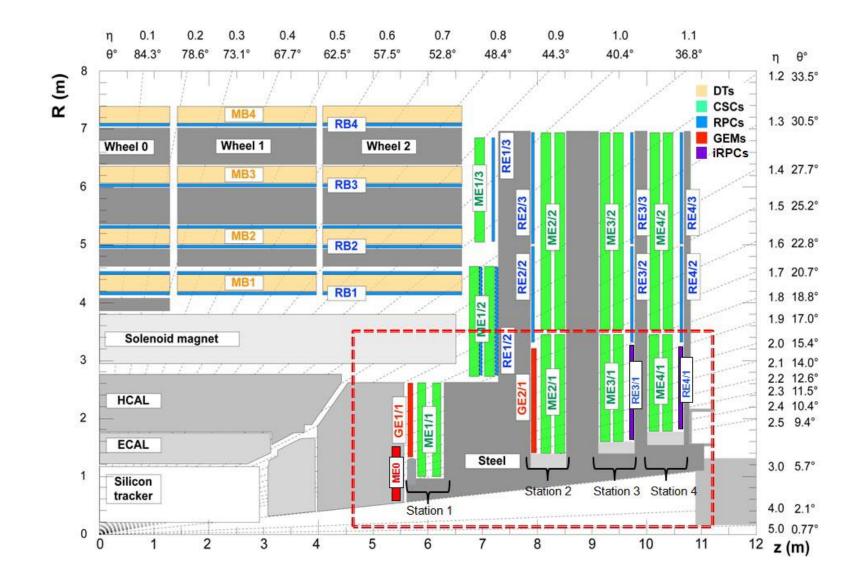

### Science Requirements

- Impact on a broad range of physics: Higgs, EW measurements and new physics searches, e.g. searches for long-lived particles decaying to muons

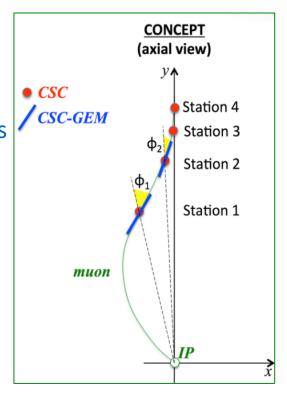

- Principles similar to GE1/1:

- Works with the CSC

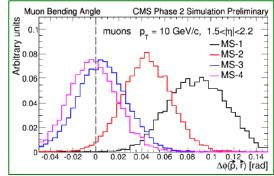

- Boost segment-finding efficiency

- Disentangle combinatorial "ghosts" in CSCs (short strips in GEMs)

- Muon direction within a station

- Trigger performance sets key design requirements:

- Position and timing resolution

- Additional requirements set by "environmental" factors:

- Operational capabilities provided high incident hit rate, radiation environment, longevity, compact design due to limited spaces, cost optimization etc.

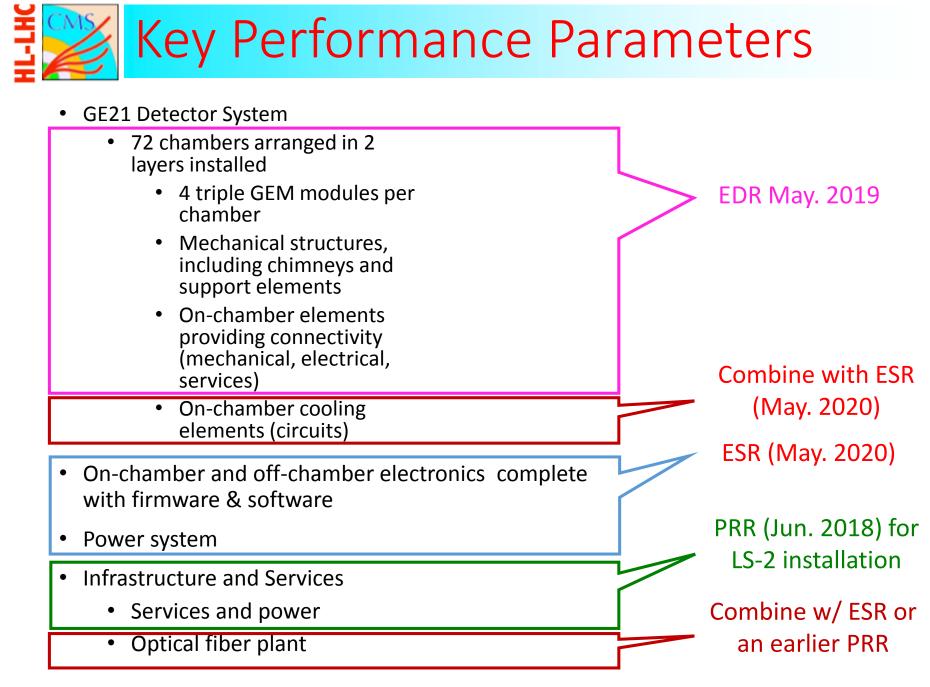

# Key Performance Parameters

- GE21 Detector System

- 72 chambers arranged in 2 layers installed

- 4 triple GEM modules per chamber

- Mechanical structures, including chimneys and support elements

- On-chamber elements providing connectivity (mechanical, electrical, services)

- On-chamber cooling circuits

- On-chamber and off-chamber electronics complete with firmware & software

- Power system

- Infrastructure and Services

- Services and power

- Optical fiber plant

Alexei N. Safonov

CMS GE2/1 TCR

# GE2/1 Milestones from TDR

#### • Up to the start of the construction project

|              | <i>J</i> 1                              | · 10                                                                                                                        |                                                         |                                                                                   |

|--------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------|

|              | ID                                      | Milestone title                                                                                                             | Date                                                    |                                                                                   |

| _            | GE21.RD.DET.1 GE21.RD.FE.1 GE21.RD.BE.1 | GE2/1 R&D: Key detector system design pa-<br>rameters are defined based on performance                                      | 21.Mar.17                                               | Achieved                                                                          |

| Design       | GE21.RD.FE.2                            | requirements<br>GE2/1 R&D: On-chamber electronics pre-<br>liminary design completed and interfaces<br>defined               | 19.Jun.17                                               | Achieved                                                                          |

|              | GE21.RD.BE.2                            | GE2/1 R&D: Off-chamber electronics pre-<br>liminary design completed and interfaces<br>defined                              | 12.Mar.18                                               | Achieved                                                                          |

|              | GE21.RD.DET.2                           | GE2/1 R&D: A full size chamber prototype<br>with partially instrumented readout built,<br>tested and performance validated  | 1.May.18                                                | Achieved                                                                          |

|              | GE21.RD.DET.3                           | GE2/1 R&D: Detector design parameters<br>optimization completed, final chamber de-<br>sign is selected for the demonstrator | 8.May.18                                                | Achieved                                                                          |

|              | GE21.RD.FE.3                            | GE2/1 R&D: On-chamber electronics proto-<br>types engineering design complete                                               | 1.Jun.18                                                | Achieved 28.Sep.18                                                                |

| Prototy ping | GE21.RD.FE.4                            | GE2/1 R&D: On-chamber electronics proto-<br>type electronics manufacturing and testing<br>is complete                       | 9.Oct.18                                                | Achieved 19.Feb.19                                                                |

| Proto        | GE21.RD.DET.4                           | GE2/1 R&D: Performance of the demonstra-<br>tor chamber with prototype electronics is<br>validated                          | 12.Mar.19                                               | Achieved 17. May. 19                                                              |

|              | GE21.RD.FE.5 GE21.RD.BE.3               | GE2/1 R&D: On-chamber and off-chamber<br>prototype electronics integration and perfor-<br>mance studies completed           | 12.Dec.19                                               | Expect in May.20                                                                  |

|              |                                         | GE2/1 PRR for the On-Detector Services<br>GE2/1 PRR for the Foil Production<br>GE2/1 Detector EDR<br>GE2/1 ESR              | 3.Aug.2018<br>13.Nov.2018<br>12.Mar.2019<br>12.Dec.2019 | Achieved (Jul.18)<br>Achieved 22.May 19<br>Achieved 22.May.19<br>Expect in May.20 |

#### • Up to the start of the construction project

|             | J 1                                       | . 10                                                                                                              |                                                         |                                                                                   |  |  |  |  |  |  |  |

|-------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|             | ID                                        | Milestone title                                                                                                   | Date                                                    |                                                                                   |  |  |  |  |  |  |  |

|             | GE21.RD.DET.1 GE21.RD.FE.1 GE21.RD.BE.1   | GE2/1 R&D: Key detector system design pa-<br>rameters are defined based on performance                            | 21.Mar.17                                               | Achieved                                                                          |  |  |  |  |  |  |  |

| Design      | GE21.RD.FE.2                              | requirements<br>GE2/1 R&D: On-chamber electronics pre-<br>liminary design completed and interfaces<br>defined     | 19.Jun.17                                               | Achieved                                                                          |  |  |  |  |  |  |  |

|             | GE21.RD.BE.2                              | GE2/1 R&D: Off-chamber electronics pre-<br>liminary design completed and interfaces<br>defined                    | 12.Mar.18                                               | Achieved                                                                          |  |  |  |  |  |  |  |

|             | CE21 PD DET 2                             | CE2/1 D&D. A full size chamber protoking                                                                          | 1 Mars 10                                               | d                                                                                 |  |  |  |  |  |  |  |

|             | Project high level sta                    | .u                                                                                                                |                                                         |                                                                                   |  |  |  |  |  |  |  |

|             |                                           |                                                                                                                   | be                                                      |                                                                                   |  |  |  |  |  |  |  |

|             | <ul> <li>Services: well in the</li> </ul> | ne construction phase                                                                                             | eu eu                                                   |                                                                                   |  |  |  |  |  |  |  |

|             | • Chambers: early c                       | onstruction phase (han                                                                                            | nnered hv                                               | d 29 Cap 19                                                                       |  |  |  |  |  |  |  |

|             |                                           |                                                                                                                   | ipered by                                               | ed 28.Sep.18                                                                      |  |  |  |  |  |  |  |

|             | funding related delays)                   |                                                                                                                   |                                                         |                                                                                   |  |  |  |  |  |  |  |

| ping        | • Electronics: last st                    | ed 19.Feb.19                                                                                                      |                                                         |                                                                                   |  |  |  |  |  |  |  |

| Prototyping | GE21.RD.DET.4                             | is complete<br>GE2/1 R&D: Performance of the demonstra-<br>tor chamber with prototype electronics is<br>validated | 12.Mar.19                                               | Achieved 17.May.19                                                                |  |  |  |  |  |  |  |

|             | GE21.RD.FE.5 GE21.RD.BE.3                 | GE2/1 R&D: On-chamber and off-chamber<br>prototype electronics integration and perfor-<br>mance studies completed | 12.Dec.19                                               | Expect in May.20                                                                  |  |  |  |  |  |  |  |

|             |                                           | GE2/1 PRR for the On-Detector Services<br>GE2/1 PRR for the Foil Production<br>GE2/1 Detector EDR<br>GE2/1 ESR    | 3.Aug.2018<br>13.Nov.2018<br>12.Mar.2019<br>12.Dec.2019 | Achieved (Jul.18)<br>Achieved 22.May 19<br>Achieved 22.May.19<br>Expect in May.20 |  |  |  |  |  |  |  |

Alexei N. Safonov

CMS GE2/1 TCR

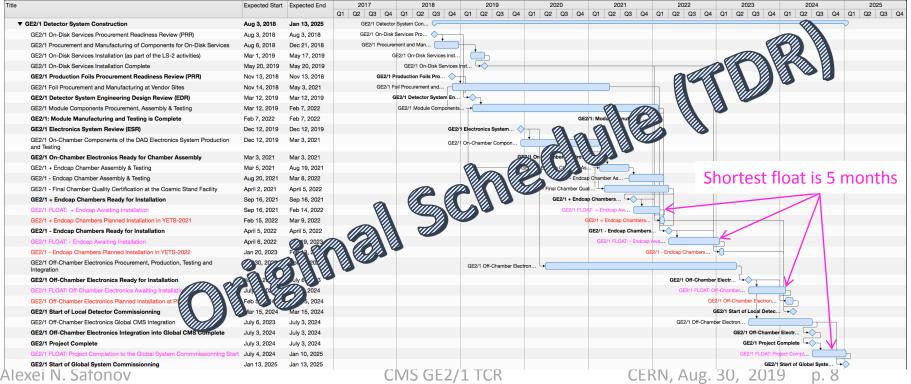

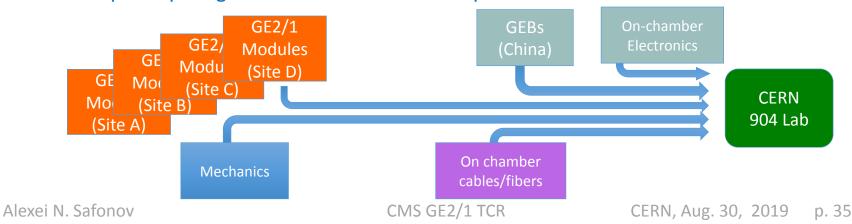

# GE2/1 Construction Schedule Overview

#### EDR, ESR, PRR kick-start the project, subject to various constraints

R&D program completion, availability of the facilities for module/chamber assembly, funding availability, resource leveling among three GEM projects (GE1/1, GE2/1, ME0)

#### Critical path for the GE2/1 project:

- Chamber assembly has to finish in time for installation

- Assembly is preceded by GEM module and on-chamber electronics production

- Shortest float is 5 months for "+" Endcap

- Actual floats somewhat larger due to staggering of batches

### Schedule Updates

- Update to the CMS official need-by-date for the full GE2/1 system to be ready for installation:

- Ready for installation: August 2023

- Readiness in the baseline schedule should be at least 6-12 months earlier to provide adequate float for delays as a number of risks will realize

- Significant change compared to the original needby dates set in the TDR:

- Ready for installation Endcap-1: Feb. 2022

- Ready for installation Endcap-2: Jan. 2023

- Additional (welcome) cushion to offset expected schedule delays, not a reason to slower down

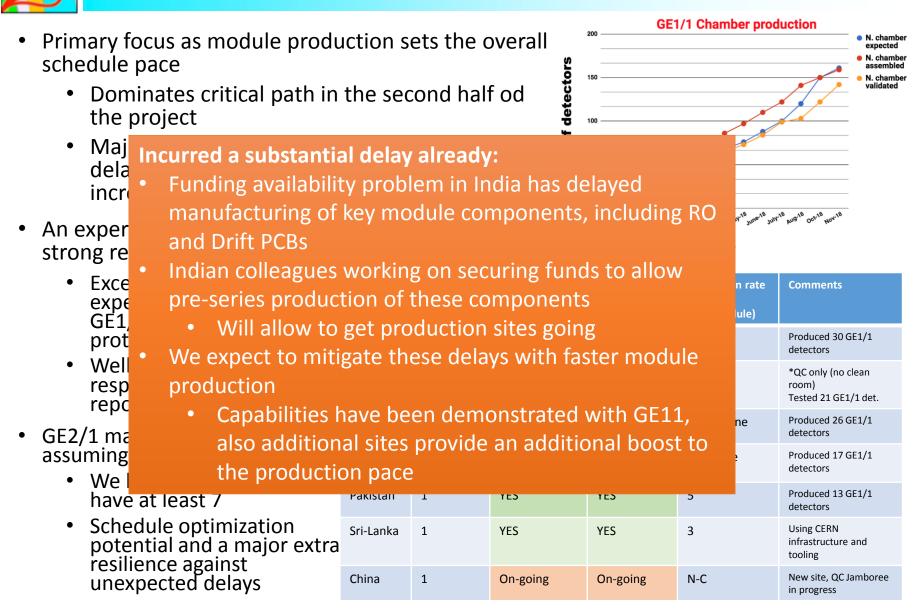

- We have seen significant risks that have already realized related to funding availability delays, e.g. in India

# New (Draft) Baseline Schedule

Chamber assembly completed well ahead of either the installation in YEST22-23 (9 months float) or the need-by-date of Aug.'23

| # WBS Code Title  |                                                                                                                            | Expected Start | 2015 2016                   | 2017                  | 2018                | 2019             | 2020                | 2021                                                                                                                                                                                         | 2022           | 2023             | 2024           | 2025          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|-----------------------|---------------------|------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|----------------|---------------|

| * VIDS Code Title |                                                                                                                            | Expected Start | Q3 Q4 Q1 Q2 Q3 Q4           |                       |                     |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 210 2.5.2.10      | ▼ GE2/1 Milestones                                                                                                         | Dec 20, 2016   | GE2/1 Milestones 👽          |                       |                     |                  |                     |                                                                                                                                                                                              |                |                  |                | $\rightarrow$ |

| 212 2.5.2.10.20   | GE2/1 R&D T5: Key Detector System Design Parameters Are Defined Based on Performance<br>Requirements                       | Mar 21, 2017   | GE2/1 R&D T5: Key Detec.    | 🔶                     |                     |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 215 2.5.2.10.40   | GE2/1 R&D T5: On-Chamber electronics preliminary principal design completed and interfaces<br>defined                      | Jun 19, 2017   | GE2/1 R&D T5: On-Cha        |                       |                     |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 216 2.5.2.10.60   | GE2/1 R&D T5: Preliminary Principal Design of the DAQ/Electronics System Complete                                          | Jun 19, 2017   | GE2/1 R&D T5: Preliminary I | P 4                   |                     |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 218 2.5.2.10.70   | GE2/1 R&D E5: Muon TDR Submitted to LHCC                                                                                   | Sep 12, 2017   | GE2/1 R&D E5: Muon 1        | TDR S 🗣 🔷             |                     |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 220 2.5.2.10.85   | GE2/1 R&D T5: Off-Chamber Electronics Preliminary Design Completed and Interfaces Defined                                  | Mar 12, 2018   | GE2/1 R                     | &D T5: Off-Chamb      | •                   |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 221 2.5.2.10.90   | GE2/1 R&D T5: Full Size Chamber Prototype with Partially Instrumented Readout Tested and Performance<br>Validated          | Apr 24, 2018   | GE2/1 F                     | R&D T5: Full Size Cha | 🔶                   |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 222 2.5.2.10.95   | GE2/1 R&D T5: A Full Size Chamber Prototype with Partially Instrumented Readout Built, Tested and<br>Performance Validated | May 1, 2018    |                             | &D T5: A Full Size    | •                   |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 224 2.5.2.10.106  | GE2/1 R&D T5: Chamber Design Opimization Studies Completed, Chamber Design Finalized                                       | May 8, 2018    |                             | R&D T5: Chamber       | •                   |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 226 2.5.2.10.120  | GE2/1 E5: PRR for On-Detector Services for Installation in LS-2                                                            | July 18, 2018  | GE                          | 2/1 E5: PRR for On-   | •                   |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 227 2.5.2.10.115  | GE2/1 R&D T5: On-chamber electronics prototypes engineering design complete                                                | Sep 28, 2018   |                             | GE2/1 R&D T5: On      | •                   |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 233 2.5.2.10.130  | GE2/1 R&D T5: On-Chamber Prototype Electronics Manufacturing and Testing is Complete                                       | Feb 19, 2019   |                             |                       | D T5: On-Chamb      |                  |                     |                                                                                                                                                                                              |                |                  |                |               |

| 235 2.5.2.10.155  | GE2/1 R&D T5: Start Assembly of the GE2/1 Demonstrator with Prototype On-Chamber Electronics                               | Feb 20, 2019   |                             |                       | D T5: Start Assem   | •                |                     |                                                                                                                                                                                              |                |                  |                |               |

| 236 2.5.2.10.160  | GE2/1 R&D T5: Performance of the Demonstrator chamber with Prototype Electronics is Validated                              | May 17, 2019   |                             |                       | R&D T5: Performa    | •                |                     |                                                                                                                                                                                              |                |                  |                |               |

| 237 2.5.2.10.185  | GE2/1 T5: On-Disk Services Installation at P5 is Complete                                                                  | May 20, 2019   |                             |                       | 1 T5: On-Disk Serv  | ~ ~              |                     | All (                                                                                                                                                                                        | 3E21 (         | chamb            | oers 📃         |               |

| 238 2.5.2.10.140  | GE2/1 T5: PRR for Foil Production                                                                                          | May 22, 2019   |                             |                       | 5: PRR for Foil Pro |                  |                     |                                                                                                                                                                                              | - In a -       |                  | al.            |               |

| 240 2.5.2.10.170  | GE2/1 E5: EDR (CMS TC - External Constraint)                                                                               | May 22, 2019   |                             | GE2/1                 | E5: EDR (CMS TC     | 🗣 🔷              |                     | tes                                                                                                                                                                                          | ted a          | nd rea           | ay             |               |

| 243 2.5.2.10.190  | GE2/1 R&D T5: On- and Off-Chamber Readout Prototype Electronics Integration and Performance<br>Studies Completed           | Dec 12, 2019   |                             |                       |                     | 5: On- and Off 🔶 |                     | fo                                                                                                                                                                                           | r insta        | allatio          | n:             |               |

| 244 2.5.2.10.200  | GE2/1 E5: ESR (CMS TC - External Constraint)                                                                               | April 3, 2020  |                             |                       | GE2/1 E             | 5: ESR (CMS TC   | <b>└</b> •◇         |                                                                                                                                                                                              |                |                  |                |               |

| 254 2.5.2.10.413  | GE2/1 T5: On-Chamber electronics components ready for Disk-1 Chamber Assembly                                              | Feb 12, 2021   |                             |                       |                     |                  | On-Chamber elec     | <h><hr/><h><hr/><h><hr/><h><hr/><h><hr/><h><hr/><h><hr/><h><hr/><h><hr/><h><hr/><hr< td=""><td>vpr. 22</td><td>2, 2022</td><td>2</td><td></td></hr<></h></h></h></h></h></h></h></h></h></h> | vpr. 22        | 2, 2022          | 2              |               |

| 257 2.5.2.10.220  | GE2/1 T5: Disk 1 Chamber Assembly Starts (FIXED EARLIEST START 03-MAR-21/RESOURCE LEVELING)                                | Apr 23, 2021   |                             |                       |                     |                  | 5: Disk 1 Chamber A |                                                                                                                                                                                              | ·              | ·                |                |               |

| 258 2.5.2.10.412  | GE2/1 T5: On-Chamber electronics components ready for Disk-2 Chamber Assembly                                              | Mar 2, 2021    |                             |                       |                     |                  | n-Chamber elec      |                                                                                                                                                                                              |                | 1                |                |               |

| 261 2.5.2.10.210  | GE2/1 T5: On-Chamber Electronics Manufacturing and Testing is Completed                                                    | Mar 3, 2021    |                             |                       |                     | GE2/1 T5: Or     | n-Chamber Ele       | •                                                                                                                                                                                            |                |                  |                |               |

| 262 2.5.2.10.270  | GE2/1 T5: Module Manufacturing and Testing is Complete                                                                     | Dec 17, 2021   |                             |                       |                     |                  | GE2/1 T5: Mod       | Υ                                                                                                                                                                                            |                |                  |                |               |

| 265 2.5.2.10.280  | GE2/1 E5: xTCA Electronics Available for Ordering (External Constraint)                                                    | Mar 7, 2022    |                             |                       |                     |                  |                     | xTCA Electronics                                                                                                                                                                             |                |                  |                |               |

| 267 2.5.2.10.415  | GE2/1 T5: Disk 2 Chamber Assembly Starts                                                                                   | Oct 11, 2021   |                             |                       |                     |                  | GE2/1 T5: Disk 2 C  | · ·                                                                                                                                                                                          |                |                  |                |               |

| 270 2.5.2.10.260  | GE2/1 T5: Chambers for Disk-1 are Assembled, Tested, and Ready for Installation                                            | Nov 5, 2021    |                             |                       |                     |                  |                     | bers for Di 🔷                                                                                                                                                                                |                |                  |                |               |

| 271 2.5.2.10.275  | GE2/1 E5: Installation date agreed upon with TC Endcap 1 (External Constraint)                                             | Feb 14, 2022   |                             |                       |                     |                  |                     | Installation date                                                                                                                                                                            |                |                  |                |               |

| 272 2.5.2.10.285  | GE2/1 T5: Chambers for Disk-1 Installed and Tested                                                                         | Mar 9, 2022    |                             |                       |                     |                  |                     | Chambers for Disk 🔷                                                                                                                                                                          | ~              |                  |                |               |

| 277 2.5.2.10.300  | GE2/1 T5: Chambers for Disk-2 are Assembled, tested, and Ready for Installation                                            | Apr 22, 2022   |                             |                       |                     |                  | GE2/1               | 15: Chambers for Di                                                                                                                                                                          |                |                  |                |               |

| 278 2.5.2.10.350  | GE2/1 E5: Installation date agreed upon with TC Endcap 2 (External Constraint)                                             | Jan 19, 2023   |                             |                       |                     |                  |                     | GE2/1 E5: Installa                                                                                                                                                                           | ~              | >                |                |               |

| 279 2.5.2.10.360  | GE2/1 T5: Chambers for Disk-2 Installed and Tested                                                                         | Feb 13, 2023   |                             |                       |                     |                  |                     | GE2/1 T5: Chamber                                                                                                                                                                            |                |                  |                |               |

| 280 2.5.2.10.380  | GE2/1 T5: Off-Chamber Electronics Manufacturing and Testing Completed and Ready for Installation                           |                |                             |                       |                     |                  |                     | GE2/1 T                                                                                                                                                                                      | 5: Off-Chamber | ~                |                |               |

| 281 2.5.2.10.390  | GE2/1 E5: Local Detector Commissionning Starts (External Constraint)                                                       | Mar 15, 2024   |                             |                       |                     |                  |                     |                                                                                                                                                                                              |                | ocal Detector    | •              |               |

| 282 2.5.2.10.395  | GE2/1 T5: Off-Chamber Electronics Integration Complete                                                                     | July 3, 2024   |                             |                       |                     |                  |                     |                                                                                                                                                                                              | GE2/           | 1 T5: Off-Chambe | r Ele 🔶        |               |

| 283 2.5.2.10.400  | GE2/1 T5: Construction Project Complete. Ready for Global System Commissionning.                                           | July 3, 2024   |                             |                       |                     |                  |                     |                                                                                                                                                                                              | GE2/1          | T5: Construction | Pr +           |               |

| 284 2.5.2.10.405  | GE2/1 E5: Global System Commissionning Starts (External Constraint)                                                        | Jan 13, 2025   |                             |                       |                     |                  |                     |                                                                                                                                                                                              |                | GE2/1 E5: Glo    | bal System C 🔶 | $\diamond$    |

Alexei N. Safonov

CMS GE2/1 TCR

#### Assumptions:

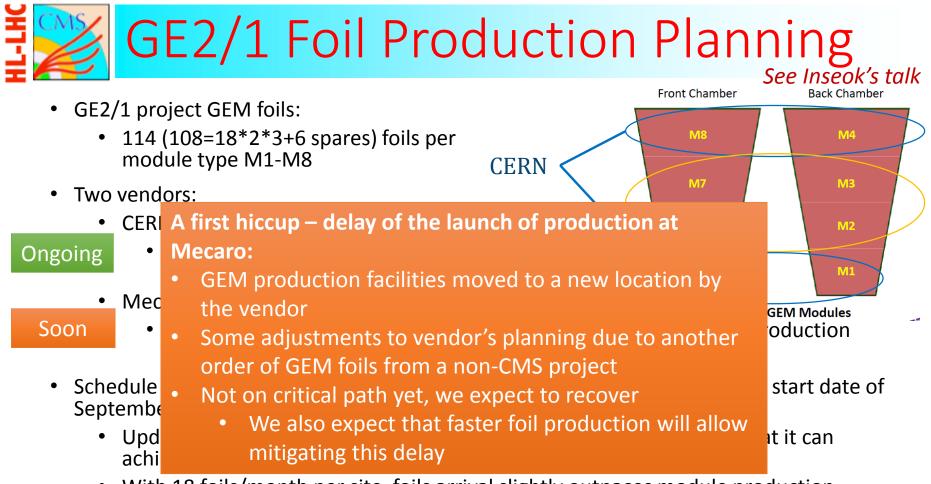

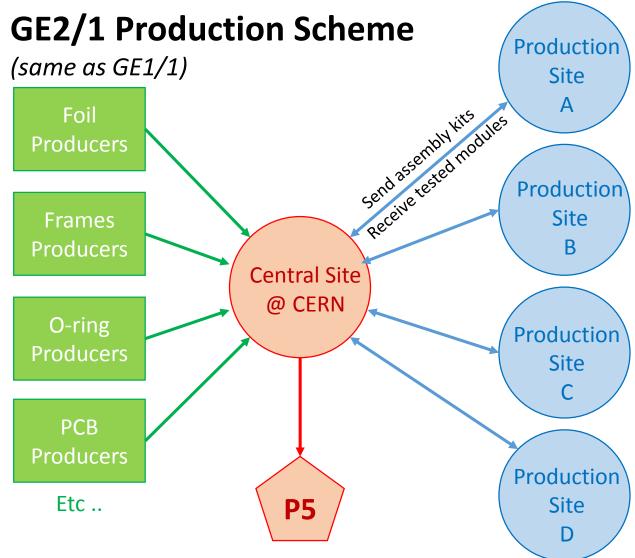

- Implement "faster" GEM module production based on a larger number of sites

- Credible based on GE11 experience, validated and presented at the GE21 EDR in May 2019

- Major impact on schedule dynamics: in previous versions, completion of the second endcap chamber assembly at CERN was dependent on too slow arrival of GEM modules

- Implement an adjustable external delay with the arrival of Indian funding for the corresponding risk

- Assume the start date of procurement of readout boards and other module components in Indian scope: Jan. 10, 2020

- Electronics R&D completion and approval for construction:

- ESR on Apr. 3, 2020; procurement of Versatile Link ASICs (GBTX, VTT/RX) procurement starts on Apr. 4, 2020

# **Design Evolution**

Alexei N. Safonov

CMS GE2/1 TCR

## **R&D** and Design Evolution

- An intense technical R&D program focusing on completing two main goals prior to the EDR:

- Thorough validation of the detector design

- Follow the experience and pay close attention to the lessons of the GE1/1 development and slice test

- Build validation program around verification of formal requirements, focus on identifying potential issues/concerns and developing solutions early

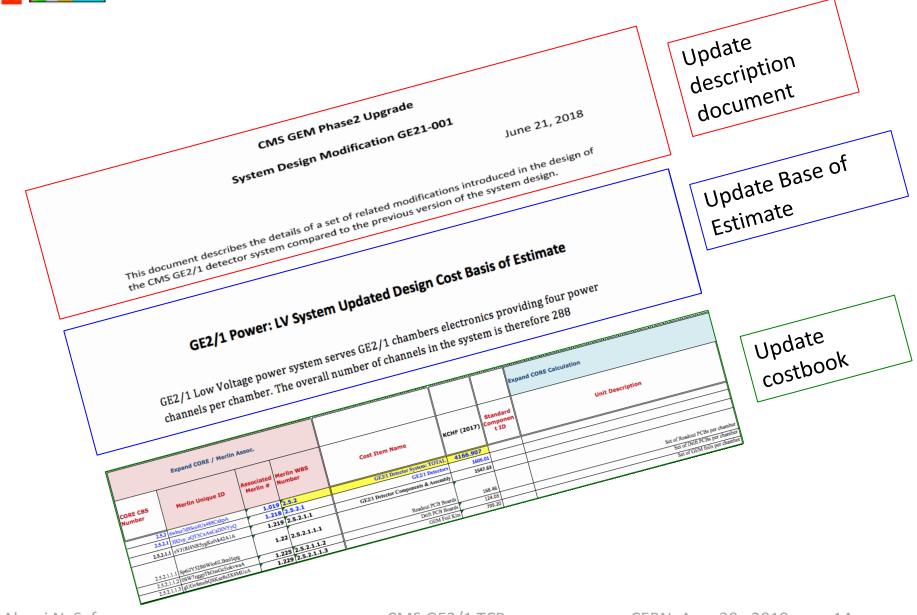

- Several non-negligible design improvements since TDR (change control)

- Validate and freeze interfaces

- Multi-faceted effort including validation of external mechanical interfaces, interfaces with services, internal interfaces, interfaces with the DAQ electronics

- Working our electronics interfaces has been a particularly high priority focus due to inherit complexities

- Closely integrated with the risk management program

CERN, Aug. 30, 2019 p. 13

Alexei N. Safonov

CMS GE2/1 TCR

### **GE2/1** Design Evolution

Alexei N. Safonov

CMS GE2/1 TCR

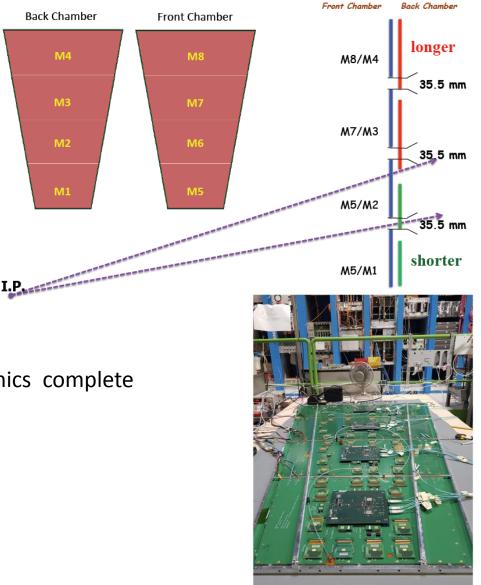

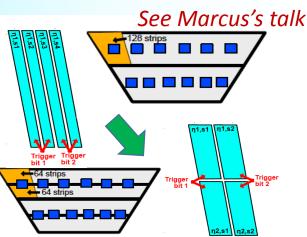

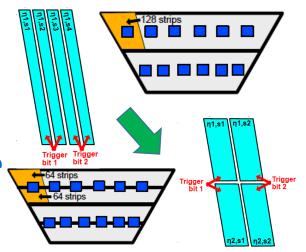

### Change-GE21-001-A: Strip Layout

- Measurements in the Spring of 2018 have shown higher than desired S/N

- GE21 strips are substantially longer than GE11

- Has been a tracked risk for a while

- Design modifications to the Readout Board:

- Split strips and change pairing for Level-1 trigger to reduce capacitance thus lowering noise

- Preserves Level-1 trigger granularity (trigger strips are pairs of strips)

- Actual measurements of S/N with the new layout are in progress

- A special ROB-OB GE11-size board manufactured and is being tested

- ROB-1A prototypes using new schema sent for production in July, will be arriving soon

- ROB-2 (final boards for EDR) to be launched shortly following testing of ROB-1A and ROB-0B

- Cost: no impact

- Schedule: has been fit into prototyping stages of the existing schedule

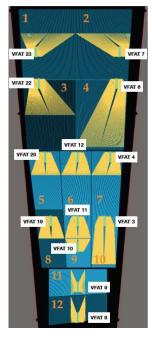

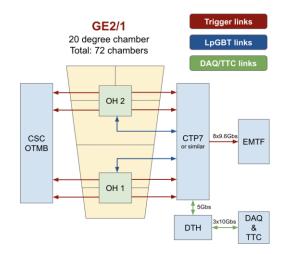

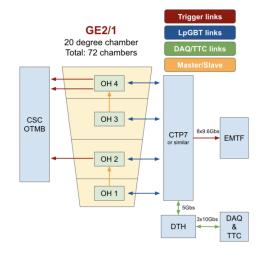

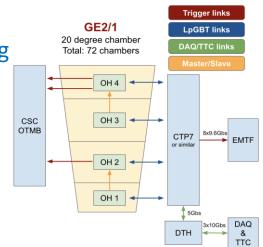

### Change-GE21-001-B: 2->4 OHs

- Motivation:

- Avoid potential mechanical stress issues (learnt from recent GE11 experience)

- Grounding/noise concerns to avoid introducing ground loops

- Reduce schedule risks (less dependences, e.g. don't need to have two modules to test optohybrids)

- Reduce impact of losing one OH (twice smaller area affected)

- Design modifications:

- Switch from using one OH per 2 adjacent modules to one OH per module

- Can use inexpensive FPGAs as each OH handles less VFAT3 FE ASICs (12 instead of 24)

- Consolidate trigger and data fiber paths, trigger will now use rad hard links

- Current developments full design cycle complete:

- New OHs: just arrived from the vendor, testing started

- ROBs: all 4 types in manufacturing

- GEBs: smallest module (highest density and complexity) in manufacturing, others will follow shortly

- Cost Impact: reduction by CHF 12k

- Schedule impact:

- Direct: 4 months delay (electronics design completion milestone slipped from June 1 to the end of September)

- Ultimate: mitigation to recover by EDR (March 12, 2019)

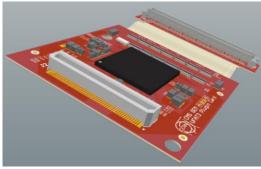

### Change-GE21-001-C: Plug-In Cards

- VFAT3 ASIC chips will be placed on special plug-in cards that connect to GEBs instead of direct soldering

- Not critical for GE21 as geometrical constraints are not a limiting factor

- Motivation:

- Schedule risks mitigation: allows parallel development of electronics and FE chip package as new electronics designs can be tested with existing GE11 hybrids, more time to allow full testing of the electronics until the arrival of packaged VFAT3 chips, less dependence on delays with packaged chips arrival, shorten schedule by removing R&D on soldering many chips on a thin large GEB board and vendor qualification

- Reduce technical risks associated with potentially low yield for GEBs with many soldered ASICs, simplifies long term maintenance (easy to remove and replace)

- Addresses export control issues (allows separating steps involving export controlled elements in manufacturing)

- Design modifications:

- New small PCBs holding VFAT3s, plug into the GEB boards and connect to the ROB via a flexPCB

- Current developments:

- Awaiting arrival of Gen-1 electronics prototypes (plug-in cards are not used in Gen-1 prototypes, instead we use GE11 hybrids), will launch production of flexPCBs and plugInCards with Gen-2 prototypes

- Cost Impact: increase by CHF 102k

- Schedule impact:

- Direct: 4 month delay to complete the design, which shifted the corresponding milestone from June 1 to the end of September (in reality, opportunistic in the shadow of the 2->4 OH changes)

Alexei N. Safonov

CMS GE2/1 TCR

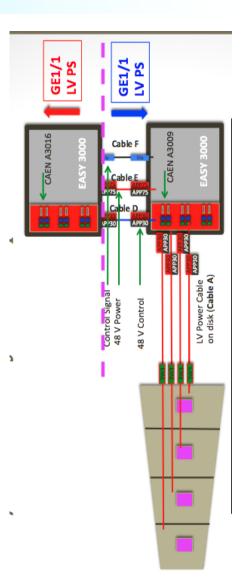

- Motivation:

- Matching changes for Change-GE21-001-B to allow independent powering of Ohs

- Technical risks mitigation reducing potential for elevated noise due to ground loops by disconnecting GEBs in different modules

- Design modifications:

- Change layout to add an extra mainframe, switch to a different type of LV power supply boards (less power, more channels), updated cable layout

- Current developments:

- All required new components identified, changes are straightforward

- On-disk elements design reviewed in CMS PRR over the summer

- Cost Impact: reduction by CHF 6.8k

- Schedule impact:

- No impact

## Lessons learned from GE1/1

- Substantial design modifications relative to the conceptual (TDR) design

- A number of them driven by the GE1/1 experiences

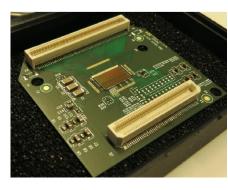

- In GE1/1, VFAT3 die bonded on hybrid:

#### GE1/1 hybrid:

- VFAT3 dies assembled on a small (~4.5 x 4.5 cm<sup>2</sup> rigid PCB)

- PCB difficult to manufacture and to bond, because of the small bond pitch (60 um)

#### Rigid+Flex PCB (PlugIn card): The flex part absorbs residual misalignment

In GE2/1, a packaged VFAT3 on a

- of GEB vs ROB • Rigid part is also

- Rigid part is also hosting VFAT3 input protection circuit

#### GE1/1:

- Optohybrid connected to two independent GEB half-boards

- Increased potential for mechanical stress

- Evolved powering schema and grounding

#### GE2/1:

- Each module has its own OH

- No potential for mechanical stresses from misalignments

- Independent powering, separate grounds

- Small lower power FPGA (Artix-7)

Alexei N. Safonov

CMS GE2/1 TCR

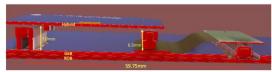

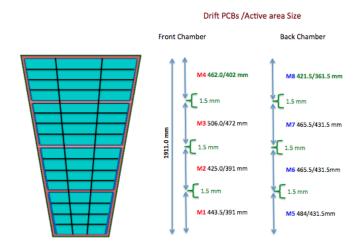

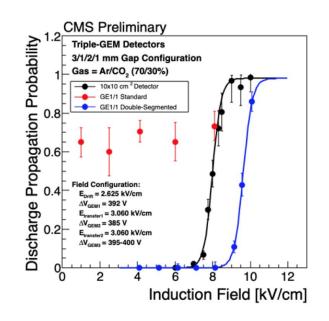

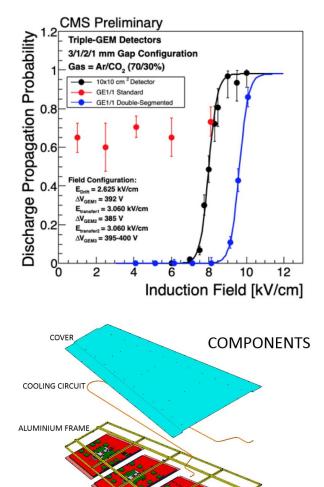

### Change GE21-002

- Rationale: a mechanical conflict discovered of the GE21 chamber in the TDR design with the elements of the RPC system

- Triggered expedited re-design of modules M4 and M8 mechanics and building new prototypes

- A second key change:

- Enhanced segmentation of GEM foils to reduce the energy released in discharges

- Further increases safety margin in addition to other system modifications to increase resistance to effects of discharges

- Cost impact insignificant

### Change GE21-003

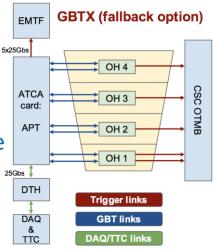

- Rationale: further delays of the LpGBT chip development

- Triggered re-design of the final system to use existing Versatile Link (VL) chipset instead of VL+

- No impact on physics performance, just more links to compensate slower link speed

- Links optimization (trigger links on rad hard path now)

- Increased backend system size without changes to architecture of baseline processor board

- Core cost increase around 200k CHF

- Additional backend boards and optical fibers

- The reality is that GBTX is more cost efficient once labor costs included (these elements are in the US scope where labor is part of the project cost)

#### Avoids delays as current electronics prototypes are very similar to the new baseline

- Intentional as we were planning that this risk may realize

- Avoids pushing GE21 schedule to overlap with the ME0 schedule

- This has been a major concern for the GEM upgrade coordination team

## GE2/1 DAQ/Electronics R&D

- One of the goals of electronics R&D has been to reliably freeze all chamber-electronics interfaces early

- Accelerate electronics development, heavy focus on early design integration to minimize mistakes

- Allow ample time for electronics integration and studies of the performance (noise levels!)

- Current status:

- Fully functional system on first trial with only a few trivial to fix issues related to optimization of component placement

- Mature near-final prototypes for the OH and GEBs, a bridging prototype of FlexPCB in order to use existing GE1/1 VFAT3 hybrid being replaced with an actual plugin-card

- Packaged prototype chips to arrive in the Fall, lots of logistics work to put a very well thought out contract for chip production

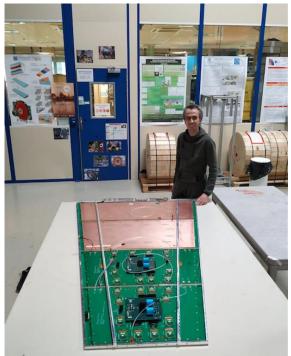

- Extensive testing at 904, the test stand bow includes chamber and the electronics

- Noise measured well below 1 fC excellent and well within specs

- Conclusions:

- Achieved mature level of understanding of the electronics design

- Interfaces frozen: remaining electronics developments are self-contained and do not affect chamber design

- The only exception is the cooling circle that we want to separate from this review

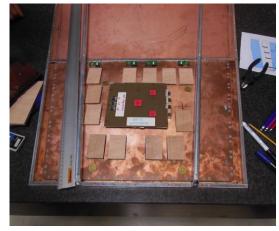

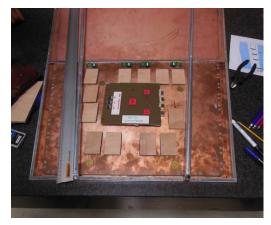

# GE2/1 Chamber Design Maturity

#### Chamber design development work flow:

- Establish a clear set of performance and operational requirements, track internal and external interfaces and external constraints

- Systematically validate each requirement through a dedicated test or tests yielding either a confirmation of the technical solutions or a design revision, systematically validate each interface via a dedicated test or other appropriate verification methods

- Including the GE1/1 experience, and the slice test studies

- Facilitate transparent development of interface areas

- The Triad Task Force working on the ROBflexPCB-GEB interface bringing people from the detector and electronics communities

- Formal internal reviews of all designs, which required sign-offs by the designers of the elements that have a common interface with the the design under review

- Integrate with the risk management program

PATCH PANEL

4 MODUL

### **R&D Steps to Completion**

### Electronics (ESR in late May 2020):

- Complete GEB boards M6-M8

- Drives critical path for the ESR readiness, risks moderate, it just takes time

- Minor adjustments and optimization of Optohybrid and select GEB boards to correct small mechanical issues

- Validate packaged VFAT3 chips

- Very close to critical path, may well get onto critical path if further delays

- Optimize chip protection and manufacture PlugIn-Cards

- Related to the above

- Integrate and test, including proof of principle with ATCA backend

- Lower risk, but potential for delays as the likelihood that at least one of over a dozen components would need another iteration is significant

### Reviews

- Many reviews as the system gets finalized:

- GEM Foils review to release design files and start production at Mecaro -Friday afternoon session

- GEB M6-M7-M8: need to finalize several rounds of reviewing the prototypes boards design to send them into production – this Friday afternoon session

- Been missing critical information and input from GEM mechanics/engineering team

- VFAT3 packaged chip design review next week

- Awaiting simulation results from the vendor

- Readout Board design review next week

- Finalize the decision on the copper layer based on all available information, essential to allow start of pre-series production in India

- PlugIn-Cards review upcoming, has dependencies:

- Requires final VFAT3 package design

- Requires a decision on the optimal spark protection electronics experts "camp" planned in around middle of November

- ATCA backend a full test-stand deployment planned for late Fall'19

- Surprises very unlikely as it is a generic plug-n-play optical backend; we are not relying on any "high tech" functionality of those boards

#### Coordinated by Kevin Black, the GEM upgrades reviews coordinator

- Became a full time job, we are lucky we have Kevin's help

- Critical element in risk mitigation towards the success of the project

### **Electronics** R&D Schedule

#### The "waterfall" plot for the updated R&D schedule

| -      |                                                                                                                                                                                                         | -              | -             | 04 (00)            | 01 (0015           | 00 ( 00 10               | 00 ( 00 0               | 0.1.10015              | 04 (0040               | 00 / 00/ 0           | 00 / 00 / -            | 0.1/0016                 | 04 (0005               | 00 ( 000-           | 00/07-7          |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|--------------------|--------------------|--------------------------|-------------------------|------------------------|------------------------|----------------------|------------------------|--------------------------|------------------------|---------------------|------------------|

| #▲ Tit | ,                                                                                                                                                                                                       | Expected Start |               | Q4 / 2017<br>11 12 |                    | Q2 / 2018<br>4 5 6       | Q3/2018<br>7 8 9        | Q4 / 2018<br>10 11 12  | Q1 / 2019<br>1 2 3     | Q2/2019<br>4 5 6     | Q3 / 2019<br>7 8 9     | Q4 / 2019<br>10 11 12    | Q1/2020<br>1 2 3       | Q2 / 2020<br>4 5 6  | Q3 / 2020<br>7 8 |

| 626    | Vilestones                                                                                                                                                                                              | July 11, 2018  | Aug 21, 2020  |                    |                    | Milestones               | •                       |                        |                        |                      |                        |                          |                        |                     |                  |

| 627    | GE2/1 R&D T4: Special ROB-0A prototype manufactured and ready for installation on chamber                                                                                                               | July 11, 2018  | July 11, 2018 | GE2/1 R&D          | T4: Special ROB-0A | prototype manufactu      | <b>♦</b>                |                        |                        |                      |                        |                          |                        |                     |                  |

| 628    | GE21 R&D T4: Gen-1 Prototypes Electronics Designs Complete, Ready for Project Level Review                                                                                                              | Sep 13, 2018   | Sep 13, 2018  |                    | GE21 R&D T4: G     | en-1 Prototypes Electro  | nics Designs 🔷          |                        |                        |                      |                        |                          |                        |                     |                  |

| 629    | GE2/1 R&D T4: Make a decision on the copper layer on ROB                                                                                                                                                | Sep 20, 2018   | Sep 20, 2018  |                    | GE2/1 R&D T4       | 4: Make a decision on th | e copper layer 🔷        |                        |                        |                      |                        |                          |                        |                     |                  |

| 630    | GE2/1 R&D T5: On-chamber electronics prototypes engineering design complete                                                                                                                             | Sep 28, 2018   | Sep 28, 2018  |                    | GE2/1 R&D          | T5: On-chamber electre   | onics prototype 🤇       |                        |                        |                      |                        |                          |                        |                     |                  |

| 631    | GE2/1 R&D T4: Special ROB-0B prototype manufactured and ready for installation on chamber                                                                                                               | Oct 4, 2018    | Oct 4, 2018   |                    | GE2/1 R&D          | T4: Special ROB-0B pr    | ototype manufact 4      | <b>&gt;</b>            |                        |                      |                        |                          |                        |                     |                  |

| 632    | GE2/1 R&D T4: ROB-1B prototype ready for installation on the demonstrator chamber                                                                                                                       | Nov 29, 2018   | Nov 29, 2018  |                    |                    | GE2/1 R&D T4: ROB-       | -1B prototype ready fo  | or installati 🔷        |                        |                      |                        |                          |                        |                     |                  |

| 633    | GE2/1 R&D T4: Initial Testing of GEB-1 and Mechanical Integration Validation Complete                                                                                                                   | Dec 5, 2018    | Dec 5, 2018   |                    |                    | GE2/1 R&D T4: Initia     | al Testing of GEB-1 and | d Mechanic 🔷           |                        |                      |                        |                          |                        |                     |                  |

| 634    | GE2/1 R&D T4: ROB-1A prototype ready for installation on the demonstrator chamber                                                                                                                       | Dec 7, 2018    | Dec 7, 2018   |                    |                    | GE2/1 R&D T4: RO         | B-1A prototype ready    | for installati 🔷       |                        |                      |                        |                          |                        |                     |                  |

| 635    | GE2/1 R&D T4: Make a decision on the ROB strip layout configuration                                                                                                                                     | Dec 13, 2018   | Dec 13, 2018  |                    |                    | GE2/1 R&D T4: M          | ake a decision on the   | ROB strip lay 🔷        |                        |                      |                        |                          |                        |                     |                  |

| 636    | GE21 R&D T4: uTCA-based Backend System for Gen-1/2 GE21 electronics is Ready for Trial Integration with<br>Gen-1 on-Chamber Electronics and Preliminary Measurements of Noise with Stage-1 Demonstrator | Dec 21, 2018   | Dec 21, 2018  |                    |                    | GE21 R&D T4: uT          | CA-based Backend S      | system for Gen 🔷       |                        |                      |                        |                          |                        |                     |                  |

| 637    | GE21 R&D T4: uTCA-based Backend System for Gen-1/2 GE21 electronics is Ready for Full Integration Testing<br>with Gen-1 on-Chamber Electronics                                                          | Jan 4, 2019    | Jan 4, 2019   |                    |                    | GE21 R&D T               | 4: uTCA-based Backe     | nd System for Gen      | •                      |                      |                        |                          |                        |                     |                  |

| 638    | GE2/1 R&D T4: All Gen-1 Electronics Boards for one module are ready for mechanical integration assessment<br>with the Stage-1 Demonstrator @ CERN                                                       | Feb 19, 2019   | Feb 19, 2019  |                    |                    |                          | GE2/1 R&D T4: All Ger   | n-1 Electronics Boards | for one 🔷              |                      |                        |                          |                        |                     |                  |

| 639    | GE2/1 R&D T5: On-Chamber Prototype Electronics Manufacturing and Testing is Complete [At least One<br>Full Module]                                                                                      | Feb 19, 2019   | Feb 19, 2019  |                    |                    | GE                       | 2/1 R&D T5: On-Char     | mber Prototype Electr  | ronic 🔸                | Т                    | CR Re                  | view to                  | ,                      |                     |                  |

| 640    | GE2/1 R&D T4: Pre-Integration and GEB production Test-stand @ PKU Complete                                                                                                                              | Feb 20, 2019   | Feb 20, 2019  |                    |                    | G                        | E2/1 R&D T4: Pre-Inte   | egration and GEB prod  | uction T 🔷             |                      | Sinine                 |                          | -                      |                     |                  |

| 641    | GE21 R&D T4: ROB-2 Boards Testing @ CERN Completed                                                                                                                                                      | Mar 12, 2019   | Mar 12, 2019  |                    |                    |                          |                         | B-2 Boards Testing @   |                        | 201                  | arove                  | GE21-0                   | 03                     |                     |                  |

| 642    | GE2/1 R&D T4: Testing and Assessment of the modules for Stage-2A Demonstrator w/ APV electronics Complete                                                                                               | Mar 27, 2019   | Mar 27, 2019  |                    |                    |                          | GE2/1 R&D T4            | Testing and Assessm    | ent of the modul <     | ahł                  | JIOVE                  |                          | 03                     |                     |                  |

| 643    | GE2/1 R&D T4: Ready for Foil PRR (Modified due to GE21-002 Change Control)                                                                                                                              | May 3, 2019    | May 3, 2019   |                    |                    |                          | GE2                     | 2/1 R&D T4: Ready for  | Foil PRR (Modified due | a to 🧹               |                        |                          |                        |                     |                  |

| 644    | GE2/1 T5: PRR for Foil Production                                                                                                                                                                       | May 22, 2019   | May 22, 2019  |                    |                    |                          |                         | GE2/1                  | T5: PRR for Foil Prod  | duction 🔸 🔷          |                        |                          |                        |                     |                  |

| 645    | GE2/1 R&D T4: Testing and Assessment of Stage-2A Demonstrator (partial: GEB M1-2) w/ Gen-1 electronics<br>Complete                                                                                      | May 17, 2019   | May 17, 2019  |                    |                    |                          | G                       | E2/1 R&D T4: Testing a | and Assessment of Sta  | ige-2A 🔷             |                        |                          |                        |                     |                  |

| 646    | GE2/1 R&D T4: Ready for EDR                                                                                                                                                                             | May 17, 2019   | May 17, 2019  |                    |                    |                          |                         | GI                     | E2/1 R&D T4: Ready fo  | r EDR                |                        |                          |                        |                     |                  |

| 647    | GE2/1 R&D T5: Performance of the Demonstrator chamber with Prototype Electronics is Validated                                                                                                           | May 22, 2019   | May 22, 2019  |                    |                    |                          |                         | GE2/1 R&D T5: Perfo    | rmance of the Demon    | nstrator 🔷           |                        |                          |                        |                     |                  |

| 648    | GE2/1 E5: EDR (CMS TC - External Constraint)                                                                                                                                                            | May 22, 2019   | May 22, 2019  |                    |                    |                          |                         | GE2/1 E5: EDR (CM      | IS TC - External Con   | straint) 🔸 🔶         |                        |                          |                        |                     |                  |

| 649    | GE2/1 R&D T4: All Gen-1 On-Chamber Prototype Electronics Manufacturing and Testing is Complete. Ready for<br>full integration with the Stage-2A Demonstrator @ CERN.                                    | May 29, 2019   | May 29, 2019  |                    |                    |                          |                         | GE2/1 R&D T4: All Ge   | en-1 On-Chamber Prot   | totype Ele 🔷         |                        |                          |                        |                     |                  |

| 650    | GE2/1 R&D T4: Testing and Assessment of Stage-2A Demonstrator w/ Gen-1 electronics Complete                                                                                                             | Jun 18, 2019   | Jun 18, 2019  |                    |                    |                          |                         | GE2/1 R&D T4:          | Testing and Assessmer  | nt of Stage-2A 🔷     |                        |                          |                        |                     |                  |

| 651    | GE21 R&D T4: uTCA-based Backend System for Gen-2 GE21 electronics is Ready for Full Integration Testing<br>with Gen-2 on-Chamber Electronics                                                            | Aug 9, 2019    | Aug 9, 2019   |                    |                    |                          |                         | GE2                    | 21 R&D T4: uTCA-base   |                      | - <b>v</b>             |                          |                        |                     |                  |

| 652    | GE2/1 R&D E5: RISK MANAGEMENT DECISION POINT: LpGBT or GBTX-based readout selected for ESR                                                                                                              | Aug 30, 2019   | Aug 30, 2019  |                    |                    |                          |                         |                        | GE2/1 R&D E5: RISK     | MANAGEMENT DEC       | ISION PO 🔷             |                          |                        |                     |                  |

| 653    | GE21 R&D T4: Hardware/firmware ready for integrated testing of the packaged chips                                                                                                                       | Oct 1, 2019    | Oct 1, 2019   |                    |                    |                          |                         |                        | GE21 R&D T             | 4: Hardware/firmware | ready for integrate    | $\diamond$               |                        |                     |                  |

| 654    | GE21 R&D T4: Components of the ATCA-based Backend Readout System Hardware Test-Stand are Ready for<br>Integration                                                                                       | Nov 4, 2019    | Nov 4, 2019   |                    |                    |                          |                         |                        |                        |                      | ts of the ATCA-based I |                          |                        |                     |                  |

| 655    | GE21 R&D T4: Gen-2 Electronics Design Complete; Ready for Manufacturing                                                                                                                                 | Oct 31, 2019   | Oct 31, 2019  |                    |                    |                          |                         |                        |                        |                      | onics Design Complete  |                          |                        |                     |                  |

| 656    | GE2/1 R&D T4: Packaged Chips Bonding to PlugInCards-2 starts at a European vendor                                                                                                                       | Nov 28, 2019   | Nov 28, 2019  |                    |                    |                          |                         |                        |                        |                      | aged Chips Bonding to  |                          |                        |                     |                  |

| 657    | GE21 R&D T4: Packaged VFAT3 performance testing and packaging validation at INFN/Bari completed                                                                                                         | Dec 27, 2019   | Dec 27, 2019  |                    |                    |                          |                         |                        |                        | GE21 R&D T           | 4: Packaged VFAT3 pe   | rformance testing 🤇      | >                      |                     |                  |

| 658    | GE2/1 R&D T4: All Gen-2 Electronics Boards are Ready for Installation on Stage-2B Demonstrator and<br>mechanical integration studies @ CERN                                                             | Jan 31, 2020   | Jan 31, 2020  | Pr                 | adv fo             | or ESR (                 |                         | · Apr                  | 2 2020                 | GE2                  |                        | Electronics Boards are R | Ť                      |                     |                  |

| 659    | GE2/1 R&D T4: Testing and Assessment of Phase-2B Demonstrator w/ Gen-2 electronics Complete                                                                                                             | April 3, 2020  | April 3, 2020 | ne                 | auy It             |                          |                         | <i>.</i>               | 5 2020                 | ,                    |                        | T4: Testing and Assess   | ment of Phase 2B       | <u> </u>            |                  |

| 660    | GE2/1 R&D T5 (OPTION): Ready for ESR in GBTX-based scenario                                                                                                                                             | April 3, 2020  | April 3, 2020 | 11-                | date 4             | to lata                  | Marca                   | iven                   | ndates                 | J                    | GE2/1 R&D TS           | OPTION): Ready for I     | ESR in GBTX-           | $\diamond$          |                  |

| 661    | GE21 R&D T4: ATCA-based Backend System for Gen-2/3 GE21 electronics is Ready for Full Integration Testing<br>with Gen-3 on-Chamber Electronics                                                          | Mar 23, 2020   | Mar 23, 2020  | <u> U</u>          | Juale              | <u>to late</u>           |                         |                        | pualed                 | <u>1</u>             |                        | ATCA-based Backend       | · · · · ·              |                     |                  |

| 662    | GE21 R&D T4: All Gen-3 Electronics Components Designs Complete                                                                                                                                          | Mar 27, 2020   | Mar 27, 2020  |                    |                    | GFR                      | sched                   | ule                    |                        |                      | GE21 R&D T             | 4: All Gen-3 Electronics |                        |                     |                  |

| 663    | GE21 R&D T4: GEB-3 Boards Arrive to CERN                                                                                                                                                                | Jun 19, 2020   | Jun 19, 2020  |                    |                    | GLD                      | Jeneu                   |                        |                        |                      |                        |                          | R&D T4: GEB-3 Board    | · ·                 |                  |

| 664    | GE21 R&D T4: Development of the Software and Firmware infrastructure with fully integrated backend Complete                                                                                             | Jun 26, 2020   | Jun 26, 2020  |                    |                    |                          |                         |                        |                        |                      |                        | GE21 R&D T4:             | Development of the S   | oftware and Firm <  |                  |

| 665    | GE2/1 R&D T4: All Gen-3 Electronics Boards are Ready for Installation and mechanical integration studies @<br>CERN                                                                                      | July 17, 2020  | July 17, 2020 |                    | Pood               | ly for E                 |                         | CDT)                   | Ohcolo                 | to no                |                        |                          | &D T4: All Gen-3 Elect |                     | Ť                |

| 666    | GE2/1 R&D T4: Testing and Assessment of Stage-3 Demonstrator w/ Gen-3 electronics Complete. Ready for ESR                                                                                               | -              | Aug 21, 2020  |                    | red0               | ly for E                 | sk (rb                  | GDIJ                   | Obsole                 |                      | VV                     |                          | E2/1 R&D T4: Testing   | and Assessment of S | tage-3 D 🔶       |

| 667    | GE2/1 R&D T5: On- and Off-Chamber Readout Prototype Electronics Integration and Performance Studies<br>Completed                                                                                        |                | Aug 21, 2020  |                    |                    |                          |                         |                        |                        |                      |                        | GE                       | 2/1 R&D T5: On- and    |                     | , i i            |

| 668    | GE2/1 E5: ESR (CMS TC - External Constraint)                                                                                                                                                            | Aug 21, 2020   | Aug 21, 2020  |                    |                    |                          |                         |                        |                        |                      |                        |                          | GE2/1 E5: ESR (C       | MS TC - External Co | nstraint) 🔸 🔿    |

| Δ      | lexei N. Safonov                                                                                                                                                                                        |                | (             |                    | GF2/               | 1 TCR                    |                         |                        | CFR                    | RN AII               | g 30                   | 2019                     | n 26                   | 5                   |                  |

Alexei N. Safonov

CMS GE2/1 TCR

### **Risk Management Program**

- Pro-active risk management program carried throughout the R&D stage will continue into the construction phase

- Continuously updating risk register, reviewing and analyzing potential new threats, developing mitigation and response strategies

- Detectors: risks significantly reduced relative to the original version of the risk register

|                    |                      |                    |         |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       | 1                        |                            |                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                  |

|--------------------|----------------------|--------------------|---------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CORE CBS<br>Number | Merlin WBS<br>Number | Activity           | Risk ID | Risk Description                                              | Impact Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Likelihood<br>(L/M/H) | CORE cost impact (L/M/H) | Schedule Impact<br>(L/M/H) | Mitigation                                                                                                                                                                                                        | Action                                                                                                                                                                                                                                                                                                                           |

| 2521               | 2521                 | GE2/1<br>Detectors | 4.1     | external vendors or delays in manufacturing                   | If quality of GEM foils is inadequate, foils will need to be re-<br>mate leading to delays in the schedule and potentially lead<br>to cost increases. If the impact on schedule is severe<br>enough, it can impact readiness of the detector for<br>installation                                                                                                                                                                                                                                                                                                                                                                     |                       | L                        | м                          | process of all ariving foils so any problems are discovered<br>immediately to reduce schedule impact, (iii) schedule monitoring, (iv)<br>adequate floats in the schedule to allow absorbing potential delays, (v) | Work with the vendors to correct the problem and speed up the foil<br>manufacturing schedule, identify additional marpower to increase the<br>number of shifts at module production sites and the chamber assembly<br>facility at CERN to increase the throughput so that delays compared to<br>original schedule are minimized. |