# 24<sup>th</sup> GEM Workshop

# VFAT3b package

Francesco Licciulli INFN Sezione di Bari

**Why packing?** The package will improve the plugin card production yield thanks to an easier design, less constrains for the board production and the replacement of the VFAT3 bonding phase with a much more reliable soldering procedure.

Some problems encountered during hybrid production\*:

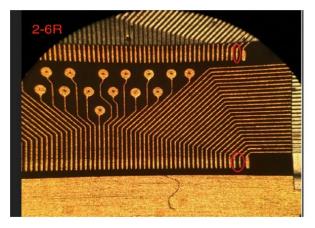

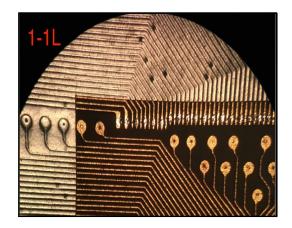

Pad catering

Over-etching on the channel pads: pads width about 37  $\mu$ m < IPC standard for wire bonding 48  $\mu$ m.

VFAT3 bondend on the hybrid

Breakage on the PCB surface/tracks and scratches of the landing pads/vias.

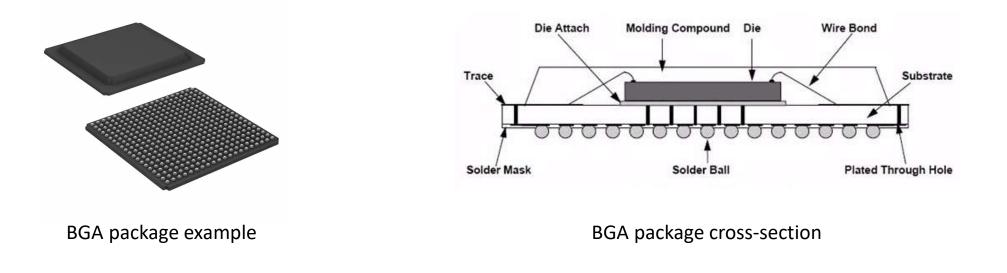

VFAT3 will be packaged in a full Ball Grid Array (BGA) package.

- The substrate is a small PCB, realized by means of advanced techniques, that hosts the die and provides the connections between the bonding wires and the solder balls.

- Solder balls are used for the electrical connection with an external PCB, mechanical support and heat transfer.

- Molding compound, plastic in this case or a metal coverage in others, protect the die and the wire bonding.

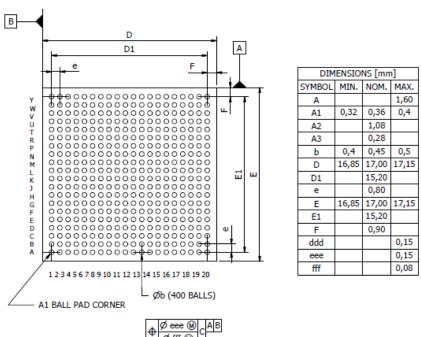

# **INFN** Package specifications

## Package specifications:

- Ball grid array: 20 x 20

- Size: 17 x 17 mm<sup>2</sup>

- Ball pitch: 0.8 mm

- Plastic encapsulation

- Ball bonding

- Ball solder composition: SAC 305 (96.5% Sn, 3% Ag, 0.5% Cu)

- 7 SMD passive components inside the package:

- 4 capacitors for power supply decoupling,

- 2 capacitors for reference decoupling (ADCs),

- 1 resistor for current monitoring.

PACKAGE OUTLINE LFBGA 17x17 400 R20x20 PITCH 0,8 BALL 0,45

|    |                |                |                 |              |                |                 |                 |                 |                 |              |               |               | 10                 |                      | ar a           |             |                |                  |                |                  |            |

|----|----------------|----------------|-----------------|--------------|----------------|-----------------|-----------------|-----------------|-----------------|--------------|---------------|---------------|--------------------|----------------------|----------------|-------------|----------------|------------------|----------------|------------------|------------|

|    | 1              | 2              | 3               | 4            | 5              | 6               | 7               | 8               | 9               | 10           | 11            | 12            | 13                 | 14                   | 15             | 16          | 17             | 18               | 19             | 20               |            |

|    | IN_128         | IN_127         | GND_FE          | IN_126       | IN_125         | GND_FE          | IN_124          | IN_123          | GND_FE          | DiffBuffOutp | DiffBuffOuts  | CFDInn        | CFDInp<br>OFD. OUT | SCAH_INO_C           | SCAN_ENO_C     | SCAN_OUTO_C | SCAN_IN1_A     | SCAM_OUT1_C      | HDLC_ADDRESS_0 | HDLC_ADDRESS_3   |            |

|    | IN_122         | GND_FE         | IN_121          | IN_120       | GND_FE         | IN_119          | IN_118          | GND_FE          | IN_117          | thaff_ibiar  | Shaporin      | DiffBuffla    | CFD_OUT            | SCAN_ENO_A           | SCAN_OUTO_A    | SCAN_IN1_C  | SCAN_EN1_C     | SCAM_OUT1_B      | HDLC_ADDRESS_1 | HDLC_ADDRESS_4   | В          |

|    | GND_FE         | IN_116         | IN_115          | GND_FE       | IN_114         | IN_113          | GND_FE          | IN_112          | IN_111          | ProAmpOut    | ShaperOut     | SCAN_INO_A    | SCAN_INO_B         | SCAN_ENO_B           | SCAN_OUTO_B    | SCAN_IN1_B  | SCAN_EN1_B     | SCAH_OUT1_A      | HDLC_ADDRESS_2 | HDLC_ADDRESS_5   | C          |

|    | IN_110         | IN_109         | GND_FE          | IN_108       | IN_107         | GND_FE          | IN_106          | IN_105          | GND_FE          | YDD_FE       | YDD_FE        | AVDD_CFD      | AVDD_CFD           | DYDD_CFD             | DYDD_CFD       | YDD         | SCAN_EN1_A     | BIST_OK          | HDLC_ADDRESS_7 | HDLC_ADDRESS_6   |            |

|    | IN_104         | GND_FE         | IN_103          | IN_102       | GND_FE         | IN_101          | IN_100          | GND_FE          | IN_99           | YDD_FE       | GND_FE        | GND_CFD       | GND_CFD            | DYSS_CFD             | DV\$\$_CFD     | YDD         | BIST_END       | TP_IH_SI         | TP_IM_SE       | BIST_START       | F          |

|    | GND_FE         | IN_98          | IN_97           | GND_FE       | IN_96          | IN_95           | GND_FE          | IN_94           | IN_93           | YDD_FE       | GND_FE        | GND_CFD       | GND_CFD            | D¥SS_CFD             | DV\$\$_CFD     | YDD         | SPI_EN         | SPL_D0           | VSS            | ¥SS              |            |

| -  | IN_92          | IN_91          | GND_FE          | IN_90        | IN_89          | GND_FE          | IN_88           | IN_87           | GND_FE          | YDD_PROT     | GND_FE        | GND_FE        | GND_FE             | ¥\$\$                | YDD_IO         | YDD         | SPI_CLK        | SPI_DI           | VSS            | TU_S=T_p         | G          |

|    | IN_86          | IN_85          | GND_FE          | IN_84        | IN_83          | IN_82           | GND_FE          | IN_81           | IN_80           | GND_FE       | GND_FE        | GND_FE        | GND_FE             | 884                  | YDD_IO         | YDD         | SCAN_CLKO_EN   | VSS              | ¥SS            | TU_S=T_N         |            |

|    | IN_79          | IN_78          | GND_FE          | IN_77        | IN_76          | IN_75           | GND_FE          | IN_74           | IN_73           | GND_FE       | GND_FE        | GND_FE        | GND_FE             | ¥88                  | YDD_IO         | YDD         | SCAN_CLK       | VSS              | TU_TED_P_0     | ¥\$\$            | J          |

|    |                | IN_71          | IN_70           | IN_69        | GND_FE         | IN_68           | IN_67           | IN_66           | IN_65           | GND_FE       | GND_FE        | GND_FE        | GND_FE             | VSS                  | YDD_IO         | YDD         | PDD_EFUSE      | VSS              | TU_TED_s_0     | ¥\$\$            | <u> </u>   |

|    | IN_64          | IN_63          | GND_FE          | IN_62        | IN_61          | IN_60           | GND_FE          | IN_59           | IN_58           | GND_FE       | GND_FE        | GND_FE        | GND_FE             | ¥\$\$                | YDD_IO         | YDD         | VDD_SLVS       | VSS              | VSS            | TU_TED_P_1       | M          |

|    |                | IN_56          | GND_FE          | IN_55        | IN_54          | IN_53           | GND_FE          | IN_52           | IN_51           | GND_FE       | GND_FE        | GND_FE        | GND_FE             | ¥88                  | YDD_IO         | YDD         | PDD_SLPS       | ¥\$\$            | ¥88            | TU_TED_s_1       | N          |

|    |                | IN_49<br>IN_40 | IN_48           | IN_47        | IN_46          | IN_45           | IN_44           | IN_43           | IN_42           | YDD_PROT     | GND_FE        | GND_FE        | GND_FE             | VSS                  | YDD_IO         | YDD         | ¥\$\$<br>¥\$\$ | VSS              | TU_TED_P_2     | ¥\$\$<br>¥\$\$   | P          |

|    |                | IN_35          | GND_FE<br>IN_34 | IN_39        | IN_38<br>IN_33 | GND_FE          | IN_37<br>GND_FE | IN_36           | GND_FE<br>IN_30 | YDD_FE       | GND_FE        | GND_CFD       | GND_CFD            | DVSS_CFD<br>DVSS_CFD | DV\$\$_CFD     | YDD         |                | ¥\$\$            | TU_TED_s_2     |                  | B          |

|    | GND_FE         | GND_FE         | IN_28           | GND_FE       | GND_FE         | IN_32           | _               | IN_31<br>GND_FE |                 | YDD_FE       | GND_FE        | GND_CFD       | GND_CFD            |                      | DVSS_CFD       | YDD         | ¥\$\$<br>¥\$\$ | TU_TED_P_6       | ¥85<br>¥85     | TU_TED_P_3       |            |

|    | IN_29<br>IN_23 | IN_22          | GND_FE          | IN_21        |                | IN_26<br>GND_FE | IN_25<br>IN_19  | _               | IN_24           | YDD_FE       | YDD_FE        | AYDD_CFD      | AYDD_CFD           | DYDD_CFD             | DYDD_CFD       |             |                | TU_TED_s_6       | 755            | TU_TED_s_3       | U          |

|    | GND_FE         | IN_17          | IN_16           | GND_FE       | IN_20<br>IN_15 | IN_14           | GND_FE          | IN_18<br>IN_13  | GND_FE          | oxtAC_puiro  | Y_BGR         | Int_Frof_ADC0 | RST_TEST_MODE      | ¥88                  | RECLK_P        | ¥88<br>¥88  | TED_P          | ¥\$\$<br>¥\$\$   | TU_TED_P_5     | ¥\$\$<br>¥\$\$   | v          |

| ЦĘ |                | GND_FE         | _               |              |                | _               | GND_FC          | GND_FE          | IN_12<br>IN_6   | Iman         | ¶_Trens_ext   | Ext_Fref_ADC1 | BOR_DISABLE        | ¥88                  | RICLK_s        |             | TED_s          | 492              | TU_TED_&_5     |                  | ÷          |

|    |                | IN_4           | IN_10<br>GND_FE | IN_9<br>IN_3 | GND_FE         | IN_8<br>GND_FE  | _               | IN_0            | GND_FE          | En_ozt_lrof  | YDD_TSENS_INT | POR_DISABLE   | TP_MOH_CLK         | ¥\$\$<br>¥\$\$       | ¥\$\$<br>¥\$\$ | RID_P       | ¥\$\$<br>¥\$\$ | TU_TED_P_7       | ¥\$\$<br>¥\$\$ | TU_TED_P_4       | ÷          |

| -  | (m_)           | - IM_4         | GNU_FC          | IN_3         | 1m_2<br>5      | GNU_FC          | IN_1            | 1M_U<br>8       | GND_FE<br>9     | Ext_Iref     | 7mm<br>11     | EXT_RESET     | TP_MON_CLK_EN      | 435                  | 15             | RID_s<br>16 | ¥35<br>17      | TU_TID_s_7<br>18 | 19             | TU_TED_s_4<br>20 | <u>–</u> – |

|    |                | 2              | 3               | •            | ,              | 0               |                 | 0               | 3               | 10           |               | 12            | 13                 | 14                   | G              | 10          |                | 10               | 13             | 20               |            |

|    |                |                |                 |              |                |                 |                 |                 |                 |              |               |               |                    |                      |                |             |                |                  |                |                  |            |

|    |                |                |                 |              |                |                 |                 |                 |                 |              |               |               |                    |                      |                |             |                |                  |                |                  |            |

### **Analog Inputs**

## **Power Supply & Digital**

The proposed signal assignment has been maintained in the substrate design!

F. Licciulli - INFN Sezione di Bari

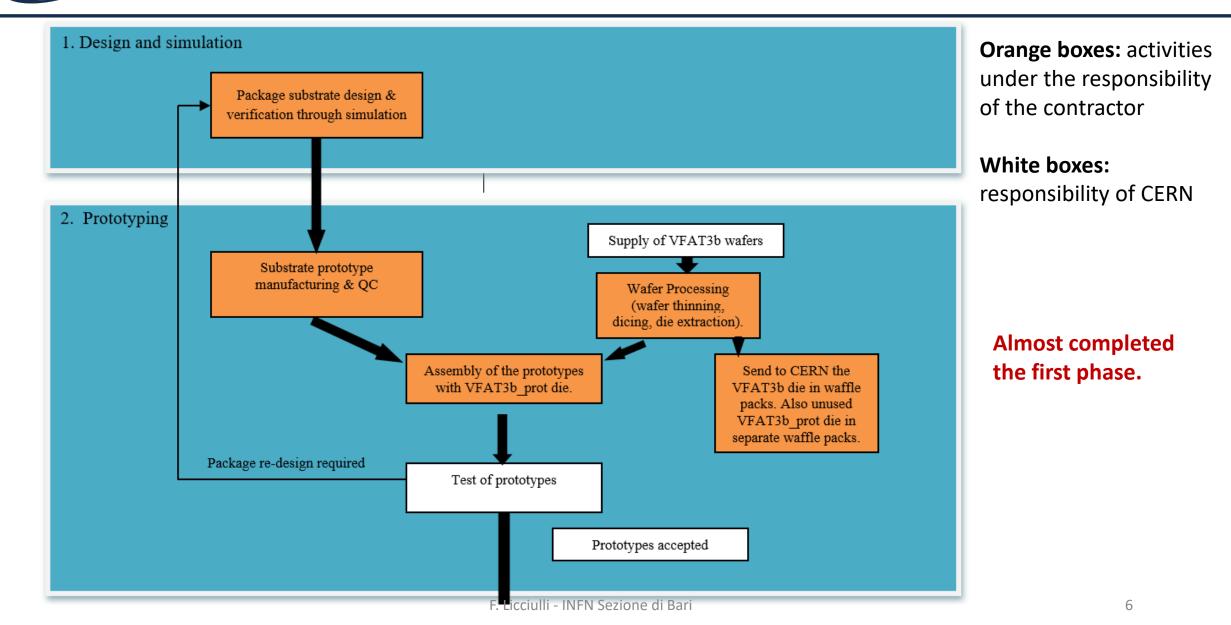

# **INFN** Flowchart of VFAT3b package production 1/2

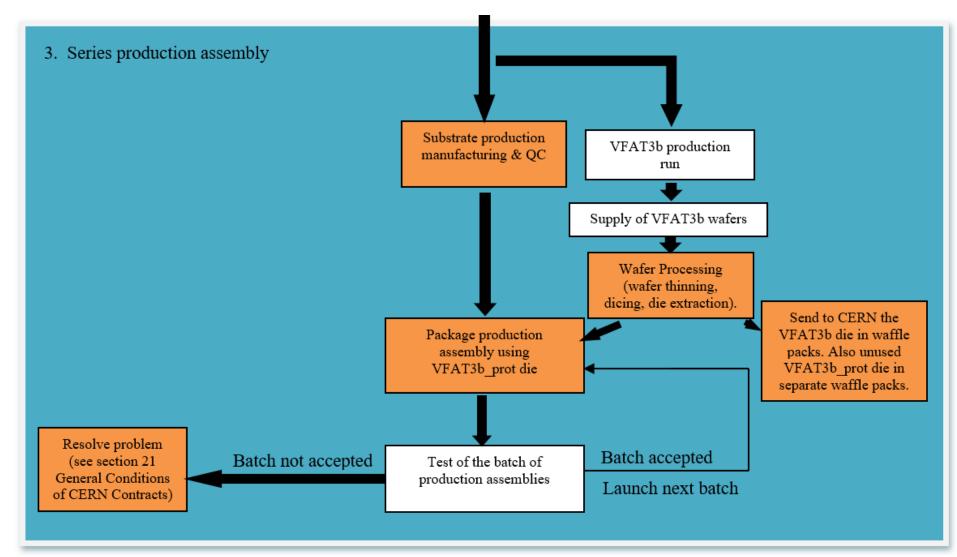

# **INFN** Flowchart of VFAT3b package production 2/2

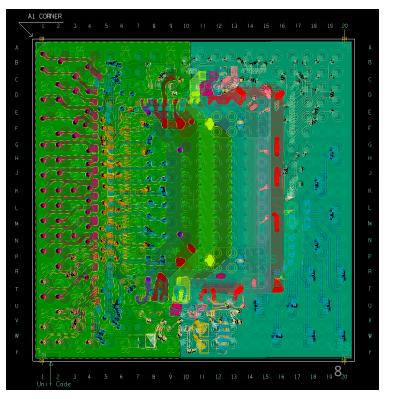

# **INFN** Package Design: 1<sup>st</sup> phase

First phase: substrate design completed.

Waiting for:

- RLC parasitic package extraction,

- Characteristic impedance simulation for differential lines,

- Crosstalk simulations,

- Package thermal behaviour simulations.

Once all the simulation results will be collected, the substrate design review will be called.

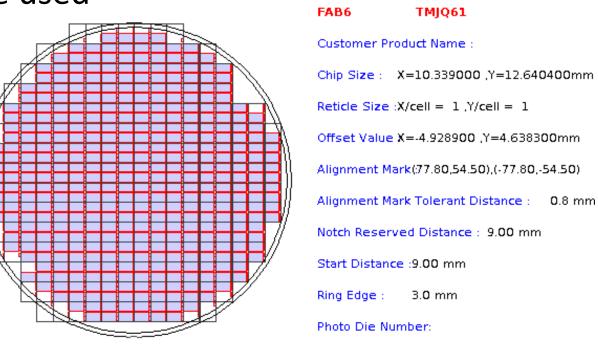

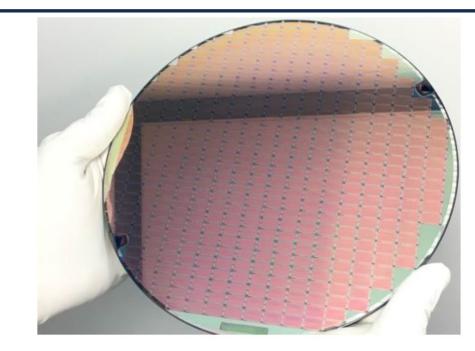

# Prototyping: 2<sup>nd</sup> phase INFŃ

- VFAT3 package prototypes: 200 pieces

- At CERN were available 4 wafers from GE1/1

- Each wafer has 205 VFAT3b prot dice

- Prototyping: one wafer of GE1/1 can be used

# One wafer was sent to IMEC: received on 19<sup>th</sup> September 2019

VFAT3B : 201 VFAT3B PROT : 205

#### F. Licciulli - INFN Sezione di Bari

SM TID : 863

TMJQ61

3.0 mm

## VFAT3 package series production:

- 5000 VFAT3 for GE2/1

- 7000 VFAT3 for ME0

## VFAT3 wafer production:

- Wafers are produced in lots of 25,

- The minimum order quantity for production is one lot,

- Orders are placed in terms of lots,

- The cost of one VFAT3b production lot is approximately 42 kUSD,

- Delivery time is about 3 months.

For the full series production 75 wafers are needed! We will get:

- 15375 VFAT3b\_prot

- 15075 VFAT3b.

| Step   | Description                                                                                                                                   | Quantity | Unit Price FCA                     | Total price |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------------------|-------------|--|--|

| 1      | Design files and analysis                                                                                                                     | 1        | 7,400 (design)                     |             |  |  |

|        | reports (substrate design,                                                                                                                    |          | 2,500 (Elect Sim)                  | 13,900      |  |  |

|        | electrical simulation,<br>thermal simulation)                                                                                                 |          | 4,000 (Therm Sim)                  |             |  |  |

| 2      | Prototype chip assemblies                                                                                                                     | 1        | 7,800 (tooling)                    |             |  |  |

|        | including wafer processing<br>(including substrate tooling,<br>manual ball mount kit,<br>grinding, setup and<br>substrates prototype series ) | 1        | 5,000 (BMK)                        | 15,794      |  |  |

|        |                                                                                                                                               | 1        | 2,650 (Setup)                      |             |  |  |

|        |                                                                                                                                               | 200      | 1.72 (unit package                 |             |  |  |

|        |                                                                                                                                               |          | incl substr)                       |             |  |  |

| 3      | Series production chip<br>assemblies including wafer<br>processing – batch 1                                                                  | 5 000    | Including charges                  |             |  |  |

|        |                                                                                                                                               |          | to avoid high MoQ                  | 25,394      |  |  |

|        |                                                                                                                                               |          | ( design and tool                  |             |  |  |

|        | (Including substrates for 5K                                                                                                                  |          | charges)                           |             |  |  |

|        | pcs - Copper wiring – see<br>"13" below)                                                                                                      |          | 1.72 (unit package<br>incl substr) |             |  |  |

| 4      | Series production chip                                                                                                                        | 7 000    | Including charges                  |             |  |  |

|        | assemblies including wafer                                                                                                                    |          | to avoid high MoQ                  | 28,831      |  |  |

|        | processing – batch 2                                                                                                                          |          | ( design and tool                  |             |  |  |

|        | (including substrates for 7K                                                                                                                  |          | charges)                           |             |  |  |

|        | pcs - Copper wiring – see<br>"13" below)                                                                                                      |          | 1.72 (unit package                 |             |  |  |

|        |                                                                                                                                               |          | incl substr)                       |             |  |  |

| TOTAL  | 83,919                                                                                                                                        |          |                                    |             |  |  |

| COST O |                                                                                                                                               |          |                                    |             |  |  |

| TRANSI | 450                                                                                                                                           |          |                                    |             |  |  |

| TOTAL  |                                                                                                                                               |          |                                    |             |  |  |

|        |                                                                                                                                               |          |                                    | 84,369      |  |  |

- The cost of the two series production is almost equal to the design and prototyping due to the high flexibility required by CERN (stop the production in any moment).

- The manufacturer asks for a series production at least of 20k pieces, only the prototyping can be lower.

- Step 3 and step 4 are like new design and prototyping phases.

| Deliverable/milestone                                   | Relative timescale       | Estimated/actual date |

|---------------------------------------------------------|--------------------------|-----------------------|

| Placement of the order by CERN                          | Τ <sub>ο</sub>           | Half July 2019        |

| Design files and associated reports                     | T <sub>1</sub>           | October 2019          |

| Approval by CERN of the substrate design                | T <sub>2</sub>           | October 2019          |

| Delivery of the prototypes                              | T <sub>2</sub> + 8 weeks | December 2019         |

| Approval by CERN of the prototypes                      | T <sub>3</sub>           | June 2020             |

| Approval by CERN to start work on the series production | T <sub>4</sub>           | June 2020             |

| Delivery of the series production (first batch)         | T <sub>4</sub> + 4 weeks | July 2020             |

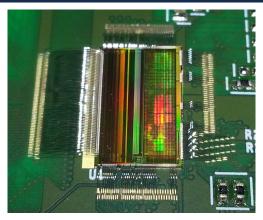

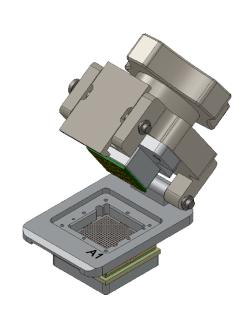

# The test will be done in Bari:

- ✓ Clam shell sockets ordered and arrived,

- ✓ PCB design completed and produced,

- ➢ PCBs will be mounted next week,

- Firmware old code from VFAT3 characterization can be used,

- Software to be done (3 weeks, we need the chip for finalization).

# 5 test systems will be realized in order to speed up the test of the series production.

# **INFN** VFAT3 package test list

## Analogue tests:

- Power supply current absorption for shorts

- VFAT3 internal references, DAC scan, ADCs

- Temperature sensors: internal and external (bias current)

- Channel gains, linearity ranges, noise

- Local channel DACs characterization

## **Digital tests:**

- Differential and common mode measurement of the TX SLVS

- Built in self test (BIST)

- Scan path

# Bonding of the input channels by means of external injection.