#### Quiz?

What is the item produced in the largest number today?

#### Topics

- Refresher: what is a MOS transistor and how does it work?

- Past predictions

- How good are we at "forecasting (imagining?) the future"?

- Revisit the major innovations that allowed VLSI scaling to go-on for 50+ years

- Sub 10 nm devices are now on the market

- ... and few atomic layers are left

- are we approaching the end of the road?

- Possible innovations allowing growth for another generation

- (Several) new devices current research

- Innovative circuit from

- What use to make of sub-10nm transistors in HEP

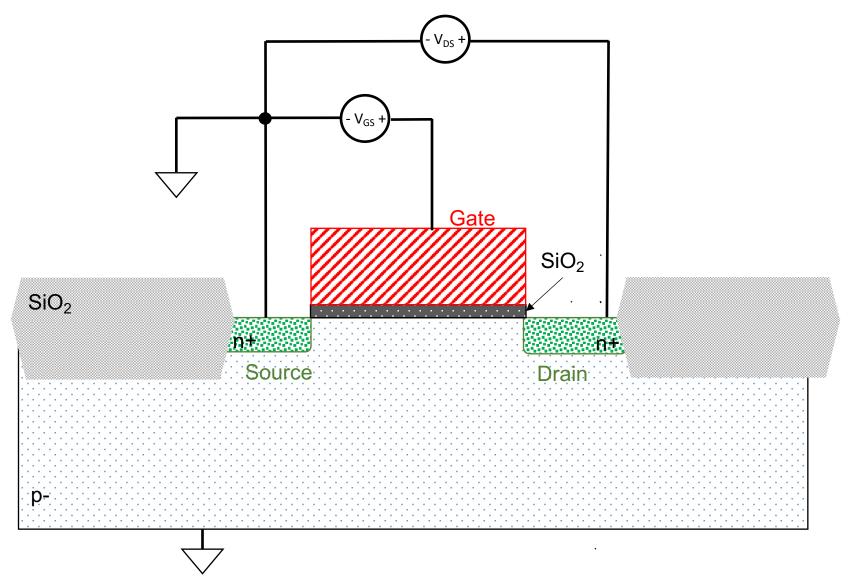

#### **MOS Transistor**

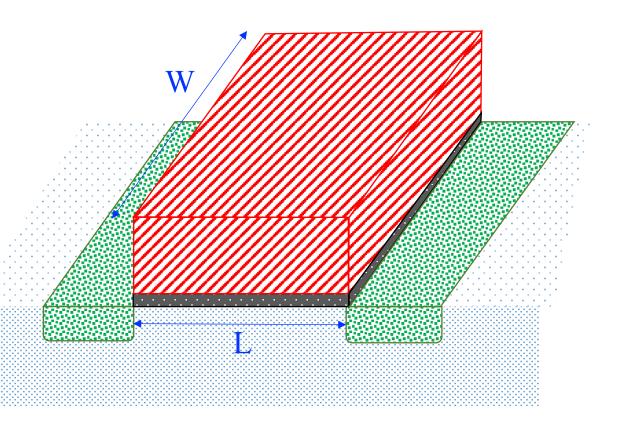

#### MOS Transistor Nomenclature

L is the defining parameter of a given CMOS technology.

Called the channel length, it is (actually was ...) the smallest dimension that could be fabricated in an integrated circuit.

L is the distance that charge carriers have to traverse to bring current between the two terminals of a transistor.

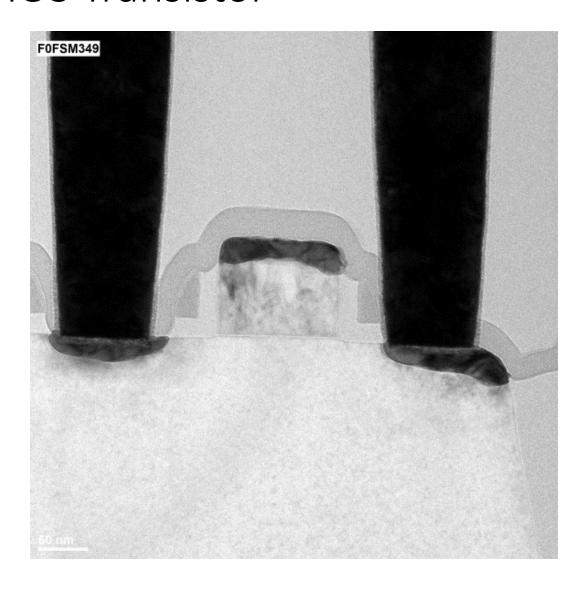

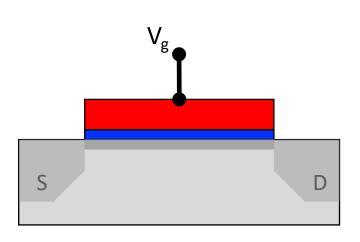

#### Real NMOS Transistor

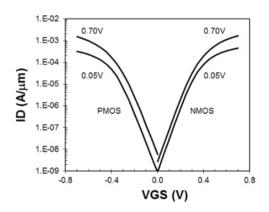

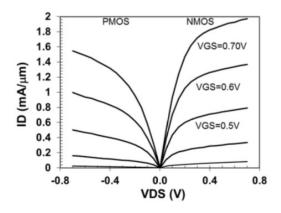

#### What do we want from a transistor anyway? (sorry analog engineers...)

- A transistor (a digital transistor) is a device that "should" have the following characteristics:

- works as a switch (on or off)

- three terminals: an input, an output, a control

- makes a "sharp" transition between the two states (open or closed) in a time as short as possible (i.e. carry charge quickly through it)

- no leakage current when off  $(I_{on}/I_{off} > [>] 10^6)$

- ... while delivering high current when on (drive strongly the load), I<sub>on.min</sub> ~ 1mA/um

- control terminal induces a transition between the two states with a voltage drive  $(V_{tr})$  as small as possible:  $P = \frac{1}{2} C V_{dd}^2$  (today  $V_{tr} \sim \frac{1}{2} V_{dd}$ )

- control terminal should not be influenced by input/output terminal(s)

- be physically small (otherwise other "parasitics" ruin the party)

- must have complementary type (i.e. a second type which is turned on when the first is turned off using the same "control").

- "Good analog" characteristics are desirable but by far not necessary or even important for the the majority of applications.

In fact modern deep-submicron devices have "horrible" analog characteristics and analog designers have a hard time to achieve what was "easy" 20 years ago

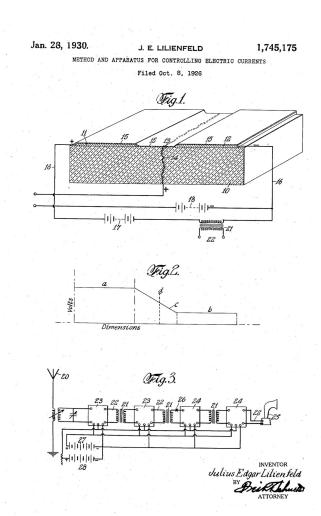

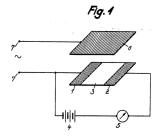

# Lilienfeld (1926)

## O. Heil (1935)

8194

Oskar Heil.

408194

Printer Eur PARETTE

MINISTÈRE

des

AFFAIRES ÉCONOMIQUES

Direction Générale de l'Industrie

SERVICE DE LA PROPRIÉTÉ INDUSTRIELLE

N. 408194.

ROYAUME DE BELGIQUE

#### BREVET D'INVENTION

Le Ministre des Affaires Économiques,

Vu la loi du 24 mai 1854;

Vu la convention d'union pour la protection de la propriété industrielle;

Vu le procès-verbal dressé le 4º mars 1925, à 41 h 55'

au Greffe du Gouvernement provincial du Brabant;

| ARRÊTE :                                                                                   |

|--------------------------------------------------------------------------------------------|

| Article 1 st Il est délivré à Mo. O. Heil                                                  |

| 31, Jaganstrasso, à Berlin Orynewold.                                                      |

| II, Jagonstrasse, à Berlin grunewold,<br>reps. pas l'Office & Parette, à Buxelles,         |

|                                                                                            |

| rrevet d'invention pour : Séllacde de commande S d'amplificale<br>de courants électriques. |

| de courante électriques.                                                                   |

| ,                                                                                          |

|                                                                                            |

|                                                                                            |

fatient l'objet d'une première demande de brevet qu'él. D. déclaré avoir déposée 29 Allemagne, l. 1. mars 4918

Article 2. — Ce brevel lui est délivré sans examen préalable, à ses risques et périls, sans garantie soit de la réalite, de la nouveauté ou du mérite de l'invention, soit de l'exactitude de la description, et sans préjudice du droit des tiers.

Au présent arrêlé demeurera joint un des doubles de la spécification de l'invertion (mémrire descriptif et éventuellement dessins) signés par l'intéressé et déposés à l'appui de sa demande de bretet.

Bruxelles, le 10 avril 1955.

Pour le Ministre et par délégation : Le Directeur, Chef de Service :

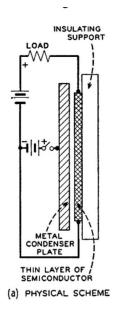

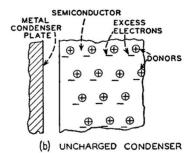

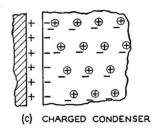

### W. Shockley (1950)

Experiments have been carried out with layers of various semiconductors, and effects of the sort discussed have been observed. However, the degree of modulation has been somewhat less than that calculated above. For layers of germanium about 5000A thick, in which the mobility was only about 40 cm<sup>2</sup>/volt sec, it was apparent upon analysis of the data that only about 10 per cent of the induced charges (holes in this instance since the evaporated germanium was p-type) were effective in changing the conductance.<sup>4</sup> This reduced effectiveness can be accounted for on the basis of a theory dealing with the behavior of the current carriers at a semi-conductor surface.

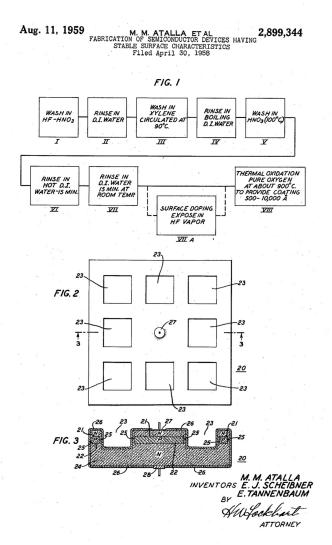

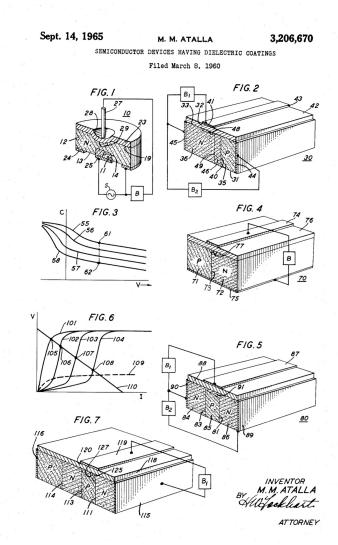

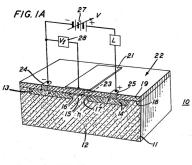

## Atalla (1959 & 1965)

# Kahng (1963)

Aug. 27, 1963

DAWON KAHNG

3,102,230

ELECTRIC FIELD CONTROLLED SEMICONDUCTOR DEVICE

Filed May 31, 1960

INVENTOR D. KAHNG HULFalchart

ATTORNEY

## Vanlass, Sah (1963) MOS -> CMOS

WEDNESDAY, FEBRUARY 20, 1963 ... UNIVERSITY OF PENNSYLVANIA—IRVINE AUDITORIUM ... 2:50-5:30 P.M.

#### SESSION III: Logic I

WPM 3.5: Nanowatt Logic Using Field-Effect Metal-Oxide Semiconductor Triodes

F. M. Wanlass and C. T. Sai

Fairchild Semiconductor Div., Fairchild Camera-Instrument Corporation

Palo Alto Calif

COMPLEMENTARY N AND P-type field-effect metal-oxide-semiconductor-triodes have been fabriented from silicon-by a planar diffusion process. These devices have gate input resistances of ~ 10° o.hms and input capacitances of < 10° pf. The cross sections of both types of these triodes, which will be referred to as N and P elements. are shown in Figure 1. If a N element is biased with a positive drain source voltage, as shown in Figure 2a, and if its gate is tied to its source, then drain source current  $I_{DS}$  will be of the order of that flowing in a reverse-biased silicon diode. But  $I_{DS}$  can be increased consider-Typically, la, can be switched from  $c_1$  to start out in the start of the Typically, la, can be switched from  $c_1$  ( $\theta^a$  to > 10 ma by a change of 20 v in  $V_{cs}$ . The P element is described the same way as the N element except that all voltages need to be reversed. Thus, if a P element is connected as in Figure 2D,  $I_{cs}$  can become very large if the gate is biased negative, with respect to the source. Figure 3 shows characteristic  $I_{DS}$  versus  $V_{SD}$  curves for both types of field-effect triodes when connected as in Figure 2.

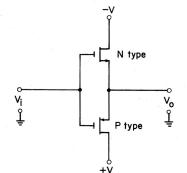

Consider the inverter circuit of Figure 4 as an example of low power logic that uses only N and P elements without the need for resistors or any other components Here the N element, acting as an active load for the P element, is turned on when the P element is off, and off when the P element is on. This combination will only dissipate appreciable power during switching. The leakage current is so low for a field-effect triode in the off-state that  $10^7$  circuits, like that of Figure 4, would use less than one watt of standby power.

Even though the standby power of the inverter of

Figure 4 is extremely low, it can still switch very fast In an effort to measure the signal propagation delay of the inverter, the three-stage ring oscillator of Figure 5 was set up. A plot of the output of one of the stages is in Figure 6; it will be seen that the propagation delay is less than 100 nsec. Part of the observed delay is due to oscilloscope input capacitance across the output.

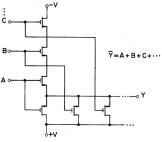

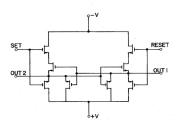

Other useful logic circuits using only complementary N and P elements can be readily designed. For example, Figure 7 shows a NOR circuit and Figure 8 a set-reset flip-flop. In these circuits appreciable energy is dissipated only at a rate proportional to the information processing

The output of a logic circuit composed of comple-mentary field-effect triodes can fan out to a large number of other inputs by direct coupling; the only consideration in limiting the number is switching speed, It should be possible to drive approximately 50 inputs from one output and have less than a I usec signal propagation delay.

delay.

Since these field-effect triodes are switched in the voltage mode and no resistor tolerances enter in the dc switching considerations, high temperature differentials between different parts of N and P element circuitry can be tolerated well. This means that a volume of N and Pof contracted well. In speaks that a volume of A and Y and William and the speaks that a volume of A and Y and William and amount of heat exhauster and the speaks that the speaks the speaks the speaks that the speaks that the speaks the speaks that the s

32 • 1963 International Solid-State Circuits Conference

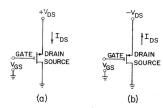

FIGURE 1-Cross sections of metal-oxide-semiconductor-triodes: (a) the N type element; (b) the Ptype element.

FIGURE 2-Suggested field-effect triode symbols and proper bias voltage polarities: (a) for N type element:

WEDNESDAY, FEBRUARY 20, 1963... UNIVERSITY OF PENNSYLVANIA—IRVINE AUDITORIUM... 2:50-5:30 P.M. [WPM 3.5]

FIGURE 3-Characteristic curves for the field-effect triodes where drain current is plotted against drain voltage for source grounded and for different values of gate bias. The N element curves are plotted in the first quadrant.

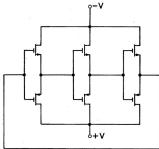

FIGURE 5-Ring-oscillator circuit for determining propagation delay of complementary inverter circuit

FIGURE 6-Plot of output voltage waveform from one stage of ring oscillator circuit.

FIGURE 7-NOR logic circuit. If any of the inputs are + V then the output will be - V.

FIGURE 8-Set-reset flip-flop. A positive pulse on the set input will put output I at +V and output 2 at - V; a positive pulse on the reset input will reverse the output voltages.

DIGEST OF TECHNICAL PAPERS . 33

# Si and SiO<sub>2</sub> – The chicken and the egg

An ideal interface is one where all of the atomic bonds are satisfied through couplings between the two layers. The successful MOSFET is very sensitive to the degree of interface perfection. Silicon dioxide on silicon is the combination of materials that comes closest to this ideal, with only one electrically active imperfection (defect) for every 100000 surface atoms. This is truly remarkable when one realizes that the two materials are so different, the oxide being an amorphous insulator and the silicon a high quality, single crystal, semiconductor. Hans Quiesser, in his exciting book, Conquest of the Microchip [14], describes the early difficulties of surface passivation and writes: "what finally saved the day was that an incredibly stable oxide of silicon can be wrapped around the crystal to protect it." Another historical account, The History of Engineering & Science in the Bell System [15], describes "surface state problems were resolved by an unexpected discovery .... Kahng and Atalla found that silicon and clean, thermally grown SiO<sub>2</sub> interfaces contain sufficiently small surface states to realize a true field effect transistor in silicon." The

### Self-Aligned Gates

Solid-State Electronics Pergamon Press 1968. Vol. 11, pp. 653-660. Printed in Great Britain

#### METAL-NITRIDE-OXIDE-SILICON FIELD-EFFECT TRANSISTORS, WITH SELF-ALIGNED GATES\*

J. C. SARACE,† R. E. KERWIN, D. L. KLEIN; and R. EDWARDS

Bell Telephone Laboratories, Inc., Murray Hill, New Jersey, U.S.A.

(Received 2 January 1968; in revised form 16 February 1968)

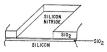

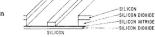

Abstract—Silicon insulated-gate field-effect transistors (FETs) have been fabricated by processes involving relatively non-critical photoresist and self-limiting etching steps. Important features of the method include the formation of the gate insulator under extremely clean conditions, incorporation of an alkali ion barrier (silicon nitride) to achieve stable device characteristics and automatic alignment of the gate electrode with respect to source and drain. The gate insulator, comprising 600 Å of grown silicon dioxide covered with 400 Å of silicon nitride, is formed at the beginning of fabrication. Thus, the Si-SiO<sub>2</sub> interface is established at a point where the best state-of-the-art cleaning techniques can be applied to the starting material. A thick (8000 Å) layer of SiO<sub>2</sub> is pyrolytically deposited over the nitride to minimize contact capacitances in the finished structure. This must be removed from the active device region, and advantage is taken of the difference in etch rate between SiO<sub>2</sub> and silicon nitride to ensure a well-controlled gate insulator thickness. Thus the nitride layer serves the dual function of providing a barrier to mobile ions in the completed structure, and of acting as an etch-resistant layer during fabrication to achieve control over geometry.

A polycrystalline layer of silicon is used to form the gate electrode, which is shaped early in the process, and is used to define the limits of the source and drain windows. This aspect of the fabrication assures self-alignment of the gate electrode with respect to source and drain. During the diffusion of source and drain regions the polycrystalline silicon is rendered sufficiently conductive that no metallization of the gate electrode is required, except at one end for contacting purposes. This eliminates the need for a critical photoresist alignment.

Both n and p induced-channel (enhancement) devices have been made with this process. Turn-on voltages at  $10 \, \mathrm{JA}$  daria current of  $+1.53 \, \mathrm{V}$  (n-channel) and  $-1.64 \, \mathrm{V}$  (p-channel) with less than  $12 \, \mathrm{per}$  cent spread over a slice were obtained. Analysis of the device characteristics indicates field-effect mobilities of  $335 \, \mathrm{and} \, 233 \, \mathrm{cm} \, 24 \, \mathrm{vec}$  for the n- and p-channel devices respectively. Aging behavior under bias at  $300^{\circ}\mathrm{C}$  indicates the presence of residual mobile positive charge of the order of  $1.5 \times 10^{11} \, \mathrm{charges}/\mathrm{cm}^2$ , resulting in turn-on voltage shifts of less than  $1 \, \mathrm{V}$  over several hundred hr with  $+10 \, \mathrm{V}$  applied to the gate.

Résumé—Les transistors d'effet de champ à porte isolée ont été fabriqués par des procédés comprenant des étapes de corrosion auto-limitatives et une photo-résistance non-cubique. Parmi les importantes caractéristiques de la méthode sont inclues la formation de l'isolement de porte sous des conditions extrèmement propres, l'incorporation d'une barrière alcaline d'ion (silicium nitré) pour pouvoir atteindre des caractéristiques de dispositif stable et un alignement automatique de l'électrode de porte par rapport à la source et au drain. L'isolement de porte, comprenant 600 Å de bioxide de silicium éveloppé couvert le 400 Å de silicium nitré est formé au début de la fabrication. Donc, l'interface Si-O<sub>2</sub>Si est établi à un point où les techniques de nettoyage les plus avancées peuvent être appliquées au matériau de départ. Une épaisse couche (800 Å) de O<sub>2</sub>Si est deposée pyrolitiquement sur l'azotate pour minimiser les capacités de contact dans la structure finale. Celle-ci doit être retirée de la région active du dispositif et on profite de la différence du taux de corrosion entre l'O<sub>2</sub>Si et el silicium nitré

acilities.

#### METAL-NITRIDE-OXIDE-SILICON FIELD-EFFECT TRANSISTORS, SELF-ALIGNED GATES 655

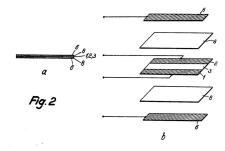

Fig. 1. Definition of general gate area.

Fig. 2. Upper silicon dioxide layer removed in gate area.

Fig. 3. Silicon evaporation in gate area.

Fig. 5. Silicon removal from source and drain areas.

Fig. 6. Excess silicon dioxide removed from source and drain areas.

Fig. 7. Definition of contact pads on upper surface.

-SILICON DIOXIDE FIG. 8. Excess silicon removed from top surface.

Fig. 9. Silicon nitride and silicon dioxide removed from source and drain.

<sup>\*</sup> Presented at the Metallurgical Society (AIME) Meeting, New York, August (1967).

<sup>†</sup> Present address: RCA Laboratories, Princeton, New Jersey.

<sup>‡</sup> Present address: IBM Corporation, East Fishkill Facilities.

# Problems and Predictions

"Prediction is very difficult, especially about the future"

Niels Bohr

### Past predictions (1971)

Solid-State Electronics, 1972, Vol. 15, pp. 819-829. Pergamon Press. Printed in Great Britain

# FUNDAMENTAL LIMITATIONS IN MICROELECTRONICS—I. MOS TECHNOLOGY\*

B. HOENEISEN and C. A. MEAD

California Institute of Technology, Pasadena, California 91109, U.S.A.

(Received 11 August 1971; in revised form 8 November 1971)

The minimum channel length of a 2V transistor is  $\approx 0.4 \,\mu\text{m}$ . This length is a factor of 10 smaller than the channel of the smallest present day devices. The mask alignment tolerances required to manufacture such a device are within the capabilities of electron beam pattern generation techniques. Thus we can envision fully dynamic or complementary integrated silicon chips with up to  $\approx 3 \times 10^7$  MOS transistors per cm<sup>2</sup>, operating in the 10 to 30 MHz range, as shown in Fig. 1.

#### The foundation paper (1974)

# Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions

ROBERT H. DENNARD, MEMBER, IEEE, FRITZ H. GAENSSLEN, HWA-NIEN YU, MEMBER, IEEE, V. LEO RIDEOUT, MEMBER, IEEE, ERNEST BASSOUS, AND ANDRE R. LEBLANC, MEMBER, IEEE

Classic Paper

This paper considers the design, fabrication, and characterization of very small MOSFET switching devices suitable for digital integrated circuits using dimensions of the order of 1 \mu. Scaling relationships are presented which show how a conventional MOS-FET can be reduced in size. An improved small device structure is presented that uses ion implantation to provide shallow source and drain regions and a nonuniform substrate doping profile. Onedimensional models are used to predict the substrate doping profile and the corresponding threshold voltage versus source voltage characteristic. A two-dimensional current transport model is used to predict the relative degree of short-channel effects for different device parameter combinations. Polysilicon-gate MOSFET's with channel lengths as short as 0.5 \mu were fabricated, and the device characteristics measured and compared with predicted values. The performance improvement expected from using these very small devices in highly miniaturized integrated circuits is projected.

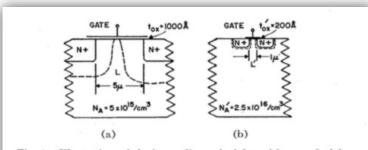

Fig. 1. Illustration of device scaling principles with  $\kappa=5$ . (a) Conventional commercially available device structure. (b) Scaled-down device structure.

# Pre-Dennard Scaling

AFCRL-62-140

3 29 3

282 930

## RCA LABORATORIES

SPECIAL SCIENTIFIC REPORT

INVESTIGATIONS OF FUNDAMENTAL LIMITATIONS

DETERMINING THE ULTIMATE SIZE OF MICROSTRUCTURES

CONTRACT NO. AF19 (604)-8040

PREPARED FOR

ELECTRONICS RESEARCH DIRECTORATE

AIR FORCE CAMBRIDGE RESEARCH LABORATORIES

OFFICE OF AEROSPACE RESEARCH

UNITED STATES AIR FORCE

BEDFORD. MASSACHUSETTS

PROJECT NO. 5633 TASK NO. 56332

REPORT DATE: FEBRUARY 28, 1962

PRINCETON, NEW JERSEY

Summarizing the scaling laws for field-effect devices, with limitations cited above:

| length         | (1)  |

|----------------|------|

| area           | (2)  |

| doping         | (-1) |

| fixed charge   | (2)  |

| electric field | (0)  |

| voltage        | (1)  |

| capacitance    | (1)  |

-6

| current            | (1)  |

|--------------------|------|

| resistance         | (0)  |

| time constant, RC  | (1)  |

| power              | (2)  |

| area power density | (0). |

These relations and limitations will be discussed quantitatively following a review of bipolar transistor scaling relationships.

School - 2021 19

### Past predictions (1989)

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 36, NO. 9, SEPTEMBER 1989

# MOSFET Scaling Limits Determined by Subthreshold Conduction

JOSEPH M. PIMBLEY, MEMBER, IEEE, AND JAMES D. MEINDL, FELLOW, IEEE

mation and ultrathin (< 50 Å) gate insulators. With vanishingly small (< 50 Å) junction depth, a 30-Å gate oxide dielectric and a channel acceptor concentration of 2  $\times$  10  $^{18}$  per cubic centimeter, one may achieve acceptably low subthreshold conduction at effective channel lengths down to 0.06  $\mu m$  at an operating temperature of 300 K.

#### Past predictions (2001)

# Device Scaling Limits of Si MOSFETs and Their Application Dependencies

DAVID J. FRANK, MEMBER, IEEE, ROBERT H. DENNARD, FELLOW, IEEE, EDWARD NOWAK, MEMBER, IEEE, PAUL M. SOLOMON, FELLOW, IEEE, YUAN TAUR, FELLOW, IEEE, AND HON-SUM PHILIP WONG, FELLOW, IEEE

The scale length theory that has been presented here provides a useful framework within which to understand the tradeoff between channel length and short channel effects. Using this theory in conjunction with the various limiting effects, we have projected that bulk-like CMOS should be extendible down to about 14-nm nominal channel length for high-performance logic and ~35 nm for very low power applications, with intermediate applications falling in between.

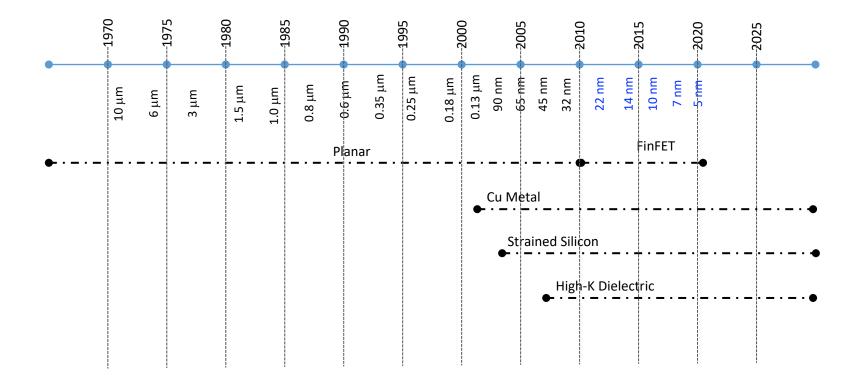

#### Brief review of breakthroughs in the last 20 years

- Lithography

- Computational lithography

- Immersion lithography

- EUV

- •

- Strained Silicon

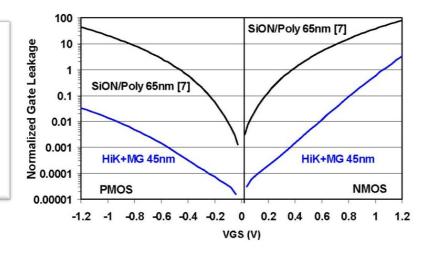

- High-K Metal Gate

- FinFET

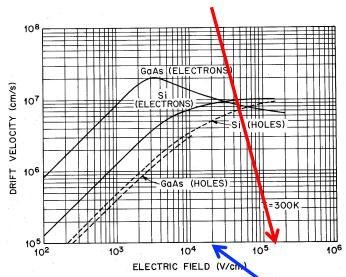

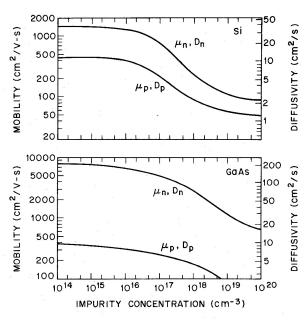

## Problem #1: velocity saturation

#### Modern transistors operate here.

**Fig. 23** Drift velocity versus electric field in GaAs and Si. <sup>12</sup>, <sup>13</sup> Note that for *n*-type GaAs, there is a region of negative differential mobility.

Si Detectors operate here

Fig. 3 Mobilities and diffusivities in Si and GaAs at 300 K as a function of impurity concentration. 4. 5

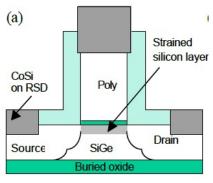

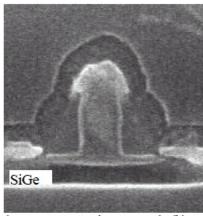

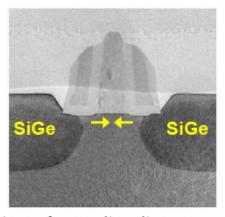

#### Faster carriers: Strained Silicon (1)

#### NMOS (strain)

PMOS (compress)

improvement. Dramatic (>50%) strain induced hole channel mobility improvement is demonstrated for our devices with 17% Ge composition. Fig. 2 shows significant improvement

from T. Ghani et al., IEDM 2003

## Strained Silicon (2)

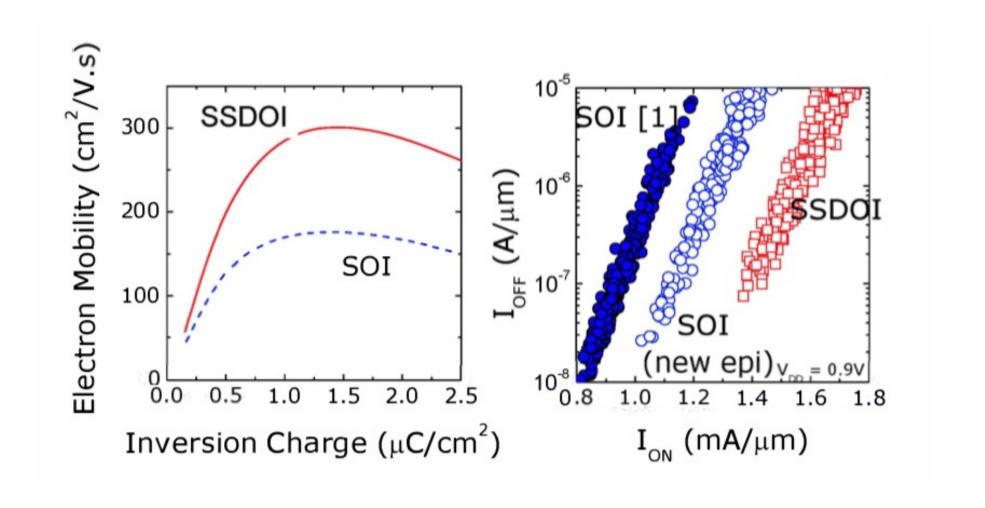

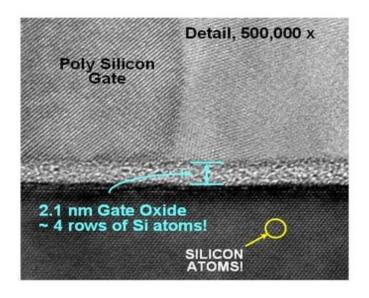

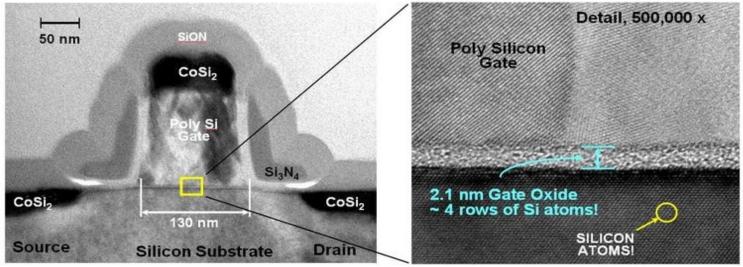

#### Problem #2: leakage through gate oxide

Gate oxide in a 130nm technology

### High-K gate dielectric

(12) United States Patent Yu et al.

(10) Patent No.: US 6,504,214 B1 (45) Date of Patent: Jan. 7, 2003

(54) MOSFET DEVICE HAVING HIGH-K DIELECTRIC LAYER

(75) Inventors: **Bin Yu**, Cupertino, CA (US); **Qi Xiang**, San Jose, CA (US)

(73) Assignee: Advanced Micro Devices, Inc., Sunnyvale, CA (US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 10/044,246

(22) Filed: Jan. 11, 2002

6,020,024 A 2/2000 Maiti et al. 438/275 (210,1999 B1 4/2001 Hobbs et al. 458/275 (210,1999 B1 4/2001 Gardner et al. 257/382 (26261,887 B1 \* 7/2001 Miyano et al. 257/382 (26261,887 B1 \* 7/2001 Hobbs et al. 438/218 (230,020 B1 \* 10/2001 Hobbs et al. 438/287 (2436,438 B1 \* 2/2002 Yagishita et al. 438/197 (240,7435 B1 \* 6/2002 Ma et al. 257/411 (2002/031909 A1 \* 3/2002 Cabral et al. 438/655

\* cited by examiner

Primary Examiner—Carl Whitehead, Jr. Assistant Examiner—Stephen W. Smoot

(74) Attorney, Agent, or Firm—Renner, Otto, Boisselle &

Sklar, LLP

(57) ABSTRACT

greater detail below. Although other materials can be selected for the gate dielectric **34**, hafnium oxide (e.g., HfO<sub>2</sub>), zirconium oxide (e.g., ZrO<sub>2</sub>), cerium oxide (e.g., CeO<sub>2</sub>), aluminum oxide (e.g., Al<sub>2</sub>O<sub>3</sub>), titanium oxide (e.g., TiO<sub>2</sub>), yttrium oxide (e.g., Y<sub>2</sub>O<sub>3</sub>) and barium strontium titanate (BST) are example suitable materials for the gate dielectric **34**. In addition, all binary and ternary metal oxides and ferroelectric materials having a K higher than, in one embodiment, about twenty (20) can be used for the gate dielectric **34**.

#### **CMOS Timeline**

## What is actually "wrong" with infinite scaling?

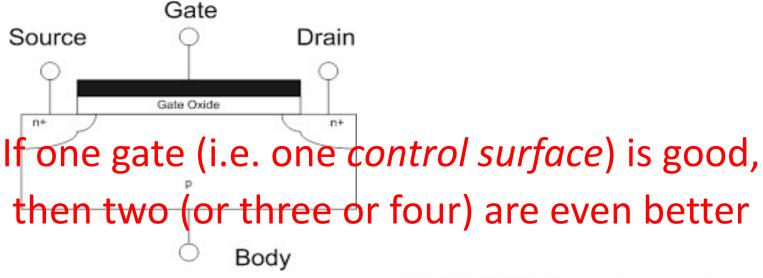

- The 1974 Scaling theory (Dennard et al.) essentially looked at the transistor as a two-dimensional (planar) structure.

- This worked ok up until about 2010

- Classical scaling is only as good as one manages to keep effects in the third dimension ("short channel effects") small, but it fails to describe the behavior of a MOS device when all dimensions are reduced, and doping are increased, and voltages are not reduced (enough).

# Raising from the surface

#### How to get to FINFETs

0038-1101/84 \$3.00 + .00 F 1984 Pergamon Press Ltd.

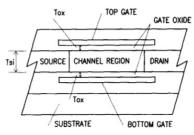

#### CALCULATED THRESHOLD-VOLTAGE CHARACTERISTICS OF AN XMOS TRANSISTOR HAVING AN ADDITIONAL BOTTOM GATE

Toshiba 1983 (Received 30 May 1983; in revised form 24 August 1983)

Fig. 1. Schematic cross-sectional structure of an XMOS transistor having an additional bottom gate which is symmetrically placed to a top gate with a channel region between them. "X" originates from Greek capital letter of xi as this structure resembles its shape.

Electronic Device Division, Electrotechnical Laboratory, Sakura-mura, Ibaraki, 305, Japan T. SEKIGAWA and Y. HAYASHI

To office of the control of the cont

Figure 1: Schematic views of the double-gate SOI MOSFET's.

Berkely 2000

IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 47, NO. 12, DECEMBER 2000

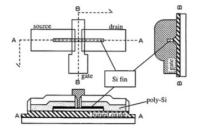

#### FinFET—A Self-Aligned Double-Gate MOSFET Scalable to 20 nm

Digh Hisamoto, Member, IEEE, Wen-Chin Lee, Jakub Kedzierski, Hideki Takeuchi, Kazuya Asano, Member, IEEE, Charles Kuo, Erik Anderson, Tsu-Jae King, Jeffrey Bokor, Fellow, IEEE, and Chenming Hu, Fellow, IEEE

Abstract — MOSFETs with gate length down to 17 nm are reported. To suppress the short channel effect, a novel self-aligned double-gate MOSFET, FinFET, is proposed. By using boron-doped  $Si_{0.4}$  ( $Ge_{0.6}$  as a gate material, the desired threshold voltage was achieved for the ultrathin body device. The quasiplanar nature of this new variant of the vertical double-gate MOSFETs can be fabricated relatively easily using the conventional planar MOSFET process technologies.

Index Terms—Fully depleted SOI, MOSFET, poly SiGe, shortchannel effect.

#### I. INTRODUCTION

O DEVELOP sub-50-nm MOSFETs, the double-gate structure has been widely studied. This is because

Fig. 1. FinFET typical layout and schematic cross sectional structures.

#### Impact of the Vertical SOI "DELTA" Structure on Planar Device Technology

Digh Hisamoto, Member, IEEE, Toru Kaga, Member, IEEE, and Eiji Takeda, Senior Member, IEEE

Abstract—A fully depleted lean channel transistor (DELTA) with its gate incorporated into a new sertical ultra-thin SOI of structure is presented. In the deep-submicrometer region, selective oxidation produces and isolates an ultra-thin SOI MOS-FET that has high crystalline quality, as good as that of conventional bulk single-crystal devices. Experiments and three-dimensional simulations have shown that this new gate structure has effective channel control, and that the vertical ultra-thin SOI structure provides superior device characteristics: read high transconductance, a minimized subtyrebodd swing, and high transconductance.

is required. Moreover, it is evident that these structures are difficult to contact to the substrate, and thus suffer from a substrate floating effect.

(a)-(c) Process flow of selective oxidation. (d) Schematic cross

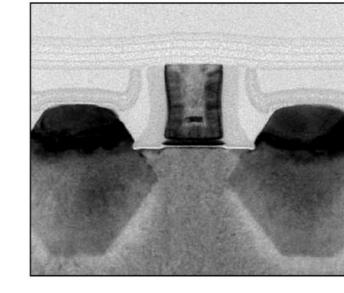

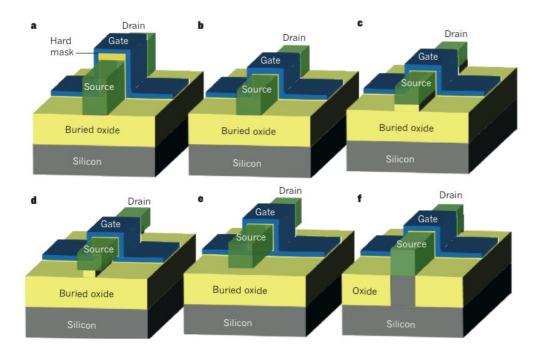

#### Multi-gate devices

• Intel: Tri-gate

• TSMC, GF, Samsung: Finfets

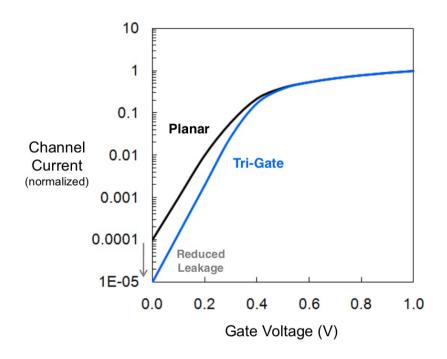

#### Subthreshold slope improvement

#### **Transistor Operation**

Intel @ 22 nm

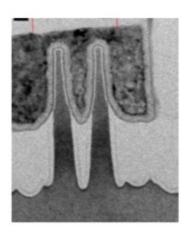

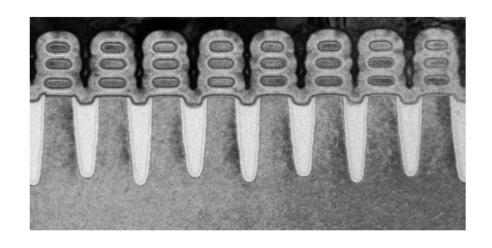

#### 10 nm Finfet

#### FinFET dimensions

#### From the ITRS 2011 report

| Year of Production  |          | 2013 | 2015 | 2017 | 2019 | 2021 | 2023 | 2025 | 2028 |

|---------------------|----------|------|------|------|------|------|------|------|------|

| FinFET Fin Width (n | ew) (nm) | 7.6  | 7.2  | 6.8  | 6.4  | 6.1  | 5.7  | 5.4  | 5.0  |

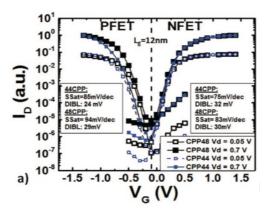

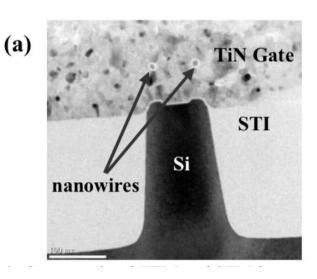

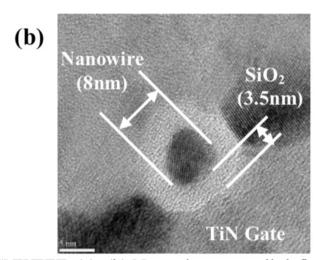

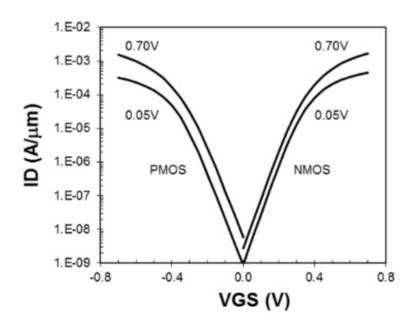

### GAA nanowire transistor = FINFET++

### GAA nanowire transistor

# and yet...

|                   |            |           | Number of       | Foundries wi | th a Cutting E | dge Logic Fal | )           |         |         |      |

|-------------------|------------|-----------|-----------------|--------------|----------------|---------------|-------------|---------|---------|------|

| SilTerra          |            |           |                 |              |                |               |             |         |         |      |

| X-FAB             |            |           |                 |              |                |               |             |         |         |      |

| Dongbu HiTek      |            |           |                 |              |                |               |             |         |         |      |

| ADI               | ADI        |           |                 |              |                |               |             |         |         |      |

| Atmel             | Atmel      |           |                 |              |                |               |             |         |         |      |

| Rohm              | Rohm       |           |                 |              |                |               |             |         |         |      |

| Sanyo             | Sanyo      |           |                 |              |                |               |             |         |         |      |

| Mitsubishi        | Mitsubishi |           |                 |              |                |               |             |         |         |      |

| ON                | ON         |           |                 |              |                |               |             |         |         |      |

| Hitachi           | Hitachi    |           |                 |              |                |               |             |         |         |      |

| Cypress           | Cypress    | Cypress   |                 |              |                |               |             |         |         |      |

| Sony              | Sony       | Sony      |                 |              |                |               |             |         |         |      |

| Infineon          | Infineon   | Infineon  |                 |              |                |               |             |         |         |      |

| Sharp             | Sharp      | Sharp     |                 |              |                |               |             |         |         |      |

| Freescale         | Freescale  | Freescale |                 |              |                |               |             |         |         |      |

| Renesas (NEC)     | Renesas    | Renesas   | Renesas         | Renesas      |                |               |             |         |         |      |

| SMIC              | SMIC       | SMIC      | SMIC            | SMIC         |                |               |             |         |         |      |

| Toshiba           | Toshiba    | Toshiba   | Toshiba         | Toshiba      |                |               |             |         |         |      |

| Fujitsu           | Fujitsu    | Fujitsu   | Fujitsu         | Fujitsu      |                |               |             |         |         |      |

| TI                | TI         | TI        | TI              | TI           |                |               |             |         |         |      |

| Panasonic         | Panasonic  | Panasonic | Panasonic       | Panasonic    | Panasonic      |               |             |         |         |      |

| TMicroelectronics | STM        | STM       | STM             | STM          | STM            |               |             |         |         |      |

| UMC               | имс        | UMC       | UMC             | UMC          | UMC            |               |             |         |         |      |

| IBM               | IBM        | IBM       | IBM             | IBM          | IBM            | IBM           |             |         |         |      |

| AMD               | AMD        | AMD       | GlobalFoundries | GF           | GF             | GF            | GF          |         |         |      |

| Samsung           | Samsung    | Samsung   | Samsung         | Samsung      | Samsung        | Samsung       | Samsung     | Samsung | Samsung |      |

| TSMC              | TSMC       | TSMC      | TSMC            | TSMC         | TSMC           | TSMC          | TSMC        | TSMC    | TSMC    |      |

| Intel             | Intel      | Intel     | Intel           | Intel        | Intel          | Intel         | Intel       | Intel   | Intel   | Futu |

| 180 nm            | 130 nm     | 90 nm     | 65 nm           | 45 nm/40 nm  | 32 nm/28 nm    | 22 nm/20 nm   | 16 nm/14 nm | 10 nm   | 7 nm    | 5 n  |

# New Ideas

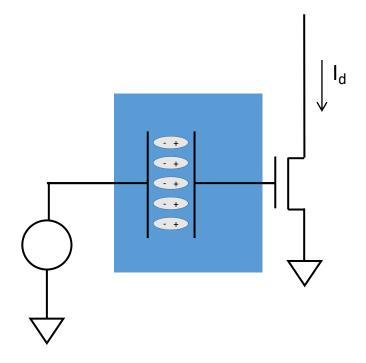

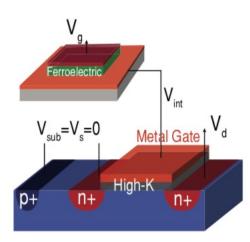

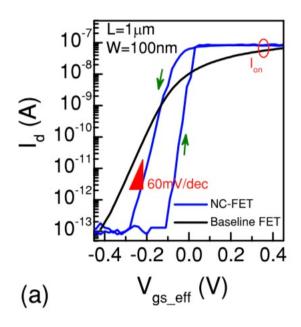

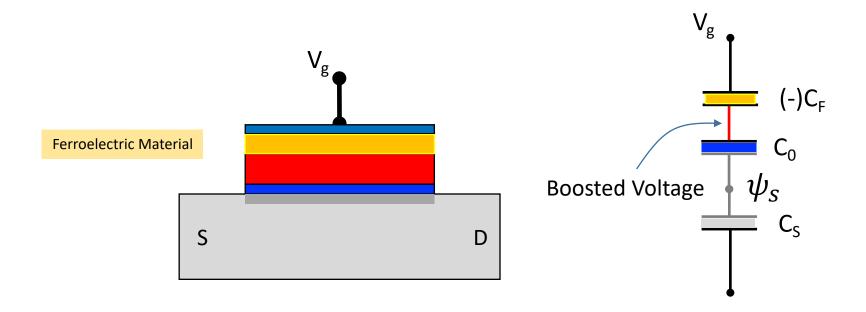

**Negative Capacitance Transistors (Ferroelectric Transistors)**

**Adiabatic Circuits**

**Tunneling Transistors**

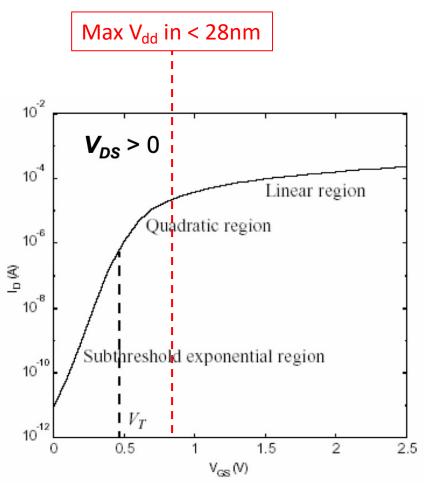

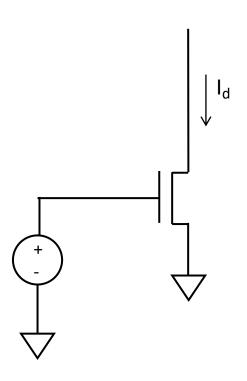

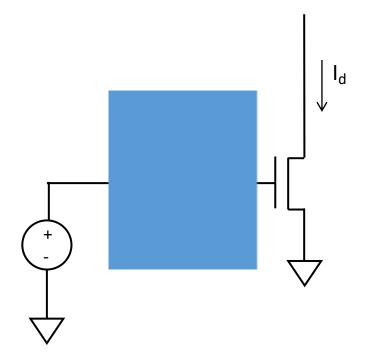

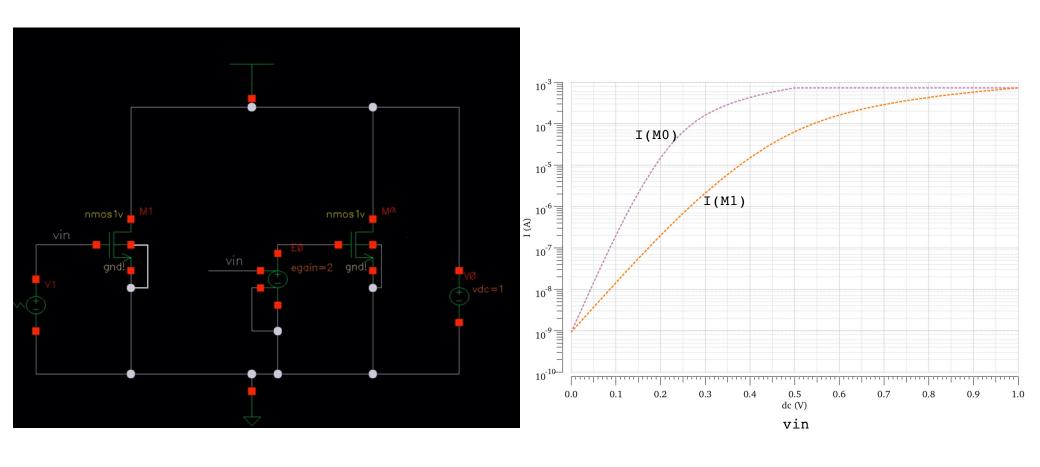

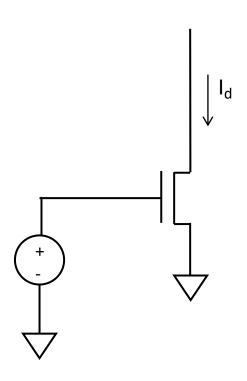

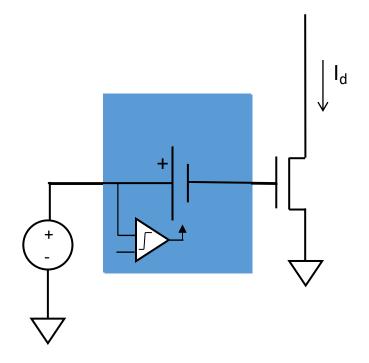

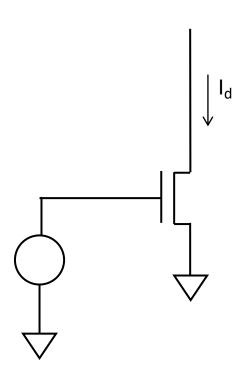

### Turning on a MOSFET

### **Short-channel MOSFET**

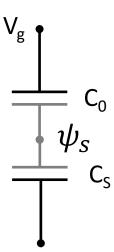

# What does Boltzmann have to do with microelectronics?

$$SS = \frac{\partial V_g}{\partial (log I_d)} = \frac{\partial V_g}{\partial \psi_s} * \frac{\partial \psi_s}{\partial (log I_d)}$$

$$\min\left(\frac{\partial \psi_{S}}{\partial (\log I_{d})}\right) = Ln(10) * \frac{k_{B}T}{q} \approx 60 \frac{mV}{decade}$$

$$\frac{\partial V_{g}}{\partial \psi_{S}} = 1 + \frac{C_{S}}{C_{o}}$$

# [A little Gedankenexperiment (1)]

# [A little Gedankenexperiment(2)]

# [A little Gedankenexperiment (3)]

# [A little Gedankenexperiment (4)]

### A real exercise

PZT (Lead-Zirconate-Titanate) capacitor

# NC gate stack

@IEDM 2018, Negative Capacitance devices occupied 3 sessions and are mentioned in 16 papers

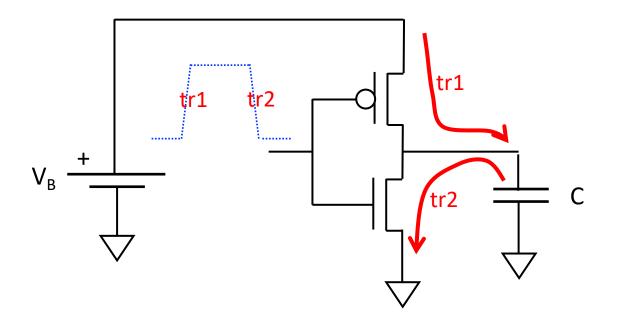

# Adiabatic Logic Circuit

# CMOS Logic: charging and discharging capacitors

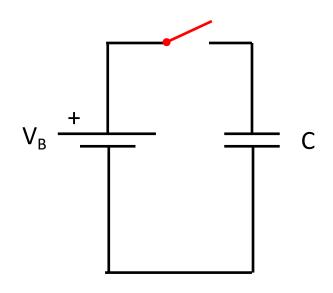

# Charging a Capacitor

A capacitor charged from a battery has a total charge:

$$Q = C * V_B$$

and the energy required to charge it is:

$$E = (C * V_B) * V_B = C * V_B^2$$

The energy stored on a capacitor C is instead:

$$E_C = \frac{1}{2}C * V_B^2$$

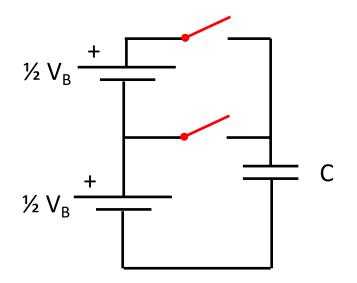

# Charging capacitors with minimal effort

$$E_C = \frac{1}{2} C V_B^2$$

$$E_{wasted} = \frac{1}{2} C V_B^2$$

$$E_C = \frac{1}{2} C V_B^2$$

$$E_{wasted} = \frac{1}{2}C \left(\frac{V_B}{2}\right)^2 + \frac{1}{2}C \left(\frac{V_B}{2}\right)^2 = \frac{1}{4}C V_B^2$$

# Other non-Boltzmann limited devices

### Tunnel diode

LETTER'S TO THE EDITOR

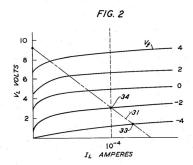

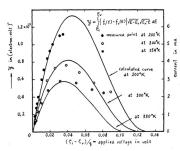

Fig. 1. Semilog plots of the measured current-voltage characteristic at 200°K, 300°K, and 350°K.

#### New Phenomenon in Narrow Germanium b-n Tunctions

LEO ESAKI

Tokyo Tsushin Kogyo, Limited, Shinagawa, Tokyo, Japan (Received October 11, 1957)

TN the course of studying the internal field emission I in very narrow germanium p-n junctions, we have found an anomalous current-voltage characteristic in the forward direction, as illustrated in Fig. 1. In this p-n junction, which was fabricated by alloying techniques, the acceptor concentration in the p-type side and the donor concentration in the n-type side are, respectively, 1.6×1019 cm-3 and approximately 1019 cm-3. The maximum of the curve was observed at 0.035±0.005 volt in every specimen. It was ascertained that the specimens were reproducibly produced and showed a general behavior relatively independent of temperature. In the range over 0.3 volt in the forward direction, the current-voltage curve could be fitted almost quantitatively by the well-known relation:  $I=I_s[\exp(qV/kT)-1]$ . This junction diode is more conductive in the reverse direction than in the forward direction. In this respect it agrees with the rectification direction predicted by Wilson, Frenkel, and Joffe, and Nordheim 25 years ago.1

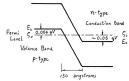

The energy diagram of Fig. 2 is proposed for the case

in which no voltage is applied to the junction, though the band scheme may be, at best, a poor approximation for such a narrow junction. (The remarkably large values observed in the capacity measurement indicated that the junction width is approximately 150 angstroms, which results in a built-in field as large as 5×105 volts/cm.)2 In the reverse direction and even in the forward direction for low voltage, the current might be carried only by internal field emission and the possibility of an avalanche might be completely excluded because the breakdown occurs at much less than the threshold voltage for electron-hole pair production.3 Owing to the large density of electrons and holes, their distribution should become degenerate; the Fermi level in the p-type side will be 0.06 ev below the top of the valence band,  $E_v$ , and that in the *n*-type side will lie above the bottom of the conduction band, Ec. At zero bias, the field emission current  $I_{v\rightarrow c}$  from the valence band to the empty state of the conduction band and the current

Fig. 2. Energy diagram of the p-n junction at 300°K

604

#### LETTERS TO THE EDITOR

Fig. 3. Comparison of the current-voltage curves calculated with the measured points at 200°K, 300°K, and 350°K.

$I_{c \rightarrow v}$  from the conduction band to the empty state of the valence band should be detail-balanced. Expressions for  $I_{c\rightarrow v}$  and  $I_{v\rightarrow c}$  might be formulated as follows:

$$I_{c \to v} \! = \! A \, \int_{E_c}^{E_v} f_c(E) \rho_c(E) Z_{c \to v} \{ 1 \! - \! f_v(E) \} \rho_v(E) dE, \label{eq:interpolation}$$

$$I_{v \rightarrow c} = A \int_{E_c}^{E_v} f_v(E) \rho_v(E) Z_{v \rightarrow c} \{1 - f_c(E)\} \rho_c(E) dE,$$

where  $Z_{c \to v}$  and  $Z_{t \to c}$  are the probabilities of penetrating the gap (these could be assumed to be approximately equal);  $f_c(E)$  and  $f_v(E)$  are the Fermi-Dirac distribution functions, namely, the probabilities that a quantum state is occupied in the conduction and valence bands, respectively;  $\rho_c(E)$  and  $\rho_v(E)$  are the energy level densities in the conduction and valence bands, respectively.

When the junction is slightly biased positively and negatively, the observed current I will be given by

$$I = I_{c \to v} - I_{v \to c} = A \int_{E_{c}}^{E_{v}} \{f_{c}(E) - f_{v}(E)\} Z \rho_{c}(E) \rho_{v}(E) dE.$$

From this equation, if Z may be considered to be almost constant in the small voltage range involved, we could calculate fairly well the current-voltage curve at a certain temperature, indicating the dynatron-type characteristic in the forward direction, as shown in Fig. 3.

Further experimental results and discussion will be published at a later time. The author wishes to thank Miss Y. Kurose for assistance in the experiment and the calculations.

H. Wilson, Proc. Roy. Soc. (London) A136, 487 (1932);

J. Frenkel and A. Joffe, Physik. Z. Sowjetunion 1, 60 (1932);

L. Nordheim, Z. Physik 75, 454 (1932).

McAfee, Ryder, Shockley, and Sparks, Phys. Rev. 83, 650 (1931);

C. Zener, Proc. Roy. Soc. (London) 145, 523 (1934).

S. L. Miller, Phys. Rev. 99, 1234 (1935);

A. G. Chynoweth and K. G. McKay, Phys. Rev. 106, 418 (1935).

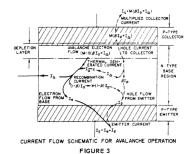

## Devices with internal gain

# 1957 TRANSISTOR AND SOLID STATE CIRCUITS CONFERENCE

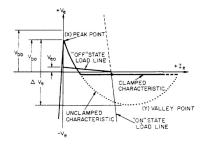

#### 1.1 A DECADE RING COUNTER USING AYAL ANCHE-OPERATED JUNCTION TRANSISTORS

J. E. Lindsay - Radio Corp. of America, Camden

- I. IMPROVED SWITCHING TIMES

- 2. CURRENT CONTROLLED N-TYPE NEGATIVE RESISTANCE CHARACTERISTICS SUITABLE FOR BISTABLE OPERATION

- AVALANCHE DERIVED PROPERTIES RELATIVELY INSENSITIVE TO TEMPERATURE CHANGE

- 4. IMPORTANT FEATURES CAN BE DESCRIBED ANALYTICALLY

SUMMARY OF AVALANCHE CHARACTERISTICS FIGURE 1

EMITTER INPUT CHARACTERISTIC AND LOAD LINES FOR THE BISTABLE FLIP-FLOR FIGURE 5

BISTABLE FLIP-FLOP

FIGURE 6

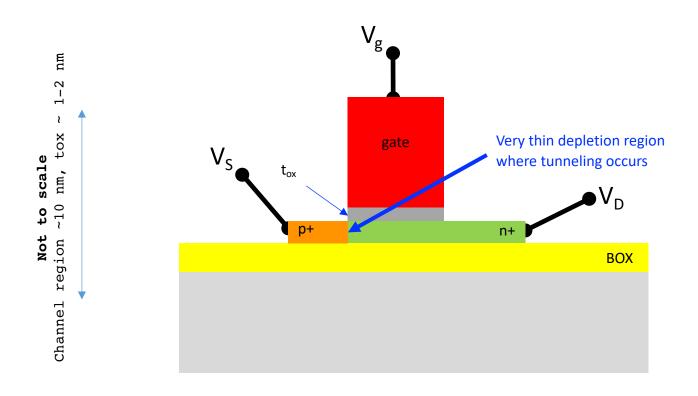

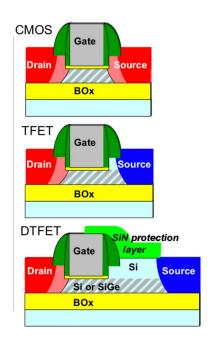

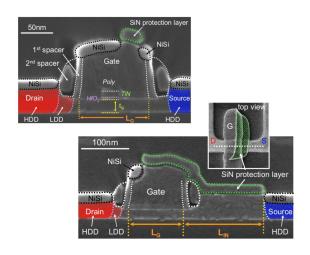

# Tunneling Transistors: Principle

- Very highly doped S and D

- $V_S < V_D$

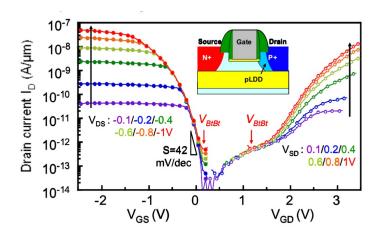

# Tunneling Transistors: Example

# Summary: low supply voltage devices

- Currently with devices powered between 0.8 and 1.2 V, we use about 400-500 mV (~70-80 mV/dec \* 6 dec) to turn them on.

- If one could reduce reduce the "transition region" to about 50 mV (SS  $\sim$  50/6 = 8-10 mV/dec)

- Then it would be conceivable to have a digital logic supply at 150 mV therefore saving:

Power saving:

$$(1.0)^2 / (0.15)^2 = 44$$

times

(i.e. you could recharge your mobile phone less than once per month)

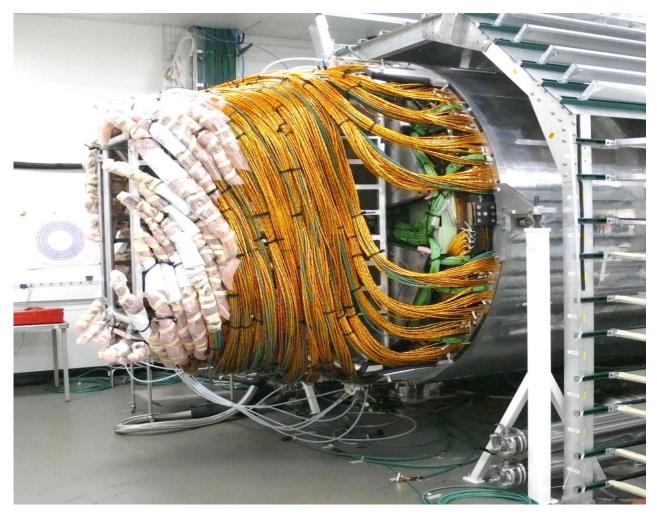

### ... and for the CMS tracker...

... in fact the CMS tracker used 2.5V transistors. If we could use 0.25V transistors the savings in power would be  $(2.5)^2 / (0.25)^2 = 100$  times less cables!!!

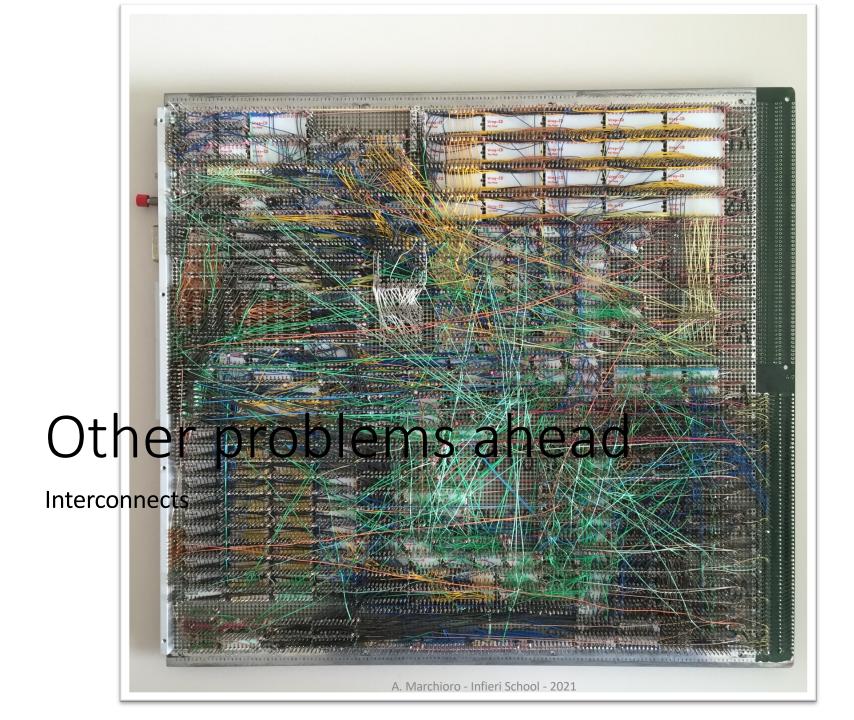

## What is more important: Transistors or wires?

| Metal | Pitch [nm] | Metal tickn.[nm] |

|-------|------------|------------------|

| 0     | 56         | 40               |

| 1     | 81         | 42               |

| 2     | 73         | 40               |

| 3     | 76         | 37               |

| 4     | 80         | 75               |

|       |            |                  |

| 11    | 1000       | 1000             |

A 14 nm FINFET process metal stack

# Metal/Gate ratio in different technologies

| Tech [nm]   | M1 Width/Space | Ratio M1 Width/Lgate |

|-------------|----------------|----------------------|

| 250         | 320/320        | 1.28                 |

| 130         | 160/160        | 1.53                 |

| 65          | 90/90          | 1.5                  |

| 28          | 50/50          | 1.7                  |

| 14 (Finfet) | 28/28          | 2                    |

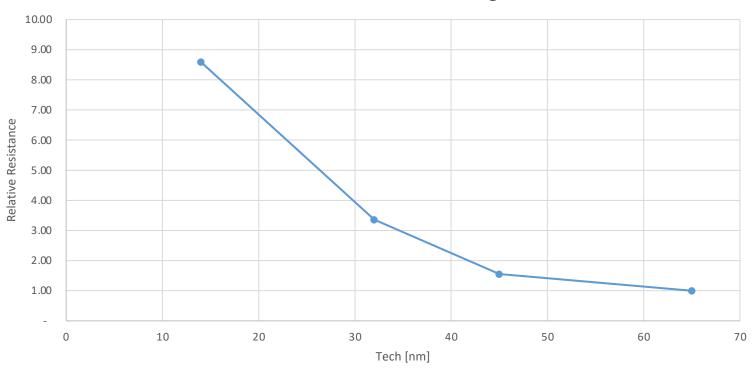

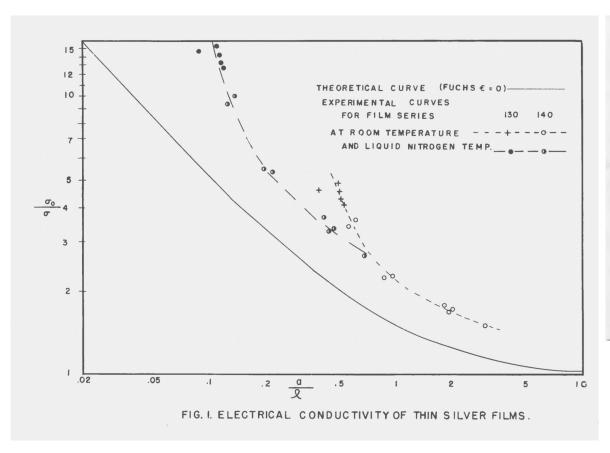

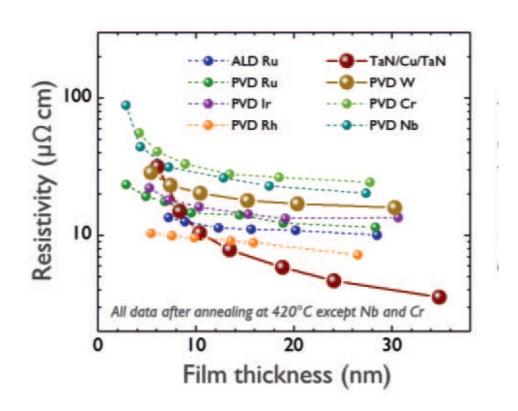

# Wire resistance in "classical" scaling

### Ultra-scaled metals

# Ultra-scaled metals (2)

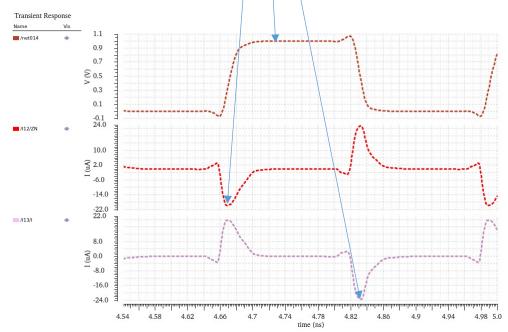

## How many electrons are needed to switch a logic gate?

• 65 nm: ~ 2500 e<sup>-1</sup>

• 28 nm: ~ 850 e<sup>-</sup>

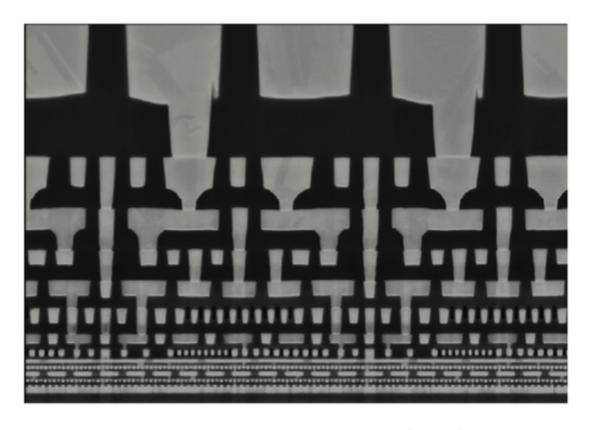

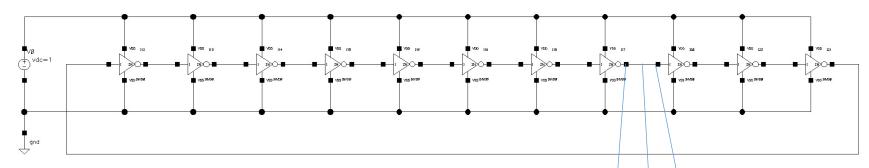

# Digital Amplifier for small cell Si sensor

# Digital Amplifier (2)

### And what about 5 nm?

- A 5 nm "transistor" switches with < ~100 e⁻ input signal

- That is the signal produced by a MIP particle in about 1um of silicon

Significant issues still exist in the integration of an appropriate sensor with very low parasitic capacitances (intrinsic and extrinsic), but from the point of view of the sensing electronics, it may well be possible to design a pixelized detector with sufficiently small cells to be read out entirely by simple inverters.

# Conclusions

### Take home message

- "Brute-force" growth (was called "scaling") is being replaced by "more-sweat" growth

- More sweat also implies more investments, much more investments (especially human)!

- But lots of opportunities are still open for creative designers.

- Much functionality can still be added to instrumentation for physics and other sciences

- The impact of "digital" is still very small in HEP, replace "quantity" of data with "quality" of data

- Beware, gain in analog may even be < 1</li>

#### will

- More exotic technologies (TSVs, 3D, wafer stacking, adv. packaging...) bey become available also for low-volume, but history teaches that one should bet on mainstream opportunities

- New engineering "structures" may be mandatory to exploit the above!

# Thank you

# A final quotation

And it ought to be remembered that there is nothing more difficult to take in hand, more perilous to conduct, or more uncertain in its success, than to take the lead in the introduction of a new order of things, because the innovator has for enemies all those who have done well under the old conditions, and lukewarm defenders in those who may do well under the new.

N. Machiavelli, The Prince, ch.6