# How Advanced Packaging Is Changing Integrated Circuits

September 3, 2021

## **Advanced Packaging**

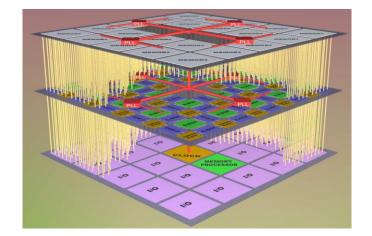

Advanced packaging is a general grouping of a variety of distinct techniques, including 2.5D, 3D-IC, fan-out wafer-level packaging and system-in-package.

From Semiconductor Engineering

$\rightarrow$  Appling semiconductor processes and techniques to packaging

## Chiplet

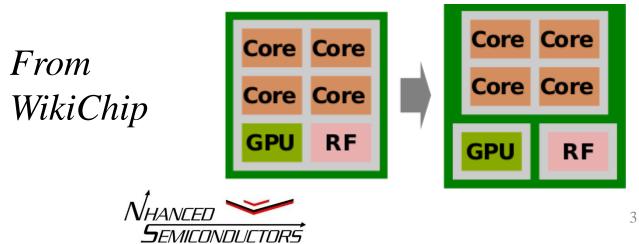

A chiplet is an <u>integrated circuit</u> block that has been specifically designed to work with other similar chiplets to form larger more complex chips. In such chips, a system is subdivided into functional circuit blocks, called "chiplets", that are often made of reusable IP blocks.

# A NEED FOR CHANGE

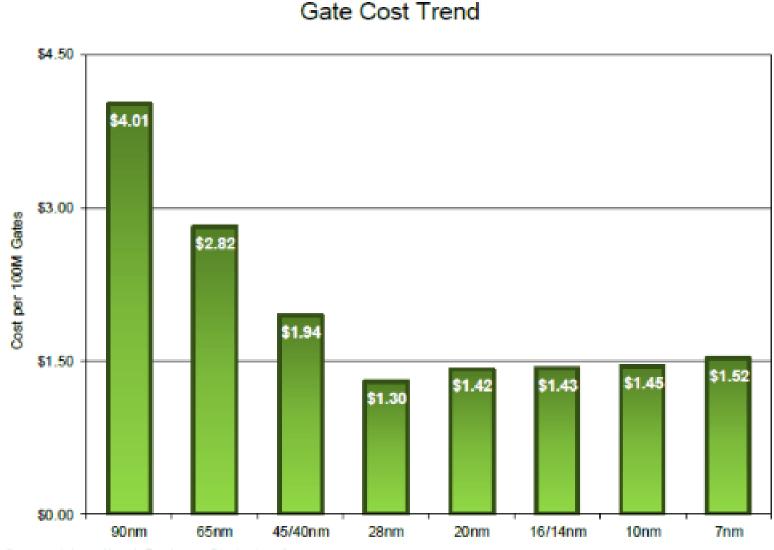

## **Cost Trend Reversal**

Source: International Business Strategies, Inc.

## More Moore

- The end is near...

- 16nm, 14nm, 10nm, 7nm, 5nm, 3nm ...

- Maybe its now. Maybe it's in 3 years or 5 years, but the end of scaling is going to happen within the next decade

- 28nm most cost effective node for years...?

## Internet Of Things

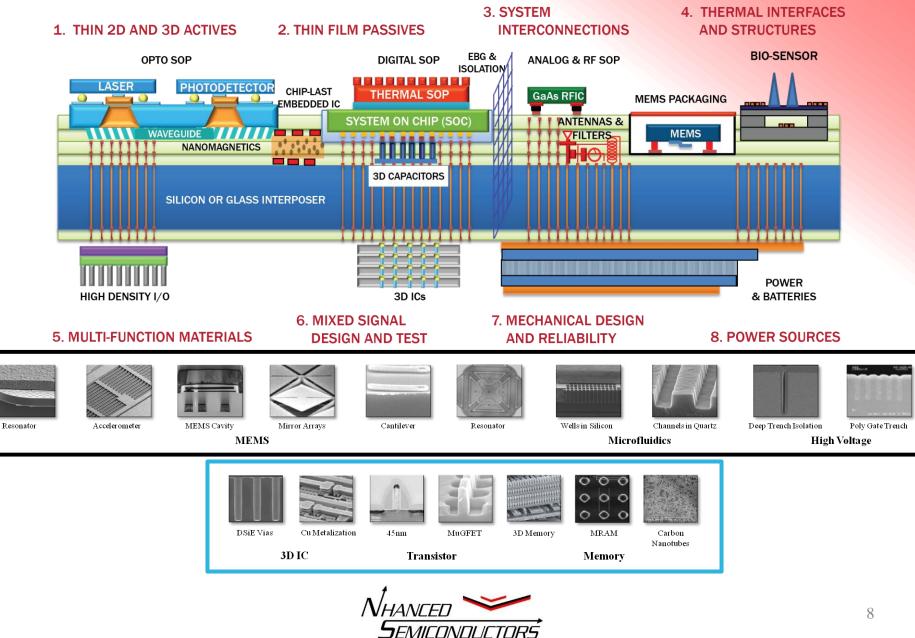

## More Than Moore

#### **GEORGIA TECH PRC**

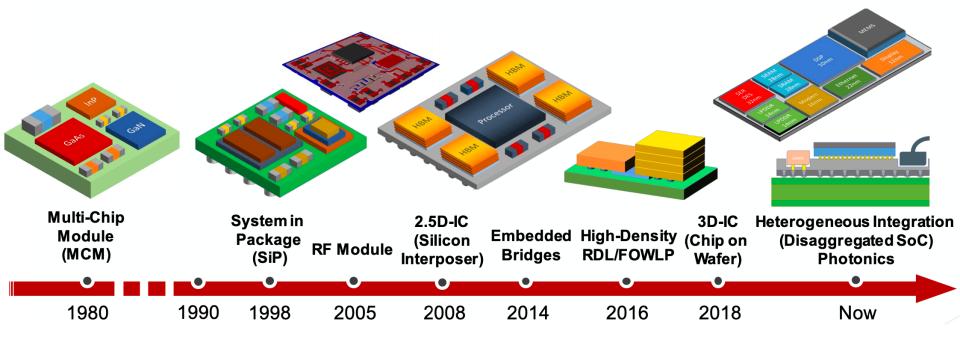

# EVOLUTION AND REVOLUTION — ADVANCED PACKAGING AND CHIPLETS

## Steps Toward Advanced Packaging and Chiplets

### Semiengineering.com

## **New Possibilities**

## **Better and Faster**

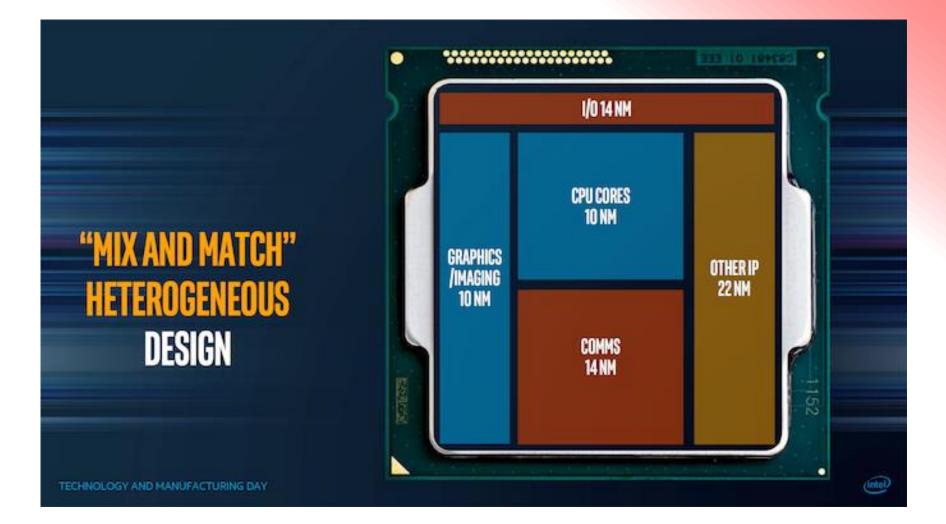

#### **IP/SOC Methodology Change**

#### Monolithic | Integrated SOC

- Verified at SOC level

- 3-4 years of Dev Time

- 100s of bugs found in Silicon

- No reuse

#### Multiple Dies | in optimal process

- Verified at IP level

- 2-3 years of Dev Time

- 10s of bugs found in Silicon

- Some reuse

#### Individual IPs | in optimal process

- Verified at IP/Chiplet level

- 1 year of Dev Time

- <10 bugs found in silicon

- Significant reuse

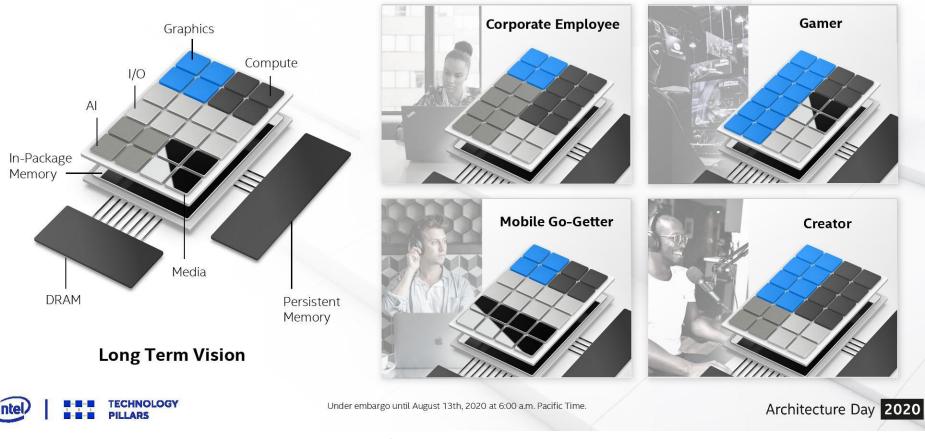

Inte

Under embargo until August 13th, 2020 at 6:00 a.m. Pacific Time.

## Easy Market Retargeting

#### **Purpose Built Client**

## Intel's Vision of the Future

### Client 2.0

|   | EXPERIENCE FIRST              | <ul> <li>Uniquely built to differentiate key experiences</li> <li>Uncompromised performance to deliver seamless experience</li> </ul>                               |

|---|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | SCALABLE                      | <ul> <li>Ability to mix and match function/IPs to processes</li> <li>React faster with reuse and enable faster TTM</li> <li>Developer Friendly Platforms</li> </ul> |

|   | ENERGY EFFICIENT              | <ul> <li>KEI's can benefit from using "Efficient" Cores in SOC Chiplet</li> <li>Pick low power technology for IOs</li> </ul>                                        |

|   | OPTIMAL USE<br>OF MOORE'S LAW | <ul> <li>Focus on Performance for General Purpose Compute (CPU)</li> <li>Focus on Density for scalable compute (GPU, AI etc.)</li> </ul>                            |

| * |                               |                                                                                                                                                                     |

Under embargo until August 13th, 2020 at 6:00 a.m. Pacific Time.

Architecture Day 2020

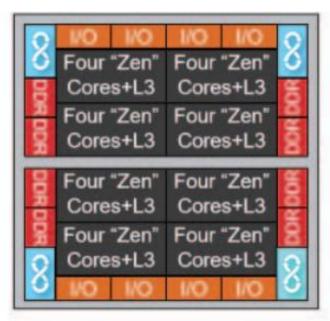

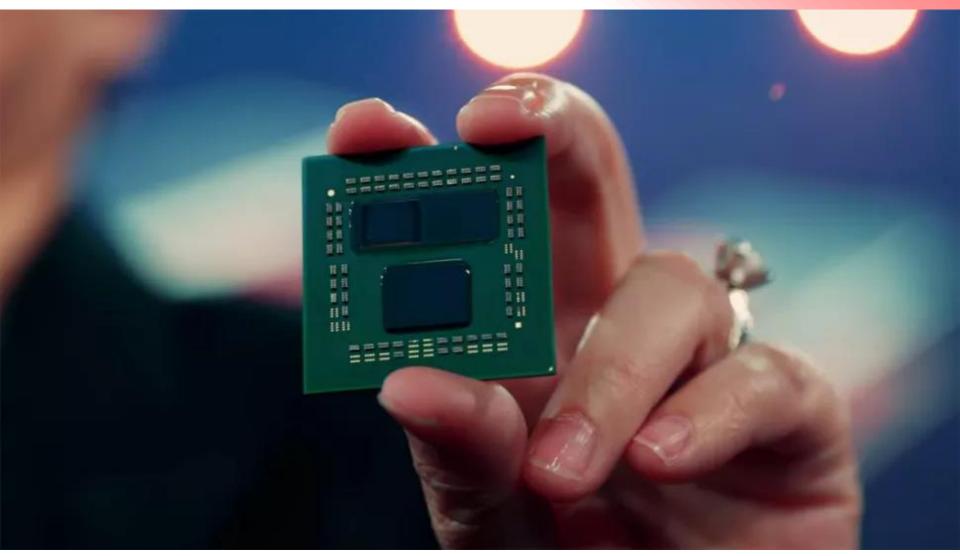

## AMD – Enormous Benefits to Chiplets

Monolithic 32-core Chip 777mm<sup>2</sup> total area 1.0x Cost 4 x 8-core Chiplet, 213mm<sup>2</sup> per chiplet 852mm<sup>2</sup> total area (+9.7%) 0.59x Cost

## **AMD Production Chiplets**

## Xilinx – Using Chiplets For >10 Years

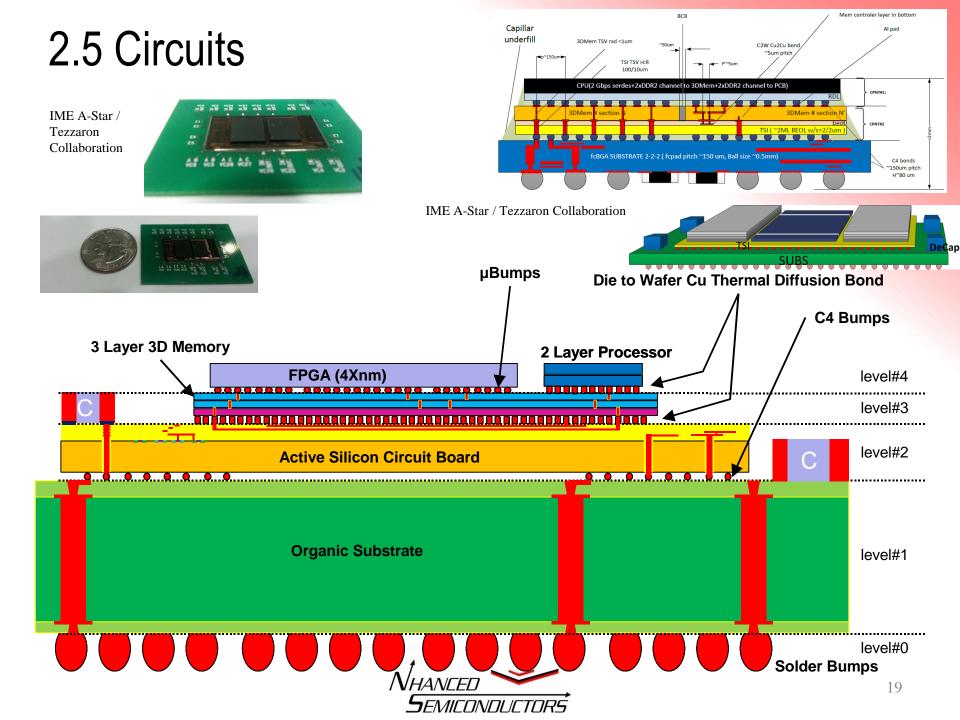

# **2.5D ADVANCED PACKAGING**

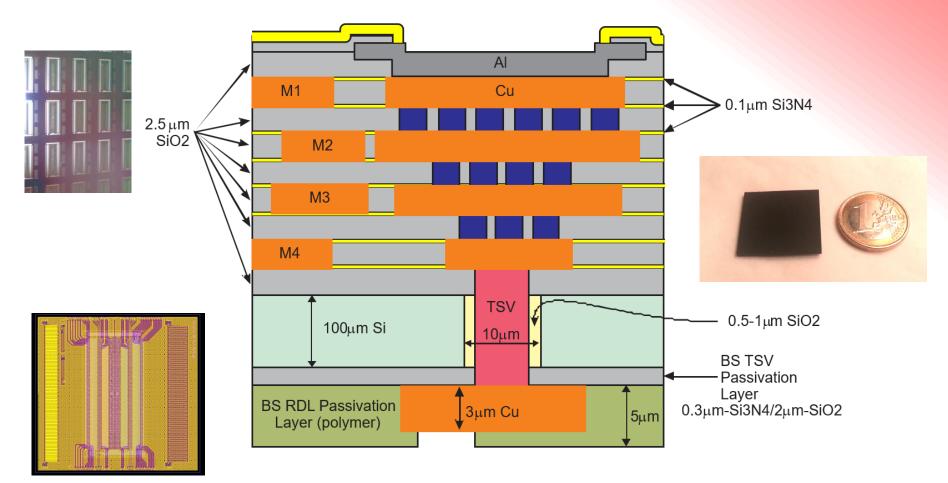

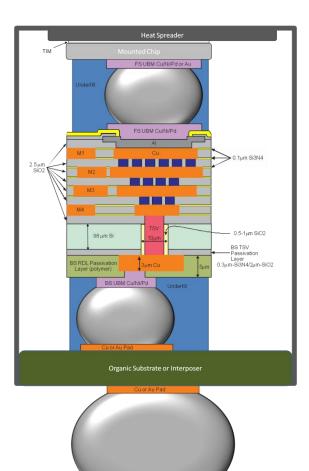

## Si Interposers

Bigger, Better, Faster >50x50mm, Up to 6 layers, Lower R,C

## High Performance Driven By Interposers

>90% performance improvement vs ideal case monolithic >200% better (lower) signal delay vs ideal case monolithic

| Layer  | Metal thickness | R(mΩ/⊡) at DC |            | W   | L       | Cg (fF) |

|--------|-----------------|---------------|------------|-----|---------|---------|

| M1     | 2.5µm           | 7.2           |            | 10  | 2       | 2.3     |

|        |                 |               |            | 200 | 10      | 52      |

| M2     | 2.5µm           | 7.2           |            | 10  | 2       | 1.5     |

| IVIZ   |                 |               |            | 200 | 10      | 17      |

| M3     | 2.5µm           | 7.2           |            | 10  | 2       | 1.1     |

| IVIO   |                 |               |            | 200 | 10      | 15      |

| M4     | 2.5µm           | 7.2           |            | 10  | 2       | 0.74    |

| 1014   |                 |               |            | 200 | 10      | 12      |

|        | TSV Diameter    | TSV<br>Height | Resistance |     | Cg (fF) |         |

| Filled | 10µm            | 100µm         | 21.2mΩ     |     | 180     |         |

| Filled | 50µm            | 400µm         | ~4mΩ       |     | ~600    |         |

## **Glass Interposers**

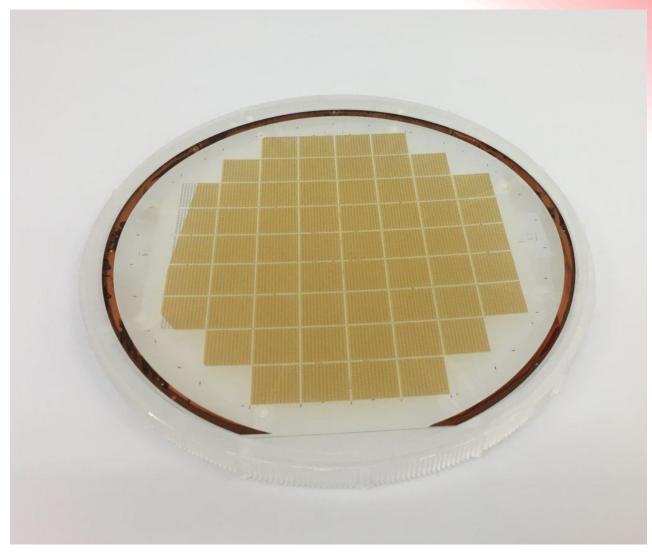

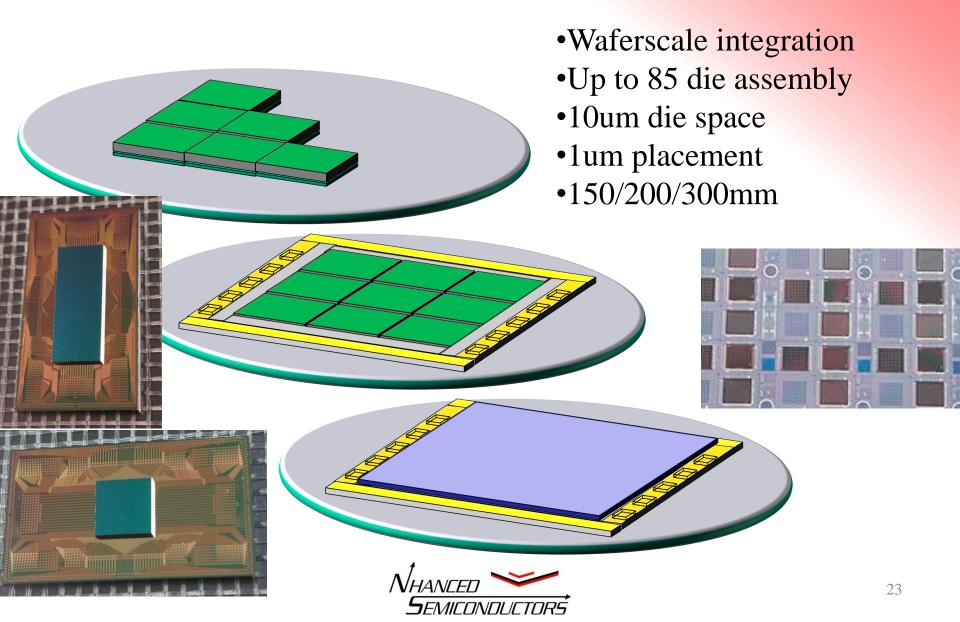

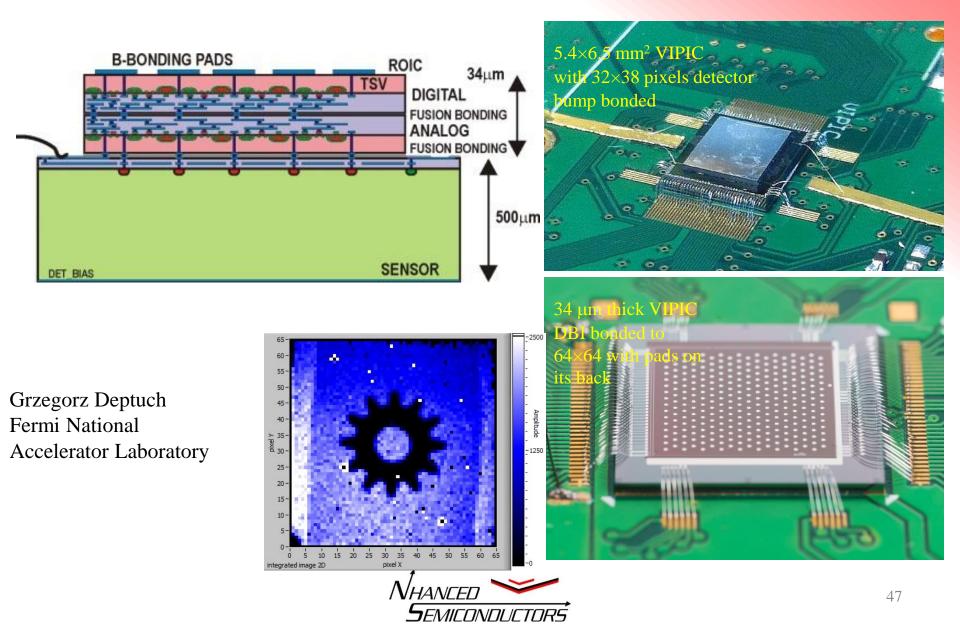

## **Die-on-Wafer and Wafer-scale FPAs**

# **3D ADVANCED PACKAGING**

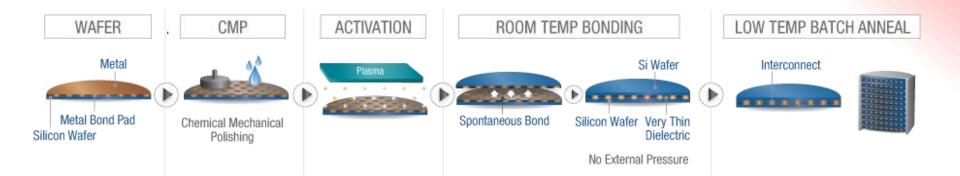

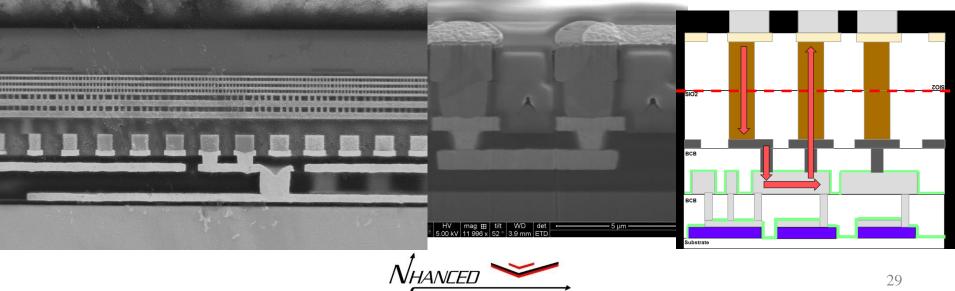

## DBI®: Low Temperature Hybrid Bonding Process

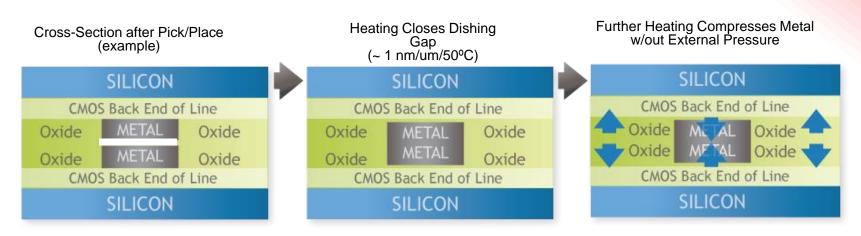

## Hybrid Bonding Internal Thermo-Compression

Electrical Interconnections without External Pressure Minimizes Stress and Cost of Ownership

Spontaneous Chemical Reaction with Byproducts Diffusing Away from Bond Interface

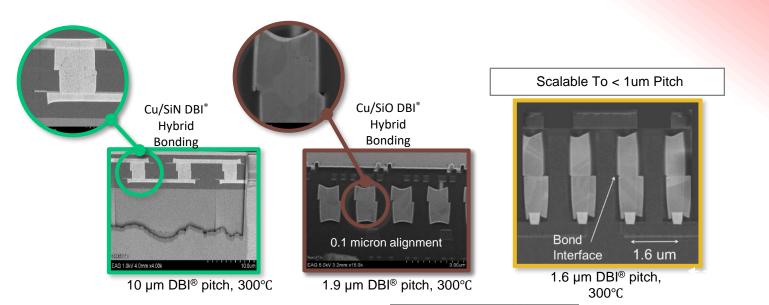

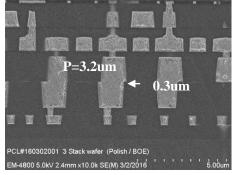

## Hybrid Bonding Interconnect Pitch Scaling

- 3sigma < +/- 1um misalign performance

- Production Minimum pitch = 2.44um

- Best alignment is achieved with face-to-face bonding

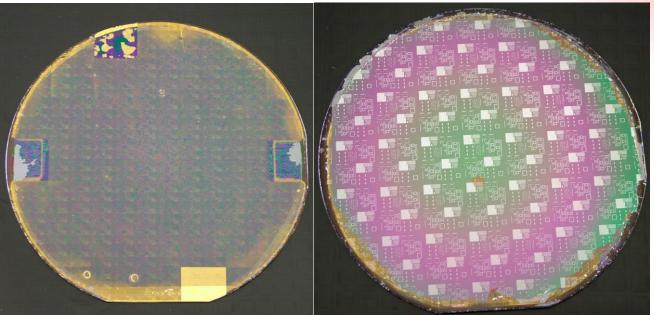

## Wafer-to-Wafer vs. Die-to-Wafer

### • <u>Wafer-to-Wafer</u>

- Process implementable in foundry back end of line (BEOL) with a low cost-of-ownership

- Particle control requirement easily met

- Proven in many applications

- CMOS BSI Image Sensors

- RF switches

- Requires wafer and die sizes to be matched

50um die stacked 4-high, optical and SEM cross-sections

4-high 50um die stacks

4-high cross section Die bond interface

### <u>Die-to Wafer (DBI Ultra)</u>

- Accommodates die tiling, stacking and mismatched die/wafer sizes

- Additional process steps of die singulation and handling required

- Additional particulate/handling challenges

#### Die Stack with DBI® Hybrid Bonding

- Improved performance, cost, and yield/reliability potential

- Throughput no reflow/alloy, throughput improved x2

- Thermals no underfill, ΔT improved x5/10 for 4/8 high stack

- Electrical parasitics DBI<sup>®</sup> replaces bumps, RC improved ~ x20

- Reduced stress eliminate reflow/alloy and underfill

- Reduced pitch pick/place tool limited, throughput dependent

## Mixed Materials – True Heterogenous Integration

- GaN

- 3D CMOS/InP/GaN

- GaAs

- Graphene

SEMICONDUCTORŚ

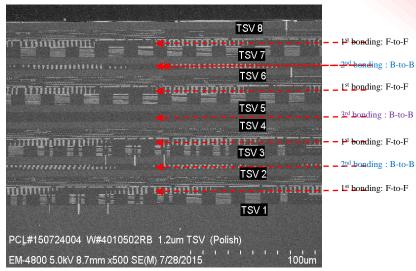

## SiO2 Bonding and Hybrid Bonding for Multi-Wafer Stacking

- 4 wafer stack : SiO2 bonding

- 8 wafer stack : Hybrid bonding

- 16 wafer stack : SiO2 bonding

- 20 wafer stacks : Hybrid bonding

- Currently ~80% of NHanced processed wafers are used for customer "production"

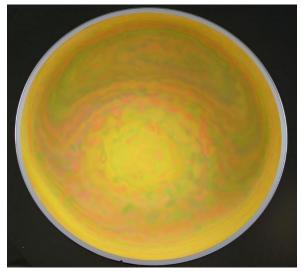

(a) Picture of 4 wafer stack bonded using SiO2 bond Top Si has been removed

(b) SEM cross sectional micrograph for 8 device wafer stack

## **DBI Integration Capabilities and Roadmap**

- Wafer-to-wafer

- 200mm @ 2.4um pitch  $\rightarrow$  300mm @ <1um pitch

- <100nm alignment error</p>

- Die-to-wafer

- 10um pitch  $\rightarrow$  3um pitch

- 8 layers  $\rightarrow$  20+ layers

- Low temperature  $-150C \rightarrow 125C$

- TSV sizes

- 80um to 0.6um

- Up to 12:1 aspect ratio

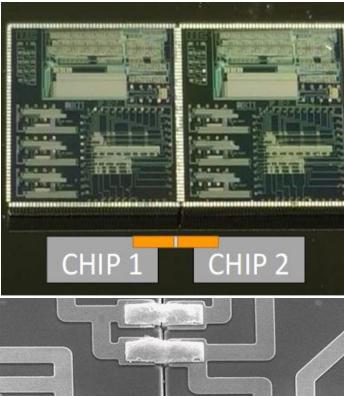

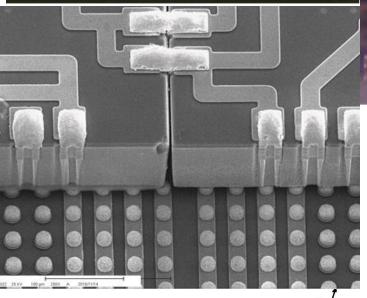

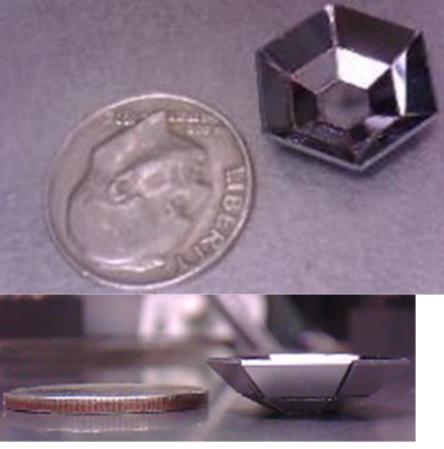

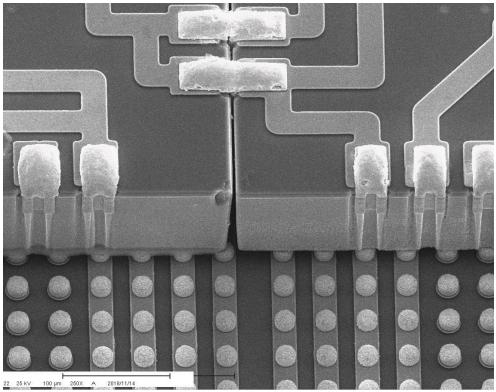

## **Quilt Packaging**

(top left) Quilt Packaging concept cross-section illustration & image of a post-reflowed QP CMOS quilt; (bottom left) SEM image of quilted chip-to-chip seam of >10 micron width; (top right) QP-enabled miniature curved array demonstration article; (bottom right) profile view of QP-enabled miniature curved array.

# 5 mm – 2x1 Quilt, Thermal Compressed – 8 $\mu$ m TSV, 35 $\mu$ m Pitch - Quilt #: NGQ-5-2615-2410

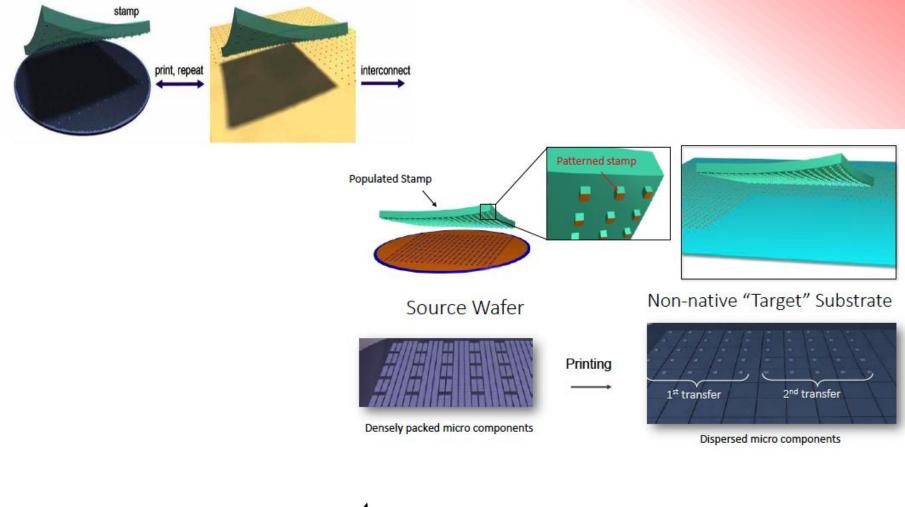

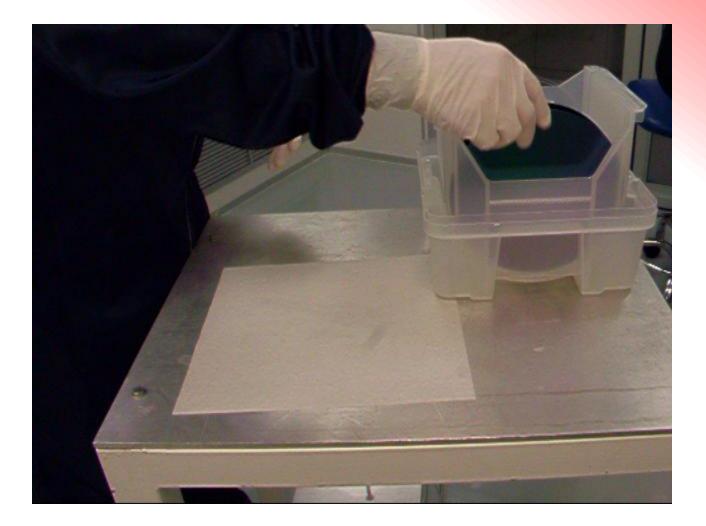

## Transfer Printing µChiplet

## Bonding in Action

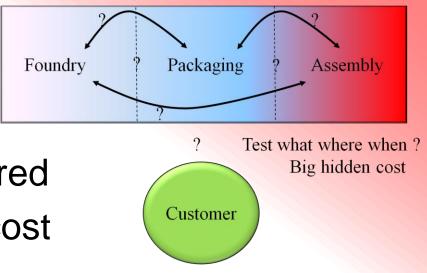

# THE BAD AND THE UGLY

# Supply Chain Complexity

**Chiplet Suppliers Advanced Packaging Manufacturers** 2.5D 3D **Transfer Printing** Quilting Interposer Manufacturers Silicon Glass Organics Bumping **Pillars** Underfill Thermal mitigation New Singulation Needs

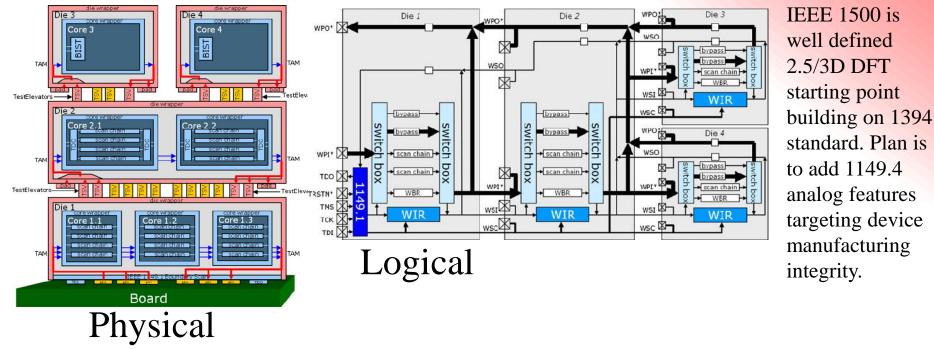

### Addressing Rel/Qual with DFT + 2.5/3D PCM

#### Images from: A DfT Architecture for 3D-SICs Based on a Standardizable Die Wrapper; Erik Jan Marinissen et al

Augmented JTAG based on IEEE 1500: Add alignment sensing, 3D interconnect R/C measurement, power, temperature, perhaps DARPA SHIELD like items... Being work by NEPP task group with others (NRO, AFRL, Honeywell, Tezzaron, Novati,...) Objective is to "prove" specific device quality and improve reliability data.

### Testing

- Significant planning required

- Careful analysis of yield cost

- New methodologies

- High I/O count requires self-test

- Deep embedding requires more effort for visibility

- Self Calibrate / Self-repair / Self-redundancy

- Dynamic Self Adjustment

#### Managing Yield

- Optimizing assembly techniques

- Repair and redundancy

- -- New tools

# The Revolutionary Path Forward FOUNDRY 2.0

#### Foundry 1.0 – Todays Model

- Current semiconductor business has been focused on driving smaller transistors.

- High development cost

- High capital cost

- Long development times

- Expensive design tools

- High risk

- Twilight of Moore's Law

#### Foundry 2.0 – New Model

- System solution focus

- Best of class components

- Relies on Advanced Packaging (AP) and <u>Chiplets</u>

- Heterogenous integration

- Photonics

- MEMS

- RF

- Advantages

- Low development cost

- Low capital cost

- Short development times

- Inexpensive design tools

- Low risk

### Foundry 2.0 Opportunities

- Low capital costs New suppliers

- More than an order of magnitude lower capital costs

- Supports low and medium volume flows High mix fabrication

- R&D, startups, large swath of industry

- More cost effective

- Competition is FPGAs

- 10x to 50x lower component cost

- IP centric

- Knowledge based value

- Complement to Foundry 1.0

- Partnering

- Customers, Capital, Pile-on

# **KILLER APPS!**

#### Applications

- Photonic Computing

- Integrated Photonic based Communication

- Sensors

- Memory Rich Processing

- RF and Power

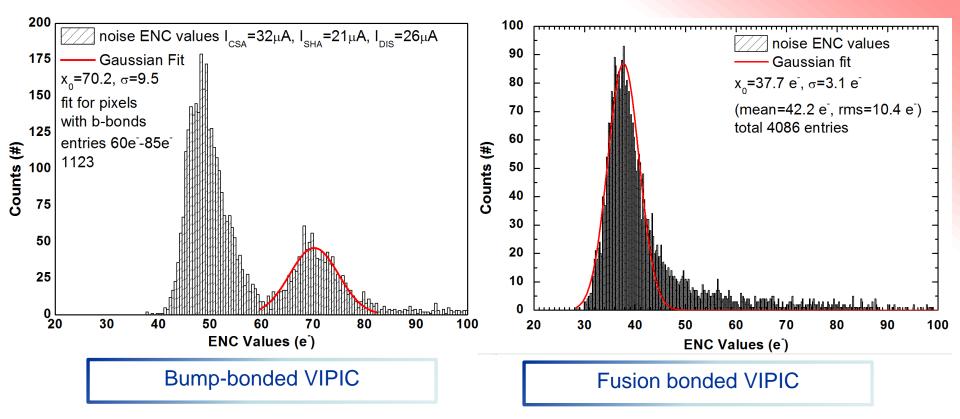

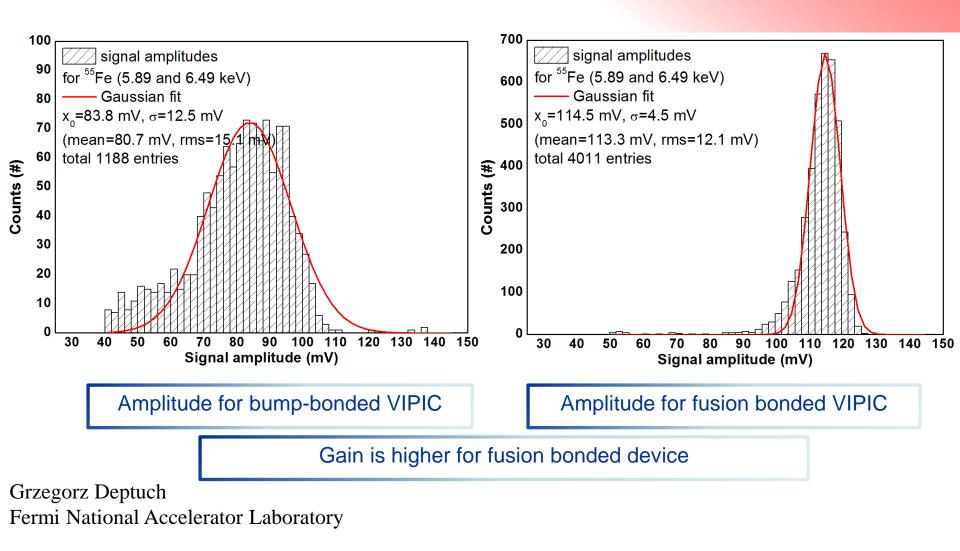

#### **Fusion Versus Bump Bonding**

#### ENC comparison: Bump vs. fusion bond

Grzegorz Deptuch Fermi National Accelerator Laboratory

#### Signal amplitude comparison: Bump vs. fusion bond

# Future is Foundry 2.0

- Lower Costs / Higher Performance

- Manufacturing

- Development

- Better Yields

- Mixed Technologies

- Mixed Materials

- New design approaches New opportunities

- Advanced Packaging

- 2.5D

- Interposers

- Glass, Silicon, ?

- 3D

- Quilting

- Transfer Printing