### Free Running DAQ for COMPASS++/AMBER

#### Igor Konorov

Institute for Hadronic Structure and Fundamental Symmetries (E18)

**TUM Department of Physics**

Technical University of Munich

COMPASS FETDAQ Workshop

CERN, March 2-3

Uhrenturm der TVM

# Physics programs and Free Running DAQ

Proton-radius measurement using elastic muon-proton scattering

Drell-Yan and charmonium production using hadron beams

Measurement of antiproton production cross sections for dark matter search

Why we choosed free running DAQ architecture?

- Flexible solution

- Combination of slow and fast detectors: TPC and others

- High quality trigger algorithm

- Recoil-proton in TPC

- Kink trigger with very low angular resolution using SciFi/Silicon detectors

- "Unlimited" time for trigger decision

- High data rate capable DAQ

- Inexpensive with current technologies

# Free Running iFDAQ

#### From 2022 Det

#### Free running DAQ ?

- Capability to run without any data reduction

- Not efficient to store all data => data reduction needed

- Triggerless FE electronics !!!

#### **Triggerless mode**

- Alignment

- Hardware trigger verification

- Pilot run

#### Triggered mode

- HW trigger mutually exclusive with HLT

- HLT complementary to HW trigger

#### Tasks

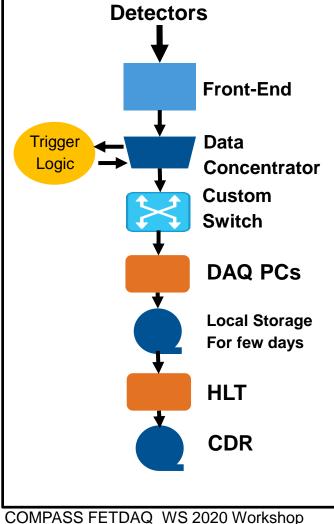

Concept of free running system ٠ Data Structure, System architecture - OK Front-end electronics MSADC, iFTDC, MuPix/Alpide, SISxx, VMM(?), TIGER(?) - only iFTDCs exist Feature extraction, data compression for ECAL - work started Fast MSADC readout DAQ firmware development ٠ DHmx, DHsw, Spill Buffer - new Spill buffer **TCS** Controller - work in progress DAQ hardware Kintex7 Ultrascale card - prototype produced Trigger processor Hodoscope trigger - work in progress Kink trigger - no man power **DAQ** Software - OK Software optimization to achieve maximum performance 1GB/s/PC New Frame Work for Analysis software being discussed

# Free Running DAQ Data Structure

COMPASS FETDAQ\_WS 2020 Workshop

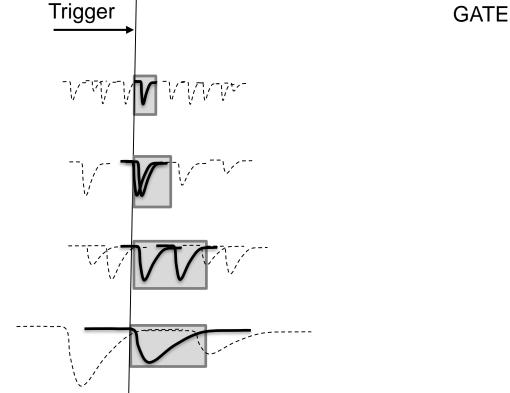

### Data Structure of Standard Triggered DAQ

SciFi GATE 20 ns Si, MM, GEM GATE 50 ns Drift Chambers GATE 400 ns RICH MWPC GATE 400 ns

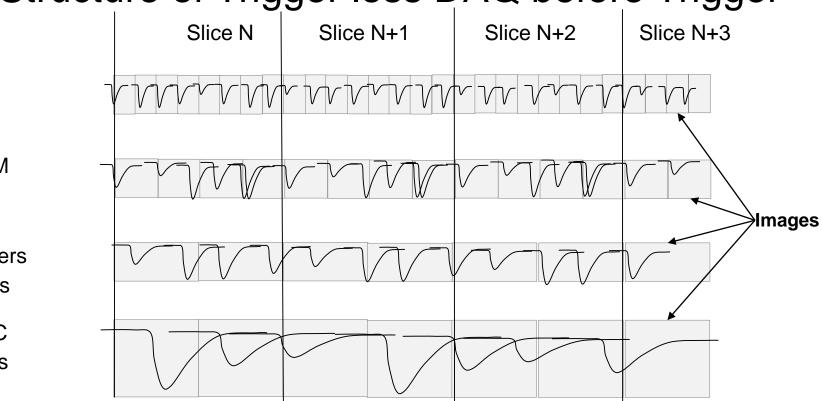

# Data Structure of Trigger less DAQ before Trigger

SciFi GATE 25 ns

Si, MM, GEM GATE 50 ns

Drift Chambers GATE 400 ns

RICH MWPC GATE 400 ns

Image length optimized to minimize overhead and > 2 GATEs Example :

- 1. TPC drift time 60 us, TPC Image = 120 us

- 2. SciFi time resolution <0.5 ns, SciFi Image = 100 ns

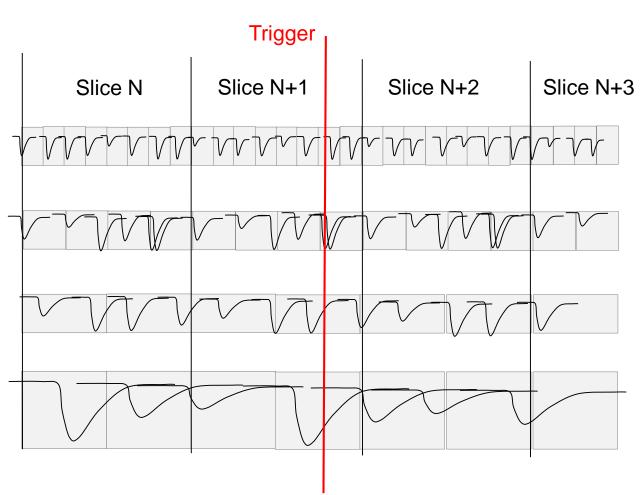

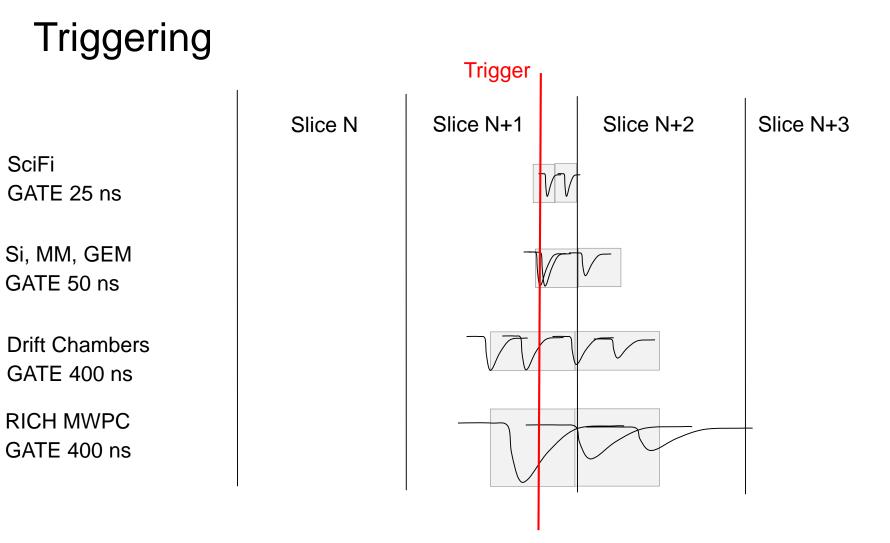

### Triggering

SciFi GATE 25 ns

Si, MM, GEM GATE 50 ns

Drift Chambers GATE 400 ns

RICH MWPC GATE 400 ns

Two consecutive sub-slices are included in the event

## ТЛП

## **Event Building Process**

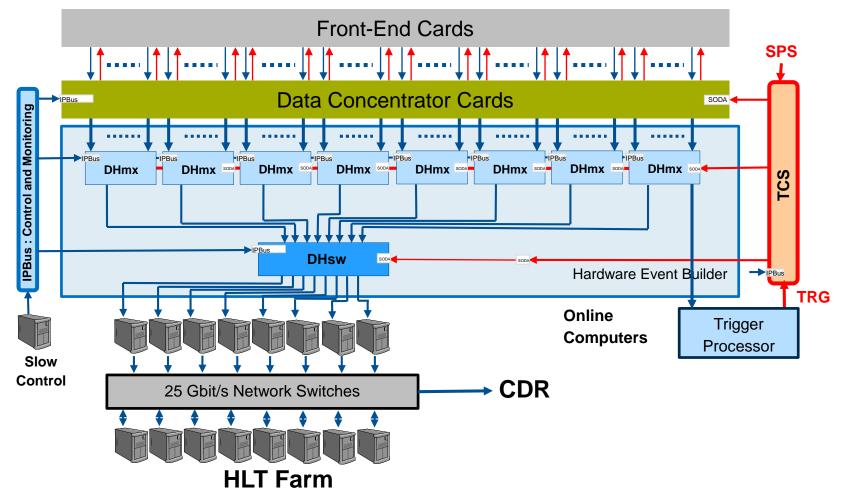

#### FEE

- Time sorted hits packed to IMAGEs

- DHmx first level

- Data buffering

- Organize hits plane wise

- Merging IMAGEs belonging to one detector plane to new IMAGE

- Hits with IMAGE placed chronologically

- DHmx second level

- Data buffering

- Merging SLICEs: Multiplexing IMAGES in chronological manner, IMAGEs keep format

#### DHsw

- Multiplexing SLICEs with identical TIME TAG to single Servers

- Round Robin distribution of SLICEs between Servers

#### Spill Buffer

- Data buffering

- DMA to Server memory

#### ТШ

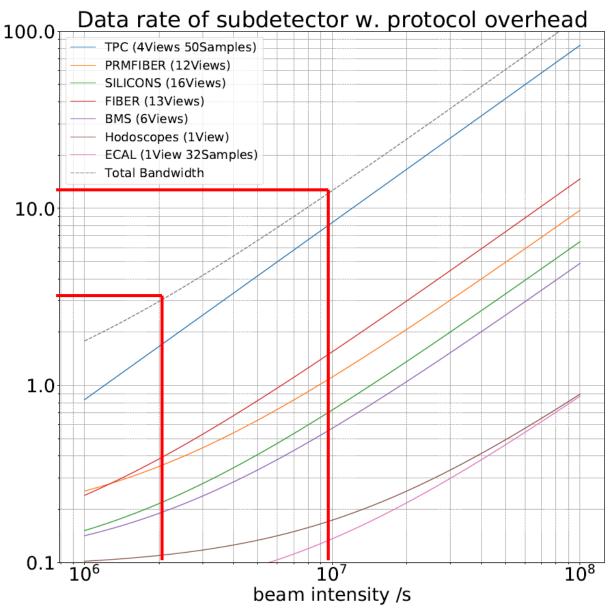

### Data Rates wo Trigger

In spill :

Beam 2  $10^6 \Rightarrow 3GB/s$ Beam  $10^7 \Rightarrow 10GB/s$

Sustained data rate: Beam 2  $10^6 \Rightarrow 1 GB/s$ Beam  $10^7 \Rightarrow 3 GB/s$  Data Rate GB/s

### Example of Detectors' Readout for PRM

```

PRM SciFi (4500 channels), 0.35-1GB/s

FE: NINO=>70x iFTDC(A7) => 6 x DHmx(V6) => 2x DHmx(V6) => Switch P0,1

SciFi (800 channels), 0.4-1.5 GB/s

FE: NINO=> 30x iFTDC(A7) => 3x DHmx(V6) => 2x DHmx(V6) => Switch P 2,3

H5 (64 channels),

0.1-0.2 GB/s

FE: NINO=> 2x iFTDC(A7) => DHmx(V6) => shared

BMS (512 channels), 0.2-0.6 GB/s

FE: NINO=> 16xiFTDC(A7) => 2 \times DHmx(V6) => 1 \times DHmx(V6) => Switch P 4

PixSil (256 HS links), 0.2-0.7 GB/s

MuPix/Alpide => 32xFE(K7) => 3 \times DHmx

=> 1x DHmx(V6) => Switch P 5

TPC.

1.7-8GB/s (no zero suppression)?

S|Sxx => ?

=> Switch P 6, 7

ECAL (100 channels),

0.05-0.15GB/s

MSADC => ??

=> DHmx(V6) => shared

GEM

```

??

### iFDAQ Architecture

### ТШП

### Challenges of Free Running DAQ

- High data rate capability

- 4 GB/s with V6 switch

- 30 GB/s with Kintex 7 switch

- Provision of online alignment for triggering or HLT

- Developing trigger algorithms and trigger emulation

- Analysis software for new data format

# THANK YOU

COMPASS FETDAQ\_WS 2020 Workshop