# New PCIe spillbuffer

#### Stefan Huber

Institute for Hadronic Structure and Fundamental Symmetries (E18)

Department of Physics

Technical University of Munich

COMPASS DAQ Workshop 03.03.2020

# Spillbuffer card

- Nereid Kintex 7 PCI Express (1k €)

- Trenz FMC SFP adapter (160 €)

- Kintex 7 XC7K160T FBG676

- 4x PCIe-Gen2 up to 2GByte/s

- 2GB DDR3 memory

- Only 6 Gbit/s per SFP

- No dedicated TCS interface

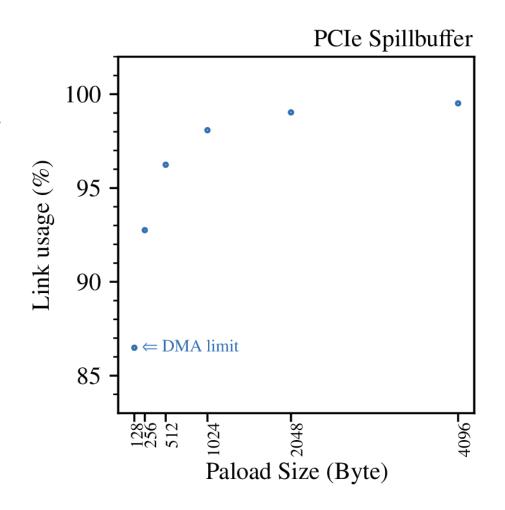

#### Basic performance limitation of PCIe

- Data is transferred via in packets with limited sizes

- 20 Bytes are used by header and trailers

=> significant overhead

- For DMA transfers, additional limit:

- Payload limited to 128 Bytes by chipset

- Better on other chipsets?

- Theoretical maximum transfer rate:

- 860 Mbyte/s PCIe Gen-1

- 1720 Mbyte/s PCIe Gen-2

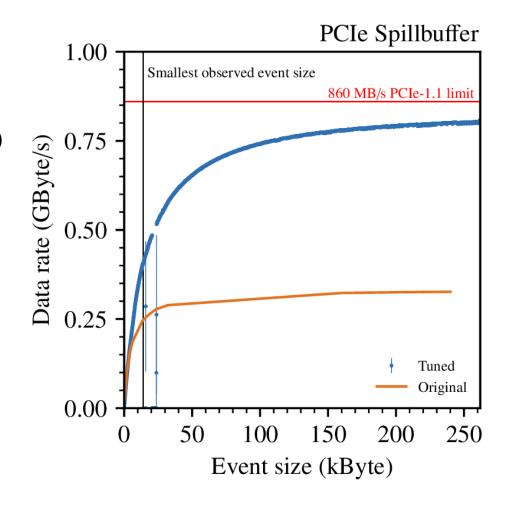

### Performance improvements in firmware

- Started with firmware of the old Virtex-5

- Test conditions:

- Internal generator (4byte 250 MHz) (continuously running)

- Data stored to '/dev/null'

- Host: PCle Gen 1.1

- State machines not optimized

- Performance improvement ~ factor 3

- Maximum data rate for big events:

794 Mbyte/s

- Tested with simplified driver only 10 Mbyte/s improvement

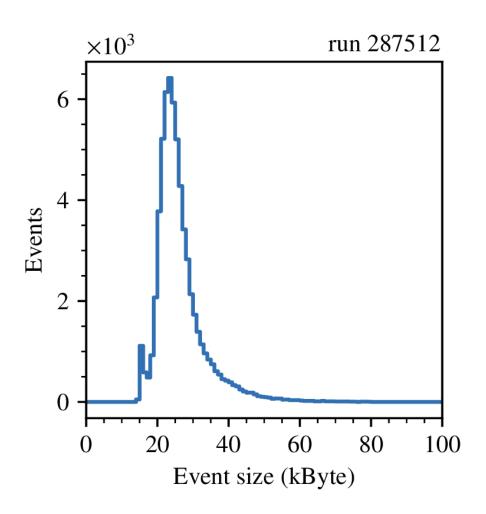

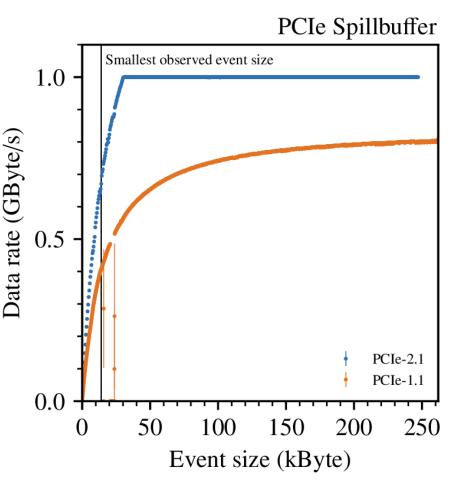

### Impact of the event size on the performance

- Interrupt for each event

- Indicates event boundaries to the computer

- 4Mbyte memory blocks allocated

- Check if these blocks are full

- Switching between the blocks

- New memory address transferred to FPGA

- Takes around 17us/event (PCIe Gen-1)

- Minimum event sizes 14kByte

- ~50% of maximum performance reached for these events

- Smaller setups => Smaller events

- PRM

- Test measurements

- May have significant impact

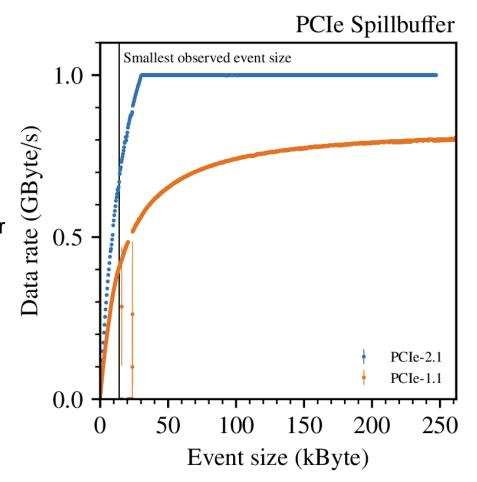

#### Tests with PCIe Gen2

- Test conditions:

- Internal generator (4byte 250 MHz) (continuously running)

- Upsizer 4byte -> 8 byte

- Data stored to '/dev/null'

- Host: PCIe Gen 2.1

- Host: PCle Gen 2.1

Generator limited to 1Gbyte/s

Upsizer needed in order to run the DMA at the maximum speed

1Gbyte/s reached at event sizes of 29kByte Q

- Interrupt handling ~13us/event

#### Outlook

- Change generator to go above 1Gbyte/s

- Test with external data source (Aurora)

- Test at COMPASSS

- Different payload sizes possible?

- Write memory interface for new EB logic (See talk by Dmytro Levit)

- TCS interface via SFP

- Event checks

- Merge several small events in one transfer

- Create UCF interface for Kintex7