# Studies for CLICTD resubmission with HR Czochralski substrate

M. Munker, 27.03.2020

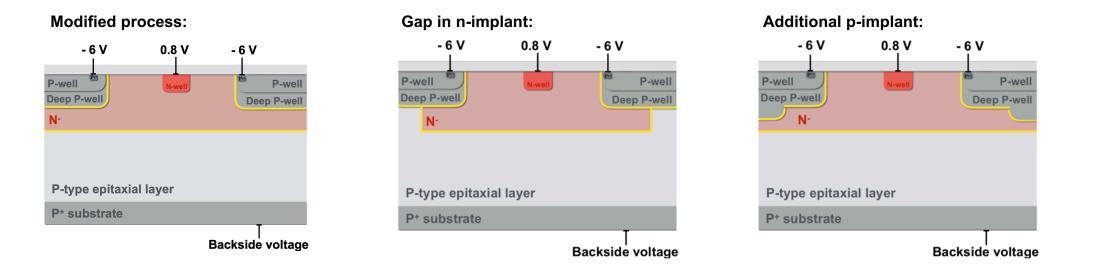

# Investigated technology & new pixel designs

#### <u>CLICTD - a fully integrated small collection electrode</u> <u>CMOS chip for the CLIC tracker:</u>

- 180nm modified CMOS imaging process

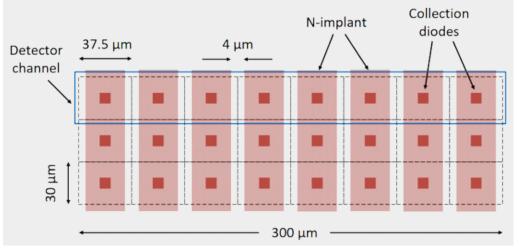

- 30µm x 37.5µm pixel size

- Implemented on epitaxial layer of 30µm

- 8 pixels combined in common digital channel

## Why to use new pixel designs for CLICTD?

#### **Faster charge collection:**

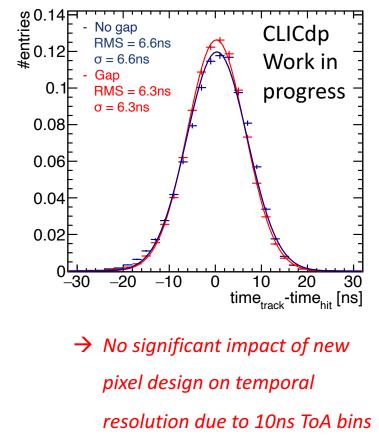

$\rightarrow$  Impact on CLICTD measured performance limited by 10ns ToA bins

#### Less charge sharing:

$\rightarrow$  Less in-channel charge sharing

→ Beneficiary for precision with channel concept, especially at angled tracks (to be confirmed)

#### $\rightarrow$ Larger seed signal:

$\rightarrow$  Higher radiation tolerance (not relevant for CLIC)

$\rightarrow$  Larger efficient operation window  $\rightarrow$  this talk

#### Temporal residual distribution:

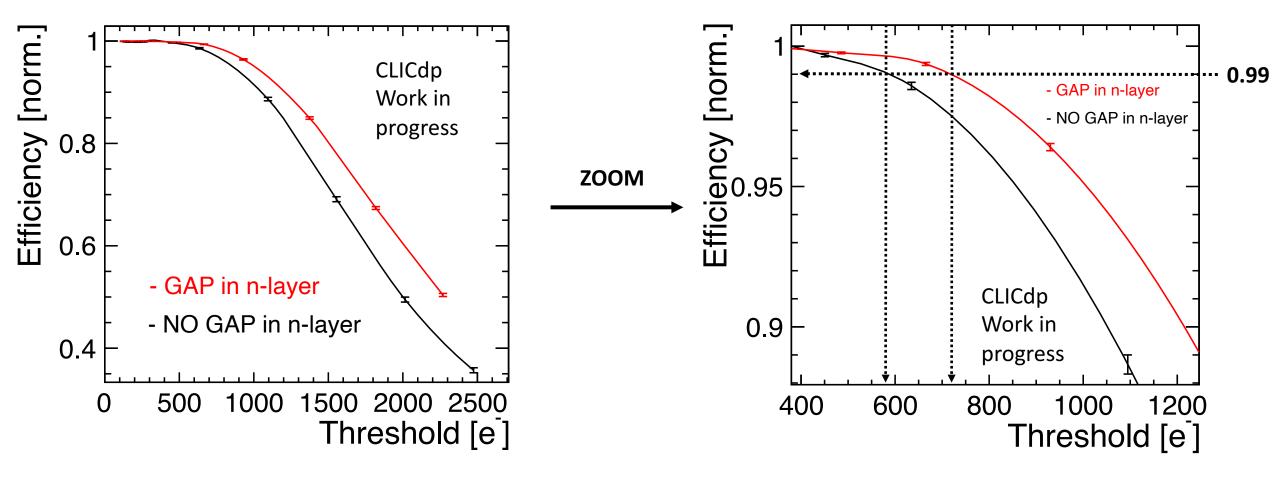

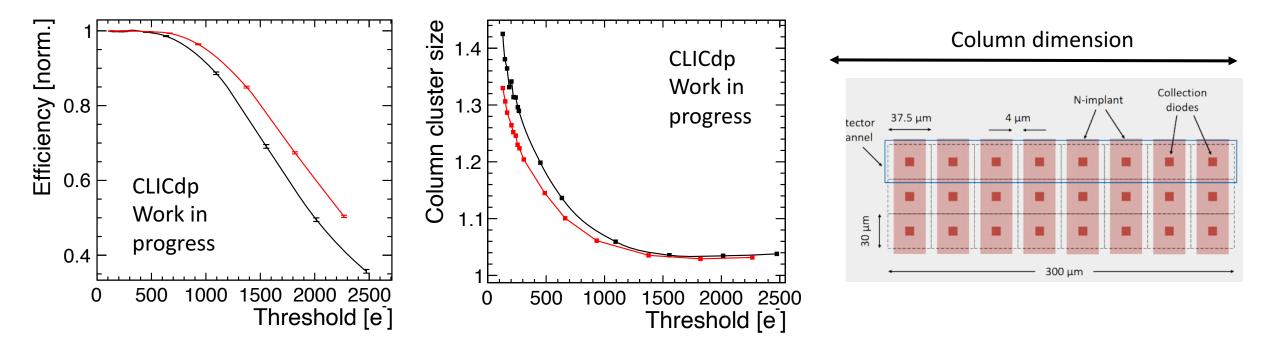

### Efficiency for different pixel designs

Data from December 2019 test-beam, bias p-well/substrate -6V/-6V

Gap in n-layer extends efficient operation window significantly to higher thresholds.

For efficiency of 0.99, the threshold range is extended by ~150e- (~25%).

### Efficiency & cluster size for different pixel designs

Bias p-well/substrate -6V/-6V

Gain in efficient operation window correlated with reduced cluster size in column dimension.

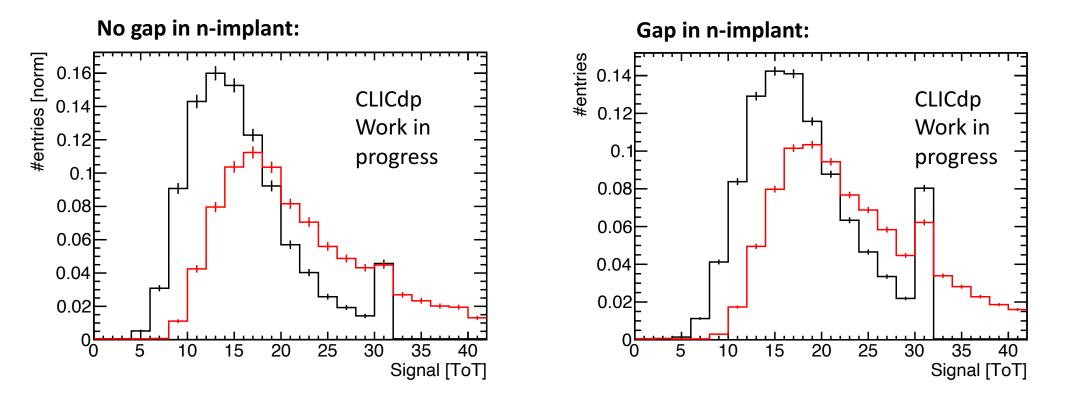

### Seed & cluster signal for different pixel designs

Threshold ~150electrons, bias p-well/substrate -6V/-6V

<u>Note</u>: no ToT calibration!  $\rightarrow$  no direct comparison between seed signal distributions of different pixel designs <u>However</u>: difference between seed & cluster signal corresponds to gain in efficiency due to reduced charge sharing

## Cz submission – process splits for CLICTD

- Submission of MALTA on Cz wafers → thicker active layer

- Difference to CLICTD submission  $\rightarrow$  higher n-implant dose (radiation hardness)

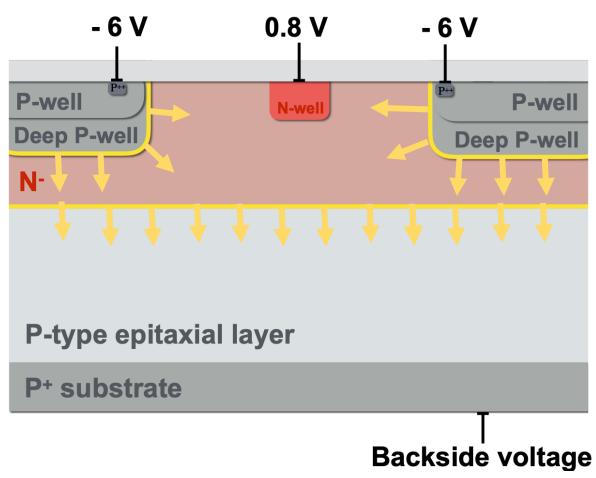

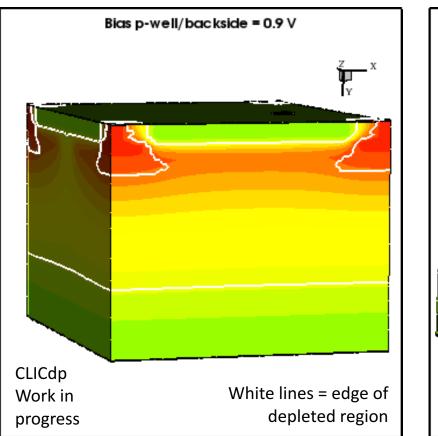

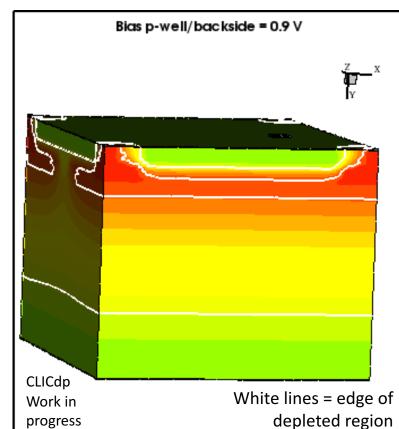

#### **Evolvement of depleted region:**

### Depletion grows from junctions (yellow lines) into lower doped regions:

- $\rightarrow$  From p-wells, depletion grows into n-layer

- → Direct impact on depletion around collection electrode and sensor capacitance

- → From deep planar junction, depletion grows mainly in epi

- → Less impact on depletion around collection electrode and sensor capacitance (see later slides)

- Do we want to pay for an extra split to get the lower n-implant dose?

How much does the higher n-implant dose increase the capacitance?

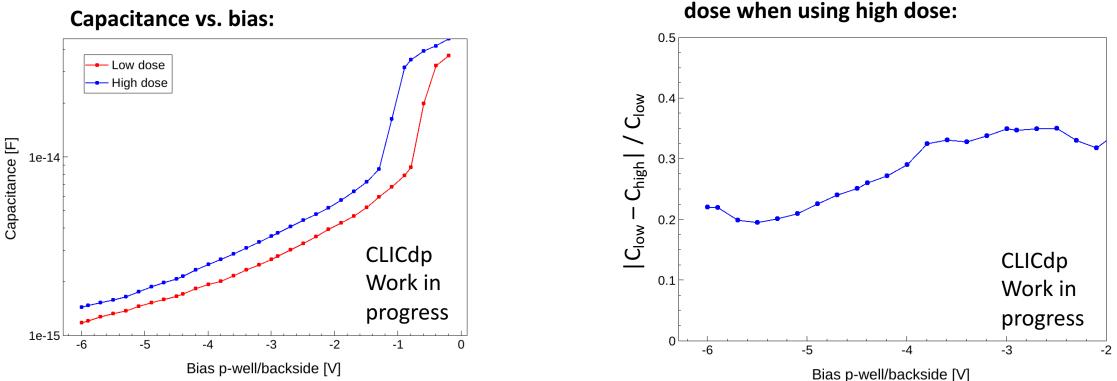

### Capacitance simulation – CLICTD different nimplant dose

Increase of capacitance w.r.t. low

**Capacitance vs. bias:**

$C_{low} - C_{high} / C_{low}$  = Increase of capacitance w.r.t. low dose when using high dose

$\rightarrow$  Capacitance increases by ~20% when using the high instead of low dose (for CLICTD design)

# Depletion for different n-implant doses at different bias

**Color scale = visualization of electrostatic potential**

Low dose:

#### High dose:

- Different slopes due to depletion under p-wells and depletion in p-well opening

- Very low bias: gap in n-layer isolates single pixel channels

- More depletion around collection electrode for low dose

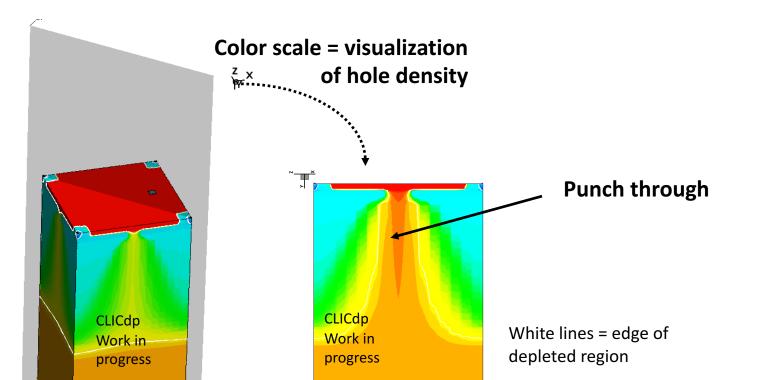

### Czochralski punch-through simulations

Czochralski simulation setup for MALTA design with gap in n-layer:

• Pixel size 36.5µm x 36.5µm, backside bias -20V, p-well bias -6V, no backside implantation

Punch through = current flow between p-well and backside if both are on different potential

• Czochralski: need higher backside voltage for depletion

CLICdp Work in progress White lines = edge of depleted region

p. 9

**Electrostatic potential:**

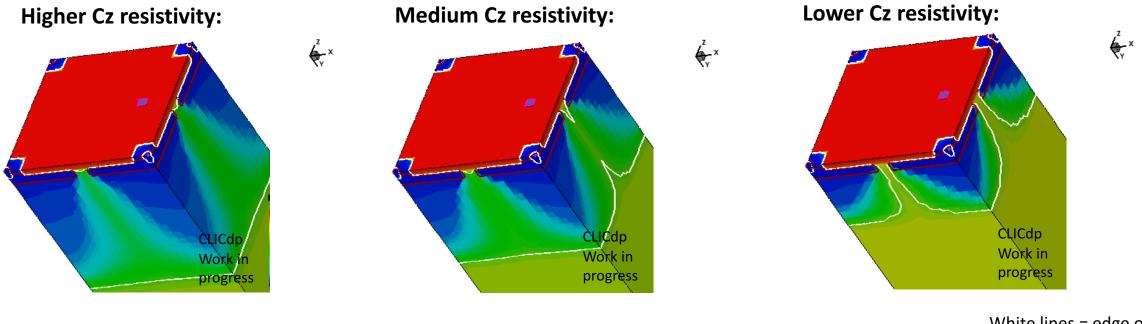

### Dependence of punch through on Cz resistivity

Bias p-well = -6V, bias backside = -20V, gap in n-layer

**Color scale = visualization of hole density**

White lines = edge of depleted region

ightarrow Strong dependence of punch through on Cz resistivity

$\rightarrow$  Better performance of lower Cz doping level due to larger depleted region  $\rightarrow$  better isolation of p-wells & larger signal

ightarrow Careful tuning of simulations

### Czochralski punch-through simulations

Bias p-well = -6V, gap in n-layer

#### MALTA matrix size, T = 2.2 degrees: from P. Freeman (ATLAS): Punch-Through Current [mA] 0.0014 CLICdp W9R11Cz, T = - 11.2 °C 0.0012 Work in 1.2W9R11Cz, T =2.2 °C progress current [A] 0.001 0.8 0.0008 0.6 0.0006 Backside 0.4 0.0004 0.2 0.0002 9.5 10 7.5 8 8.5 9

#### Measurements MALTA,

Simulations of single pixel cell scaled by

8

Backside voltage [V]

9

10

- Simulations similar order of magnitude compared to measurements

- Don't expect perfect agreement since e.g. edge effects are not simulated

SUB [V]

Note: no punch through for pixel design with no gap in n-layer due to better isolation of p-wells

CLICTD test beam measurements show significant gain in efficient operation window when using gap in n-layer

**CLICTD** capacitance C<sub>CLICTD</sub> for higher n-implant dose:

- **C**<sub>CLICTD</sub> ~20% higher for higher for higher compared to lower n-implant dose:

```

C<sub>CLICTD</sub> ~ noise

C<sub>CLICTD</sub> ~ 1/signal

Signal/noise ~ 1/ C<sub>CLICTD</sub><sup>2</sup>

```

$\rightarrow$  BUT: compensated by higher signal for Cz compared to epi!

#### **Capacitance & punch-through:**

- Very relevant parameters for small collection electrode CMOS ٠

- Only accessible with finite element simulations •

- Complex dependence on other design parameters •

### Next steps

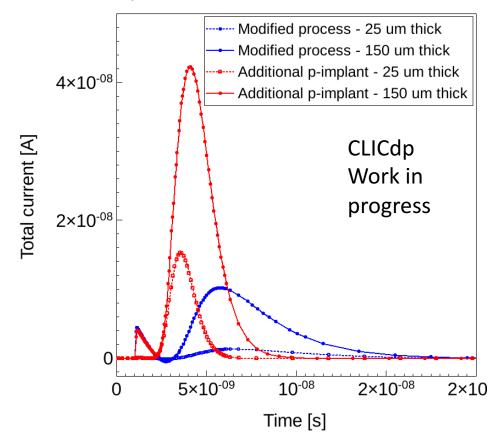

#### **Transient simulation for Cz:**

- What is the impact of the punch through current on the collected charge?

- What is the gain in signal when using epi instead of Cz?

- Do the process modifications still help for thick Cz sensor?

### Transient simulation for different epi thickness:

# BACKUP