Front-End Board Version 1 or Version 2 ?? 23<sup>rd</sup> Jan 2020 Mark McLean

### Introduction

- V2 Front-End Board for the SEM Beam Position Monitors was developed with the aim of improving SNR and few other minor tweaks.

- Unfortunately it was not a clear improvement.

- First problem was a 250kHz signal around 100 bits in amplitude. This was traced to an oscillating power regulator and fixed.

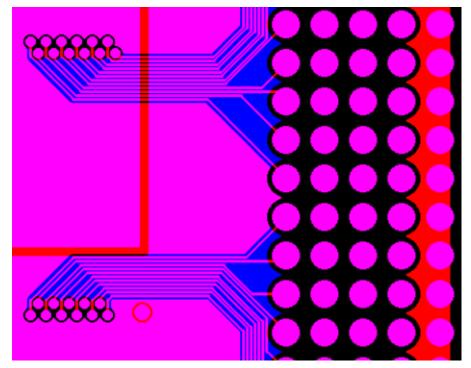

- Second problem was an additional sensitivity to noise from the power supply. This was traced to the ASIC signal tracks being routed across a power plane.

- Beam sensitivity of both boards has been shown to be similar. 10<sup>6</sup>

H<sup>-</sup> ions gives a response of around 150 bits.

#### Plan

- To combine the best features of V1 and V2 into a new V3 board. Changes from V1 will be minimal, to minimize risk.

- This board will be designed and manufactured in-house, we are meeting the Electronics Design Office tomorrow.

- Hoping that they will do the work of drawing V1 in the CERN supported software package (Altium). Then I will make some further changes in line with what we have learnt from V2. Design complete end February.

#### Plan

- In March get a small number (how many?) of V3 boards manufactured by CERN or CERN controlled sub-contractors.

- Test on the bench in April, if no problems then commence volume manufacture of the bare PCBs (approx. 80).

- Test with beam in May, if no problems then populate the 80 PCBs with components and bond ASICs.

- This would give us the boards for the complete installation by end of June.

#### Other issues – Back-End Boards

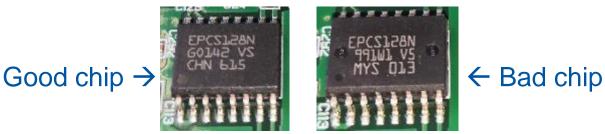

Many (20 out of 43) Back-End Boards cannot be programmed. They have a visibly different memory chip fitted.

- I will obtain some alternative devices and test them.

- The Back-End boards also have the same oscillating regulator that caused problems with the Front-End boards, so I will have those changed too.

#### Other issues – In-Out Boards

- The In-Out Board prototypes are not yet populated.

- Masaki will hand them over to me and I will sort it out...

# **Grid inspection**

- The GBar SEM and the SEM from the source have been removed.

- The GBar SEM had just one missing wire, as expected

- The source SEM has several broken wires

- The units are currently with Radio-Protection

- After that we will be able to inspect fully

- Masaki asks that we provide an updated requirement for the number of grids that we need. We said we would do this after the grid survey, by the end of February.

### Thank you – The End

Following slides are spares in case of questions

# Changes from V1

- Changes needed to V1 are:

- Change the oscillating regulator to LT1962EMS8-5

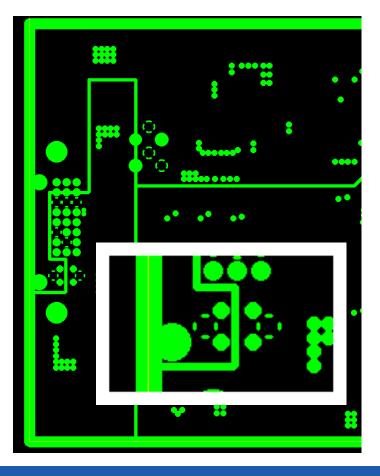

- Remove the GNDIO-AGND connection but add a link

- Remove the trimmer

- Make the LEDs different colours

- R43 = 309R

- C312 = 10k resistor

- R80 = 1k

- Q1 and Q2 replaced with BCM847

- Ensure LT1964BYP used

- Make provision to connect the ASIC pad to -2V

# **Oscillating regulators**

- V1 had an error which caused AGND and GNDIO to be connected. This made more capacitance available to the regulator and reduced the amount of noise at the power input connector.

- Thus the amplitude of the noise spread to the rest of the board was reduced in V1, and the problem was not noticeable.

# Oscillating regulators

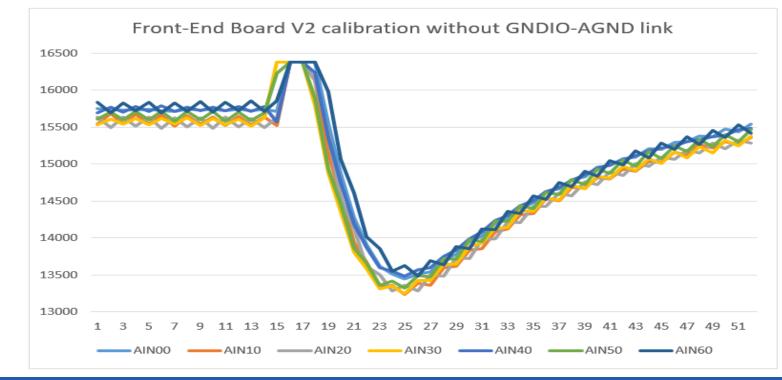

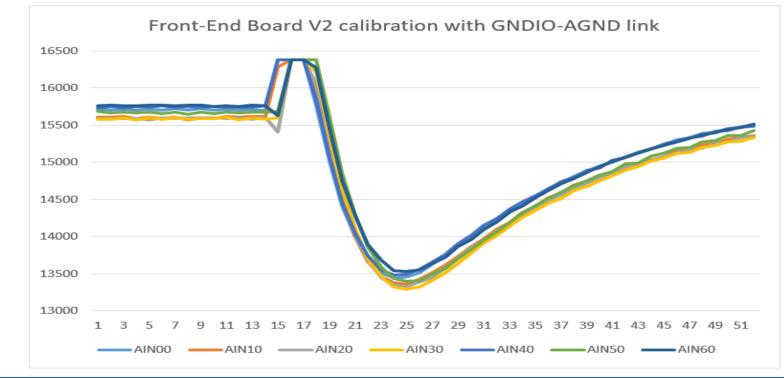

Calibration waveforms

### **Oscillating regulators**

Calibration waveforms

1/23/2020

# Nature of remaining noise

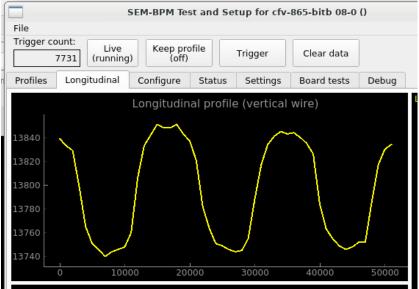

The big clue came from comparing the amplitude of the signal from different inputs, particularly while the cleaner was using a vacuum cleaner nearby!

SEM-BPM Test and Setup for cfv-865-bitb 08-0 0

| Input | PCB Layer | Noise amplitude |

|-------|-----------|-----------------|

| AIN01 | Un-bonded | <10 bits        |

| AIN20 | Layer 1   | 20 bits         |

| AIN21 | Layer 10  | 100 bits        |

| AIN35 | Layer 10  | 100 bits        |

| AIN36 | Layer 1   | 30 bits         |

| AIN58 | Un-bonded | <10 bits        |

# Nature of remaining noise

- It turns out that in V1, all the signal tracks were on the top or bottom layers of the board and were adjacent to a ground plane.

- But in V2, half the signal tracks are on a buried layer and the adjacent layer is a power plane.