# A novel SOI pixel detector with depleted substrate

M. Battaglia<sup>1,2,3</sup>, D. Bisello<sup>3</sup>, D. Contarato<sup>2</sup>, P. Denes<sup>2</sup>, P. Giubilato<sup>1,3,4</sup>, S. Mattiazzo<sup>3</sup>, D. Pantano<sup>3</sup>, N. Pozzobon<sup>3</sup>, S. Zalusky<sup>1,4</sup>

<sup>1</sup>University of California at Santa Cruz, Santa Cruz, CA, USA

<sup>2</sup>Lawrence Berkeley National Laboratory, Berkeley, CA, USA

<sup>3</sup>University of Padova & INFN Padova, Padova, IT, EU

<sup>4</sup>CERN, Geneva, CH

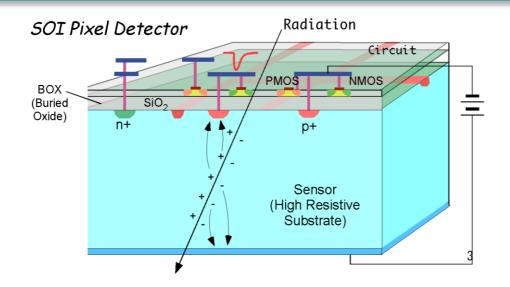

#### Some SOI basics

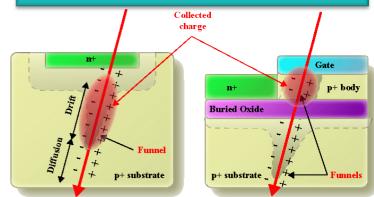

- SOI technology integrates CMOS electronics on top of a Buried Oxide (SOI), ensuring full dielectric isolation, small active volume and low junction capacitance: latch-up immune, low power, high speed designs are thus favoured

- 0.15-0.20  $\mu$ m Fully-Depleted (FD) SOI processes from OKI, Japan allow contacting a high-resistivity (700  $\Omega$ /cm) substrate through the BOX for pixel implanting and substrate reverse bias

- Possibility for small pitch pixel sensors with high density, full CMOS readout electronics integrated in the same device -> SOI Monolithic Pixel Sensors

40 nm silicon layer isolated from the bulk by the SiO<sub>2</sub> layer -> No PNPN parasitic structs.

Small charge generation into the active area of the transistor, lower sensitivity to SEE.

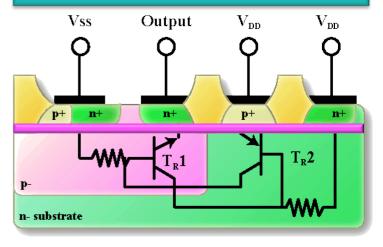

#### OKI SOI process

#### OKI 0.15 μm SOI process

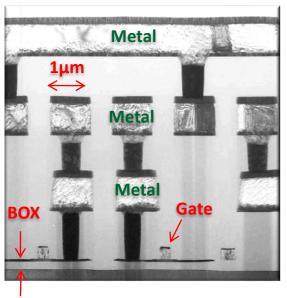

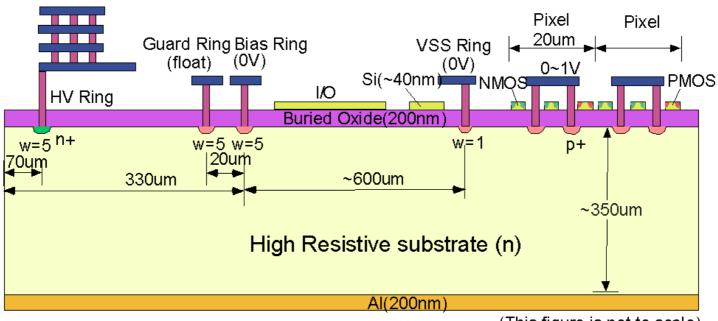

Process: OKI 0.15μm fully-depleted SOI CMOS process, 1 Poly, 5 Metal

Wafer Diameter: 150 mm, Buried Oxide: 200 nm thick

Top Si : Cz, ~18  $\Omega$ -cm, p-type, Handle wafer: Cz 700  $\Omega$ -cm, 650 wafer:

40 nm thick fully depleted µm thick (SOITEC ion cut)

Backside: Thinned to 350 μm, plated with Al (200 nm).

(This figure is not to scale)

#### SOI 1

# **Analog pixels Digital pixels**

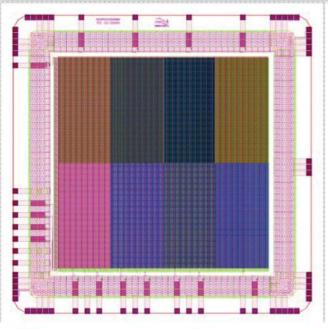

# SOI Imager 1

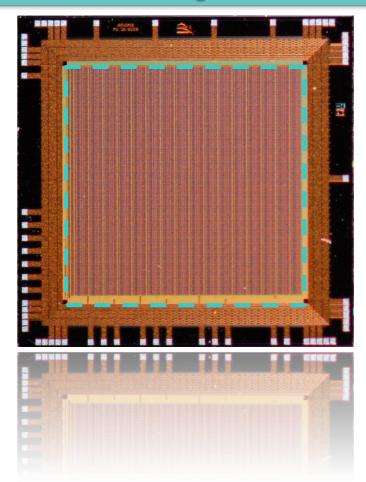

- OKI 0.20 μm FD-SOI process, 5x5 mm<sup>2</sup> area, 256x256 analog pixels, 13.75 μm pitch

- 4 parallel analog outputs, readout up to 50 MHz, 2-3 kframes/s

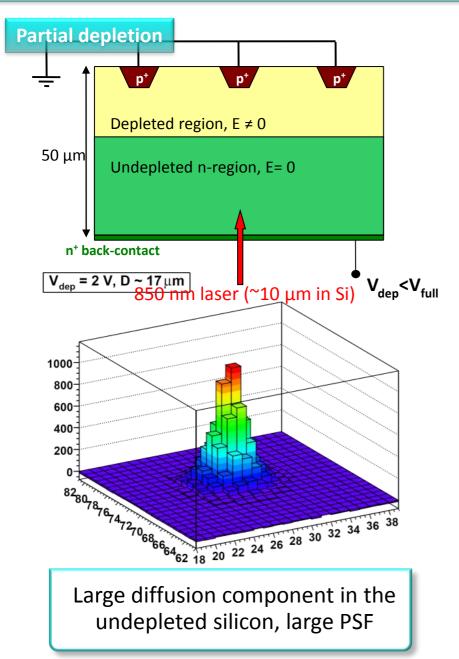

# Charge diffusion measurements with 850 nm laser on a thinned chip

Charge collection dominated by drift, smaller PSF and faster collection time

# Back-gating effect on both SOI and SOI imager chip

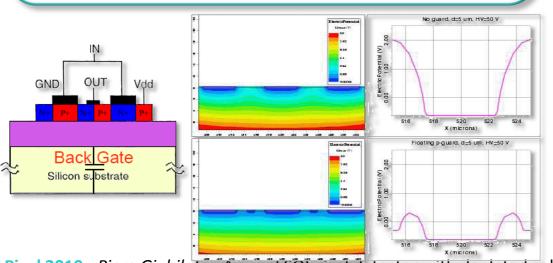

$V_{DD} = 1.8 \text{ V}$

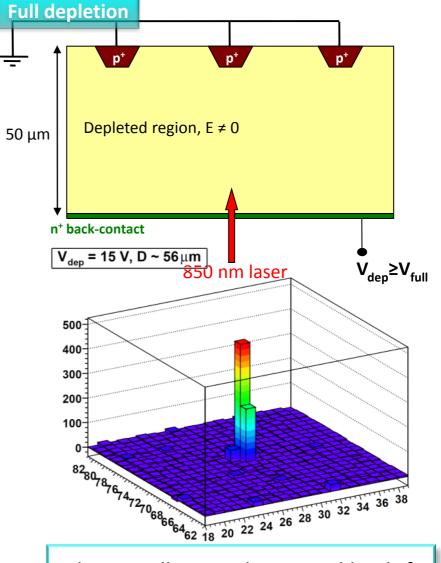

- The high field in the depleted substrate causes back-gating of the CMOS electronics on top of the BOX

- Test of single transistors vs. depletion voltage: shift in the threshold voltage with increasing substrate voltage

- Significant effect observed in single transistor tests: expect analog section functional only for  $V_{dep} < 20 V$

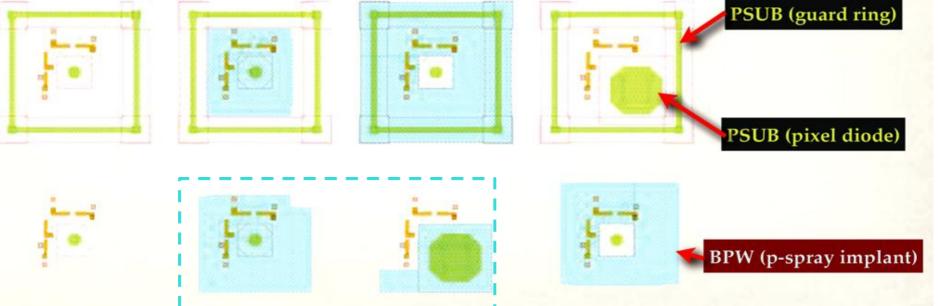

- Floating pguard structures around each pixel to keep potential low and limit back-gate effects on **MOSFETs**

Pixel 2010 - Piero Giubilato - A novel SOI pixel detector with depleted substrate

# SOI Imager 2

- Improved version specifically designed to survive back-gating

- OKI 0.20 μm FD-SOI process, 5x5 mm<sup>2</sup> area, 256x256 analog 3T pixels, 13.75 μm pitch, 1.8 V operation, 8 different pixel flavours

- R&D version of 2009 LDRD-SOI-Imager prototype, exploring different pixel layouts and use of light p-doped implant (Buried P Well, BPW) vs pixel guard-ring (See Y. Arai talk).

- Is the BPW effective in containing back-gating?

- Can we avoid the floating guard-ring around the pixel (space)?

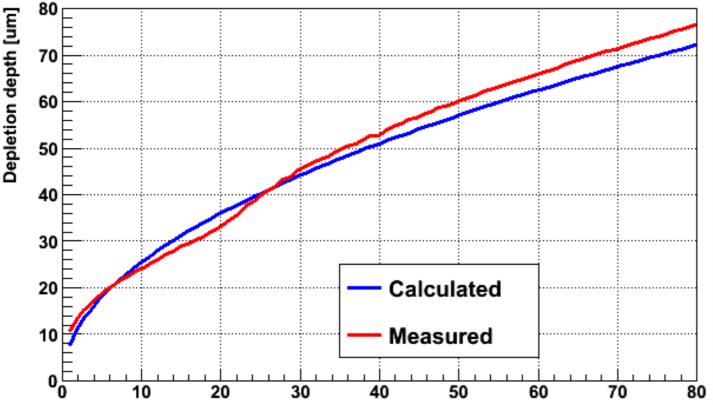

#### Actual depletion depth

#### **Depletion Depth**

- We measured depletion thickness by C-V measurements of the substrate, using the pixel guard-ring grid as electrode

- At first we had no agreement with resistivity data provided by company, then the company gave us new values which match near perfectly with our measurements.

• Measured depletion depth from  $C_j$

$$W_{meas} = \varepsilon_{S} \cdot \frac{A}{C_{i}}$$

A: detector area  $\varepsilon_s$ : silicon permittivity

• Calculated depletion depth from the nominal resistivity ( $\rho = 200 \Omega \cdot \text{cm}$  $\leftrightarrow N_B = 2 \times 10^{13} \text{cm}^{-3}$ )

$$W_{calc} = \sqrt{2\varepsilon_{S}(V_{bi} - V_{back})\rho\mu_{n}} = \sqrt{\frac{2\varepsilon_{S}(V_{bi} - V_{back})}{qN_{B}}}$$

$V_{\text{back}}[V]$

$\mu_n$ : electron mobility  $\varepsilon_S$ : silicon permittivity  $V_{bi} = V \text{ built-in}$   $N_B = \text{doping}$

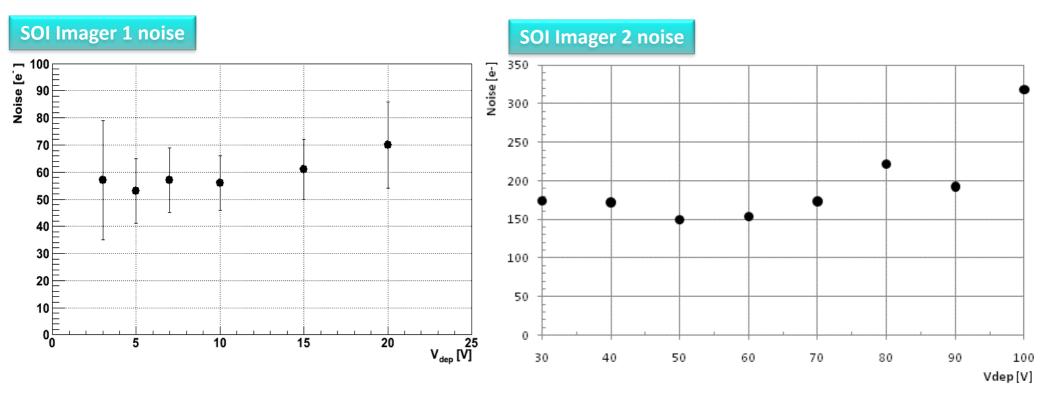

#### Noise

- Noise measured with the <sup>55</sup>Fe peak at *room temperature*.

- Noise much better with first run substrate batch (SOI Imager 1), but process is identical for both chip. Second batch shows much higher leakage current, so we think is just a quality issue with that batch.

- Tighter control over substrate should fix the issue in the future.

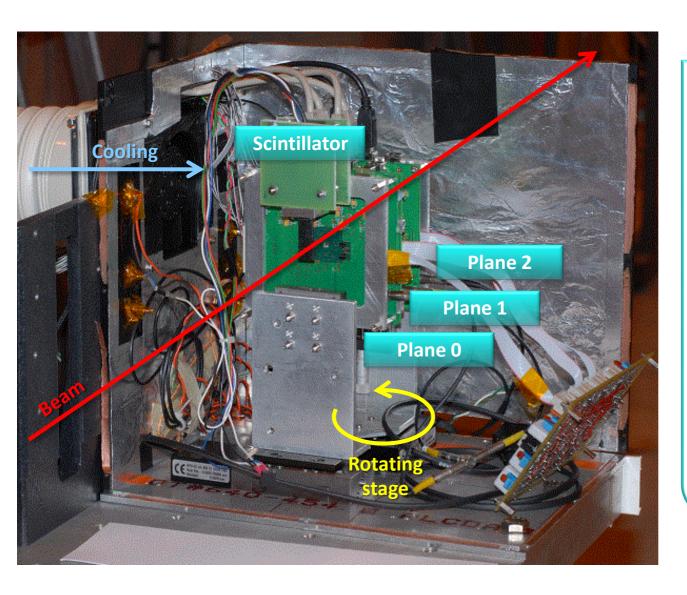

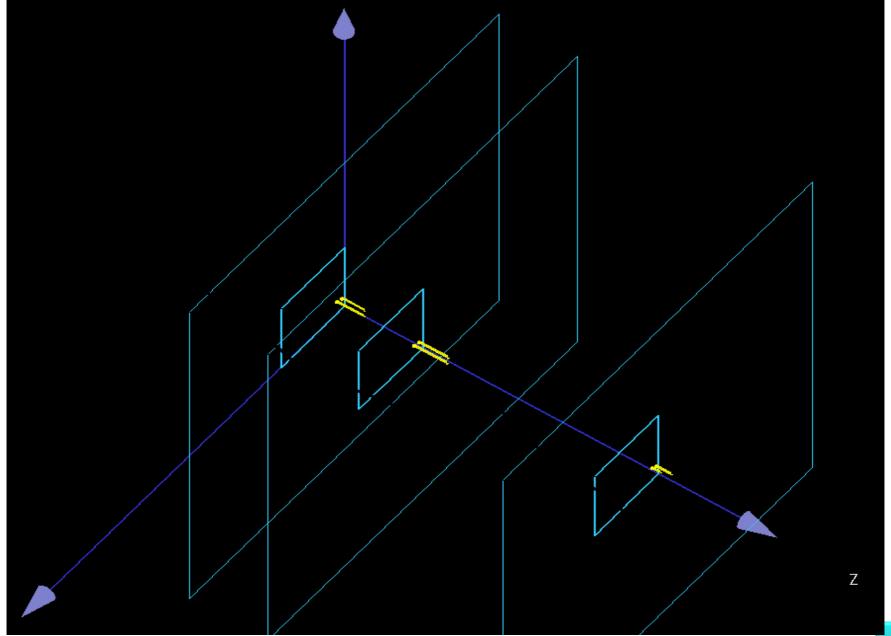

#### Test beam with 200 GeV $\pi$

- Detectors arranged in one cemented "doublet" (9 mm spaced) and one rotating plane (33 mm spaced).

- The doublet is optically aligned with a better than 50 μm precision → easy and precise coincidence cuts in cluster recognition.

- Single plane can be rotated up to 20° for slanted tracks and cluster studies.

- Temperature is maintained around 20° by cool air flow and continuously monitored.

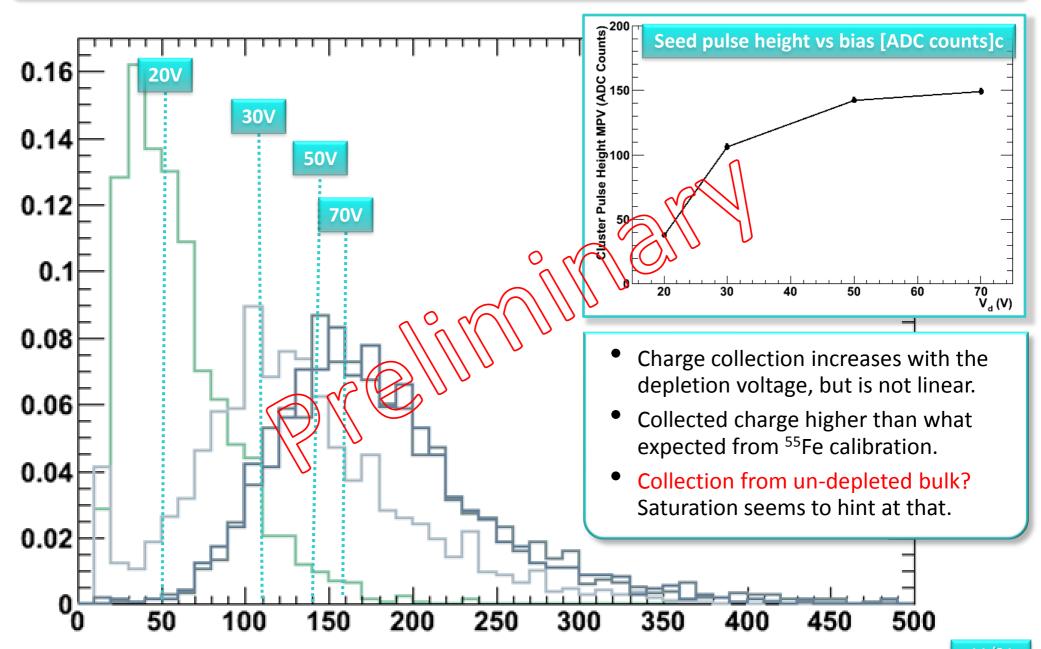

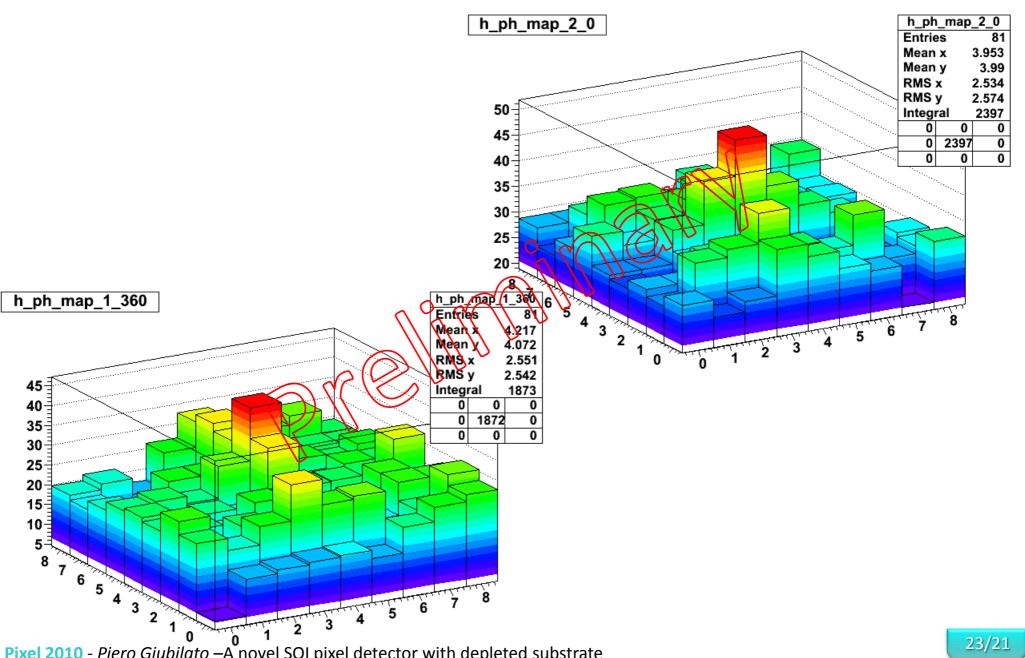

# Test beam results – seeds height

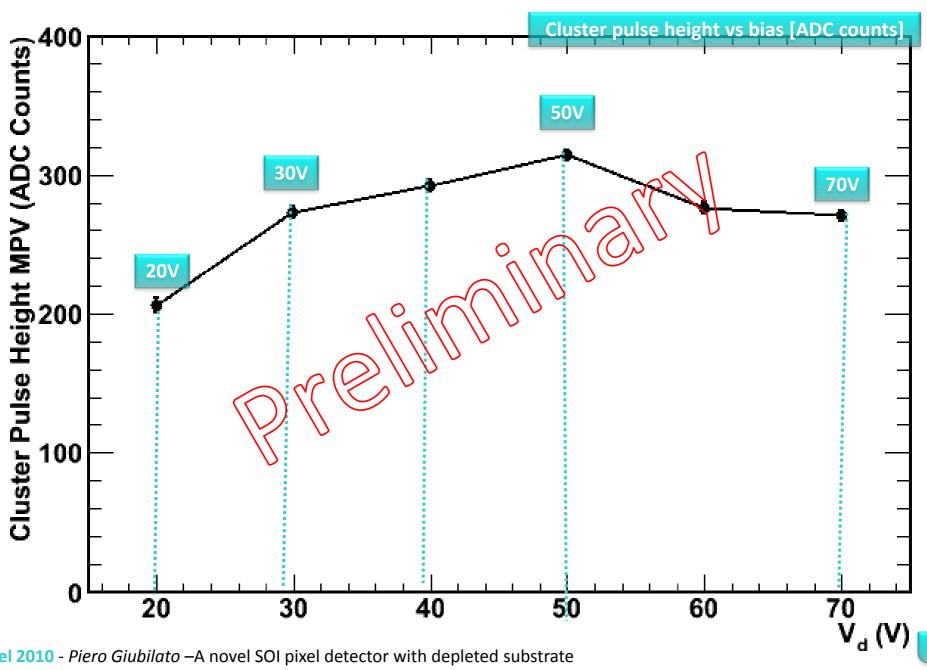

# Test beam results – cluster pulse height

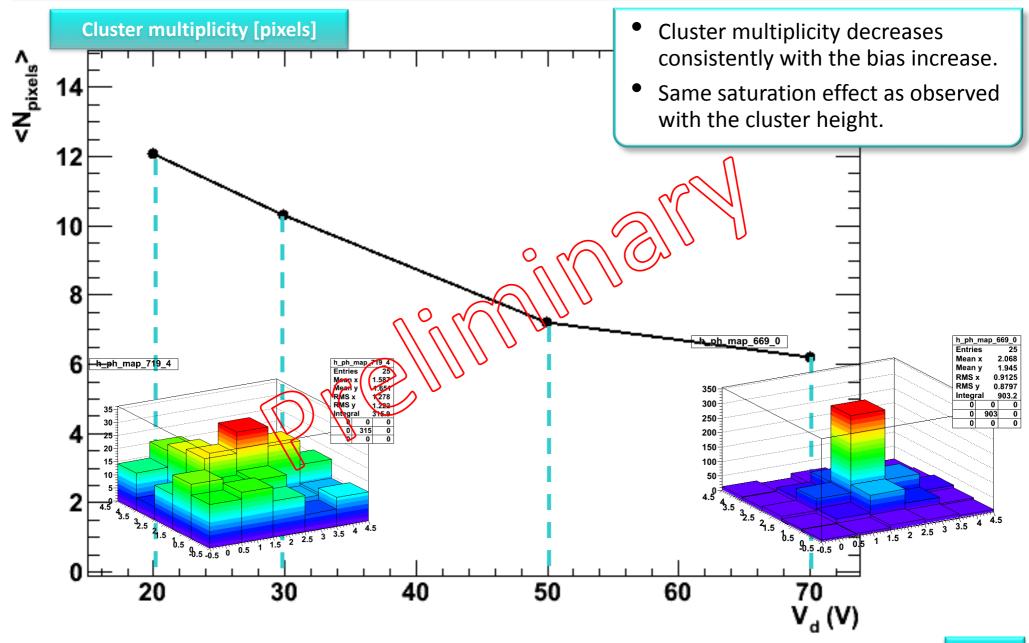

# Test beam results – cluster multiplicity

# Test beam results – 3 planes tracking

14/21

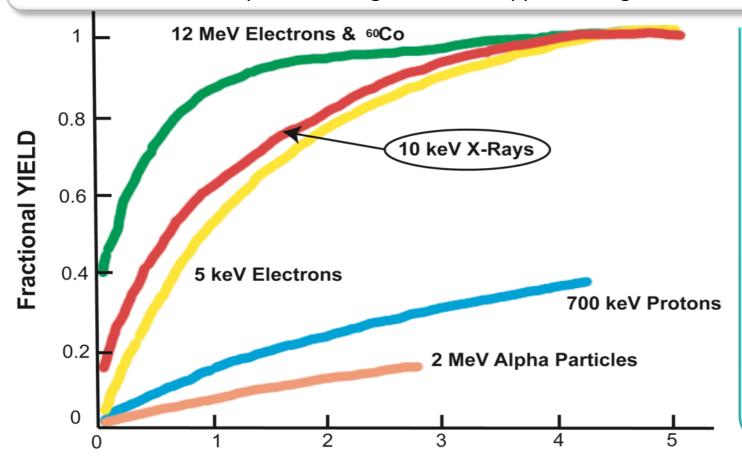

### Total dose – fractional yield

- In SOI technology, the thick buried oxide is expected to be sensitive to ionizing doses, which lead to positive charge trapping and consequently to an increase of the top-gate leakage current.

- This effect is even larger for depleted structures: the strong electrical field across the BOX splits the electron-holes pair generated by ionizing radiation, reducing the recombination yield. This greatly increases the amount positive charge which is trapped throughout the BOX  $\rightarrow$  leakage current.

- number • The of electron-hole pairs escaping recombination (fractional vield) strongly depends the bias given to the substrate.

- It also depends on the stopping power of the incident particle (the lower the ionization density, the lower the recombination probability).

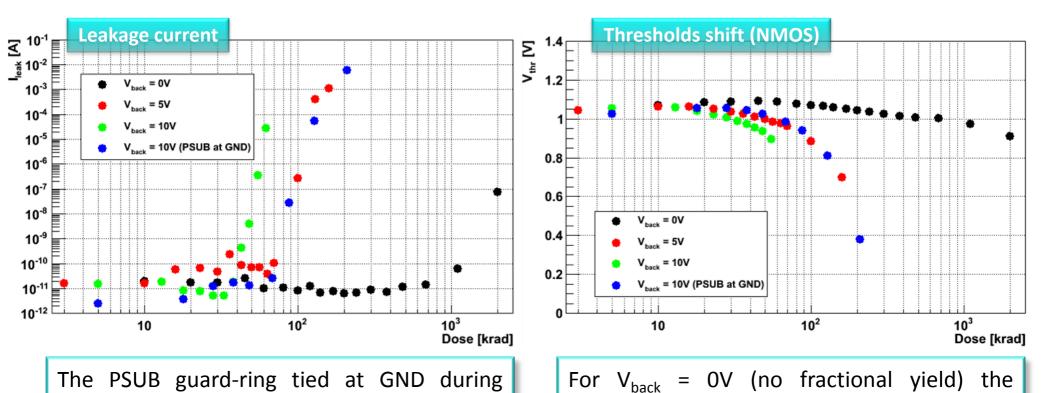

# Total dose (10 keV XRay)— leakage current and thresholds shifts

Provided to keep low the voltage under the BOX, technology can tolerate dose level up to <u>~1Mrad</u>

<u>But this is exactly what the BPW provide → we need to test!</u>

of ~1Mrad

transistor is still working properly up to doses

irradiation indeed limits the electrical field

through the BOX and improves the radiation

hardness of the device.

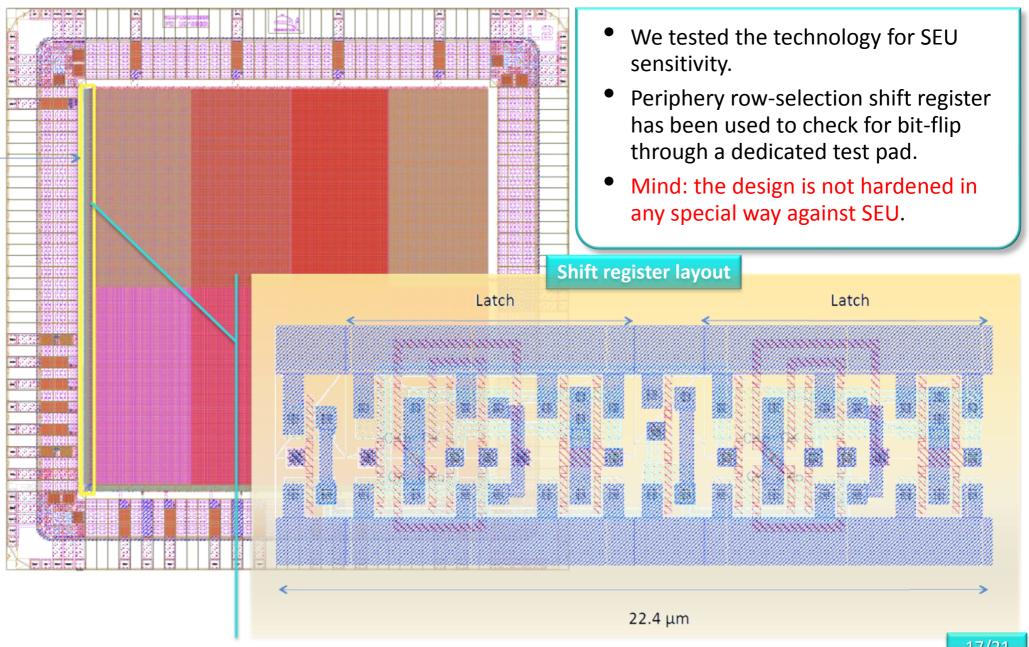

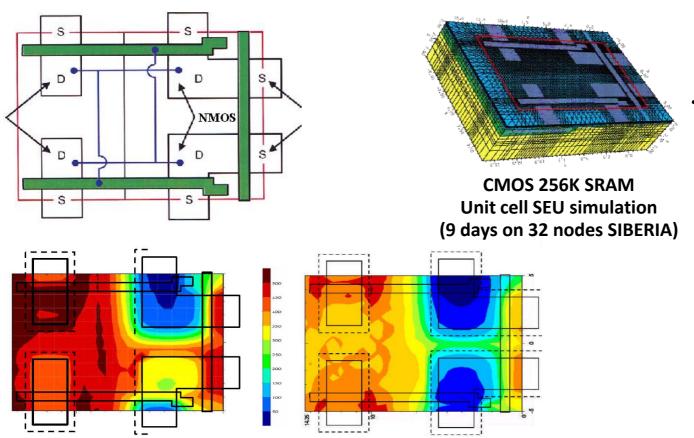

# Single Event Upset (SEU) measurement

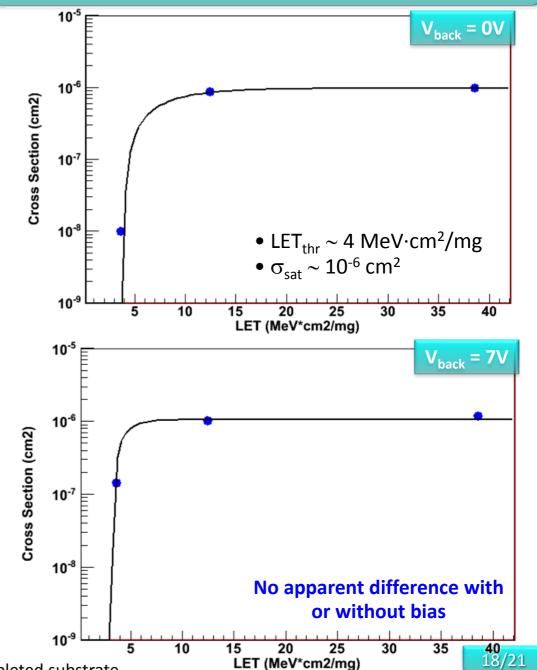

#### SEU - global cross section

- Single Event Upset (SEU) study performed at the SIRAD irradiation facility, LNL, Italy.

- A known logical pattern is written in and read back from the row selection shift register through dedicated pads during irradiation. Differences between the loaded and read-back pattern highlight a SEU occurred in the cells.

- Irradiation performed with three different ion species and, for each ion beam, for two substrate bias conditions (V<sub>back</sub> = 0V - 7V).

| lon              | Energy<br>[MeV] | LET in Si<br>[Mev cm² mg <sup>-1</sup> ] |

|------------------|-----------------|------------------------------------------|

| <sup>19</sup> Fe | 118             | 3.67                                     |

| <sup>35</sup> Cl | 170             | 12.5                                     |

| <sup>79</sup> Br | 240             | 38.6                                     |

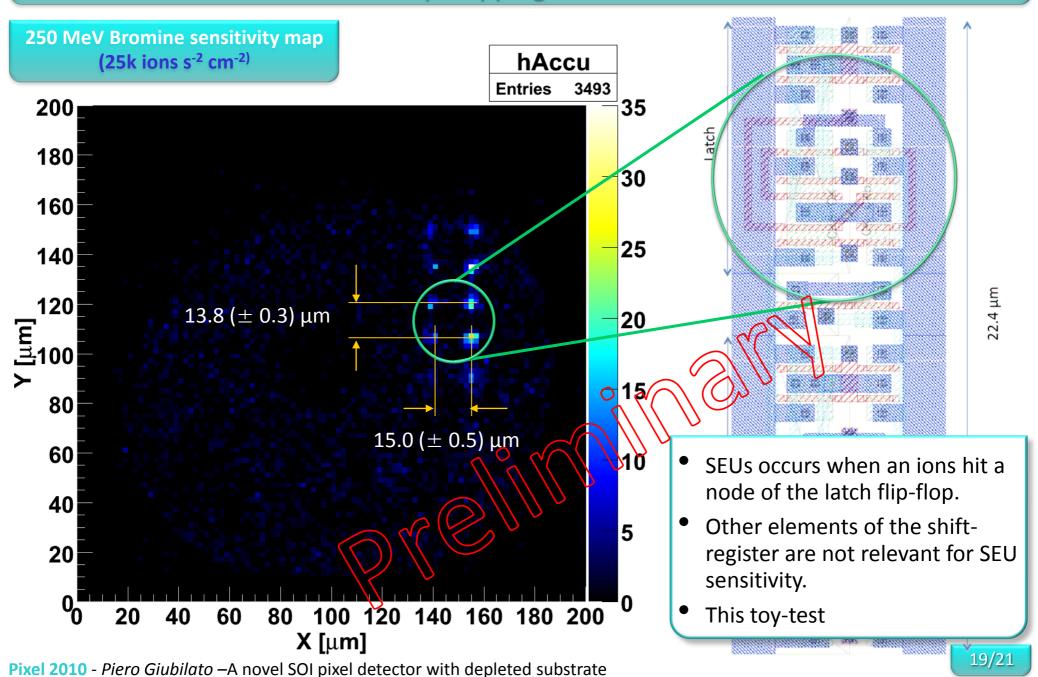

# SEU - µmapping first results

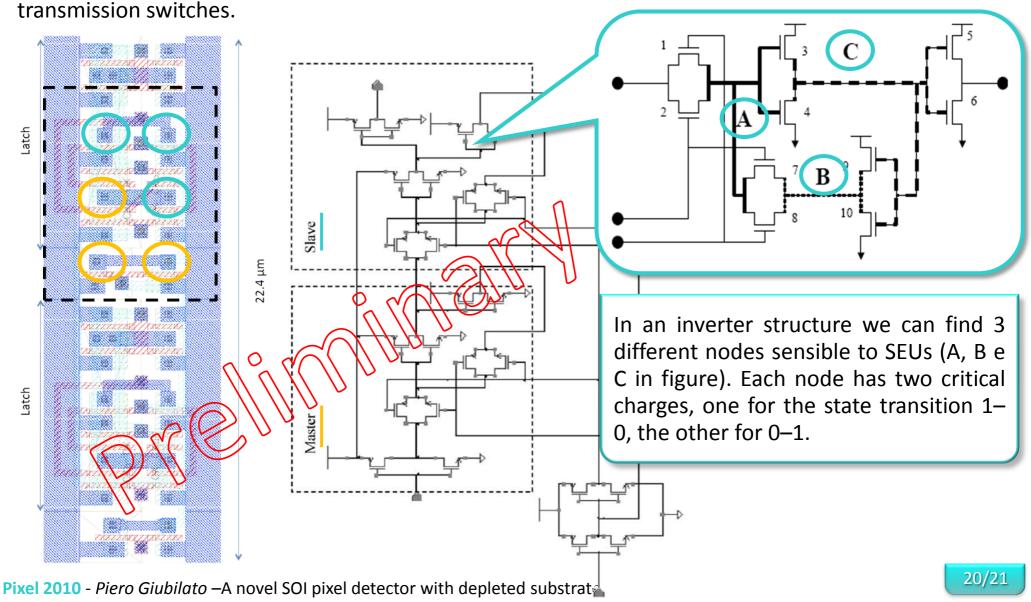

#### SEU - $\mu$ mapping, what we see

SEUs can be induced in both master and slave sections of each type of DFF, depending on whether the clock is high or low. Both master and slave of the DFF are two cross-coupled inverters with two

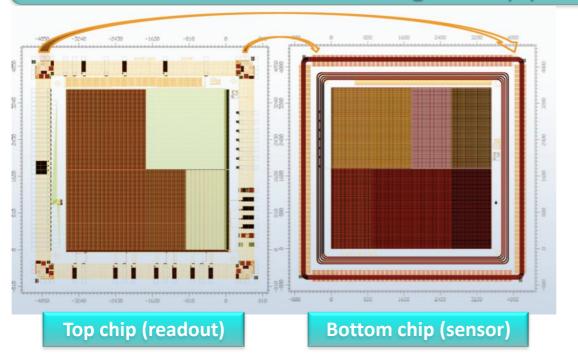

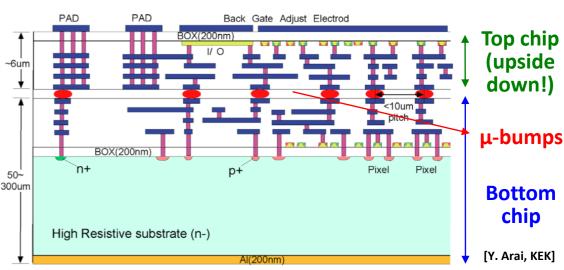

#### Waiting in the pipeline... SOI-3D

- OKI 0.20 μm FD-SOI process (submitted 2009)

- Sensor chip with graded p-type guardrings

- Readout chip to be wafer-bonded on top (ZyCube process)

- 256×256 analog pixels, 13.75 μm pitch, 4 parallel outputs

- 8 different pixel types, several test structures for process and interconnection evaluation

- 3D vertical integration process allows higher integration, improved radiation tolerance and lower power dissipation

- Vertical integration performed with ZyCube μ-bump bonding (~5 μm) technique

- After chip stacking, Si etching and pad lithography on back of top chip

- Process under way, chips waiting...

#### Conclusions

- Detectors play well in test beam

- It seems possible to improve radiation tolerance for total dose up to 1 Mrad

- PBW implant works well, freeing room (when compared to traditional guard ring) for more transistors to be packed in a single pixel

- Still waiting for the 3D chip...

- With an established pixel structure, we have to plan for a complete chip with some realistic features like periphery memory, ADCs, time-stamping... (not necessarily together on the same chip!)

- SEU tolerance still an issue for any application where it is a concern, needs to be investigated and in case addressed in future designs.

# Test beam results – cluster shapes

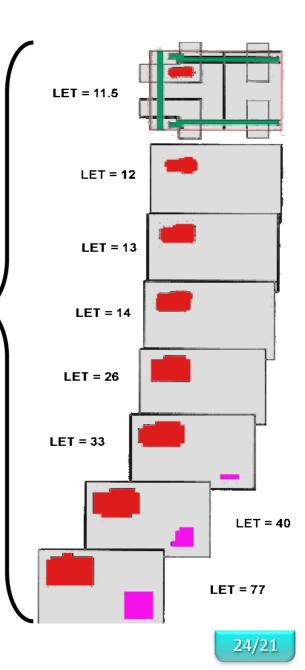

### SEU umapping in solid state devices

#### Look at this famous example:

- By increasing the impinging ion energies is possible to discover that some areas of the device become sensible to radiation only over a precise LET threshold.

- These sensible areas are precisely defined inside the device volume, and every one has its own LET threshold level.

Pixel 2010 - Piero Giubilato - A novel SOI pixel detector with depleted substrate

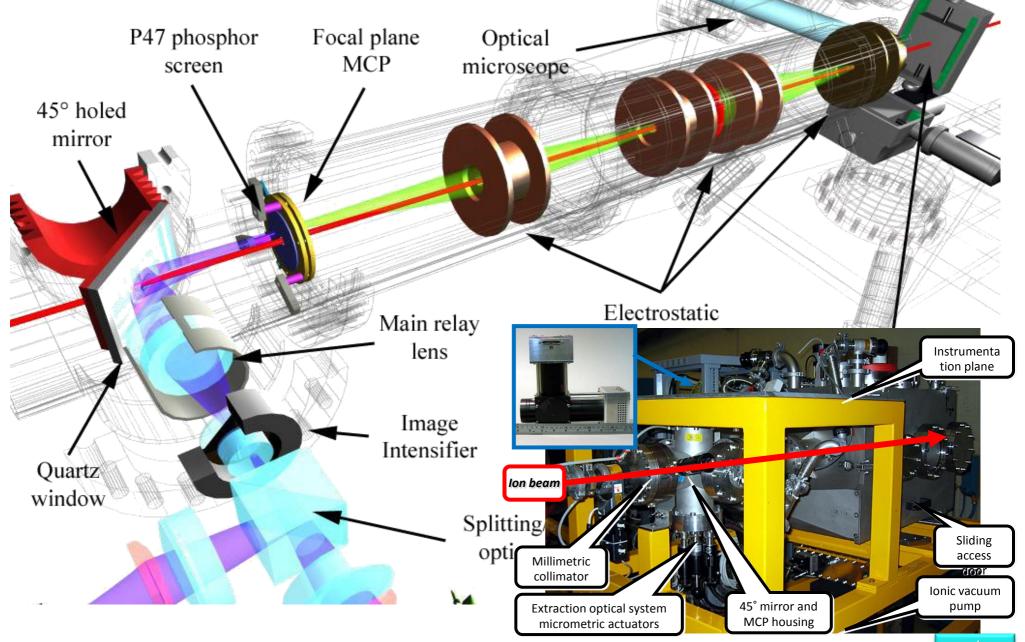

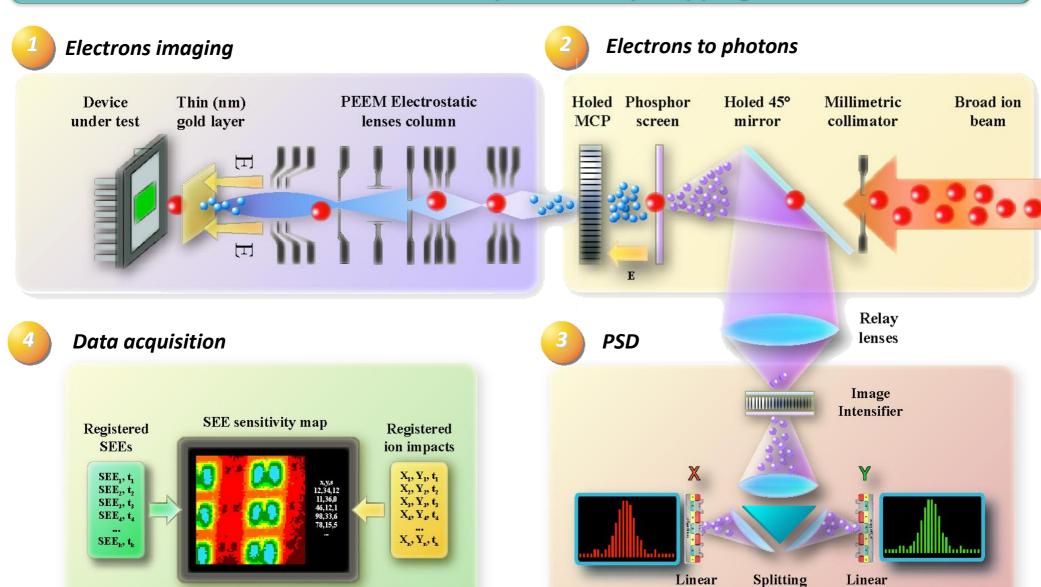

# The IEEM technique for SEU µmapping

sensor

opticts

sensor

# The IEEM system for SEU µmapping