#### ebg *Med* Austron

# Power Converter Controller Overview

Joze Dedic (joze.dedic@cosylab.com) ... on behalf of Cosylab team

### Outline

#### ...CWO-1

#### PCC

- overview

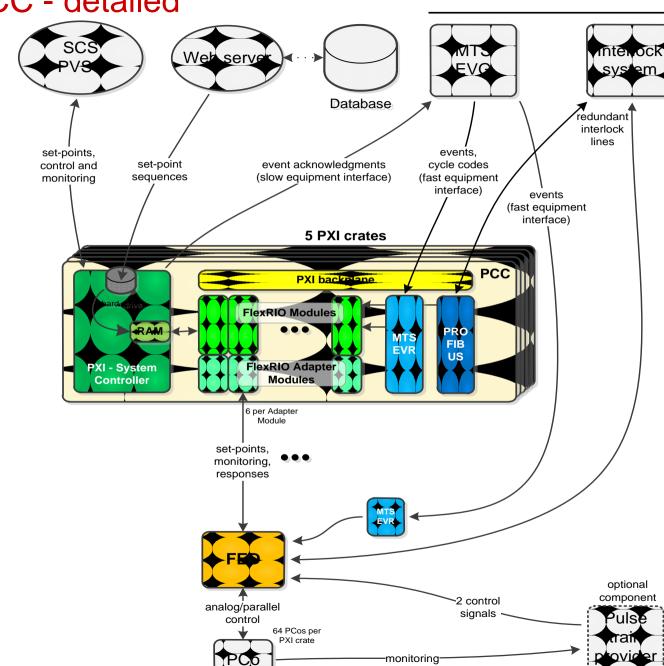

- detailed architecture

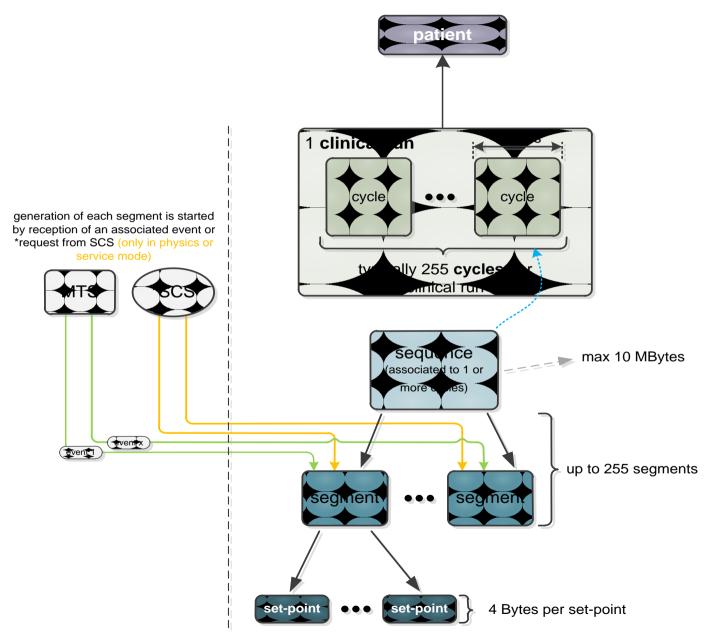

operational view (run, cycles, events)

architecture design / implementation

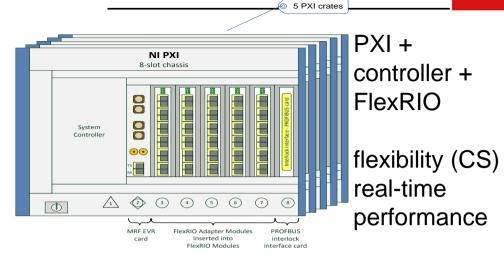

- PXI + controller + FlexRIO

- FlexRIO adapter board

FED

- link to PCo controller board

- link diagnostic

# PCC activities in CWO-1

- studied & refined requirements (simplified<sup>©</sup>)

providing support to define PCo I/F

- moved reqs. to EA model (traceability)

- made high-level architecture design

- did a step further to allow better architectural decisions (CWO-2)

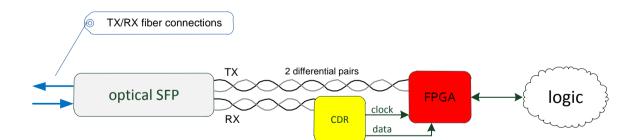

optical link prototype (protocol)

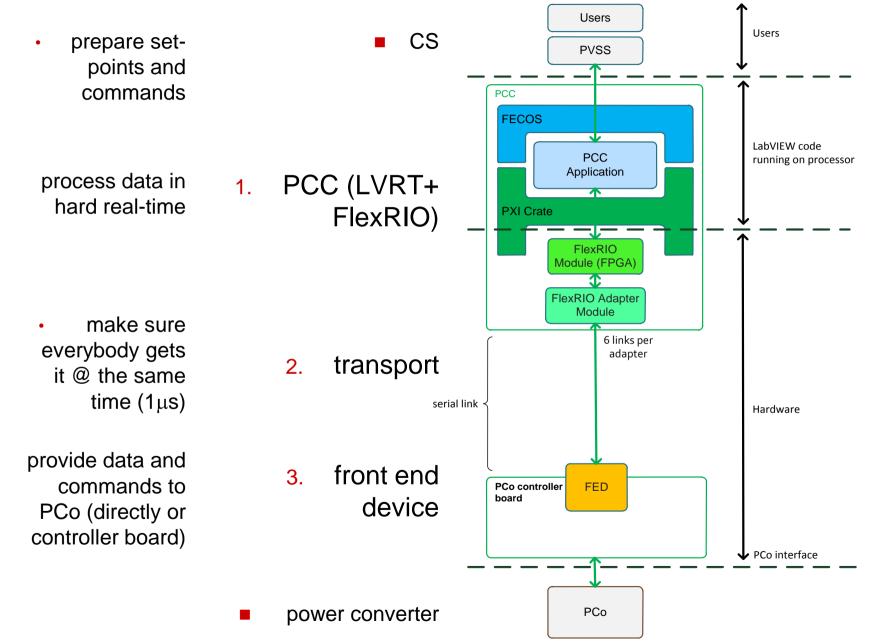

### PCC - overview

#### **Operational view**

# PXI book

S T

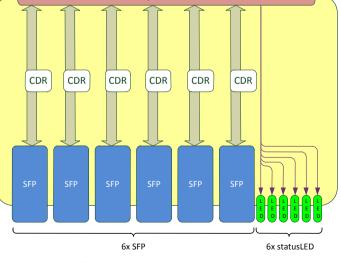

6 SFPs per

Adapter

Module

FlexRIO Adapter Module Interface

FlexRIO adapter module

cosylab

### Implementation

FlexRIO Adapter Modules

6 SFPs per

Adapter Module

ard drive

PXI - System Controller

BAM

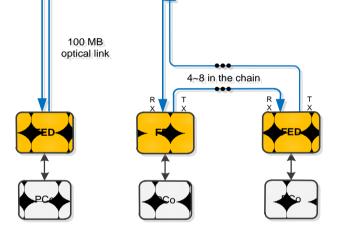

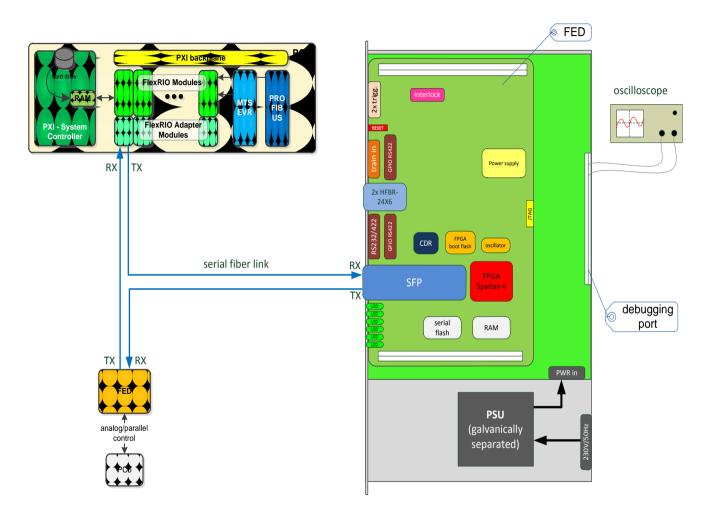

### Front End Device – FED

- standardized IF to

PCo analogue controller board (piggyback)

PCo with serial I/F

- optical isolation

- bandwidth (100MB/s)

- set-point values

- hard real-time

- + commands

- Iower priority

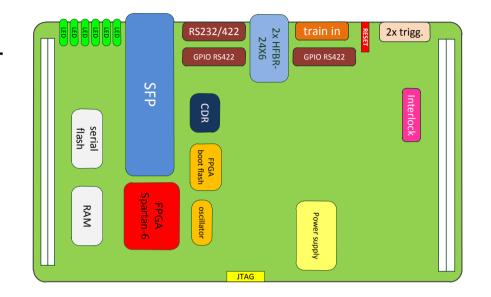

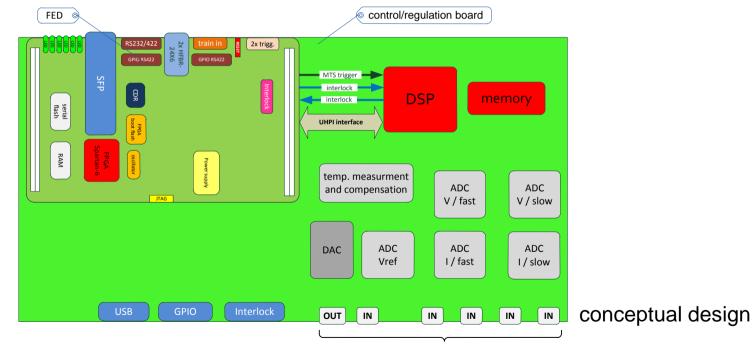

#### PCC controller board

- interface to analogue controller board DSP

- piggyback

- memory mapped

analog PCo interface

cosylab

### Link diagnostics

#### CWO-2

- define FED-DSP communication I/F

- finalize requirements and architecture design for PCC and FED

- pre-production FlexRIO adapter module

- pre-production FED with base board

to be used by other teams

- PCC FECOS component (not final version)

- data compression algorithm

$\odot$