# Upgrade of the LHCb tracking system: some French-biased perspectives

Stefano Matthias Panebianco CEA – Université Paris Saclay

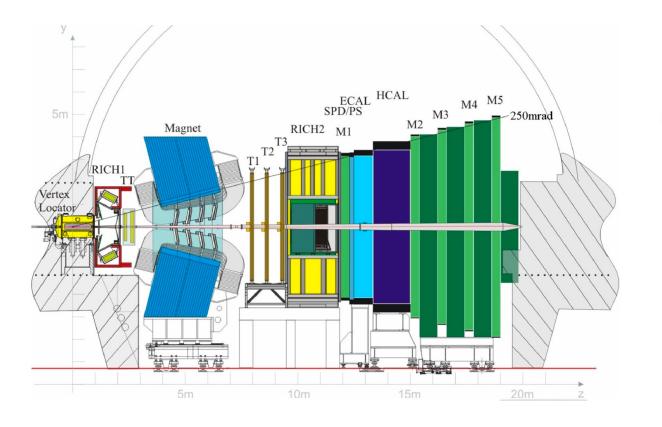

- An ambitious program implying the upgrade of almost all detectors

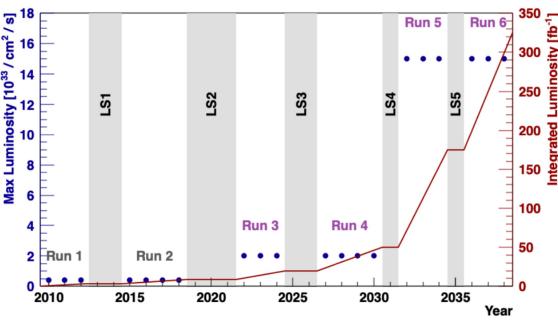

- Structured in two phases

- Consolidation and enhancement phase in LS3 (formerly called Upgrade Ib): no luminosity change (baseline)

- Main installation phase in LS4 (the so-called U2): luminosity increase

- Detailed in a Framework-TDR being completed in the coming months (for LHCC November session)

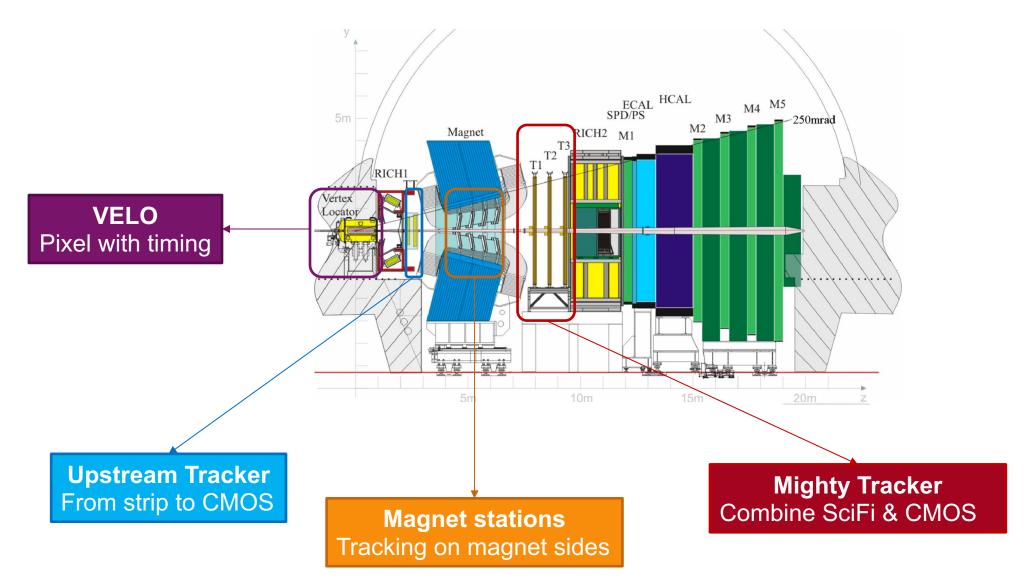

#### THE TRACKING SYSTEM UPGRADE

#### THE VELO UPGRADE

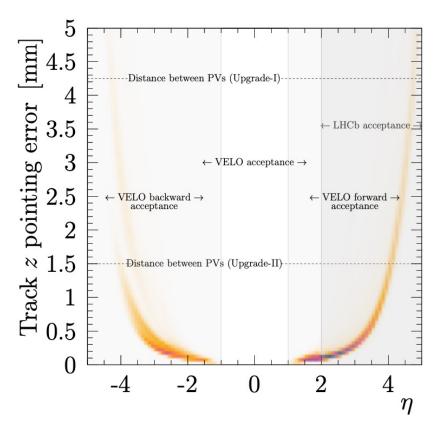

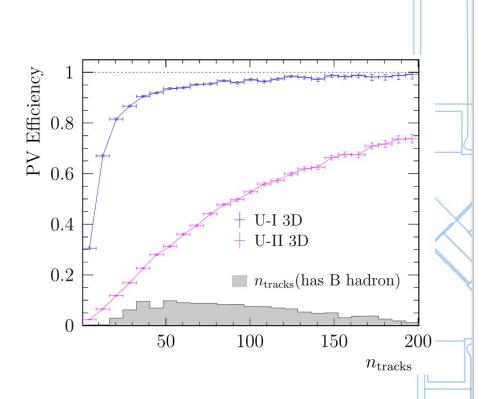

# Vertex Reconstruction @ $\mu \sim 50$ The Phase II Upgrade Challenge

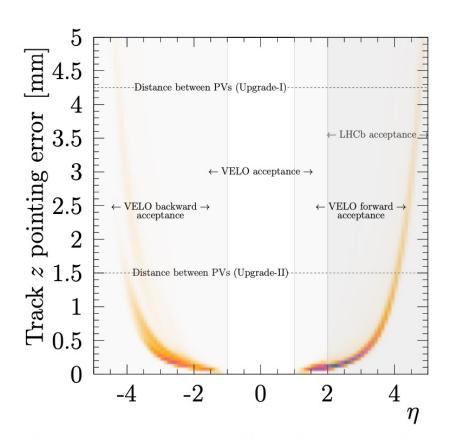

$\triangleright$  At  $\sim$  50 interactions / bunch crossing, PV separation is comparable to the per-track pointing resolution to the beam axis ( $\sim$  1 mm): Reconstruction becomes tough.

Tim Evans

#### Vertex Reconstruction @ $\mu \sim 50$ The Phase II Upgrade Challenge

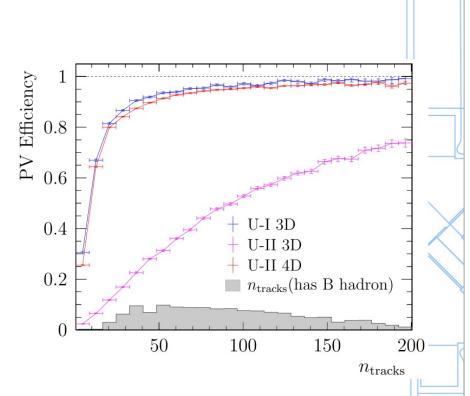

- $\triangleright$  At  $\sim$  50 interactions / bunch crossing, PV separation is comparable to the per-track pointing resolution to the beam axis ( $\sim$  1 mm): Reconstruction becomes tough.

- ▶ Initial studies show adding 50 ps / hit timestamp almost completely recovers the Upgrade-I vertex reconstruction efficiency.

Tim Evans

#### THE VELO UPGRADE

|                                                         |                       |                               | <u>8</u>                       |

|---------------------------------------------------------|-----------------------|-------------------------------|--------------------------------|

|                                                         | VeloPix (2016)        | Timepix4 $(2018/9)$           | Picopix? (2024)?               |

| Technology [nm]                                         | 130                   | 65                            | < 65                           |

| Pixel Size [µm]                                         | $55 \times 55  \mu m$ | $55 	imes 55  \mu \mathrm{m}$ | $55 \times 55  \mu \text{m}$ ? |

| Pixels                                                  | $256 \times 256$      | $512 \times 448$              | $256 \times 256$ ?             |

| ${ m Area} \left[ { m cm}^2  ight]$                     | 1.98                  | 6.94                          | 1.98                           |

| Event packet [bit]                                      | 24                    | 64                            | 64?                            |

| Max. Rate $\left[10^6 \text{Hits/cm}^2/\text{s}\right]$ | $\sim 400$            | $\sim 180$                    | $\sim 4000?$                   |

| Time resolution (TDC)                                   | $25\mathrm{ns}$       | $200\mathrm{ps}$              | $20 - 50 \mathrm{ps}$ ?        |

| Readout bandwidth [Gb/s]                                | 19.2                  | $\le 81.92$                   | $\sim 500?$                    |

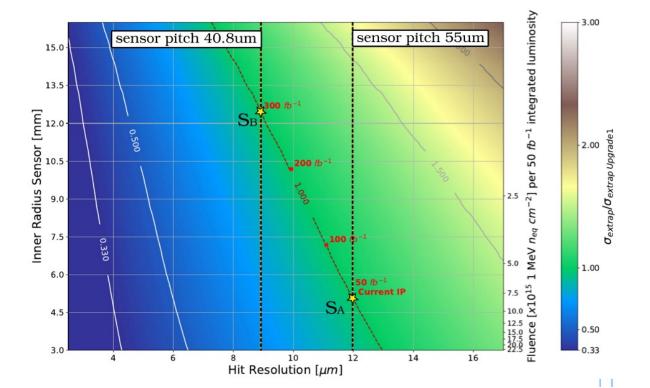

#### Push the limits of Frontend ASIC

Limit the radiation damage (10<sup>16</sup> 1 MeVn<sub>eq</sub>/cm<sup>2</sup>/year)

- Optimize position, pitch and material

- Several scenarios under study

- The most critical point seems to be the foil

5

#### THE UT UPGRADE — FROM STRIPS...

| Sensor        | A      | В      | С      | D      |

|---------------|--------|--------|--------|--------|

| Туре          | p-in-n | n-in-p | n-in-p | n-in-p |

| Thickness(μm) | 320    | 250    | 250    | 250    |

| Pitch (μm)    | 187.5  | 93.5   | 93.5   | 93.5   |

| Length (mm)   | ~100   | ~100   | ~50    | ~50    |

| Strips/sensor | 512    | 1024   | 1024   | 1024   |

| SALTs/sensor  | 4      | 8      | 8      | 8      |

| Numbers       | 888    | 48     | 16     | 16     |

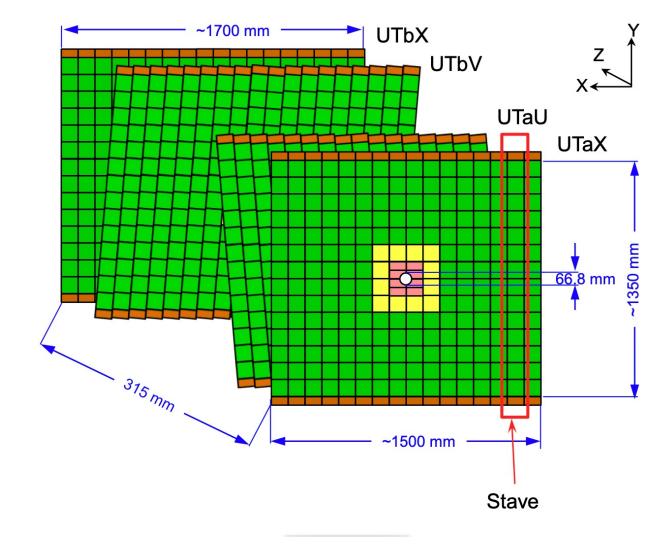

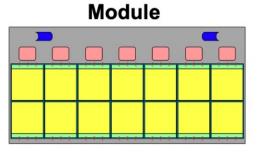

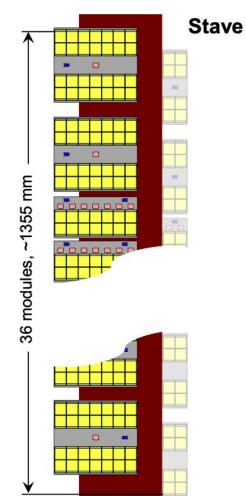

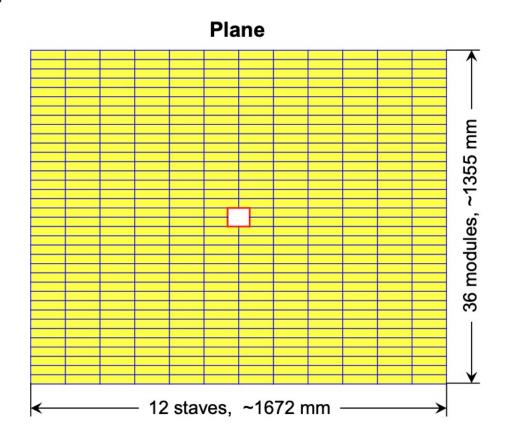

- ☐ Four planes of silicon strip detectors, readout ASICs at sensor proximity.

- ☐ Higher segmentations near the center. Max occupancy ~ 1.4%.

- ☐ Stave structure: modules on 2 sides for overlapping, readout at 2 ends.

- ☐ In total 68 staves, 968 sensors, 4192 ASICs.

#### The present UT upgrade

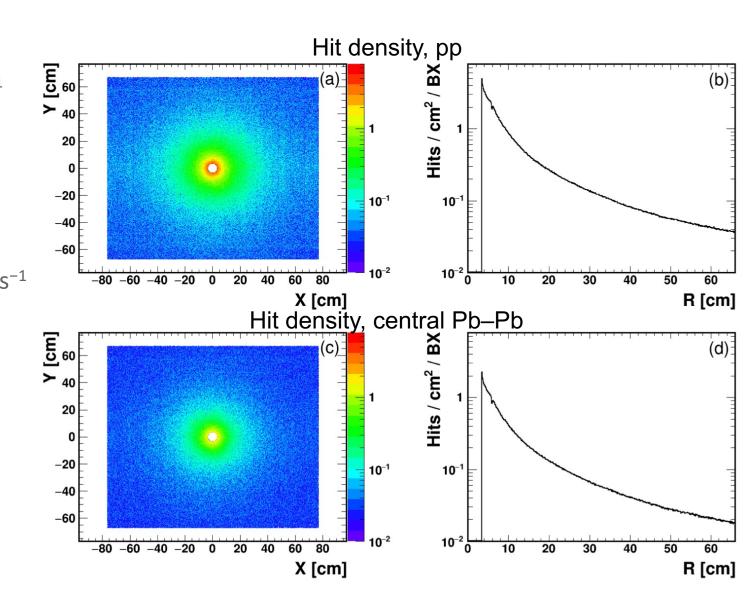

#### pp collisions

► Instantaneous Luminosity 2 × 10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> 67% of BX have beam-beam collisions O(10) tracks per pp collision Average hit rate in UT: 5.9 hits/cm<sup>2</sup>/BX<sub>coll</sub>

#### Pb-Pb collisions

► Instantaneous Luminosity up to 10<sup>28</sup> cm<sup>-2</sup>s<sup>-1</sup> Pile-up: negligible O(1000) tracks per central Pb—Pb collision Average hit rate in UT: 2.9 hits/cm<sup>2</sup>/BX<sub>coll</sub> Maximum hit rate in UT: 52.5 hits/cm<sup>2</sup>

#### Lighter ion collisions

► Allow larger integrated luminosity

Still no significant pile-up (except O–O)

Smaller track densit than Pb–Pb

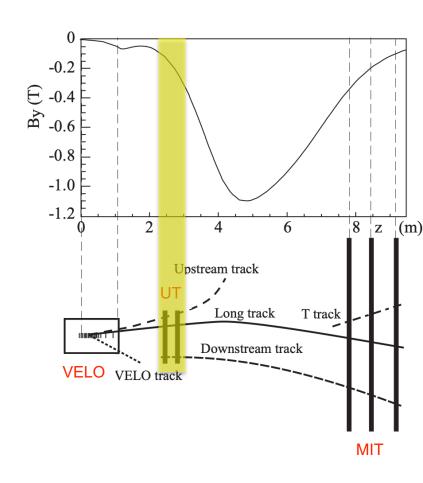

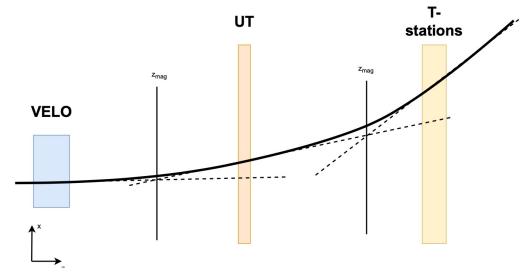

UT is key to connect VELO and MIT track segments

UT is essential for Upstream and Downstream tracks

Possibility of standalone UT track segment

- ► Will likely require three UT stations

- ► Could improve and speed-up track matching

- Could provide momentum estimation

#### Need of timing is being studied

- ► Minimum requirement: BX identification, few ns time resolution

- ➤ Tracking: e.g. background rejection, sub-ns time resolution

Need to handle high-occupancy of most central Pb-Pb collisions

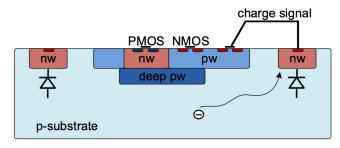

#### **Solution: replace the Si strips with CMOS MAPS**

Large interest within the French HI community and beyond...

- ► LLR, LPNHE, Irfu, Subatech,...

- ► Several labs in China

#### THE UT UPGRADE - FROM STRIPS... TO PIXELS

#### Two main CMOS options under development

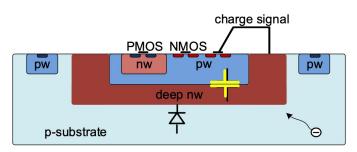

Large collection electrode

- Typical pixel size: 50 x 150 μm<sup>2</sup>

- Circuitry inside the collection well (requires high field: HV-CMOS)

- High radiation hardness

- Higher noise (high capacitance)

- Higher power consumption

- Possible cross-talk (digital to sensor)

- Presently developed under AMS-180 (MuPix, ATLASPix) and LF-150 technologies (Monopix2)

Small collection electrode

- Typical pixel size: 30 x 30 μm<sup>2</sup>

- Circuitry outside the collection well (requires low/moderate field: LV-CMOS)

- High radiation hardness thanks to process modification (increase of depletion zone)

- Lower noise (low capacitance)

- Lower power consumption

- Less sensitive to cross-talk

- Presently developed under TJ-180 (Monopix2, MALTA2)

#### **Main advantages**

- Excellent space resolution

- Low budget

- Good radiation hardness

- High integration in monolithic technology

#### Main challenges

- Readout architecture for very high hit rate

- Provide high radiation tolerance

- Improve time resolution (eventually to sub-ns range)

- Keep low power consumption

Final choice on MAPS technology will be based on refined and consolidated detector specifications

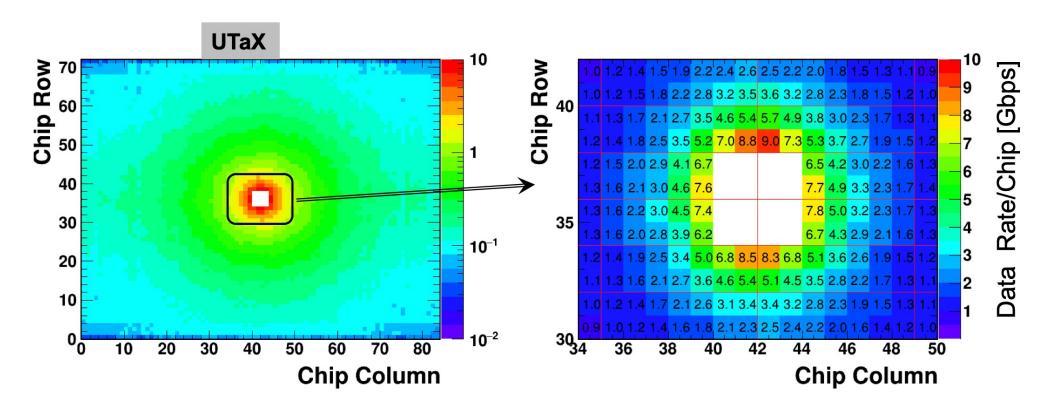

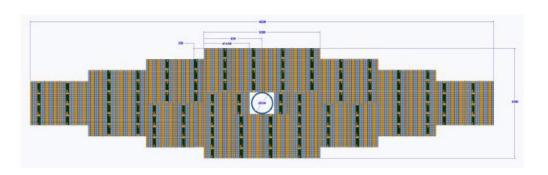

#### A possible setup, very preliminary

# Reticle size ~ 20.2×21.4 mm² Pixel Orientation 50×150 μm²

Jianchun Wang

- Use minimal 28 bits per pixel hit.

- The whole UT throughput is 6.8 Tbps.

- The hottest chip ~9.0 Gbps, which needs at least 8 links of 1.28 Gbps/link.

| BXID         | Column    | Row       |

|--------------|-----------|-----------|

| 12b (0-3563) | 9b (≤399) | 7b (≤127) |

Jianchun Wang

#### THE UT UPGRADE — TRACKING PERFORMANCES

| Characteristics     | LV-CMOS                                       | HV-CMOS                           |

|---------------------|-----------------------------------------------|-----------------------------------|

| Chip size           | $3.5 \times 3.5 \text{ cm}^2$                 | $2.0 \times 2.0 \; \mathrm{cm}^2$ |

| Pixel size          | $30 \times 30 \ \mu\mathrm{m}^2$              | $50 	imes 150 \; \mu\mathrm{m}^2$ |

| Chip thickness      | $100~\mu\mathrm{m}$                           |                                   |

| Position resolution | $510~\mu\mathrm{m}$                           | $15,40\;\mu\mathrm{m}$            |

| Time resolution     | O(1 ns)                                       |                                   |

| Power consumption   | $100300~\mathrm{mW/cm^2}$                     |                                   |

| Data rate per chip  | Up to $30 \text{ Gb/s}$                       | Up to $9 \text{ Gb/s}$            |

| Radiation dose      | $3 \times 10^{15} \text{ n}_{eq}/\text{cm}^2$ | , and 240 Mrad TID                |

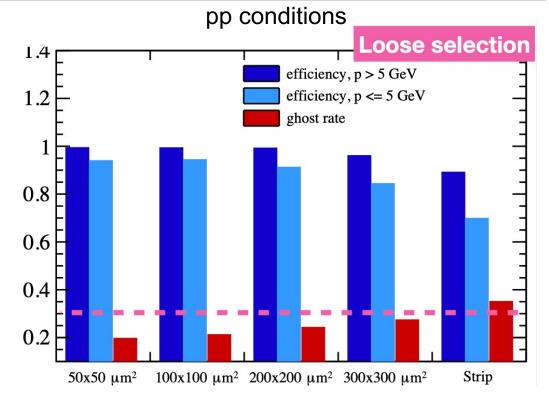

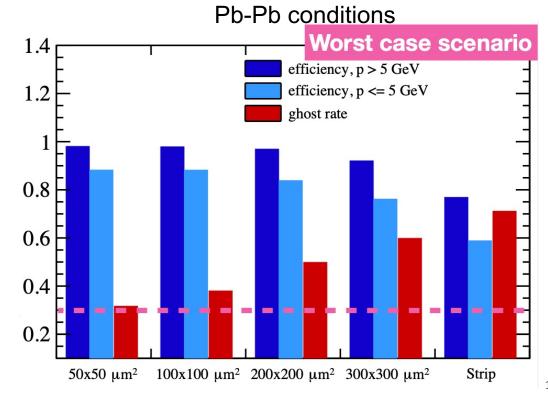

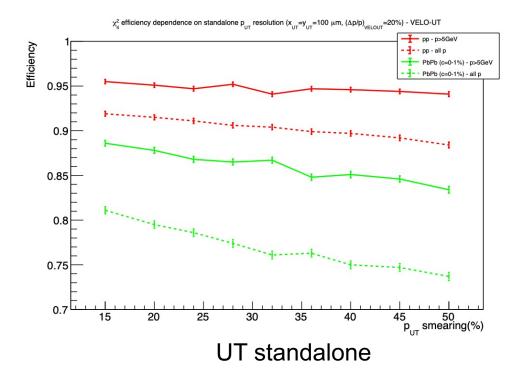

#### **UT standalone performances** (Cristina Agapopoulou)

- Small pixels required to reduce ghost rate (especially in Pb-Pb) and improve efficiency at low momentum

- Similar efficiency achievable in pp and Pb-Pb

#### THE UT UPGRADE — TRACKING PERFORMANCES

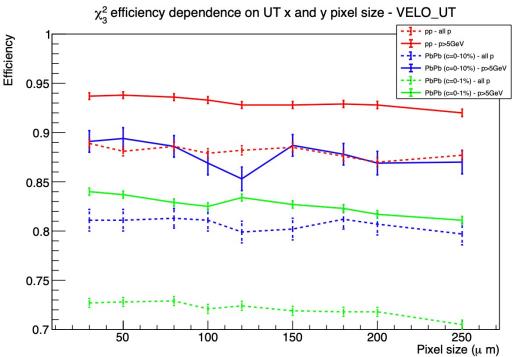

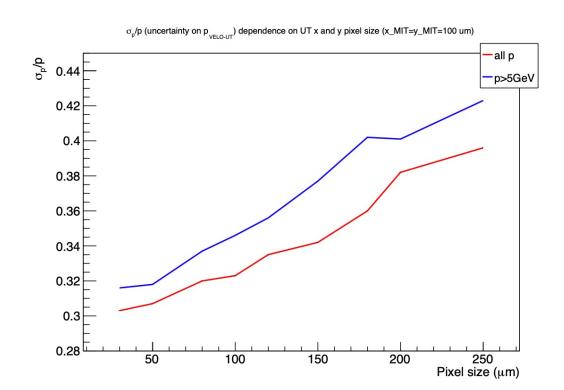

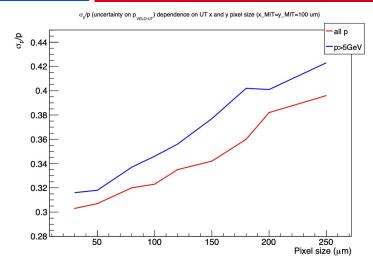

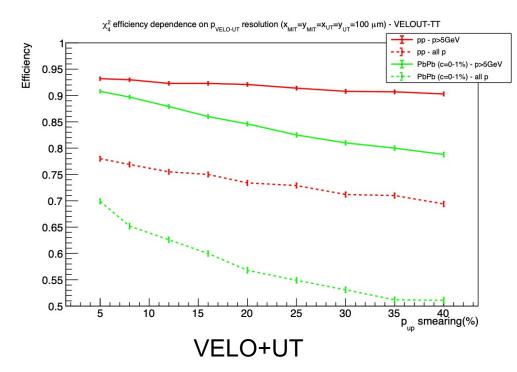

#### Matching studies (B. Audurier, G. Legras, M. Winn)

- All very preliminary!!!!

- Efficiency in most central Pb-Pb can be kept reasonably high, even at low momentum

- Impact of pixel size negligible on efficiency but essential for momentum resolution

#### THE UT UPGRADE — TRACKING PERFORMANCES

#### Matching studies (B. Audurier, G. Legras, M. Winn)

- All very preliminary!!!!

- Efficiency in most central Pb-Pb can be kept reasonably high, even at low momentum

- Impact of pixel size negligible on efficiency but essential for momentum resolution

- Momentum resolution sensibly increase the efficiency

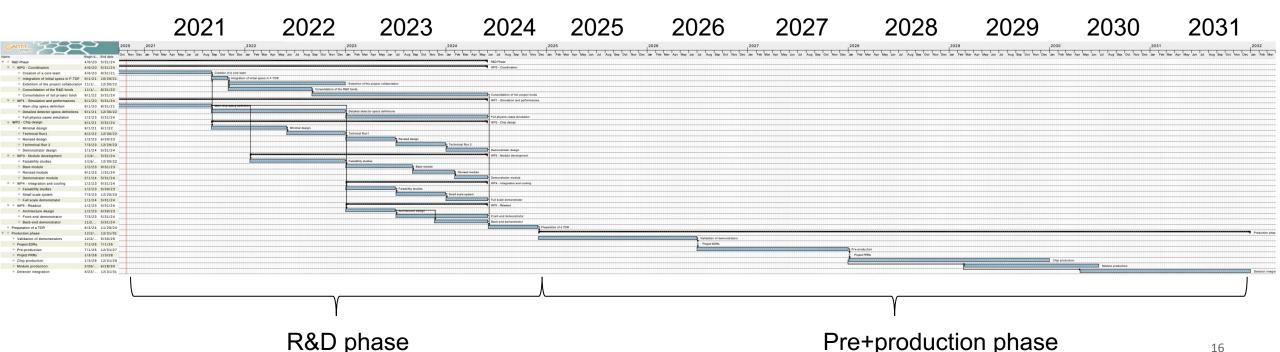

- Preliminary studies and performances included in the F-TDR

- Proto-collaboration being consolidated (high impact of French labs)

- In the ~3 years to come

- Consolidate the performance studies and apply them to the largest set of physics cases (quantify projections)

- Start the R&D on the CMOS with a preliminary design (LV/HV?) to qualify under beam test

- Implement a technical solution of the mechanical setup (power distribution and cooling) and the readout scheme

- Complete the R&D by a Technical Design Report (together with a detailed cost/funding assessment)

- Attract new labs (within and eventually from outside LHCb)

16

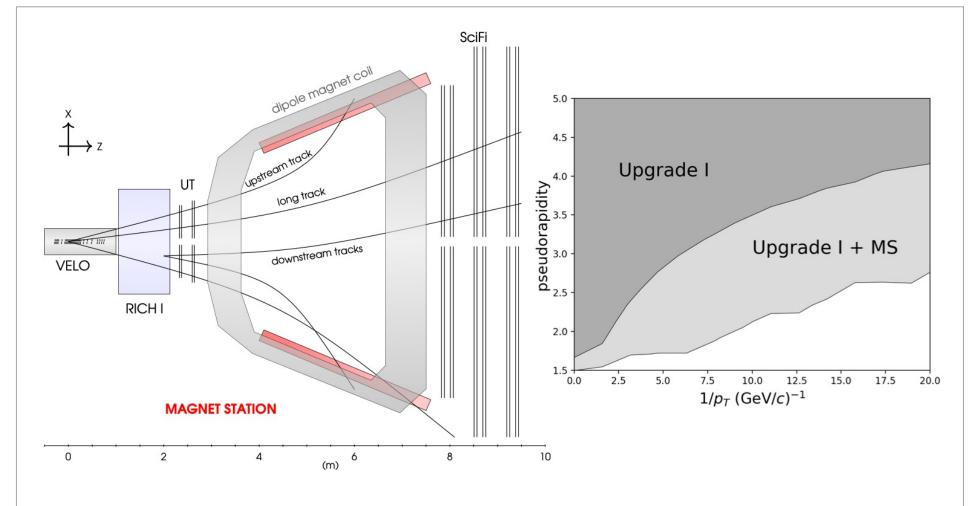

- provides high precision tracking for an extended momentum and pseudorapidity region

- help reconstruct tracks at the outer edges of the SciFi

Cesar Luiz da Silva

#### THE MAGNET STATIONS

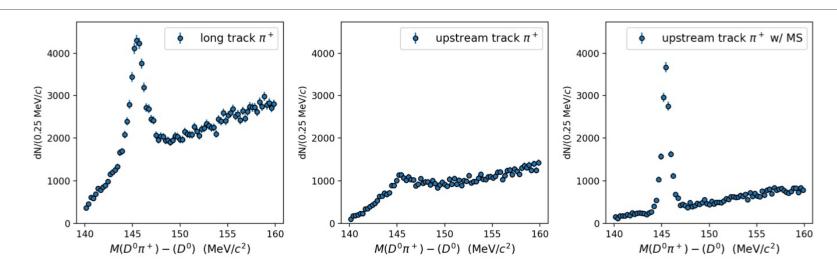

- VELO+UT tracks can be taken for granted for Physics analysis?

- new study with Run 2 simulation using  $p_T < 1$  GeV/c  $D^{*+} \rightarrow D^0 \pi$  decays

- ullet Pbp simulation: PYTHIA+EPOS with  $\sim 15$  binary pp collisions

- the pion can be a long or upstream track

- almost no peak is seen for Upstream tracks

- if the pion track information is replaced by its true 4-momentum smeared in  $\delta p/p=1\%$  (twice the momentum resolution of the MS), a sharp peak is observed

- MS allows momentum resolution improvement and ghost track rejection

- zero  $p_T$  D<sup>+</sup> and D<sup>\*+</sup> are at reach with the Magnet Trackinh Station

Cesar Luiz da Silva

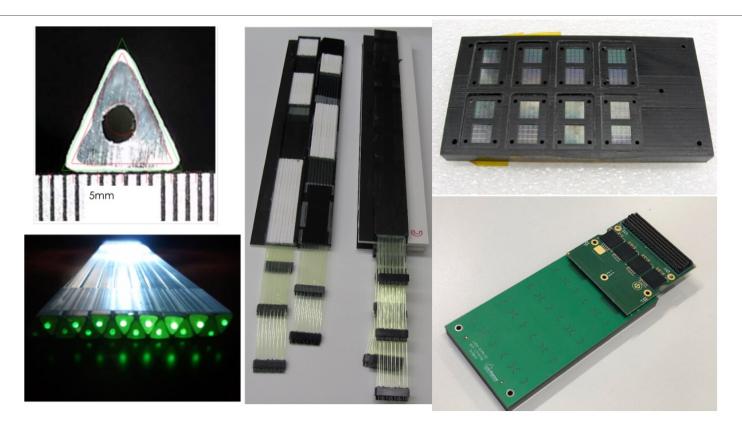

- extruded triangular scintillating bars

- 5% light loss after 1Mrad(10kGy) exposure, more than expected with 50 fb<sup>-1</sup>

- light collected by a WS and guided through clear fibers to SiPMs located outside the magnet

Cesar Luiz da Silva

#### THE MIGHTY TRACKER

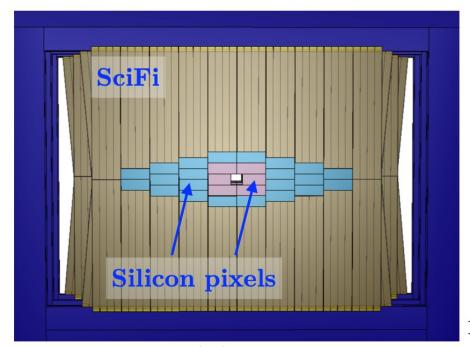

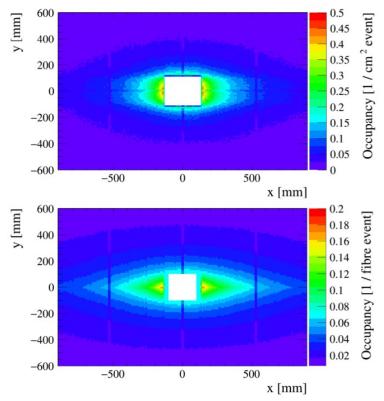

- $\int \mathscr{L} = 300 \text{fb}^{-1} \implies \text{significant fibre radiation damage in inner region}$

- ullet  $\mathscr{L}_{\mathrm{inst}} = 1.5 imes 10^{34} \ \mathrm{cm}^{-2} \ \mathrm{s}^{-1}$

- $\Rightarrow$  very high occupancy (up to 20%/fibre/event)

- ⇒ SciFi must be replaced near beam pipe to maintain the same (or better) tracking performance

- Solution: instrument the inner region with a pixel detector, while keeping scintillating fibres in the outer region

(Distinguish between Inner and Middle regions because LHCb is exploring the option to install Inner part for Run4) Fred Blanc

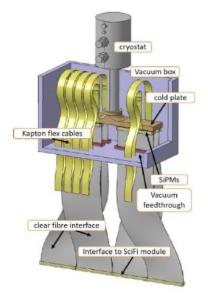

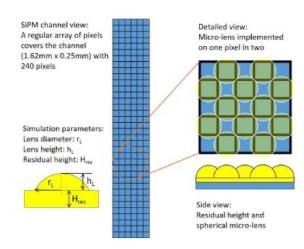

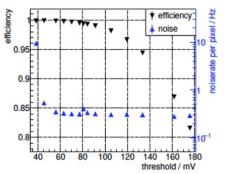

### SciFi enhancement

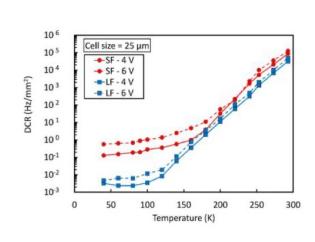

Major improvement seen cryogenic cooling to allow to run below -120 °C

- Essential to maintain reasonable noise rate for SiPMs after irradiation

- Should allow to reduce the cluster thresholds while keeping acceptable dark count rate

Additional interface ~ 16 % loss in light

Can gain back ~ 20 % by microlens.

Geometry packing of SiPMs also improved

Fred Blanc

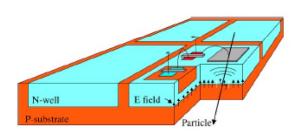

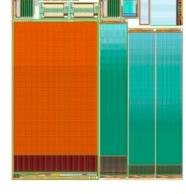

# The MightyPix

- Monolithic Active Pixel Sensor (MAPS)

- Integrated pixel sensor & chip on single piece of silicon

- Low-cost commercial process

- e.g. used for mobile phone cameras

- First radiation hard CMOS tracker at LHC

- Chip based on existing MuPix/ATLASPix

- https://arxiv.org/abs/2002.07253

- "MightyPix" Specification document in preparation

| Parameter                              | Depleted CMOS Sensors for LHCb                                      |

|----------------------------------------|---------------------------------------------------------------------|

| Chip Size                              | $\sim 2\mathrm{cm} \times 2\mathrm{cm}$                             |

| Sensor Thickness (µm)                  | 200 (ATLASPix3)                                                     |

| Pixel Size (µm)                        | $100 \times 300$ (with smaller sizes to be explored)                |

| Time Resolution (ns)                   | Must be within 25 ns window                                         |

| Inactive area                          | < 5%                                                                |

| Power Consumption (W/cm <sup>2</sup> ) | 0.15                                                                |

| Data transmission (Gbps)               | 4 links of 1.28 Gb/s each, multiplexed to 2 and 1 links             |

| NIEL (TBC)                             | $3 \times 10^{14} \ (6 \times 10^{14} \ \text{with safety factor})$ |

Fred Blanc

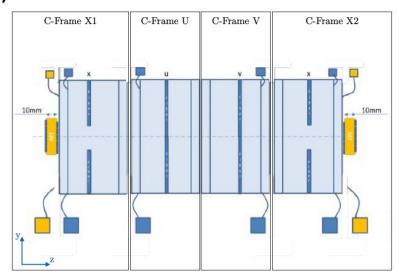

# SciFi-CMOS integration

- SciFi layers and station layout similar to Upgrade 1 (modulo cryogenic cooling and mounting of layers on individual C-frames)

- Silicon layer panels (+ services) mounted on front and back of first/last x-layers in each station

- Panels integrated into Airex support box that provides thermal isolation (allowing operation below 0°C)

Services for Silicon run across Fiber acceptance Care needed with material budget

Fred Blanc

Alex Bitadze, Trevor Savidge

## Conclusions

- HL-LHC conditions require a major upgrade of all LHCb trackers

- Very important effort in prospecting solutions which use innovative techniques

- Preliminary studies (physics cases, tracking performances, technological solutions) have been made and integrated within the Framework-TDR

- Large interest of several French labs in contributing to the Upstream Tracker upgrade

- Leading role in performing preliminary studies and accreting a proto-collaboration

- Ambitious physics program thanks to the complementary role of Mighty Tracker and (eventually)

Magnet Stations

- The R&D program is being started and will gain momentum in the coming 3 years

- Exciting physics and technological developments ahead of us and important occasion to significantly enhance the impact of the French community in the HI program for the Run5 and beyond...