# Depleted Monolithic Active Pixel Sensors in LF 150nm and TJ 180 nm CMOS technologies: The Monopix developments

Vertex 2020 conference October 7<sup>th</sup>, 2020

Marlon Barbero, CPPM, Aix-Marseille University, CNRS / IN2P3, France

On behalf of

#### Introduction

#### 1- Introduction

- 2- TJ 180 nm TJ-Monopix development

- 3- LF 150 nm LF-Monopix development

- 4- Conclusion

## Monolithic depleted CMOS

Depleted

monolithic

**CMOS Pixels**

active

In some context, could provide advantageous alternative to hybrid pixels.

#### Key ingredients:

- Charges collected by drift.

- to go above  $\sim 10^{13} \, n_{\rm eq}.\rm cm^{-2}$ , collecting charge by diffusion is problematic  $\rightarrow$  drift (hence standard MAPS  $\rightarrow$  Depleted MAPS).

- Consequence → Fast signal response & radiation hardness.

- Technology requirements → High Voltage process (apply 50-200 V), High Resistive wafers (>100Ωcm) and multiple nested wells (for full CMOS & shield)

(depleted layer:  $d \sim \sqrt{\rho \cdot V}$ )

p- substrate

#### Advantages:

- Usage of commercial process: production capability, reliability, low cost...

- Simple less expensive module (wrt hybrid): no hybridization and much easier production! Can be used for larger area applications

- Small pixel size possible (in some process)

- Less power, less material...

#### MAPS and DMAPS

#### STAR experiment

1st MAPS-based vertex detector for HEP

#### ALPIDE for ALICE upgrade

- DMAPS Monopix development based on original specs for ATLAS ITk outer pixel layer: NIEL >  $10^{15}$  n<sub>eq</sub>.cm<sup>-2</sup>, TID > 80 Mrad, Hit Rate > 100 MHz.cm<sup>-2</sup>

- Higher radiation hardness & faster readout need:

- → Cope with NIEL / trapping:

- Fast collection by drift

- $\rightarrow$  Have high time resolution:

- Fast collection by drift

- Fast analog FE

- Time stamping on chip

- → Cope with high TID:

- Process + design methodology

- → Cope with high hit rate:

- Fast return to baseline in analog

FE (<~ 1 μs, avoids pile-up)</li>

- High logic density

- High output bandwidth

## Specifications vs. environments

In terms of radiation hardness and speed:

|                        | STAR             | ALICE       | e.g. futur<br>e+e-: ILC | ATLAS HL-LHC<br>Outer layer | ATLAS HL-LHC<br>Inner layer |

|------------------------|------------------|-------------|-------------------------|-----------------------------|-----------------------------|

| Fluence<br>[neq.cm-2]  | 10 <sup>12</sup> | $2.10^{13}$ | 10 <sup>12</sup>        | 2.10 <sup>15</sup>          | 2.10 <sup>16</sup>          |

| TID [MRad]             | 0.2              | <3          | 0.4                     | 100                         | 1000                        |

| Timing [ns]            | ~200000          | 20000       | O(1000)                 | 25                          | 25                          |

| Hit rate<br>[kHz.mm-2] | 4                | 10          | 250                     | 1000                        | 10000                       |

## **DMAPS CMOS Community**

Collaboration of ~25 institutes (european project STREAM)

Many technologies tried, but focus last ~3 years has been on: AMS/TSI 180 nm, LF 150 nm, and TJ 180nm

## CMOS sensor development lines

#### Monolithic sensors with electronics all in one!

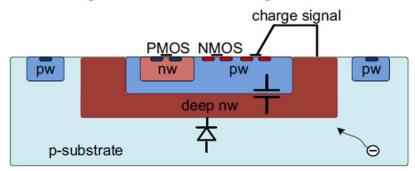

(a) large electrode design

- LFoundry 150 process (or AMS/TSI 180)

- <u>Pros</u>:

- Full CMOS

- Uniform field, short drift distance  $\rightarrow$  radiation hardness (TID & NIEL), 2.10<sup>15</sup> n<sub>eq</sub>.cm<sup>-2</sup> proven

- HV rev. bias > 300V possible

- BS thinning and processing possible

- Cons:

- Deep nwell Q collection → big Capacitance

(>200 fF) → noise, power & crosstalk

- I. Peric, DOI: 10.1016/j.nima.2007.07.115

- T. Kishishita, et al., DOI: 10.1088/1748-0221/10/03/C03047

- P. Rymaszewski, et al., DOI: 10.1088/1748-0221/11/02/C02045

- T. Hirono, et al., DOI: 10.1109/NSSMIC.2016.8069902

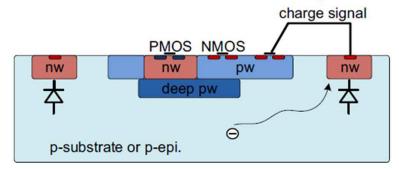

(b) small electrode design

- TowerJazz 180 process

- Pros:

- Full CMOS

- Small capacitance (<10fF) → low noise, less crosstalk & low power.

- Thin detector possible.

- Cons:

- Limited depletion, long drift distance, low field region → radiation hardness TBD

R. Turchetta, et al., DOI: 10.1016/S0168-9002(00)00893-7 W. Dulinski, et al., DOI: 10.1109/TNS.2004.832947 A. Dorokhov, et al., DOI: 10.1016/j.nima.2010.12.112 M. Havránek, et al., DOI: 10.1088/1748-0221/10/02/P02013

- 1- Introduction

- 2- TJ 180 nm TJ-Monopix development

- 3- LF 150 nm LF-Monopix development

- 4- Conclusion

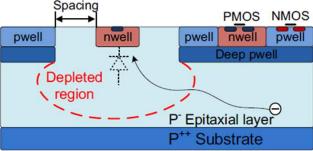

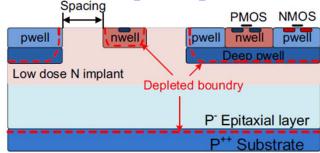

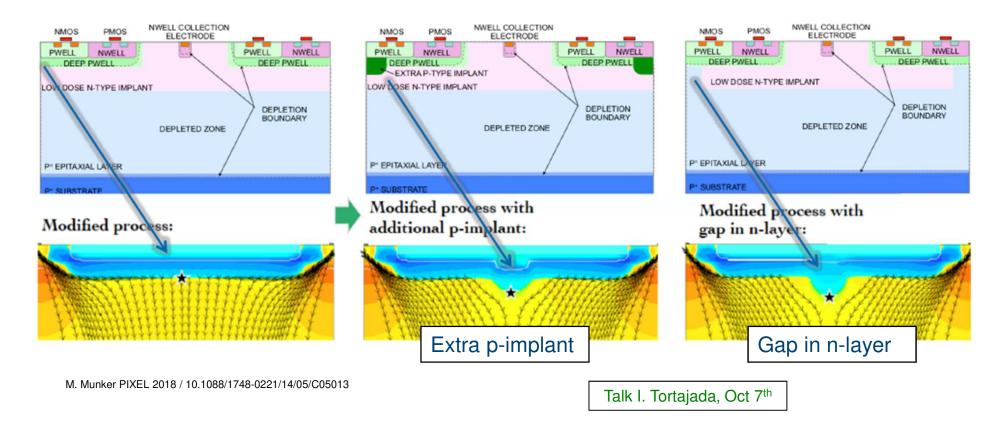

### TJ 180nm: process modification

- A small electrode design:

- Small pixel size (< 50 μm²)</li>

- Low capacitance (<3 fF)</li>

- Low power

- Reduced digital-analog Xtalk

Collection electrode

Analog part

Digital part

- ... but suffers from limited radiation-hardness → Requires process modification!

- Standard TJ 180 nm Process:

- High resistivity p-type epi layer (>  $1k\Omega.cm$ )

- Depleted region stays limited (in particular after irradiation)

- ALPIDE-like

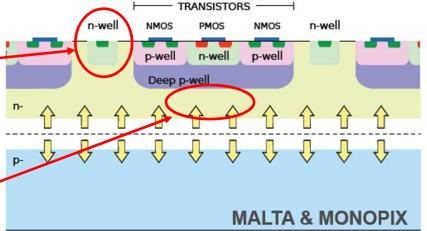

- Modified TJ 180 nm Process:

- Additional n- implant → full depletion possible

- Keeps small capacitance & no big changes to electronic layout

- MALTA / MONOPIX

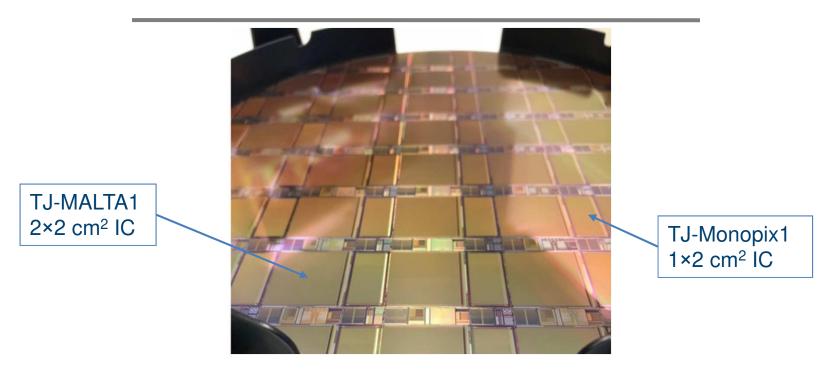

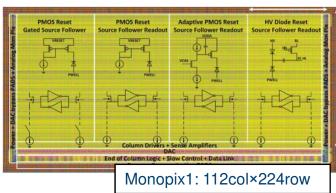

## TJ: The Digital Architectures

- 2 approaches have been followed:

- TJ-Malta1:

- Asynchronous readout: high hit rate, fast signal response, very low power

- → Lead to TJ-Malta2 developments.

Talk I. Tortajada, Oct 7th

- TJ-Monopix1:

- Synchronous readout (a la FE-I3 IC): column drain architecture, ToT measurement

This talk

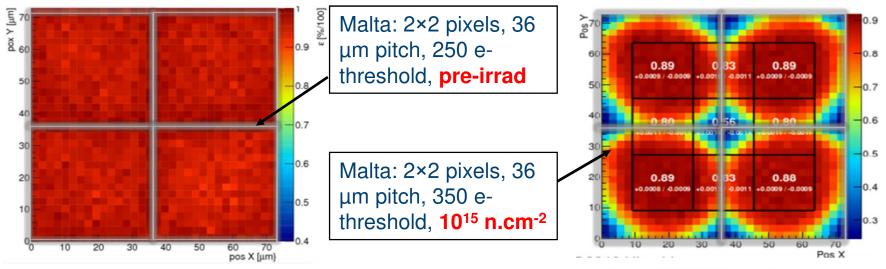

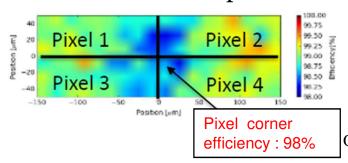

## Loss of efficiency in corners

The field configuration under the DPWell far from the collection electrode is the issue:

- Requires full depletion under DPW

- Need transversal field components in corners → proposition of extra process modification(s)

- Operation at low threshold essential

## Process optimization for radiation hardness: MiniMALTA

- several possibilities found:

- Deep p well extra implant.

- Gap in n-type implant.

Change field configuration under DPW to "push" charges towards collection electrode

##

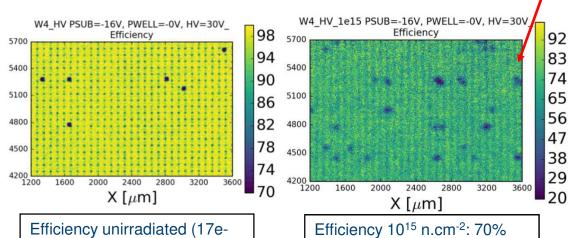

- Fully functional, but efficiency drop after irradiation.

ENC / 350 e- threshold): 97%

#### TJ-Monopix2:

- Full-scale small-collection diode with improved charge collection.

(23 e- ENC / 570 e- thresh.)

- Decrease minimal threshold.

- Joint TJ-Malta + TJ-Monopix submission!

- Design on-going, final verification on-going (1st mock layout already sent to founder...).

## TJ-Monopix2 sensor

Kostas Moustakas

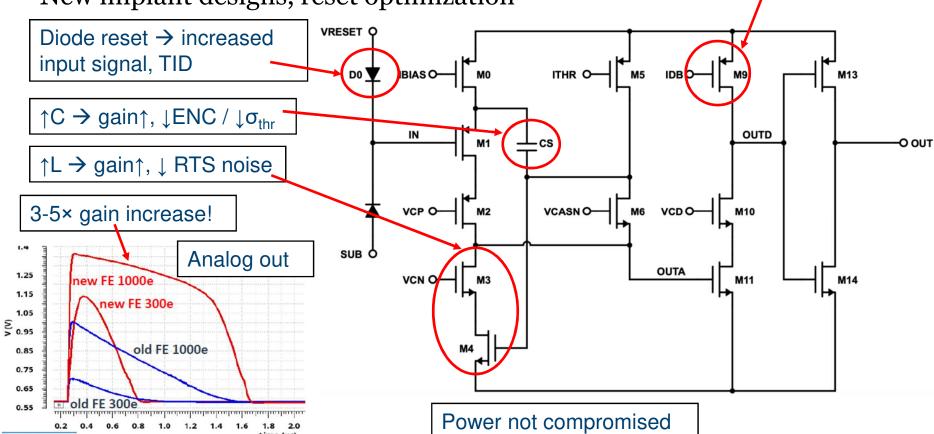

## TJ-Monopix2 FE

3-bit threshold tuning

- Low threshold operation crucial! → New FE design for higher gain and less noise.

- Threshold adjustment on pixel level.

- New implant designs, reset optimization

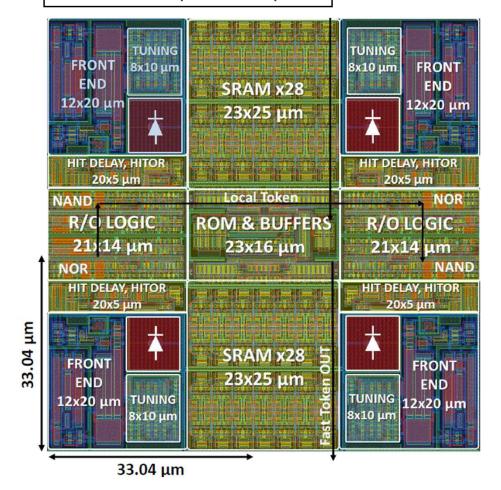

#### The TJ-Monopix2 2×2 pixel

- $\rightarrow$  Built as 2×2 core (area  $\downarrow$ )

- → Readout Logic based on Column Drain architecture a la FE-I3

- → 7-bit BCID Time-Stamp

- → Fast token: Internal token ring & group token

- → Propagation delay reduced from >100 ns to 35 ns

- → Does not impact readout speed (< 50 ns)

- → Readout logic improvements to mitigate timing issues related to READ slope

- → Hit delay through column for compensation of BCID propagation time

- → 4 flavors: Normal, Cascode, HV, HV Cascode

- → Modular 8-bit DAC, 32 column grouping for voltage drop compensation

- → LVDS TX, RX designed for 5 Gbps

- $\rightarrow$  Power:

- → 4 domains: Matrix Analog, Matrix Digital, DAC, Digital Periphery

- → Matrix analog: ~90 mW.cm<sup>-2</sup>

- → BCID distribution: ~80 mW.cm<sup>-2</sup>

- → Periphery: ~ 60 mW

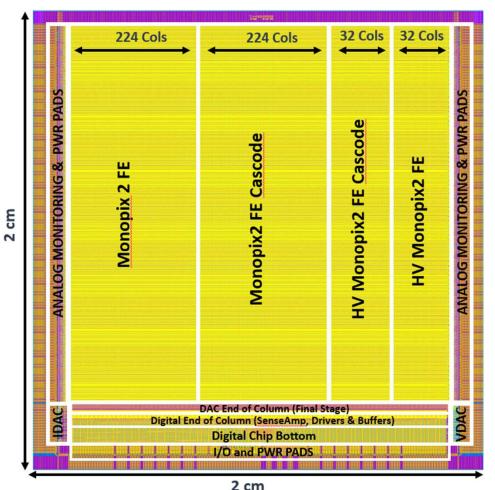

## TJ-Monopix2 Chip Overview

|                         | TJ-Monopix1                       | TJ-Monopix2                                       |

|-------------------------|-----------------------------------|---------------------------------------------------|

| Chip Size               | 1x2 cm <sup>2</sup> (224x448 pix) | 2x2 cm <sup>2</sup> (512x512 pix)                 |

| Pixel size              | 36 × 40 μm²                       | 33.04 × 33.04 μm²                                 |

| Noise                   | ≅ <b>11 e</b> ⁻                   | < 10 e <sup>-</sup> (improved FE)                 |

| LE/TE time stamp        | 6-bit                             | 7-bit                                             |

| Threshold<br>Dispersion | ≅ 30 e⁻rms                        | < 15 e <sup>-</sup> rms<br>(improved FE + tuning) |

| Minimum<br>threshold    | ≅ <b>300</b> e⁻                   | < 100 e-                                          |

| In-time threshold       | ≅ 400e⁻                           | < 150 e <sup>-</sup>                              |

| Efficiency (epi)        | $\cong$ 70 % (irradiated)         | > 95% (irradiated)                                |

\* Expectations

→ Submission TJ-MALTA2 + TJ-MONOPIX2 mid-October!

- 1- Introduction

- 2- TJ 180 nm TJ-Monopix development

- 3- LF 150 nm LF-Monopix development

- 4- Conclusion

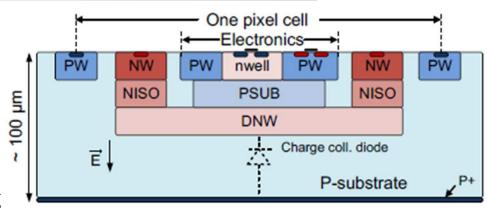

### LF DMAPS development line

- A large collection diode design:

- LF 150 nm process

- Multiple nested wells

- 6 metal layers + thick top

- Substrate resistivity >  $2k\Omega$ .cm

- Backside thinning and processing

#### Several prototypes:

- Pixel size: 33×125 μm<sup>2</sup>

- Chip size: 5×5 mm<sup>2</sup>

Fast Readout with FE-I4

- Thickness: 750/300/100 μm

- Pixel size: 50×250 μm²

- Chip size: 10×10 mm<sup>2</sup>

- Fast Readout with FE-I4

- Thickness: 750/300/100 μm

LF-CPIX (subm. Feb.16)

LF-Monopix1 (subm. Aug.16)

- Pixel size: 50×250 μm<sup>2</sup>

- Chip size: 10×10 mm<sup>2</sup>

Monolithic: Includes

Column Drain Readout.

Thickness: 750/300/100 μm

$M. \ Barbero \ et \ al. \ doi.org/10.1088/1748-0221/15/05/P05013$

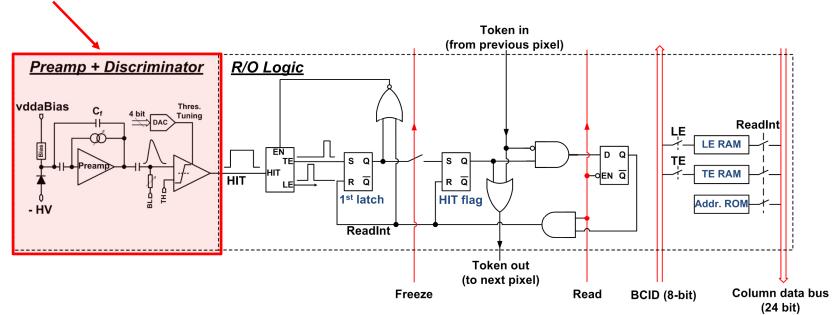

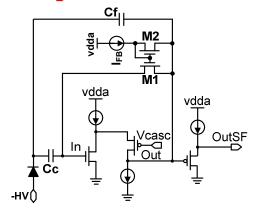

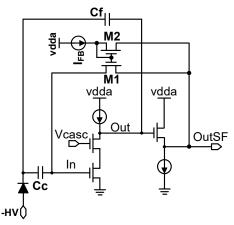

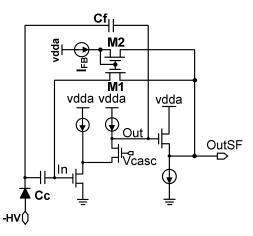

## Focus on LF-Monopix1 analog FE

The analog FE uses a Charge Sensitive Amplifier

- Gain independent of large C<sub>detector</sub>? (~400 fF here!)

- $\rightarrow$  Small C<sub>f</sub> as G ~ 1/C<sub>f</sub> (C<sub>f</sub> ~ 5fF)

- $\tau_{CSA} \alpha \frac{c_D}{g_m \cdot c_f}$  and  $ENC^2 \alpha \frac{kT c_D^2}{g_m \tau}$ Need a large  $g_m$  for these large  $C_D$ !

- Threshold trimming a must (4 bits in-pixel)

Power: ~40 µW/pix in LF-Monopix1

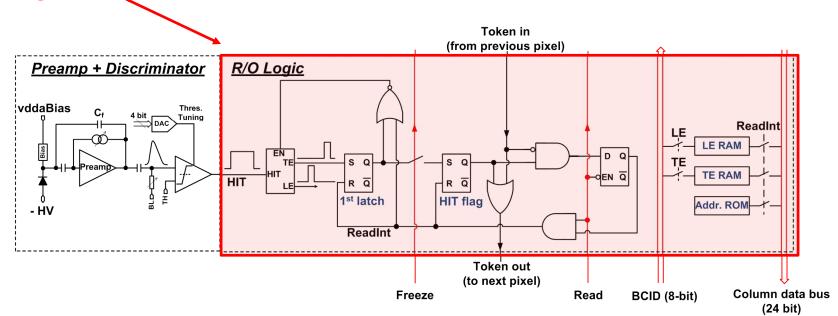

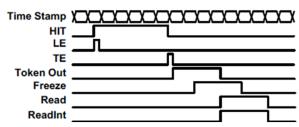

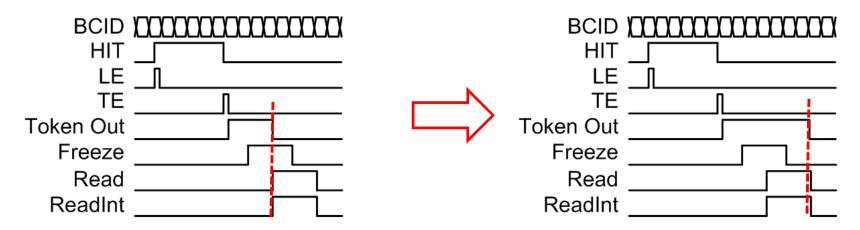

## Focus on LF-Monopix1 digital FE

• The digital FE is based on Column Drain Architecture

- It provides 8-bit ToA and ToT

- Full custom design:

- to minimize area and  $C_{\text{digital}}$

- Low noise design for critical digital blocks

(e.g. current steering logic)

T. Wang, et al., DOI: 10.1088/1748-0221/12/01/C01039

P. Rymaszewski et al., DOI: http://doi.org/10.22323/1.313.0045 v

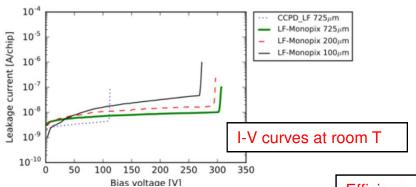

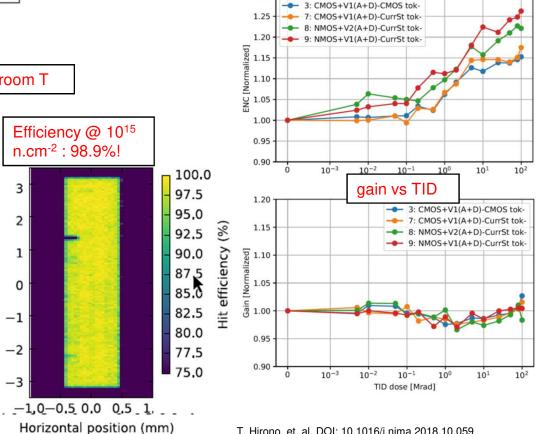

## LF-Monopix1 performances

Vertical position (mm)

- High breakdown voltage >250 V

- Improved wrt previous designs

15-25% ENC ↑ / < 5% gain ↓

**ENC vs TID**

J. Liu, et al, DOI: 10.1088/1748-0221/12/11/C11013 I. Caicedo et. al, DOI: 10.1088/1748-0221/14/06/C06006

High & uniform efficiency after 10<sup>15</sup> n.cm<sup>-2</sup>

- Bias -130V, dry ice cooled

- Thres. ~1700 e-

- 0.2% masked pixels

T. Hirono, et. al, DOI: 10.1016/j.nima.2018.10.059

##

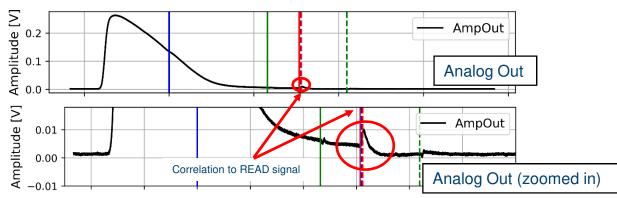

#### LF-Monopix1:

- Fully functional, high efficiency after 10<sup>15</sup> n.cm<sup>-2</sup>.

- ... but: found (small) crosstalk correlated to digital read signal → can generate spurious signals

- Issue understood (layout)

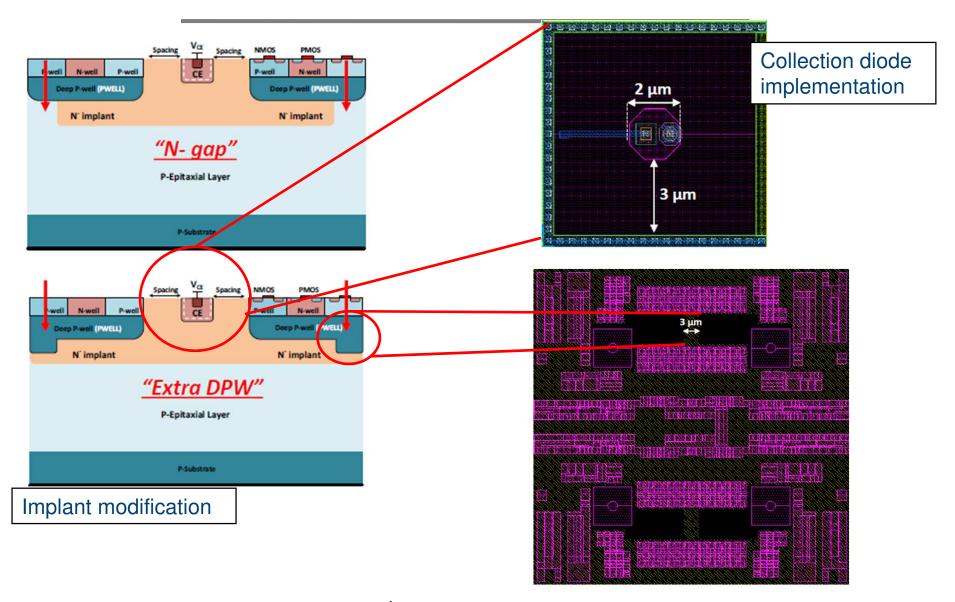

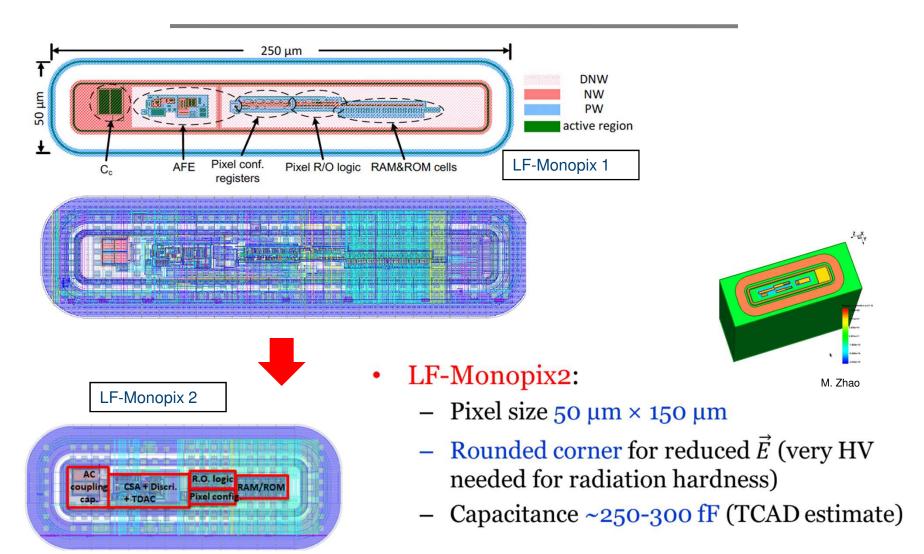

#### LF-Monopix2:

- Improved logic and layout (READ signal related → Xtalk reduction)

- BCID propagation better and better Column reading.

- Detector capacitance reduction (for better SNR)

- Lowering of pixel power consumption (preamp and comparator)

- Improved discriminator (faster, better match to 6-bit ToT)

- → Submitted June 2020!

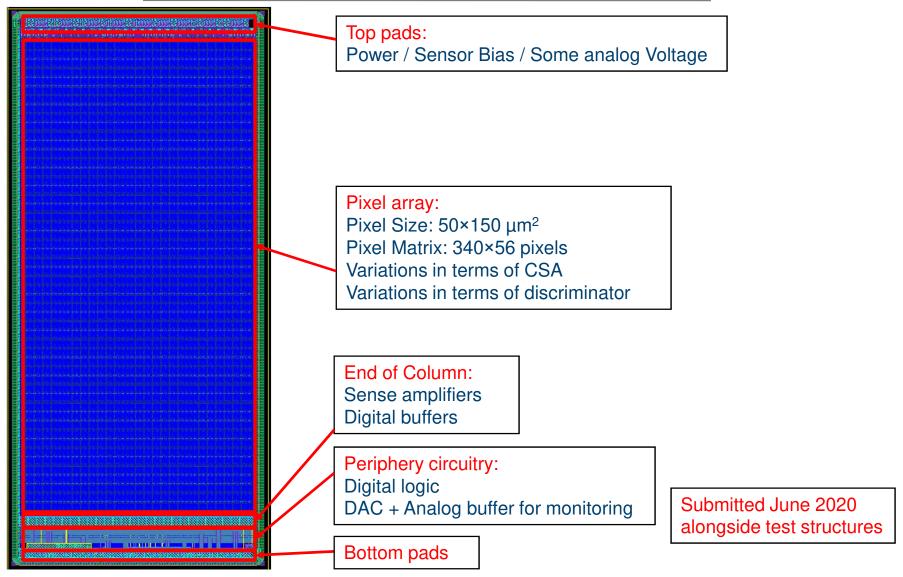

## LF-Monopix2 sensor / pixel layout

## LF-Monopix2: Analog FE

Explores several CSA flavors:

CSA 1 (a la LF-Monopix1) Folded cascode

CSA 2 Telescopic cascode SF in DC feedback loop

CSA 3 Open loop gain vs BW SF in DC feedback loop

- Try also lower C<sub>f</sub> for higher CSA gain, mitigates discriminator dispersion

- Explores 2 discriminators:

- 1<sup>st</sup>: a la LF-Monopix1

- 2<sup>nd</sup>: Bring improvements to discriminator design for better timing

## READ crosstalk fixing

- Was related to the fact the token was cleared by the READ rising edge, which led to switching during READ...

- Change logic to clearing on READ falling edge.

Solution makes longer read cycle, but avoids unnecessary digital switching during read...

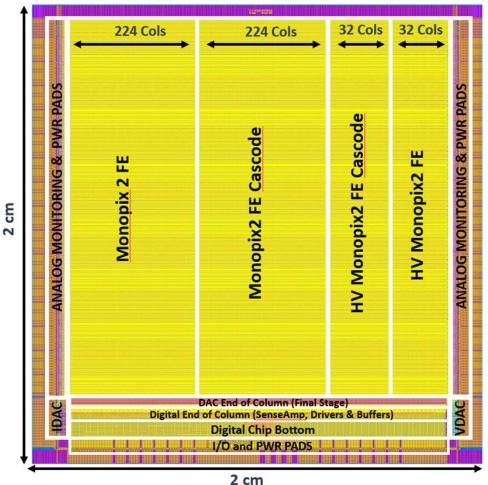

## LF-Monopix2 Chip overview

## LF-Monopix2 Chip overview

|                                                 | LF-Monopix1                 | LF-Monopix2                             |

|-------------------------------------------------|-----------------------------|-----------------------------------------|

| Pixel size                                      | 50 × 250 μm2                | 50 × 150 μm2                            |

| Cd                                              | ~ 400 <u>fF</u> (estimated) | 250 – 300 <u>fF</u> (estimated)         |

| Analog Power/pixel (CSA + <u>Discri</u> .)      | 15 μΑ + 5 μΑ = 20 μΑ        | 10 μΑ + 2 μΑ = 12 μΑ                    |

| Noise                                           | ~200 e-                     | 100 ~ 150 e <sup>-</sup>                |

| LE/TE time stamp                                | 8-bit                       | 6-bit                                   |

| <u>ToT</u> @ 6 <u>ke</u> -                      |                             | 200 – 250 ns                            |

| Max. <u>ToT</u>                                 |                             | 400 ns                                  |

| p-p ( <u>rms</u> ) <u>thres</u> .<br>dispersion | (~ 100 e <sup>-</sup> )     | 800 e <sup>-</sup> (80 e <sup>-</sup> ) |

| Min. threshold                                  | 1500 e <sup>-</sup>         | 1000 e <sup>-</sup>                     |

| In-time threshold                               | ~ 2000 e-                   | 1500 e <sup>-</sup>                     |

Submitted June 2020 alongside test structures

### Conclusion

- 1- Introduction

- 2- TJ 180 nm TJ-Monopix development

- 3- LF 150 nm LF-Monopix development

- 4- Conclusion

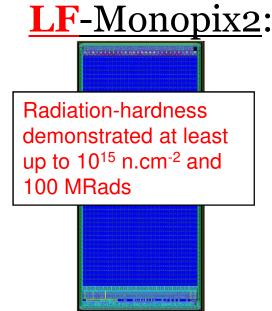

## The Monopix2 development

Out of ITk (challenging schedule)  $\rightarrow$  interesting for post-ITk applications ... e+e- environments or future hh ...

Talk C. Gemme, Oct 6th

## **IJ**-Monopix2: Small pixels, low capacitance, low power design

2×2 cm<sup>2</sup>, 512×512 pixels, 33×33 μm<sup>2</sup> New implants for better charge collection after irrad, lower threshold Submission foreseen October 2020

2×1 cm<sup>2</sup>, 340×56 pixels, 50×150 μm<sup>2</sup> Analog and digital FE improvements Smaller pixels, better layout Submitted in June 2020

→ Back Dec. 2020

#### **Thanks**

• Many slides / original material / results borrowed from many colleagues:

Tomasz Hemperek, Magdalena Munker, Kostas Moustakas, Patrick Pangaud, Heinz Pernegger, Walter Snoeys, Tianyang Wang, Norbert Wermes... and more...

<u>University of Bonn</u>: C. Bespin, I. Caicedo, J. Dingfelder, T. Hemperek, T. Hirono, F. Hügging, H. Krüger, K. Moustakas, P. Rymaszewski, T. Wang, N. Wermes, S. Zhang

UNIVERSITÄT BONN

<u>CERN</u>: I. Berdalovic, R. Cardella, V. Dao, L. Flores, T. Kugathasan, H. Pernegger, F. Piro, P. Riedler, E. Schioppa, C. Solans, W. Snoeys, C.M. Tobon

Centre de Physique des Particules de Marseille: M. Barbero, P. Barrillon, S. Bhat, P. Breugnon, Z. Chen, A. Habib, P. Pangaud, A. Rozanov

IRFU CEA-Saclay: Y. Degerli, F. Guilloux, F.J. Iguaz, P. Schwemling