# Development of the thin and fine-pitch silicon strip detector aiming for the Belle II upgrade

K.R. Nakamura, E. Hamada, K. Hara, T. Kishishita, M. Miyahara, T. Tsuboyama High Energy Accelerator Research Organization (KEK), Tsukuba JAPAN

The 29th International Workshop on Vertex Detectors (Virtual VERTEX2020)

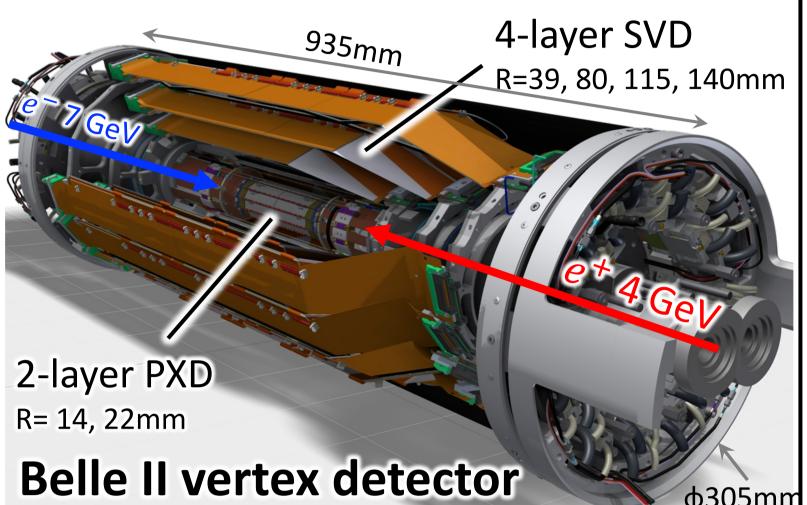

### Belle II and vertex detector

- The vertex detection in the Belle II experiment is essential for the time-dependent CP violation measurement.

- Currently, the Belle II vertex detector consists of

- inner 2-layer Si pixel detector (PXD): DEPFET sensors

- outer 4-layer Si strip detector (SVD): DSSD sensors

- One big concern for the future operation is harsh beam background from the SuperKEKB accelerator, which can eat up the safety factors of the radiation tolerance of the detectors.

- Moreover, some SVD features can be improved for better physics performance.

- Material budget, Position resolution in N-strips, Level-1 trigger latency

#### **SVD DSSD large sensor (HPK)**

| Sensor size                             | 125 mm x 60 mm |        |  |

|-----------------------------------------|----------------|--------|--|

| Thickness                               | 320 μm         |        |  |

| Readtout (RO)                           | P-side         | N-side |  |

| RO strip pitch                          | 75 μm          | 240 μm |  |

| RO strip num.                           | 768            | 512    |  |

| RO and floating are on alternate strips |                |        |  |

# Thin/fine-pitch Si strip detector

#### The vertex detector upgrade is under discussion to improve the radiation tolerance and the performance. (see the talk of [B03] by J. Boydet)

In our project, we are developing new DSSD detector to upgrade SVD.

Target hit-rate tolerance: 10 MHz/cm<sup>2</sup>

Target detector performance:

- smaller material budget < 0.7% X<sub>0</sub> / layer

- Position resolution ( $\theta$ =0) < 20  $\mu$ m (TBC with MC)

- Level-1 trigger latency > 8.0 μs

Target radiation tolerance: TID: 10 Mrad, NIEL: 2.5 x 10<sup>13</sup> neq/cm<sup>2</sup>

Concept is thin and fine-pitch DSSD for a small material budget, a high rate tolerance, and a good position resolution.

## Thin/fine-pitch DSSD development

- The prototype DSSD design:

- 140  $\mu m$  thickness (c.f. current DSSD thickness is 320  $\mu m$ .)

- 50 μm (p) / 75 μm (n) pitch

- Reduction of material budget from 320 μm to 140 μm Si :

$\Delta = 0.19\% X_0 / layer$

- Very rough estimation of position resolution :  $50 \mu m / \sqrt{12} =$

- 14.4 μm (p-side)

- Production company:Micron

- Sensor mask design is completed.

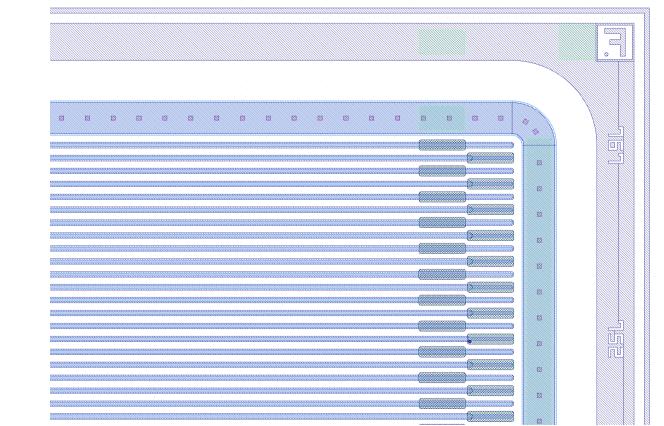

## DSSD n-side mask layout

#### **DSSD** sensor design (Prototype)

|              | •                 | , , ,  |

|--------------|-------------------|--------|

| Sensor size  | 52.6 mm x 59.0 mm |        |

| Active area  | 51.2 mm x 57.6 mm |        |

| Thickness    | 140 μm            |        |

| Substrate    | N-type            |        |

|              | P-side            | N-side |

| Strip pitch  | 50 μm             | 75 μm  |

| Strip number | 1024              | 768    |

No floating strip. P-strips and N-strips are orthogonal.

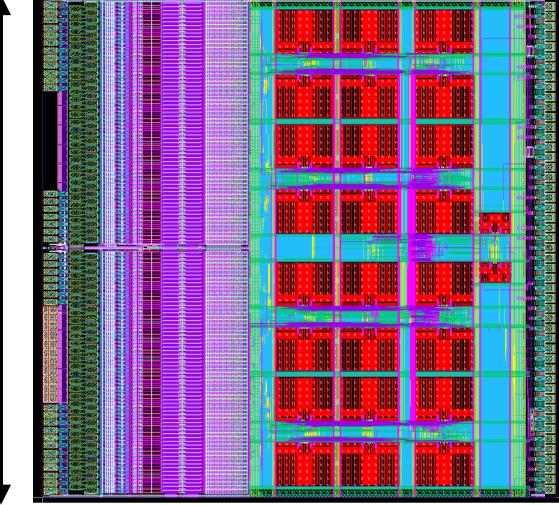

## Development of front-end ASIC

Requirements on front-end ASIC

- Readout of binary hit information, to minimize the number of cables.

- Short pulse width < 100 ns, to avoid signal pile-up</li>

- Small noise < 900 e-, due to smaller signals from thin sensor

- Fast clock sampling, for good time resolution to separate the beam background hit

AIN[127]

#### Prototype ASIC: SNAP128A

- SNAP128 is developed based on 'SliT' chips, which are for silicon tracker of J-PARC g-2 experiment.

- 180nm CMOS

- 128ch inputs / chip

- 127MHz sampling of binary hit information after discriminator

- Hit time resolution: ~7.9ns

- Contain 2k-depth memory in each channel

- Maximum trigger latency : 15.8 μs

- Estimated total power-consumption : 363 mW / chip

- ASIC design is finalized.

#### Analog part

- CSA+PZC / CR-RC shaper / discriminator

- bi-polar (readout for pand n-side)

- Optimize the design to achieve a short pulse width and small noise

- pulse width: 55 ns

- noise : 640 e- (@ 12pF)

## Design of SNAP128A

6120 um

Input charge: 9000 e<sup>-</sup>

RC-extracted model

Detector capacitance [pF]

Simulated shaper output

schematic model

RC-extracted model

positive signal (p-side)

about 55nsec

@ 25% pulse height

Input charge: 9000 etime [ns]

####

## Plan for the next

Detector capacitance [pF]

The prototype DSSD sensor and SNAP128A will be produced by Mar 2021.

**RC-extracted model**

- Using those prototype, test modules will be assembled by the next summer to measure the detector performance.

- From the results, we will decide the final specification of the thin/fine-pitch silicon strip detector.

- Still many things to be done:

- Detector mechanics, cooling, back-end electronics, so on...

- The target completion time of the new detector production: in 2026