#### Fermilab **ENERGY** Office of Science

# **LGADs for 5D Tracking**

Ronald Lipton

Fermilab

- Contributing to aspects of this work - A. Apresyan, R. Heller, G. Gabriele, M. Mannelli, R. Islam, C. Wei, A. Tricoli

### Introduction

We describe simulation studies of double sided (inverted) low gain avalanche diodes with small pixel readout on the cathodes. This configuration has the potential to provide 5D (X, Y, Z, T, $\theta$ ) tracking information. The concept utilizes:

- 3D integration of electronics for fine pitch, low capacitance pixels and complex on-sensor processing

- Double sided LGADs to provide a distinctive pulse shape and "time expansion" due to slower hole drift

- Substrate engineering with epitaxial and buried layers to allow separate tuning of drift and avalanche fields

Interest in angle information is motivated by the current CMS track trigger stub concept and possible future FCC-hh and muon collider background reduction applications

This work is based primarily on Silvaco TCAD studies – there is some work shown from an ongoing FNAL/BNL collaboration to study buried layer LGADs

# LGADs / AC LGADs

Low gain avalanche diodes now being used for timing layers for CMS and ATLAS have excellent timing capability. But:

- Current versions must have large pixels large due to the areas needed for HV edge termination

- They are not very radiation hard due to low density implants

AC-LGADs solve the pixel size problem by adding Gabriele Giacomini et al resistive and capacitive layers and moving the edge terminations from the pixels to the edge of the device.

- Must still be bump or 3D bonded to the readout electronics

- Pixel size and resolution determined by the resistance of the n<sup>+</sup> layer and capacitance from n<sup>+</sup> to the AC pads.

🛠 Fermilab

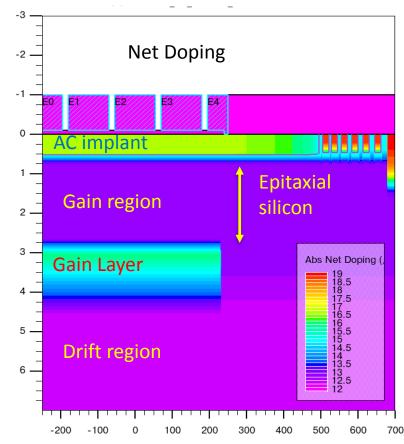

# **Buried Layers**

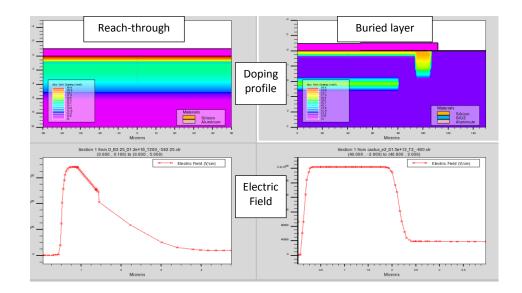

The current generation of LGADs utilize "reach -through" deep implants to provide the high-field gain layer.

- Depth defined/limited by the energies of the implants

- Radiation hardness limited by acceptor removal – related to the gain layer doping density

One can gain flexibility by depositing or implanting a gain dopant, then adding a lightly doped gain layer by epitaxy or wafer bonding.

- Separate control of width and depth of dopant layer

- Can be deposited by implantation or graded epitaxy

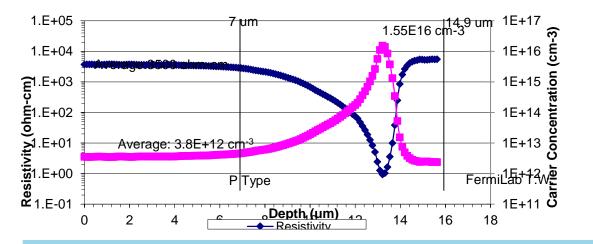

Spreading resistance profile for a graded epitaxy test wafer (Lawrence semiconductor)

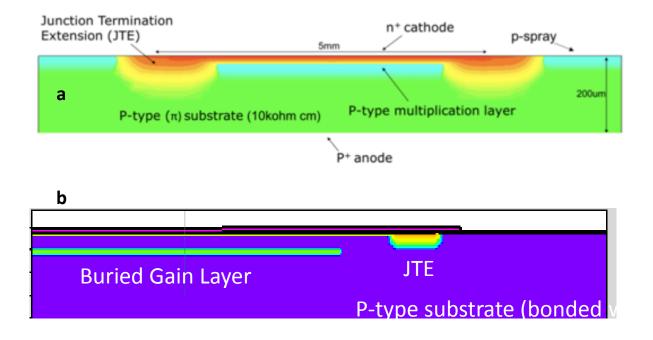

# **Buried Layers (2)**

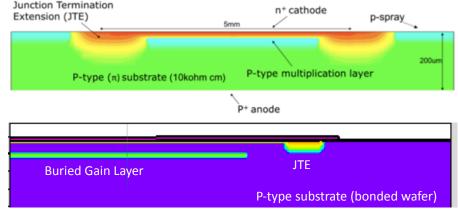

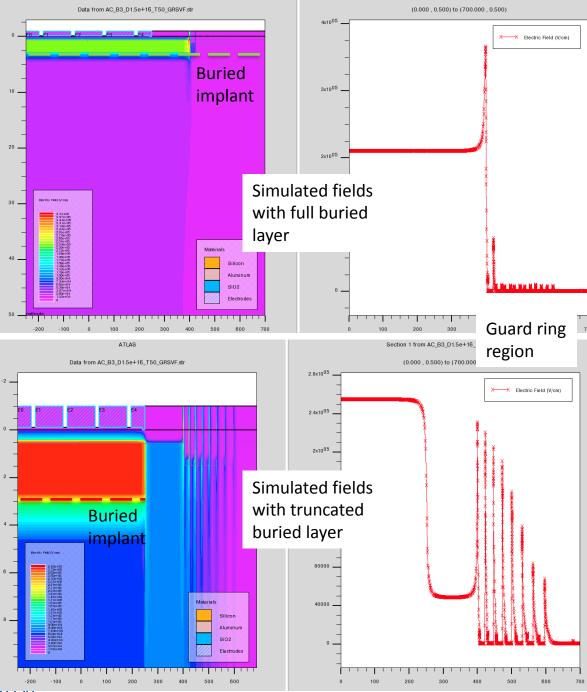

A uniform buried layer is the easiest to achieve by graded epitaxy, but it suffers from the same edge effects as reachthrough devices and a deep JTE implant would be needed. Patterning the implant avoids this problem.

Patterned implantation on the base wafer before epitaxy is more difficult to achieve due to the amorphization of the surface and resulting defects in the epitaxial layer. We see apparent stacking faults in our patterned test devices.

### Engineering the Substrate – Buried layers, epitaxy

6

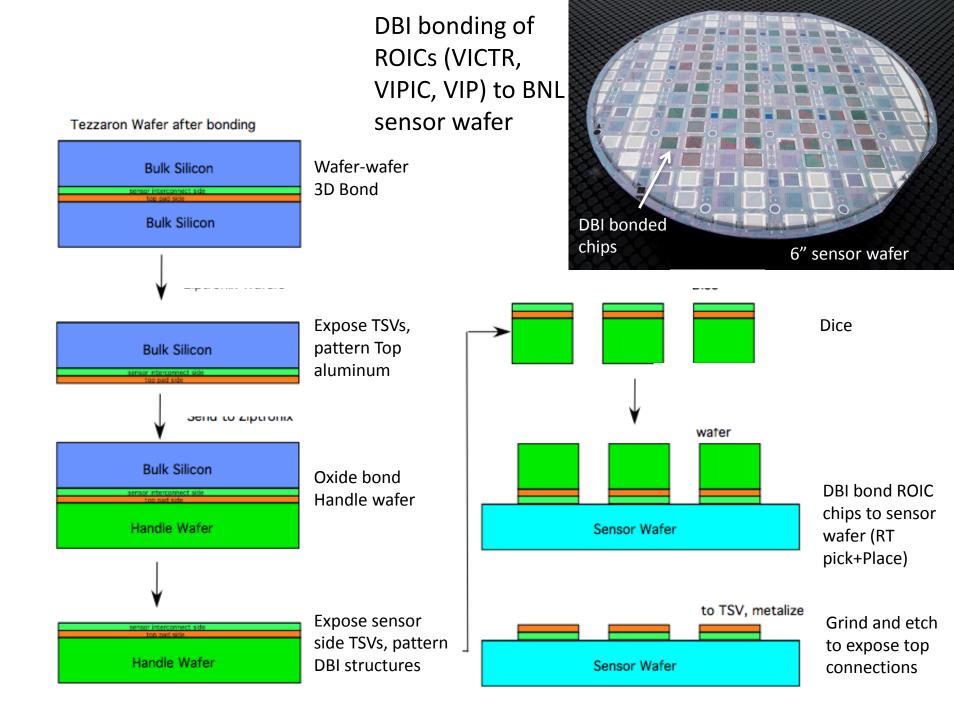

# **3D Integration (NOT 3D sensors)**

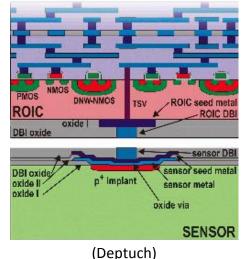

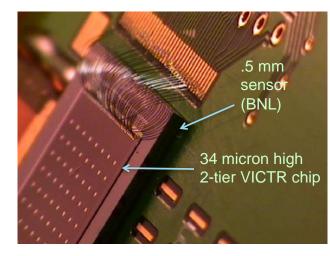

A three-dimensional integrated circuit (3D-IC) structure is composed of two or more layers of active electronic components using horizontal intra-tier and vertical inter-tier connectivity by Through-Silicon-Vias (TSVs). We pioneered this for HEP circa 2010-12.

- Very fine pitch (~3 micron)

- Can be rad hard

- Separate optimization of sensors and electronics

- Sensor optimized for speed and resolution (LGAD or CMOS)

- Multiple layers of electronics would allow processing of fields of pixels - important for angle and charge deposition extraction

Can be combined with MAPS, LGADs, active edge ... for optimal combined detector system with complex processing.

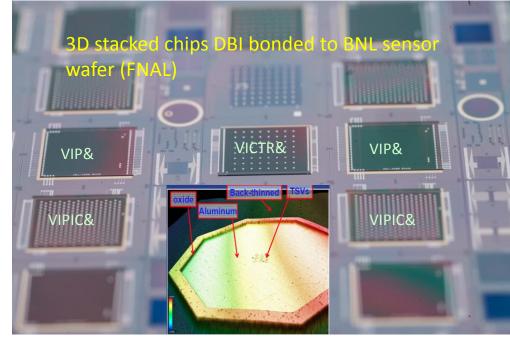

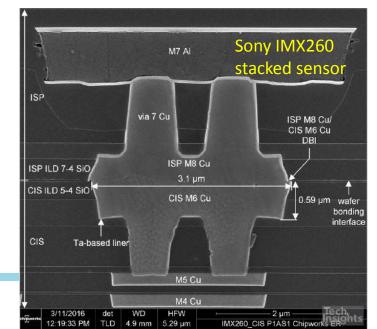

"Hybrid Bonding" now a standard technology ("almost all of the stacked CIS manufacturers or their foundries have HB available") DBI licensed to > 20 foundries.

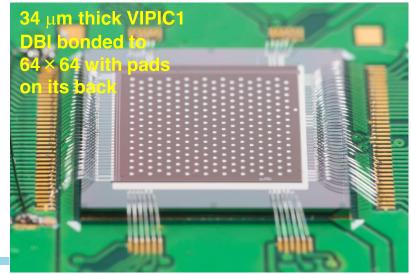

.5 mm sensor (BNL) 34 micron high 2-tier **VICTR** chip

Two layers of 130 nm **CMOS** electronics Connections from top (or edge)

#### **Possibilities and Challenges**

3D integration offers a number of possibilities

- Very fine pitch

- Multiple layers of electronics (analog/digital)

- Low noise (low capacitance interconnect, small pixels)

• Heterogeneous integration (different sensor, IC technologies in a stack)

Challenges

- Access/cost (Nhanced, MIT-LL, Tower/Jazz, Sandia. IZM ...)

- TSV integration (only from some foundries)

- Die-to-wafer bonding

- Multi-chip stack yield

- Design tools

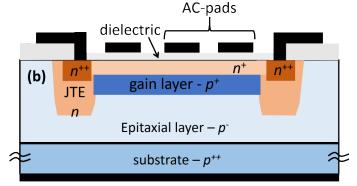

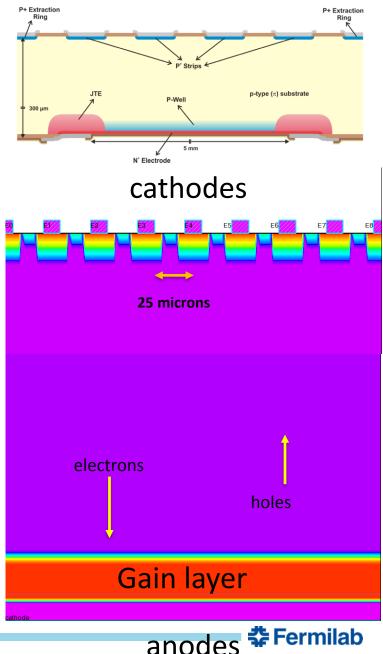

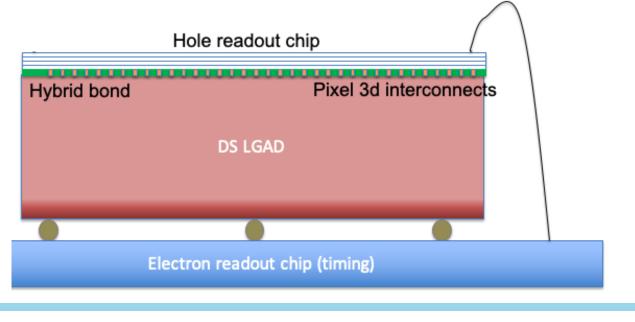

#### Double Sided (inverse) LGAD – Example of combining Technologies

Low Gain Avalanche Diode with fine pixels on the hole-collecting side (G. Pellegrini et al ...)

- Anode can provide timing with coarse pitch

- Lower total power and complexity

- Cathode subdivided into small pixels

- Records "primary" hole collection, then holes from gain region – double peak that reflects charge deposition pattern

- Lower power due to large signal from the gain layer

- Resulting current pattern can be used to measure angle and position.

- A thicker detector can be optimized to measure angle or charge deposit location at some sacrifice to time resolution

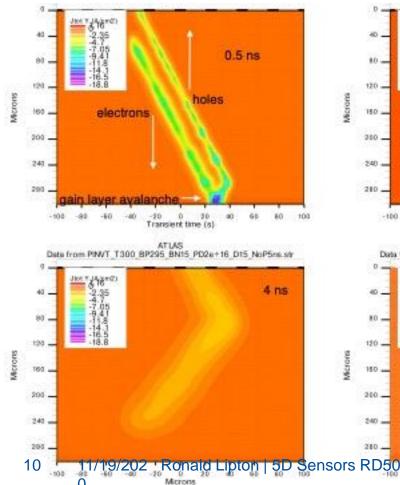

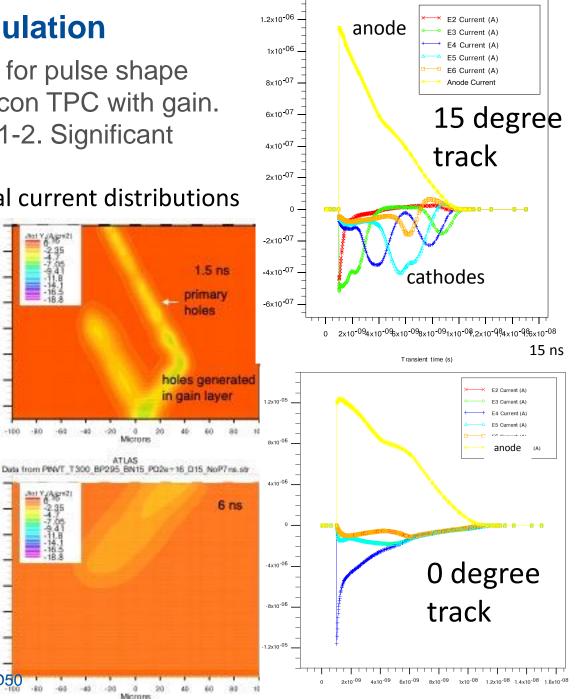

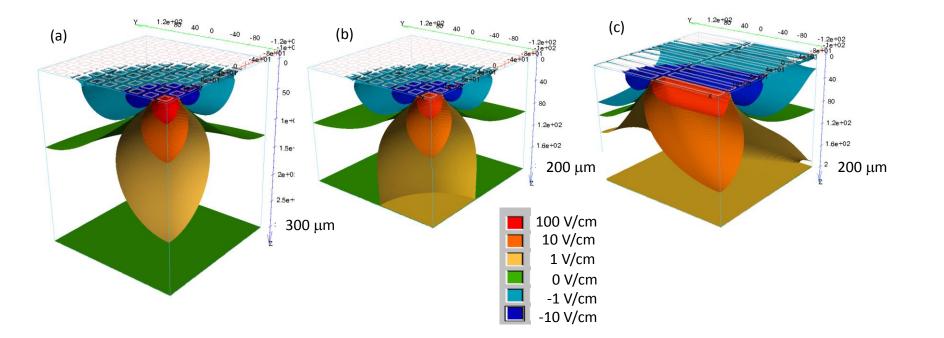

#### **Double Sided LGAD Simulation**

Use anode for timing, cathodes for pulse shape discrimination. Essentially a silicon TPC with gain. Time scale ~ 10 ns rather than 1-2. Significant diffusion.

#### 15 degree track detector internal current distributions

holes

ATLAS

Microns

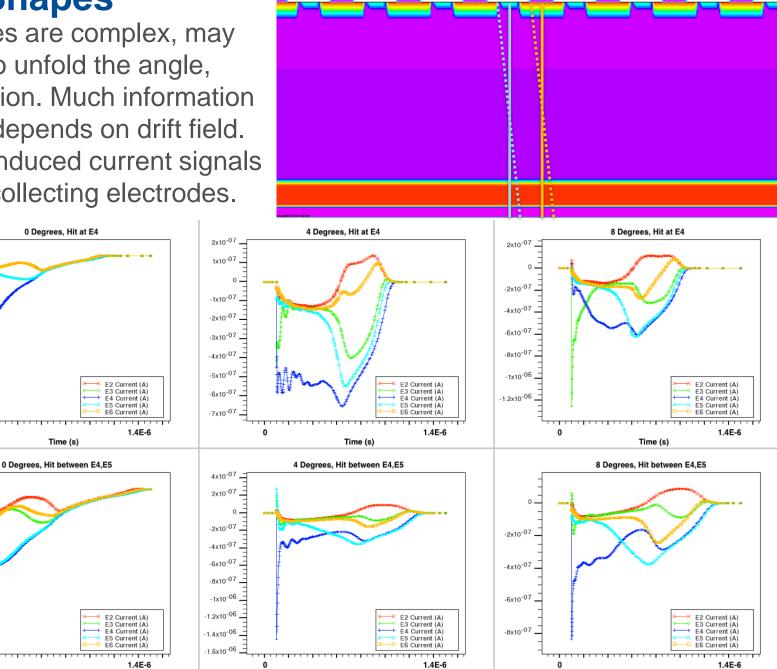

### **Pulse Shapes**

0

-2x10<sup>-06</sup>

-4x10<sup>-06</sup>

-6×10<sup>-06</sup>

-8×10<sup>-06</sup>

-1x10<sup>-05</sup>

-1.2x10<sup>-05</sup>

-1x10<sup>-06</sup>

-2x10<sup>-06</sup>

-3x10<sup>-06</sup>

4x10<sup>-06</sup>

0

Time (s)

0

Pulse shapes are complex, may be difficult to unfold the angle, impact position. Much information at 6-7 ns – depends on drift field. Significant induced current signals away from collecting electrodes.

Time (s)

F1

F2

E3

F4

E5

E6

Time (s)

F7

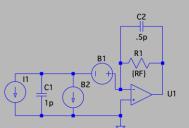

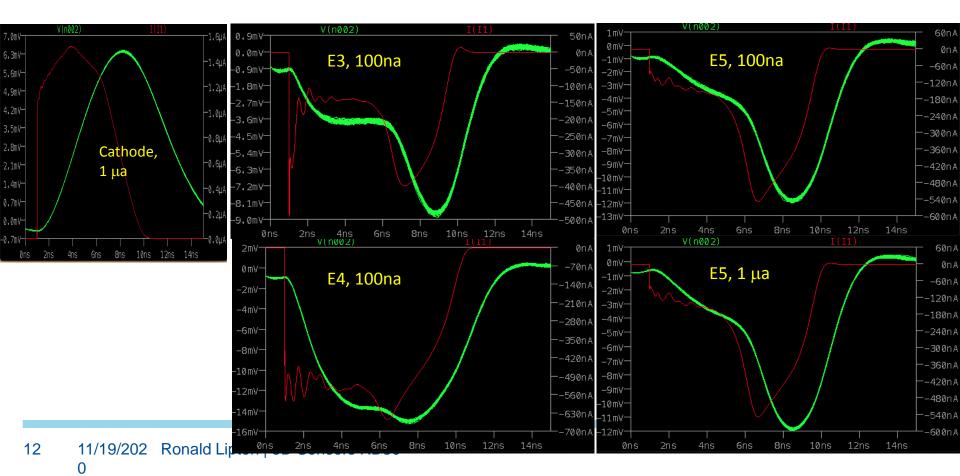

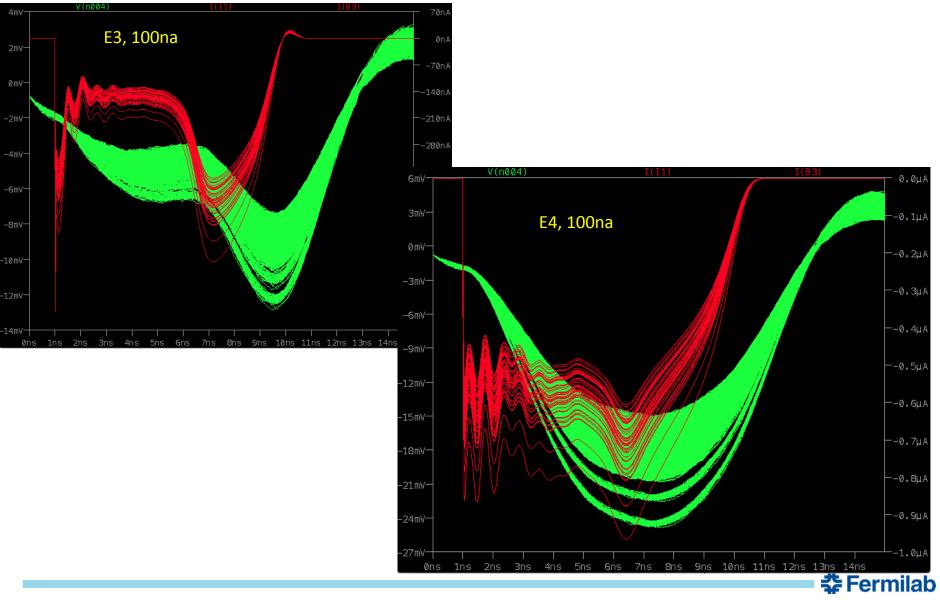

## **Estimating Amplifier Effects**

mW/cm<sup>2</sup>) + digital ...

Simple SPICE amp model using TCAD current shapes. Noise parameterized by front-end transistor transductance – 20 ff load – just a BOE estimate Front end transistor power – 16 mW/cm2 + disc (> 80

.param rm=5.31e7 .param qe=1.6e-19 .param gm=(qe]\*I(le])/(2\*{k}\*{T}) .param gam=.5 .param gam=.5 .param l=293 .param l=10e-6 .lib opamp.sub .param KF=5k .param kF=5k .param tstep=1/(2\*{FMAX}) .param isg=sqrt{[psd]\*{FMAX}} .param isg=sqrt{[psd]\*{FMAX}} .step param msceed 10 35 .5 .tran {tstep} 15n .noise V(n002) V(0) dec 100 100k 1000k

PWL file=/Users/ronlipton/Dropbox/Timing/PULSE/D4\_T300\_Cathode.txt V=sig\*(sqrt(-2\*ln(rand({mcseed}\*1e10\*time)))\*cos(2\*3.14159\*rand({mcseed}\*1.1e10\*time))) l=isig\*(sqrt(-2\*ln(rand({mcseed}\*1e10\*time)))\*cos(2\*3.14159\*rand({mcseed}\*1.1e10\*time)))

#### Implementation

- 3D Assembly with electron and hole ROICs

- This is similar to VICTR from the 2012 3D run using chip to wafer bonding

The geometry is admittedly awkward, the anodes must be AC coupled to isolate the bias voltage. Dead regions are needed for top-bottom interconnect. This could be limited to one edge.

🚰 Fermilab

#### Issues

This has been primarily a TCAD exercise to explore the concept. There are several outstanding issues

- The pulse shapes are complex the effort needed to reconstruct angle and accuracy of the results has not been established

- A thicker detector does not provide optimal time resolution.

- Power is an issue anytime one combines fast timing and high pixel density

- A possible low-ish power mode is to latch several waveform values of the cathode pulses based on an anode trigger with later pulse processing

- The viability of pattered buried layers has yet to be established

- Design optimization would depend on the final application.

- 3D assembly is complex and access limited I believe this will become easier over time (now limited by TSV insertion)

## **Current Work**

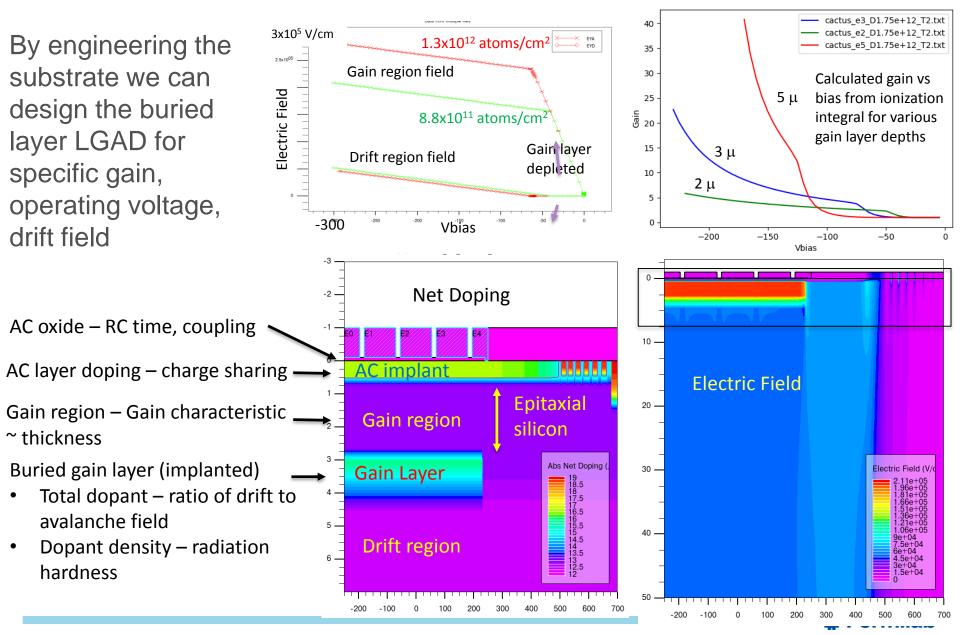

We (FNAL, BNL, Cactus Materials) are prototyping a buried layer device with

- 50  $\mu$  drift region FZ wafer Si-Si bonded to the substrate.

- Patterned gain layer implant removes need for junction termination extension

- 3-4 μ epitaxial gain region over gain layer

- AC coupling top layer

This design allows independent control of the depth of the gain layer; a thin, high density gain layer implant. Recently received a first batch.

## Summary

We have described a concept that utilizes 3D integration, substrate engineering and LGAD ideas to potentially reconstruct track angles as well as provide X,Y and time information.

- The buried layer concept has the potential to allow independent tuning of implant density, depth, and drift and gain fields.

- 3D integration allows for dense analog and digital circuitry for post-processing and readout

- The 5D LGAD is an example of combining these technologies.

Work is currently underway to explore patterned buried layers.

### **Include Landau Fluctuations of peak**

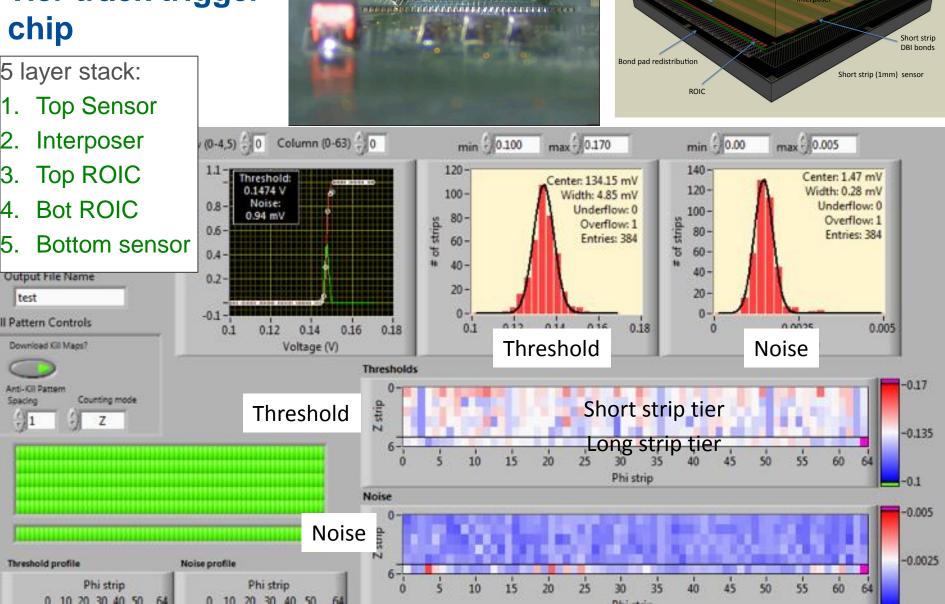

# **3D Test Results**

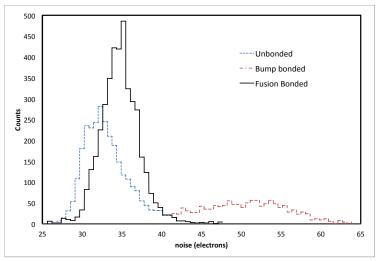

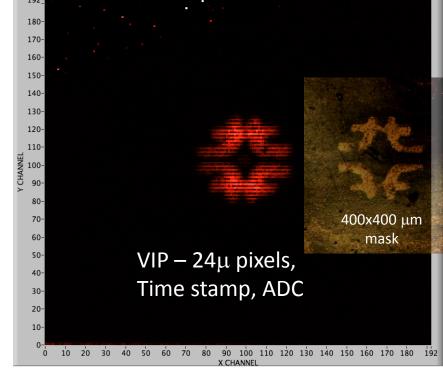

- All three 3D Chips worked VIP and VICTR tested on the bench. VIPIC was extensively tested in particle and x-ray beams.

- Yields were about 50% 3D bonding and multiple tier assembly

- VIP(ILC) is on hold no ILC R&D funds VICTR not relevant to current CMS design

For the VIPIC x-ray imaging chip we were able to compare noise of the oxide-bonded pixels to the same chip with bump bonds. The noise in the oxide bonded pixels is almost a factor of two lower than the conventionally bump bonded parts due to lower capacitance.

#### CD109 radiogram of tungsten mask

#### 3D Results – VICTR – CMS 5 Tier track trigger chip

Long strip (5mm) sensor

8 mi

Interposer

Bump

bonds

🛟 Fermilab

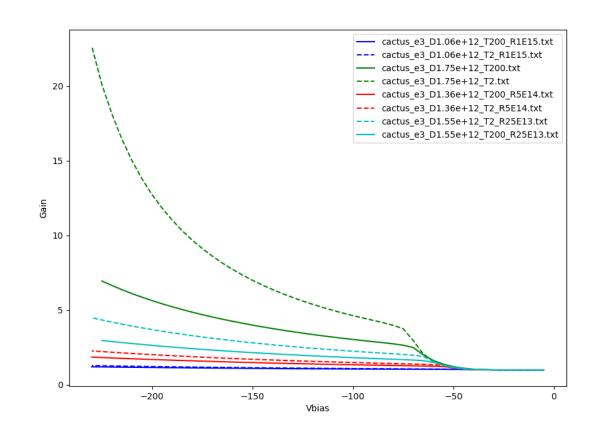

## Gain as a function of fluence

- Plot gain for different fluence values for high and low density gain layers with starting dose of 1.75x10<sup>12</sup>. All runs ended by compliance limit.

- cactus\_e3\_D1.36e+12\_T2\_R5E14

- D = Dose 1.75x1012 calculated acceptor removal

- T = Anneal time (minutes)

- R = Radiation fluence