First Thoughts on UT for Upgrade II

Yiming Li, Jianchun Wang, Quan Zou Institute of High Energy Physics, CAS

Mar 30<sup>th</sup>, 2020

### Introduction

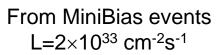

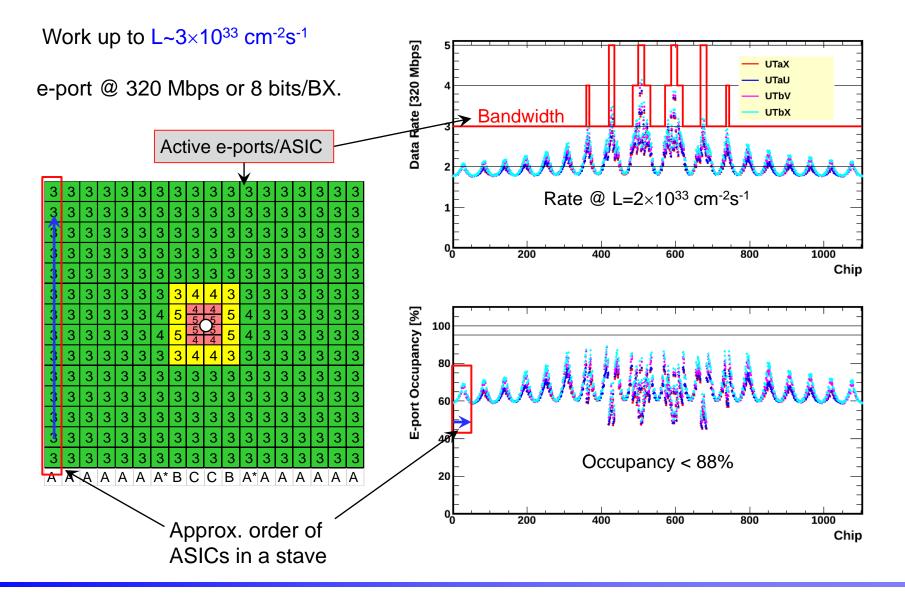

- The UT detector was designed for nominal L = 2×10<sup>33</sup> cm<sup>-2</sup>s<sup>-1</sup>, can run up to L~3×10<sup>33</sup> cm<sup>-2</sup>s<sup>-1</sup>. At even higher luminosity some ASICs do not have sufficient bandwidth for event data.

- □ The channel occupancy is kept < 1% at the nominal luminosity.

- The silicon sensors and SALT ASICs will still be efficient after 50 fb<sup>-1</sup> equivalent radiation damage.

- LHCb will operate at L = 1.5×10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup> in Upgrade II, a ×7.5 increase, and collect ~250 fb<sup>-1</sup> data.

- We want to check the occupancy and data rate of the UT system at U2 luminosity, see how it works and whether any part may be kept.

- We also try simple designs and compare a few possibilities: a UT-like detector in the outer area + a CMOS pixel detector at the center, or a full CMOS pixel detector.

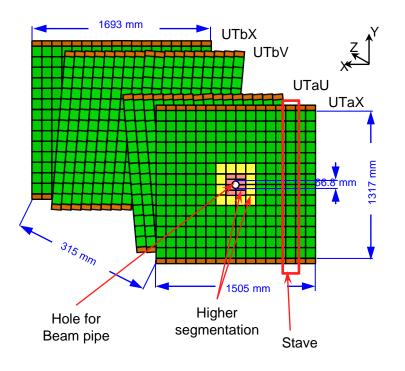

### UT Detector In Upgrade I

| Sensor        | A     | В    | С    | D    |

|---------------|-------|------|------|------|

| Pitch (µm)    | 187.5 | 93.5 | 93.5 | 93.5 |

| Length (mm)   | ~100  | ~100 | ~50  | ~50  |

| Strips/sensor | 512   | 1024 | 1024 | 1024 |

| Numbers       | 888   | 48   | 16   | 16   |

- Given the segmentations: A, B, C & D.

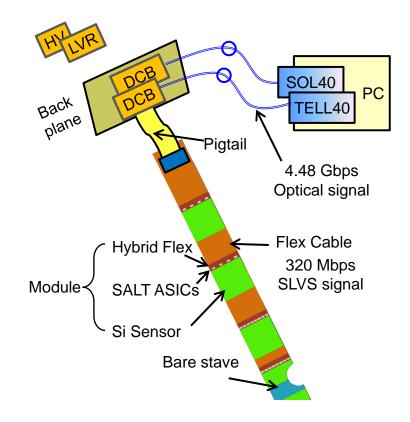

- □ Stave structure, modules on two sides of staves for overlapping, readout at 2 ends of each stave.

- □ In total 68 staves, 968 sensors, 4192 ASICs.

#### Channel occupancy rate [%]

| 0.18 | 0.19 | 0.19 | 0.20 | 0.20 | 0.21 | 0.21 | 0.22 | 0.22         |

|------|------|------|------|------|------|------|------|--------------|

| 0.19 | 0.20 | 0.20 | 0.21 | 0.21 | 0.22 | 0.23 | 0.24 | 0.24         |

| 0.20 | 0.21 | 0.22 | 0.23 | 0.24 | 0.25 | 0.27 | 0.29 | 0.30         |

| 0.22 | 0.23 | 0.24 | 0.26 | 0.28 | 0.30 | 0.33 | 0.37 | 0.40         |

| 0.25 | 0.26 | 0.28 | 0.31 | 0.33 | 0.38 | 0.43 | 0.52 | 0.59         |

| 0.28 | 0.30 | 0.33 | 0.36 | 0.41 | 0.47 | 0.57 | 0.57 | 0.74         |

| 0.33 | 0.36 | 0.38 | 0.43 | 0.47 | 0.56 | 0.71 | 0.83 | 0.75<br>0.94 |

- Noise, spill-overs, and the bunch structure are taken into account.

- With this design, the channel occupancy rate of the inner-most module is ~0.94%. The highest ASIC is ~1.4%.

- The simulation was done in year 2015. The SALT performance was not fully modelled.

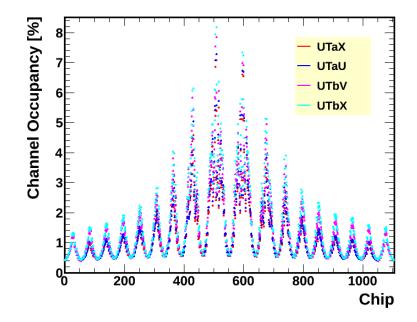

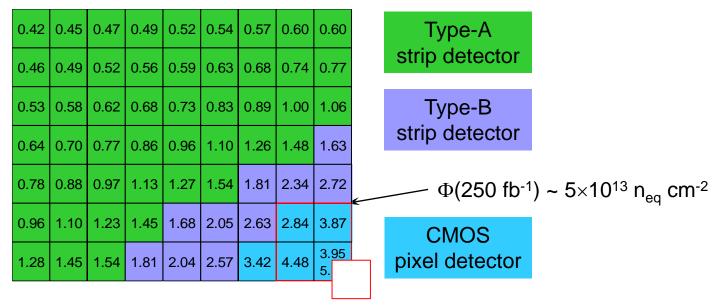

- We check UT at U2 luminosity L=1.5×10<sup>34</sup> cm<sup>-2</sup>s<sup>-1</sup>, basing on the old simulation. New simulation is not ready yet.

- Luminosity increases  $\times 7.5$ , cluster size  $1.45 \Rightarrow 1.1 \& 1.2$  for modules of pitch = 187.5 & 93.5  $\mu$ m respectively.

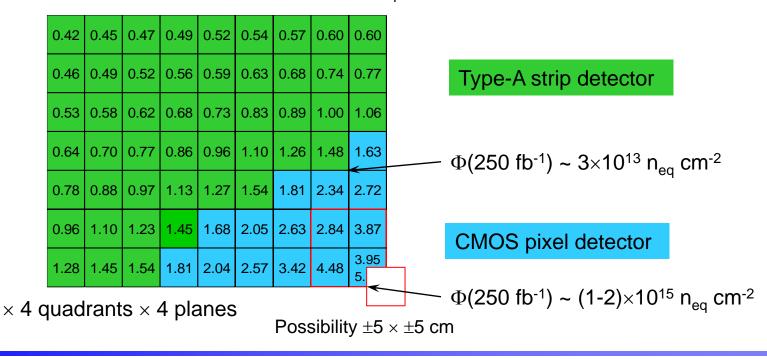

- Taking into account noise, spill-overs and bunch structure, the occupancy of the inner-most module is ~5.1%. The highest ASIC is ~8.2%.

| 0.42 | 0.45 | 0.47 | 0.49 | 0.52 | 0.54 | 0.57 | 0.60 | 0.60         |

|------|------|------|------|------|------|------|------|--------------|

| 0.46 | 0.49 | 0.52 | 0.56 | 0.59 | 0.63 | 0.68 | 0.74 | 0.77         |

| 0.53 | 0.58 | 0.62 | 0.68 | 0.73 | 0.83 | 0.89 | 1.00 | 1.06         |

| 0.64 | 0.70 | 0.77 | 0.86 | 0.96 | 1.10 | 1.26 | 1.48 | 1.63         |

| 0.78 | 0.88 | 0.97 | 1.13 | 1.27 | 1.54 | 1.81 | 2.34 | 2.72         |

| 0.96 | 1.10 | 1.23 | 1.45 | 1.68 | 2.05 | 2.63 | 2.84 | 3.87         |

| 1.28 | 1.45 | 1.54 | 1.81 | 2.04 | 2.57 | 3.42 | 4.48 | 3.95<br>5.13 |

Channel occupancy [%]

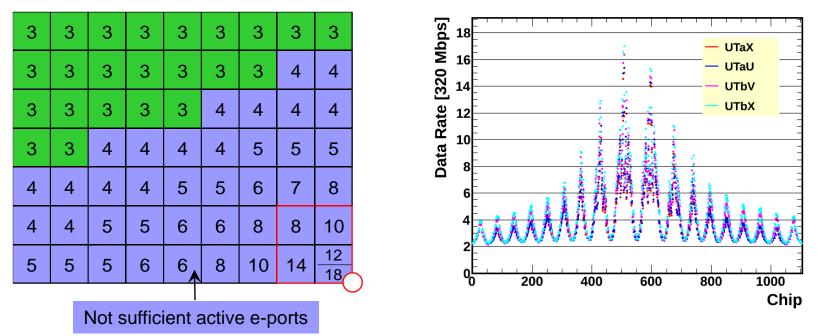

- Data rate =  $(12 + 12 < nHits) \times 40$  MHz, i.e 1.5 e-ports for header, and 1.5 per hit.

- An ASIC can have up to 6 active e-ports, thus can handle up to <nHits> = 2.8, or

2.2% channel occupancy rate, for e-ports to be < 95% busy.</li>

- Due to constraints of the flex cable, not all e-ports were connected. Each UT stave would have some modules fail this data rate. None of them can be kept in U2.

Number of e-ports needed (<95% busy)

# **Scenario I: Type-A Strip + CMOS Pixel**

- An outer UT-like strip detector + an inner CMOS pixel detector. Benefit from both the UT and the Mighty Tracker activities.

- We can try a similar stave design to provide mechanical support and cooling.

- By the time of U2, the speed of e-link may be doubled or faster. So are GBTx and PCIe40s. In this exercise we assume that UT electronics can still be used.

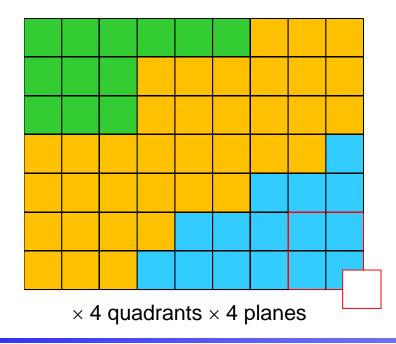

- Following is a 1<sup>st</sup> attempt. The outer detector uses 712 type-A sensors (187.5 μm pitch), which was validated up to ~2×10<sup>14</sup> n<sub>eq</sub> cm<sup>-2</sup> particle fluence.

# **CHCP** Scenario I: Outer Silicon Strip Detector

- 712 new UT modules (sensor, hybrid, stiffener, SALT). To simplify designs of flex cable, pigtail and backplane, the modules are 4 × 3 e-ports or 4 × 5 e-ports, 168 & 544 modules respectively.

- ✤ 68 new bare staves with cooling tubes etc.

- ✤ 272 new flex cables, 272 new pigtail cables, 24 new backplanes.

- Readout needs 224 DCBs and 110 TELL40s, all of them can be from UT.

- ✤ LV/HV, electronics in SBCs, etc can also be reused.

Outer: silicon strip detector

Inner: CMOS silicon pixel detector

The inner detector is CMOS pixel sensor based. Shape and size of the beam pipe hole are to be evaluated.

Area ~

$$4 \times 60 \times (10 \times 10 \text{ cm}^2) = 2.4 \text{ m}^2$$

.

- It can share the stave with the outer detector, for both mechanical and cooling.

- The LV / HV and communication also need to be integrated.

- □ The stave-end electronic chassis will be modified to support two sub-systems.

- ✤ Use the same stave structure as the UT.

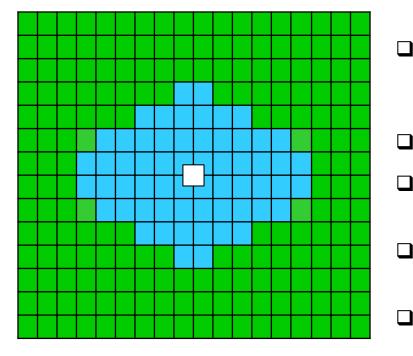

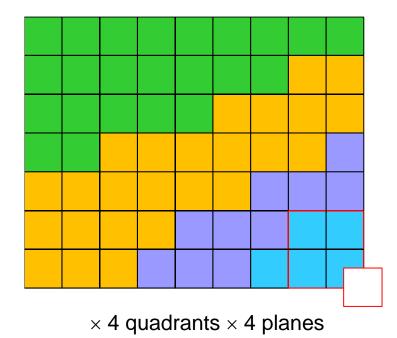

- The outer detector has 712 type-A sensors (pitch = 187.5 μm), 160 type-B sensors (pitch = 93.5 μm). Sensor radiation hardness was validated.

- The inner detector use CMOS pixel sensor, covers ~  $80 \times (10 \times 10)$  cm<sup>2</sup> area.

$\times$  4 quadrants  $\times$  4 planes

- 872 new modules of 4 × 3 e-ports and 4 × 5 e-ports for type-A, 8 × 5 e-ports for type-B, 334, 376 & 160 modules respectively.

- Readout needs 304 DCBs and 144 TELL40s. The current UT can provides at least 240 and 108 respectively.

- ✤ Area for the CMOS pixel detector: ~0.8 m<sup>2</sup>.

- ✤ We can use full CMOS pixel detector option.

- The overall area is about 8.5 m<sup>2</sup>. With overlaps it will be ~10% larger. Thus we can use 9.4 m<sup>2</sup> estimation.

- At U2 luminosity all UT staves, which were designed for U1, have insufficient bandwidth for event data. No stave can be reused. If we include the UT style modules, the current supporting electronics, HV/LV etc can be reused.

- We compared 3 scenarios:

- Scenario I: An outer silicon strip detector of UT type-A strip sensor + SALT, and an inner CMOS pixel detector.

- Scenario II: Similar as scenario I, but use UT type-B strip sensors to replace the low intensity outer rim of the CMOS detector.

- Scenario III: A full CMOS silicon pixel detector.

- Scenario II is favored in budget, but more complicated to build.

- We are working on a more realistic simulation to re-evaluate different scenarios, and plan to have a full U2 detector simulation to validate and optimize the design.

- Other high segmentation detector may also be considered. The CMOS option benefits from the Mighty Tracker activities, and the R&D project at IHEP.