SEM Grid Front-End Board V3 Mark McLean, 28<sup>th</sup> April 2020

# Background

- Six V3 Front-End Boards from Japan have undergone some bench tests.

- Six more Front-End Boards are being manufactured in Europe.

- The two batches should be identical except the bare board materials are different.

# Light sensitivity

- In general, the ASIC gives a flat output when exposed to light (self-calibration sometimes works).

- This (embarrassingly) is one of the big reasons why V1 had lower noise than V2, because V2 had an opaque ASIC cover, and therefore was working and detecting real environmental noise.

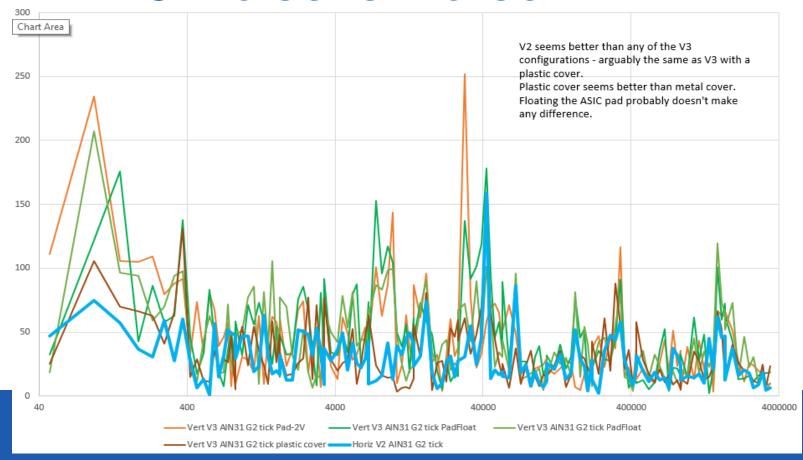

#### Build differences between versions

- Slight differences in ground area separation

- Differences in tracking of ASIC inputs

- ASIC pad floating in V1 (V2 @ -2V, V3 linked to -2V)

- Trimmer removed after V1

- Matched pair used after V1

- V2 has R84 and R94 fitted so the DET\_BIAS is connected

- Metal ASIC covers on V3 (with Kapton against board)

- More small decoupling capacitors in V2

#### Behavioural diffs between versions

- ASIC\_G2 "Positive charge linearity correction" seems to cause different behaviours – sometimes...

- Higher noise maybe, in some areas, see more graphs…

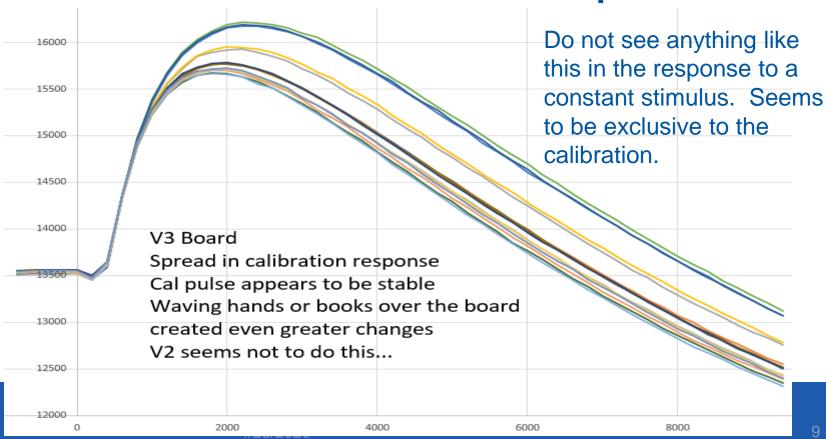

- Size of the calibration response is variable in V3, V2 is much more stable, V1 also somewhat variable

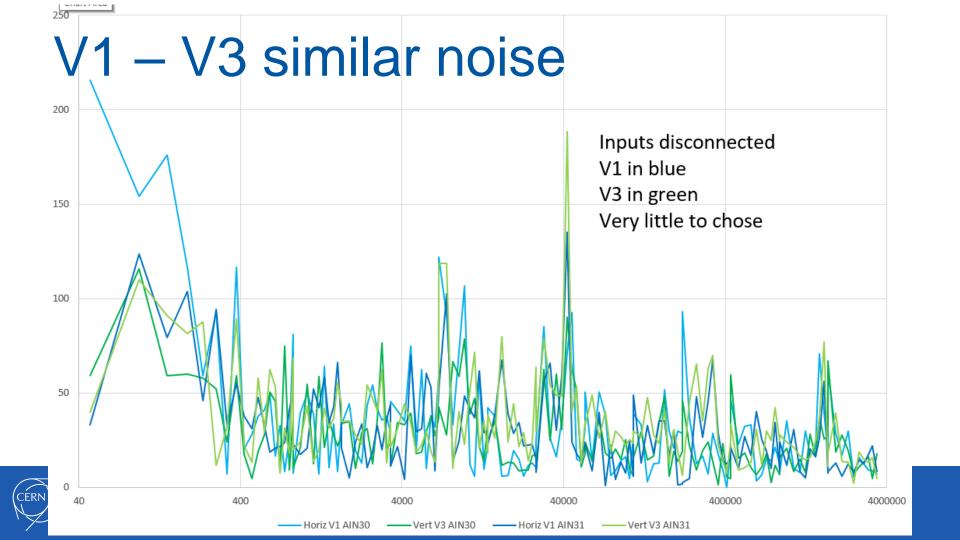

#### Noise

- "Noise" has two components

- Inherent noise coming from the circuit itself.

Hard to measure because generally lower than noise pickup.

- "Picked-up" noise detected by the sense wires,

e.g. local radio station, other EM noise

### V2 – V3 Noise is worse

## Variation in calibration response

## Variation in profile level

- On bench, "dc" level of profile varies by approx. ±50 bits. All versions do this.

- Stimulus picks up noise, so this may not really be a problem.

### Test board

With 250mV stim this injects 221fC

### Conclusions

- Still confused...

- Not ready to launch volume production yet

- Things to do:

- Does the metal cover make the noise worse?

- Why does the calibration response vary on V3 (and V1)?

- Measure noise installed in ELENA (but of course without kickers, etc)

- Measure response size and linearity, but need stable performance first.

- Investigate DET\_BIAS

- Put the boards in a metal box for testing?

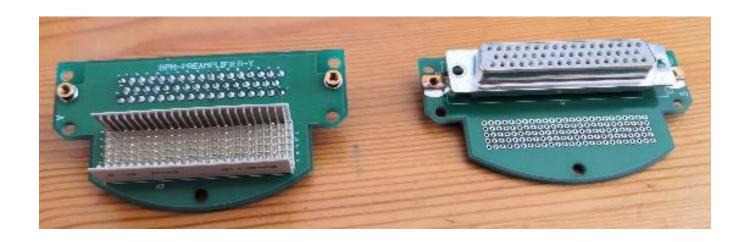

# Attenuating Half-Moon Board

Bare Board delivered to CERN, will populate one by hand to test when beam is available.

### InOut Board

The Electronics Workshop are sending out the order for manufacture of four prototype InOut Boards.

## Possible problem

- There is some kind of unreliability of the communication with the VME Module.

- Only seems to happen when the FPGA has booted from the NAND FLASH

- Only seems to effect some boards

- Still being looked at

- I could investigate changing the VME VHDL code block to the one provided by CO