# EMCI non-exhaustive testbench proposal

Daniel Blasco Serrano

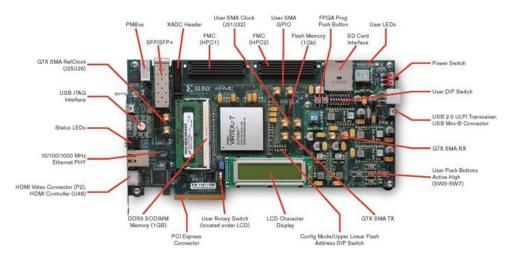

#### VC707: Virtex 7 Evaluation Board

- FMC HPC connector

- Banks configurable @1.2V (VADJ)

- SFP+ connector

- SMA clock input

- Used in VLDB+ testbench

## Testbench implementation

- Plugging EMCI FMC male connector directly into FMC connector of a VC707

- VC707 may be configured to work @1.2V

- 12V power coming from VC707 (FMC)

- High speed link is tested using VTRx+/SPF+

- External 320MHz clock needed (SMA connectors)

- eLinks need the CDR from the downlink stream to work

- Auxiliary connector tested by means of Raspberry Pi separately (provided with VLDB+)

### Tested features

- eLinks testing

- Downlink: from 80 to 320 Mbps

- Uplink: from 160 to 1280 Mbps

- With normal IO pin (using SERDES)

- VLDB+ has been tested up to 640 MHz

- VC707 FMC transceivers cannot be used

- Need external clock coming from FMC

- High speed testing

- SPF+ transceiver

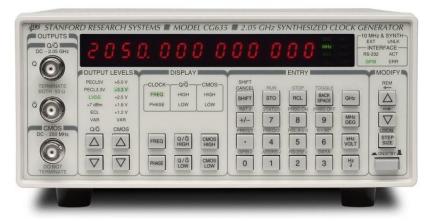

- External clock generator needed [Proposal: CG635 (available in e-pool)]

- I2C master/slave, GPIO, PSClock, \*ADC/DAC

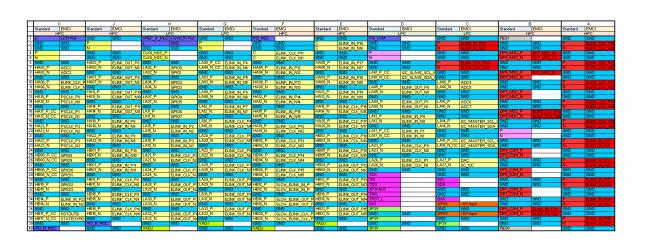

| Input eLinks (up-link)   |      |     |     |       |     |     |      |     |      |       |     |      |

|--------------------------|------|-----|-----|-------|-----|-----|------|-----|------|-------|-----|------|

| Up-link bandwidth [Gb/s] |      |     | 5.  | 12 1  |     |     |      |     | 10.  | 0.24  |     |      |

| FEC coding               | FEC5 |     |     | FEC12 |     |     | FEC5 |     |      | FEC12 |     |      |

| Bandwidth [Mb/s]         | 160  | 320 | 640 | 160   | 320 | 640 | 320  | 640 | 1280 | 320   | 640 | 1280 |

| Maximum number           | 28   | 14  | 7   | 24    | 12  | 6   | 28   | 14  | 7    | 24    | 12  | 6    |

| Output eLinks (down-link) |    |     |     |  |  |  |  |  |  |

|---------------------------|----|-----|-----|--|--|--|--|--|--|

| Bandwidth [Mb/s]          | 80 | 160 | 320 |  |  |  |  |  |  |

| Maximum number            | 16 | 8   | 4   |  |  |  |  |  |  |

## Problems

- Not all eLinks/features can be tested (even with optimal routing)

- Max 58 pairs for testing (including eLinks TX/RX/CLK, GPIO, I2C...)

- ADC and DAC (1V range) cannot be properly tested

- lpGBT ADC max input 1V, but 1.2V should be OK

- lpGBT DAC can deliver 1V to VC707 (1.2 V high level)

- For better testing, a different testbench with an FMC breakout board would be needed to plug to a function generator/oscilloscope

- Cannot be tested at the same time as the rest of the features

- Final pinout depends on routing