# RD50-MPW2 active pixel matrix measurements

Ricardo Marco Hernández IFIC (CSIC-UV)

#### **RD50-MPW2** active pixel matrix measurements setup

- Three RD50-MPW2 chip boards used:

- RD50-MPW2-2: RD50-MPW2 W10 device bonded (1.9 k $\Omega$ ·cm). Current consumption, ToT measurements and ADC/ABUFF measurements.

- RD50-MPW2-1: RD50-MPW2 W7 device bonded (0.5-1.1 kΩ·cm). bonded (1.9 kΩ·cm). ADC/ABUFF measurements.

- RD50-MPW2-3: RD50-MPW2 W14 device bonded (> 2 kΩ·cm). bonded (1.9 kΩ·cm). ADC/ABUFF measurements.

- FMC CaR board, ZC702 board and own firmware/software used.

- VHDL blocks for RD50-MPW2 stream data generation, analog buffer control, test pulse generation and comparator pulse readout.

- Linux running in Zynq ARM (from SD card).

- Python scripts and UIO driver/I2C driver for controlling the system.

1360

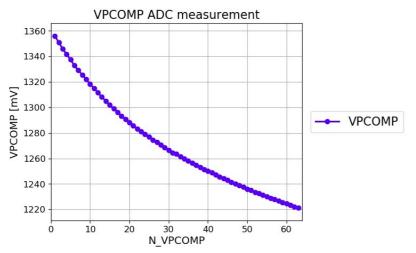

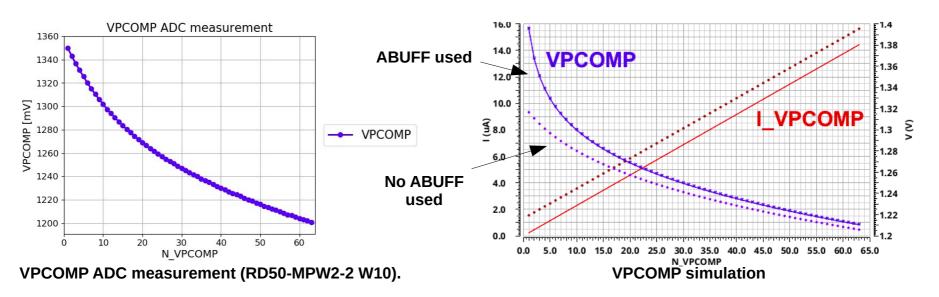

- Measurement details: VPCOMP (sets current of comparators).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

1340 1320 1300 1280 1260 1240 1220 1200 0 10 20 30 40 50 60 N\_VPCOMP

VPCOMP ADC measurement

VPCOMP ADC measurement (RD50-MPW2-1 W7).

VPCOMP ADC measurement (RD50-MPW2-3 W14).

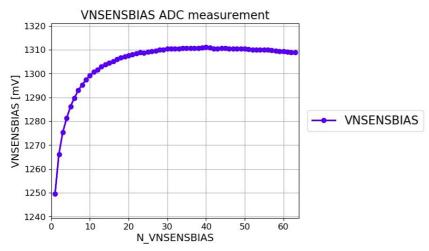

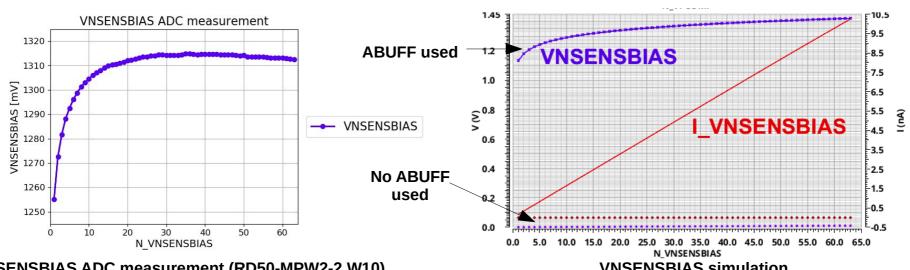

- Measurement details: VNSENSBIAS (bias transistors as the R for DNWELL).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VNSENSBIAS ADC measurement 1290 1280 [AE] 1270 1260 1250 1240 VNSENSBIAS 1230 1220 50 60 N VNSENSBIAS

VNSENSBIAS ADC measurement (RD50-MPW2-1 W7).

VNSENSBIAS ADC measurement (RD50-MPW2-3 W14).

VNSENSBIAS ADC measurement (RD50-MPW2-2 W10).

VNSENSBIAS simulation

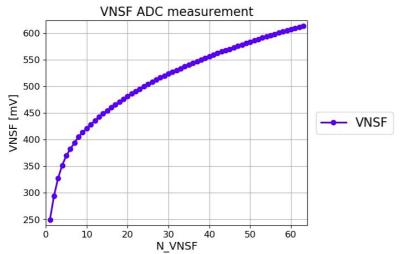

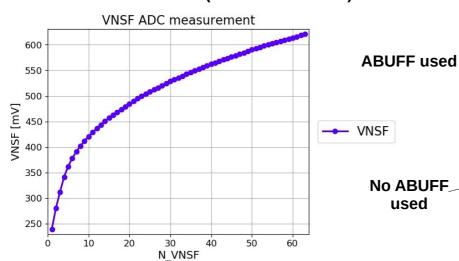

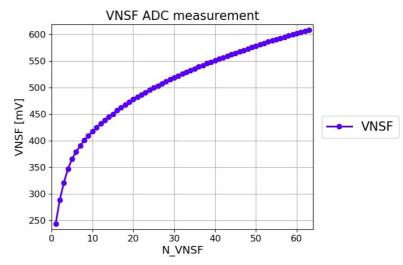

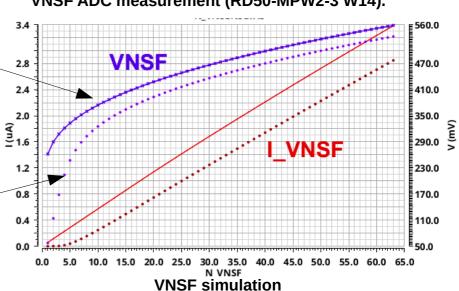

- Measurement details: VNSF (sets current of source followers).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VNSF ADC measurement (RD50-MPW2-1 W7).

VNSF ADC measurement (RD50-MPW2-2 W10).

VNSF ADC measurement (RD50-MPW2-3 W14).

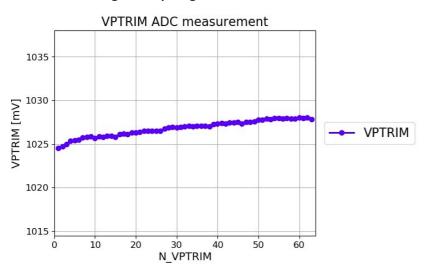

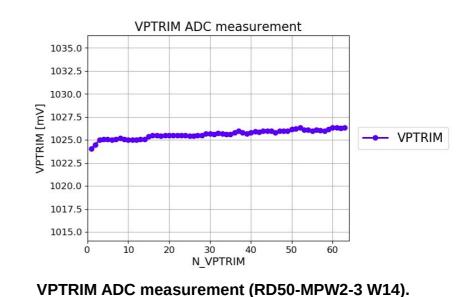

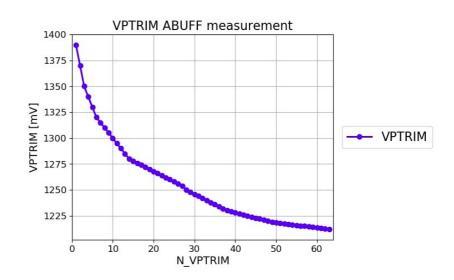

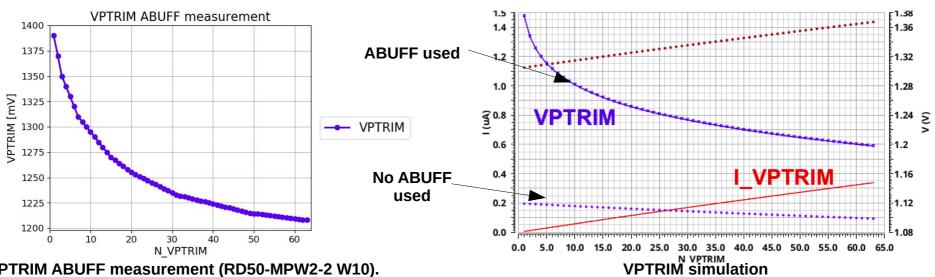

- Measurement details: VPTRIM (sets current of trimming DACs).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VPTRIM ADC measurement (RD50-MPW2-1 W7).

VPTRIM ADC measurement 1040 1.4 1.36 **ABUFF** used 1.32 1035 1.28 1.0 VPTRIM [mV] 8.0 (R VPTRIM 1.24 § **VPTRIM** 0.6 No ABUFF 0.4 1.16 1020 used 0.2 1.12 40 60 N VPTRIM VPTRIM simulation

VPTRIM ADC measurement (RD50-MPW2-2 W10).

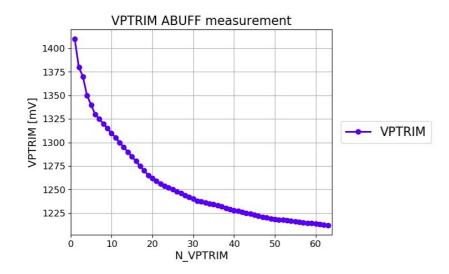

- Measurement details: VPTRIM (sets current of trimming DACs).

- Measurement from **ABUFF output with scope**.

- Bias register programmed from 0 to 63.

VPTRIM ABUFF measurement (RD50-MPW2-1 W7).

VPTRIM ABUFF measurement (RD50-MPW2-3 W14).

VPTRIM ABUFF measurement (RD50-MPW2-2 W10).

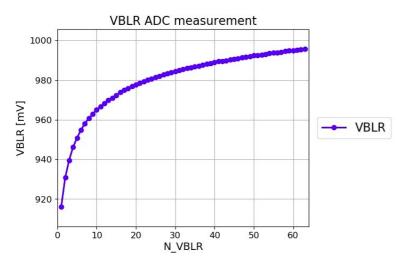

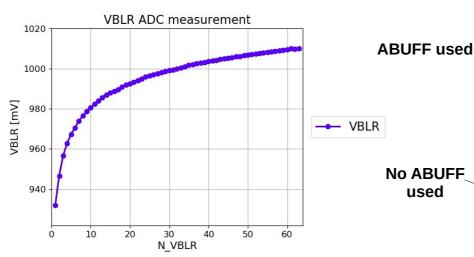

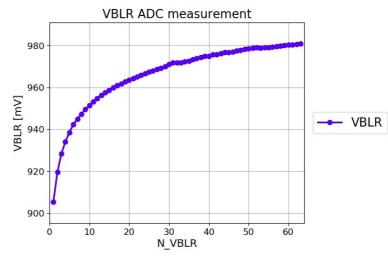

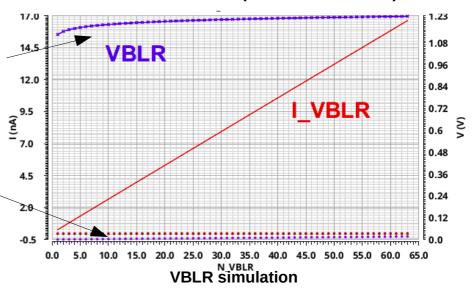

- Measurement details: VBLR (bias transistors as the R in HP-filters).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VBLR ADC measurement (RD50-MPW2-1 W7).

VBLR ADC measurement (RD50-MPW2-2 W10).

VBLR ADC measurement (RD50-MPW2-3 W14).

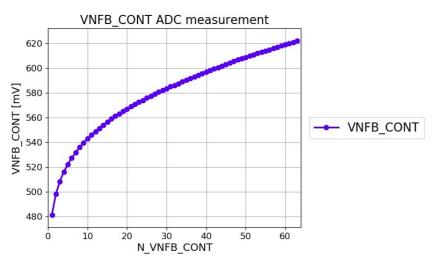

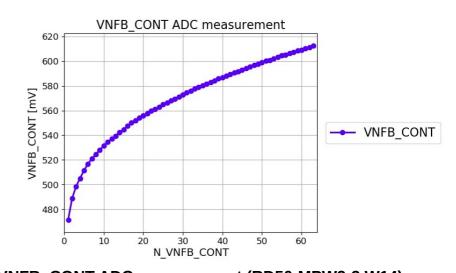

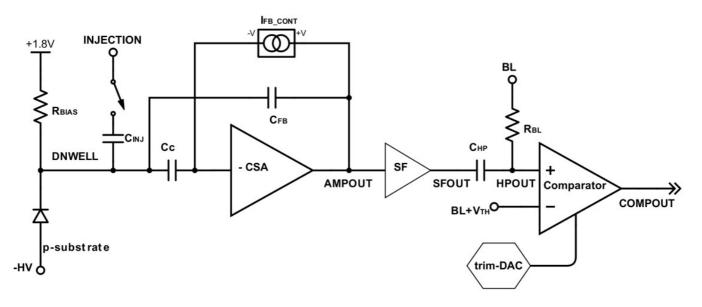

- Measurement details: VNFB\_CONT (sets  $I_{FB}$  of continuous-reset pixels).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VNFB CONT ADC measurement (RD50-MPW2-1 W7).

VNFB\_CONT ADC measurement (RD50-MPW2-3 W14). 560.0 VNFB CONT ADC measurement 560.0 640 480.0 **ABUFF** used VNFB\_CONT 620 480.0 400.0 600 400.0 CONT [mV] 320.0 (u) 580 320.0 560 VNFB CONT VNFB CONT 240.0 240.0 540 160.0 520 160.0 No ABUFF used 500 80.0 80.0 480 0.0 20 60 10 N VNFB CONT 5.0 10.0 15.0 25.0 30.0 35.0 40.0 N VNFB CONT VNFB CONT simulation

VNFB\_CONT ADC measurement (RD50-MPW2-2 W10).

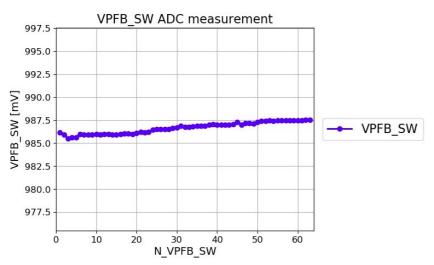

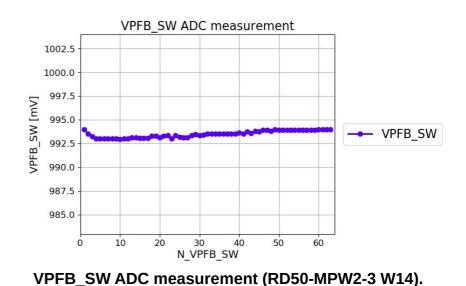

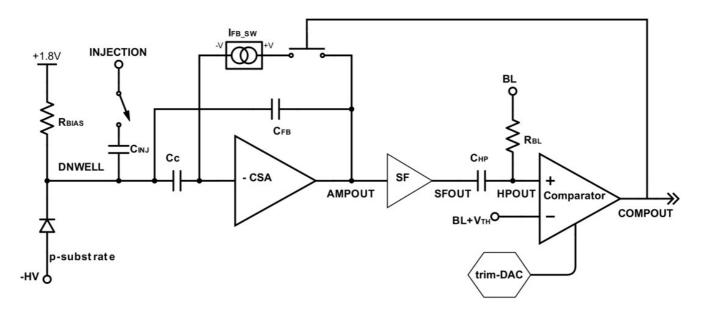

- Measurement details: VPFB\_SW (sets I<sub>FB</sub> of switched-reset pixels).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VPFB\_SW ADC measurement (RD50-MPW2-1 W7).

VPFB SW ADC measurement 1.36 1005.0 0.9 **ABUFF** used 1002.5 8.0 1.28 1000.0 VPFB SW VPFB SW [mV] 9.6 0.5 997.5 1.2 VPFB SW 995.0 ₹1.16 0.4 992.5 1.12 0.3 990.0 No ABUFF 0.2 1.08 987.5 used 0.1 985.0 0.0 10 20 N VPFB SW N VPFB SW **VPFB\_SW simulation**

VPFB\_SW ADC measurement (RD50-MPW2-2 W10).

- Measurement details: VPFB\_SW (sets I<sub>FB</sub> of switched-reset pixels).

- Measurement with on-board ABUFF output with scope...

- Bias register programmed from 0 to 63.

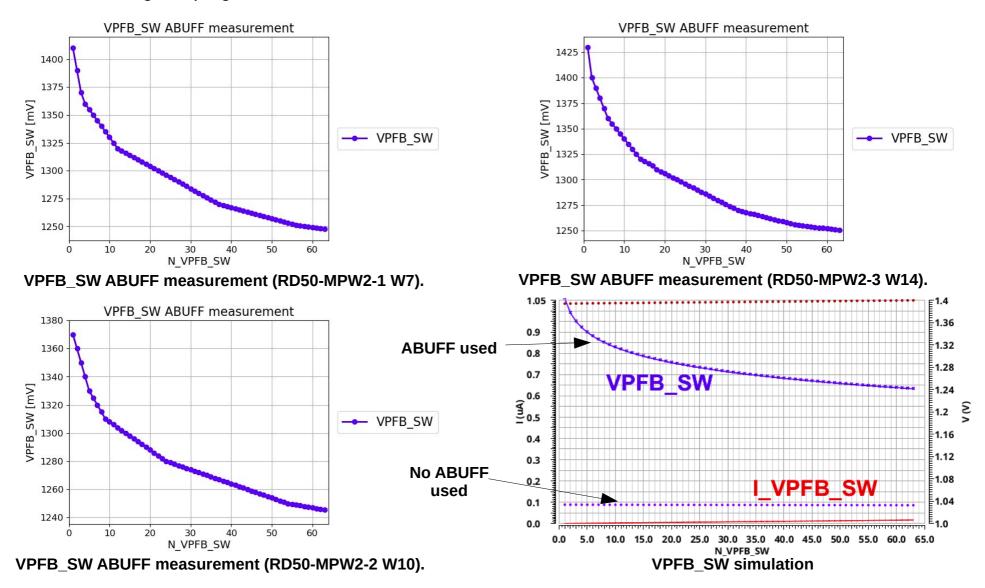

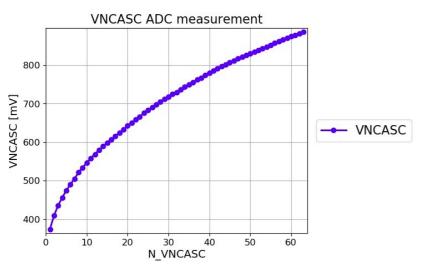

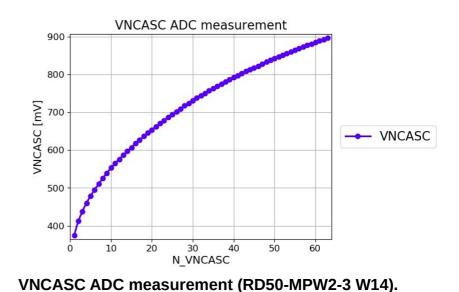

- Measurement details: VNCASC (bias the cascode transistor of CSAs).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VNCASC ADC measurement (RD50-MPW2-1 W7).

**VNCASC ADC measurement** 900 VNCASC 2.0 **ABUFF** used 800 1.6 VNCASC [mV] 9 1.2 VNCASC 8.0 500 No ABUFF used 400 20 40 50 60 N VNCASC 5.0 10.0 15.0 30.0 35.0 40.0 45.0 50.0 55.0 60.0 65.0 N\_VPBIAS\_VNCASC

VNCASC ADC measurement (RD50-MPW2-2 W10).

VNCASC simulation

0.83

0.67

0.35

0.19

⊙ 0.51 >

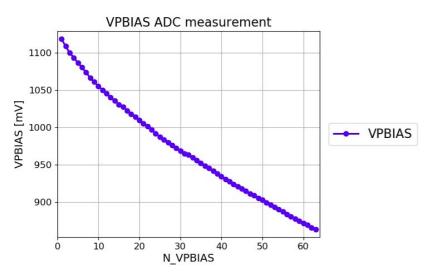

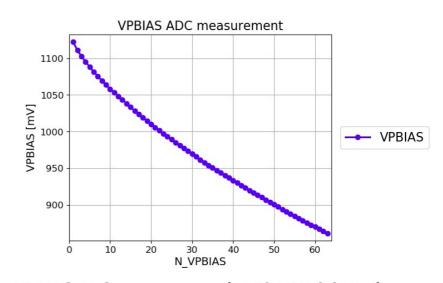

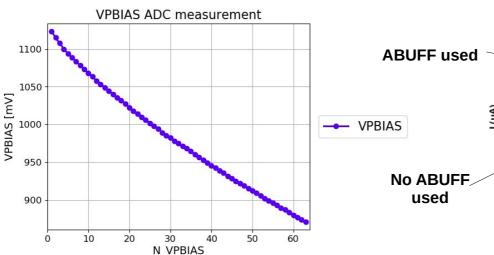

- Measurement details: VPBIAS (sets current of the load of CSAs).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VPBIAS ADC measurement (RD50-MPW2-1 W7).

VPBIAS ADC measurement (RD50-MPW2-3 W14). 7.0 1.19 **VPBIAS** 6.0 1.15 1.11 5.0 <u>§</u> 4.0 1.07 S 1.03 3.0 0.95 1.0 0.91 0.0 5.0 10.0 15.0 N\_VPBIAS\_VNCASC VPBIAS simulation

VPBIAS ADC measurement (RD50-MPW2-2 W10).

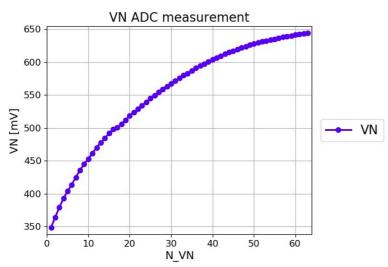

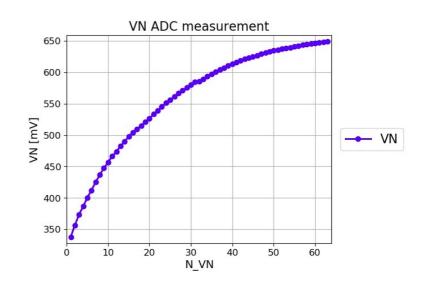

- Measurement details: VN (sets current of CSAs).

- Measurement with on-board ADC.

- Bias register programmed from 0 to 63.

VN ADC measurement (RD50-MPW2-1 W7).

VN ADC measurement 650 600 550 450 400 350 50 60 10 20 30 N VN VN ADC measurement (RD50-MPW2-2 W10).

VN ADC measurement (RD50-MPW2-3 W14). 650.0 600.0 6.0 VN **ABUFF** used 550.0 5.0 500.0 450.0 돌 4.0 -3.0 400.0 350.0 300.0 No ABUFF 250.0 1.0 200.0 5.0 10.0 15.0 20.0 45.0 50.0 55.0 60.0 65.0 N VN

VN simulation

used

#### **RD50-MPW2 current consumption measurement**

- Measurement details: RD50-MPW2-2 (W10)

- RD50-MPW2 voltage levels (V) and current levels (mA).

- Registers of device not configured from DAQ.

- ABUFF powered.

```

root@RD50 MPW2_DAQ_v2:~/Apps# python Meas_curr_RD50_MPW2.py --temp -v

# RD50 MPW2 power levels current measurement started #

CaR temperature (C): 36.875000

P1V8A NW RING (PWR OUT 1) voltage (V): 1.837500

P1V8A NW RING (PWR OUT 1) current (mA): 0.000000

P1V8D_VDD_IO (PWR_OUT_2) voltage (V): 1.841250

P1V8D VDD IO (PWR OUT 2) current (mA): 0.300000

P1V8A VSENSBIAS (PWR OUT 3) voltage (V): 1.838750

P1V8A VSENSBIAS (PWR OUT 3) current (mA): 0.500000

P1V8A VDDA (PWR OUT 4) voltage (V): 1.823750

P1V8A_VDDA (PWR_OUT_4) current (mA): 6.800000

P1V8D VDDC (PWR OUT 5) voltage (V): 1.822500

P1V8D VDDC (PWR OUT 5) current (mA): 4.500000

P1V3A_VSSA (PWR_OUT_6) voltage (V): 1.348750

P1V3A_VSSA (PWR_OUT_6) current (mA): 0.800000

P1V8D_VDDD (PWR_OUT_7) voltage (V): 1.845000

P1V8D VDDD (PWR OUT 7) current (mA): 0.500000

P1V8A BG VDD (PWR OUT 8) voltage (V): 1.843750

P1V8A BG VDD (PWR OUT 8) current (mA): 0.800000

# RD50 MPW2 power levels current measurement finished #

root@RD50 MPW2 DAO v2:~/Apps#

```

RD50-MPW2 current consumption. No registers not configured. ABUFF powered.

| Name      | Description                           | Voltage | Current  |

|-----------|---------------------------------------|---------|----------|

| NW_RING   | Nwell guard ring bias                 | 1.8 V   | Leakage  |

| VDD_IO    | Pads protection diodes cathode bias   | 1.8 V   |          |

| VSENSBIAS | DNWELL bias (cathode of sensing diode | 1.8 V   | ~ nA     |

| VDDA      | Analog circuits power supply          | 1.8 V   | < 5.5 mA |

| VDDC      | In-pixel comparators power supply     | 1.8 V   | < 0.5 mA |

| VSSA      | CSAs power supply                     | 1.3 V   | < 0.5 mA |

| VDDD      | Digital circuits power supply         | 1.8 V   | < 100 µA |

| BG_VDD    | Bandgap power supply                  | 1.8 V   | ~ 100 µA |

RD50-MPW2 current consumption from pad description.

Higher values of current measured than expected

#### **RD50-MPW2 current consumption measurement**

- Measurement details: RD50-MPW2-2 (W10)

- RD50-MPW2 voltage levels (V) and current levels (mA).

- Registers of device configured from DAQ.

- ABUFF powered.

```

root@RD50 MPW2 DAQ v2:~/Apps# python Meas curr RD50 MPW2.py --temp -v

# RD50 MPW2 power levels current measurement started #

cak temperature (c): 37.187500

P1V8A_NW_RING (PWR_OUT_1) voltage (V): 1.838750

P1V8A NW RING (PWR OUT 1) current (mA): 0.300000

P1V8D_VDD_IO (PWR_OUT_2) voltage (V): 1.842500

P1V8D_VDD_IO (PWR_OUT_2) current (mA): 0.000000

P1V8A_VSENSBIAS (PWR_OUT_3) voltage (V): 1.840000

P1V8A VSENSBIAS (PWR OUT 3) current (mA): 0.500000

P1V8A_VDDA (PWR_OUT_4) voltage (V): 1.822500

P1V8A VDDA (PWR OUT 4) current (mA): 6.500000

P1V8D VDDC (PWR OUT 5) voltage (V): 1.820000

P1V8D VDDC (PWR OUT 5) current (mA): 4.800000

P1V3A VSSA (PWR OUT 6) voltage (V): 1.347500

P1V3A VSSA (PWR OUT 6) current (mA): 0.500000

P1V8D_VDDD (PWR_OUT_7) voltage (V): 1.846250

P1V8D VDDD (PWR OUT 7) current (mA): 0.300000

P1V8A BG VDD (PWR OUT 8) voltage (V): 1.843750

P1V8A BG VDD (PWR OUT 8) current (mA): 0.800000

# RD50 MPW2 power levels current measurement finished #

root@RD50 MPW2 DAO v2:~/Apps#

```

RD50-MPW2 current consumption. Registers configured. ABUFF powered.

| Name      | Description                           | Voltage | Current  |

|-----------|---------------------------------------|---------|----------|

| NW_RING   | Nwell guard ring bias                 | 1.8 V   | Leakage  |

| VDD_IO    | Pads protection diodes cathode bias   | 1.8 V   |          |

| VSENSBIAS | DNWELL bias (cathode of sensing diode | 1.8 V   | ~ nA     |

| VDDA      | Analog circuits power supply          | 1.8 V   | < 5.5 mA |

| VDDC      | In-pixel comparators power supply     | 1.8 V   | < 0.5 mA |

| VSSA      | CSAs power supply                     | 1.3 V   | < 0.5 mA |

| VDDD      | Digital circuits power supply         | 1.8 V   | < 100 µA |

| BG_VDD    | Bandgap power supply                  | 1.8 V   | ~ 100 µA |

RD50-MPW2 current consumption from pad description.

Similar values of current measured as previous case

#### **RD50-MPW2 current consumption measurement**

- Measurement details: RD50-MPW2-2 (W10)

- RD50-MPW2 voltage levels (V) and current levels (mA).

- Registers of device configured from DAQ.

- ABUFF powered down.

```

root@RD50 MPW2 DAO v2:~/Apps# python Meas curr RD50 MPW2.py --temp -v

# RD50 MPW2 power levels current measurement started #

CaR temperature (C): 37.187500

P1V8A NW_RING (PWR_OUT_1) voltage (V): 1.837500

P1V8A NW RING (PWR OUT 1) current (mA): 0.300000

P1V8D VDD IO (PWR OUT 2) voltage (V): 1.843750

P1V8D VDD IO (PWR OUT 2) current (mA): 0.000000

P1V8A VSENSBIAS (PWR OUT 3) voltage (V): 1.840000

P1V8A VSENSBIAS (PWR OUT 3) current (mA): 0.000000

P1V8A_VDDA (PWR_OUT_4) voltage (V): 1.838750

P1V8A VDDA (PWR OUT 4) current (mA): 1.000000

P1V8D_VDDC (PWR_OUT_5) voltage (V): 1.821250

P1V8D VDDC (PWR OUT 5) current (mA): 5.000000

P1V3A VSSA (PWR OUT 6) voltage (V): 1.346250

P1V3A VSSA (PWR OUT 6) current (mA): 0.800000

P1V8D_VDDD (PWR_OUT_7) voltage (V): 1.846250

P1V8D_VDDD (PWR_OUT_7) current (mA): 0.300000

P1V8A_BG_VDD (PWR_OUT_8) voltage (V): 1.842500

P1V8A BG VDD (PWR OUT 8) current (mA): 0.800000

# RD50 MPW2 power levels current measurement finished #

root@RD50 MPW2 DAO v2:~/Apps#

```

RD50-MPW2 current consumption. Registers configured. ABUFF powered down.

| Name      | Description                           | Voltage | Current  |

|-----------|---------------------------------------|---------|----------|

| NW_RING   | Nwell guard ring bias                 | 1.8 V   | Leakage  |

| VDD_IO    | Pads protection diodes cathode bias   | 1.8 V   |          |

| VSENSBIAS | DNWELL bias (cathode of sensing diode | 1.8 V   | ~ nA     |

| VDDA      | Analog circuits power supply          | 1.8 V   | < 5.5 mA |

| VDDC      | In-pixel comparators power supply     | 1.8 V   | < 0.5 mA |

| VSSA      | CSAs power supply                     | 1.3 V   | < 0.5 mA |

| VDDD      | Digital circuits power supply         | 1.8 V   | < 100 µA |

| BG_VDD    | Bandgap power supply                  | 1.8 V   | ~ 100 µA |

RD50-MPW2 current consumption from pad description.

Current consumption at VDDA reduced 5 mA with ABUFF off as expected

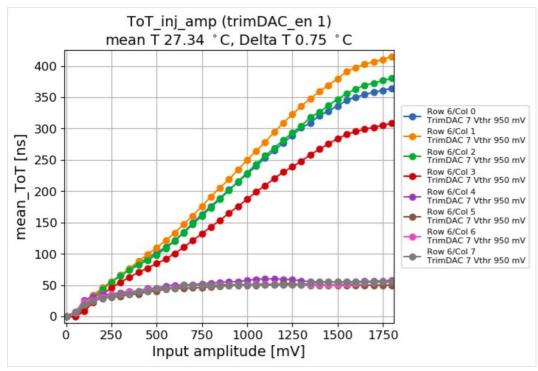

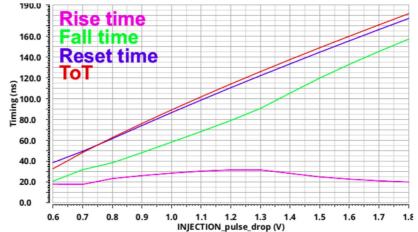

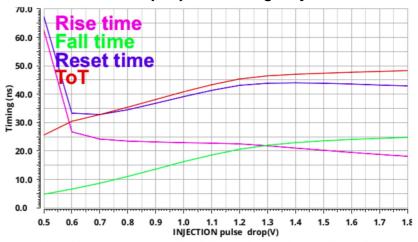

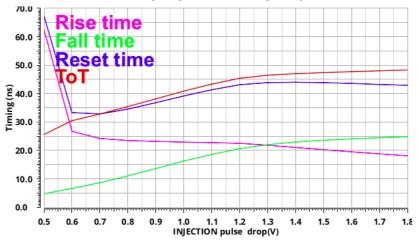

#### **RD50-MPW2 ToT measurement**

#### Measurement details:

- 400 test pulses generated (100 us of width and 1 ms of period). Amplitude 0 mV to 1800 mV.

- Different types of pixels measured: R6/C0-C3 (CR pixel) and R6/C4-C7 (SR pixel).

- Mean of ToT calculated for each injection amplitude.

- Nominal values of bias voltage registers. BL 900 mV. TH 950 mV.

TrimDAC enabled and programmed to 7.

R6/C0-C3 (CR) and R6/C4-C7 (SR) mean ToT (ns) versus input voltage pulse amplitude (mV).

Simulated ToT (red) with voltage injections for a CR pixel.

Simulated ToT (red) with voltage injections for a SR pixel.

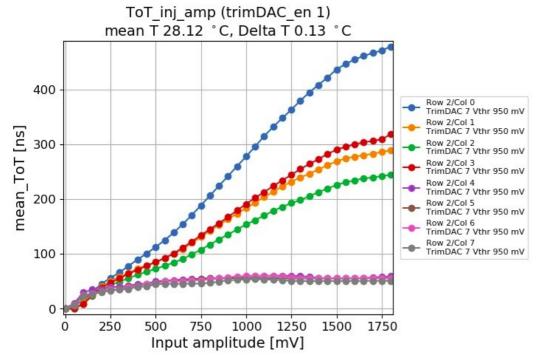

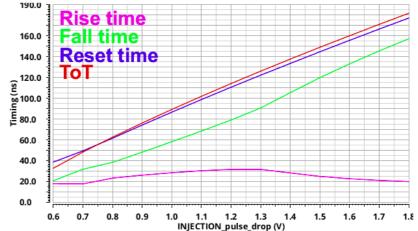

#### **RD50-MPW2 ToT measurement**

- Measurement details:

- 400 test pulses generated (100 us of width and 1 ms of period). Amplitude 0 mV to 1800 mV.

- Different types of pixels measured: R2/C0-C3 (CR pixel) and R2/C4-C7 (SR pixel).

- Mean of ToT calculated for each injection amplitude.

- Nominal values of bias voltage registers. BL 900 mV. TH 950 mV.

- TrimDAC enabled and programmed to 7.

R2/C0-C3 (CR) and R2/C4-C7 (SR) mean ToT (ns) versus input voltage pulse amplitude (mV).

Simulated ToT (red) with voltage injections for a CR pixel.

Simulated ToT (red) with voltage injections for a SR pixel.

#### **Next steps**

- RD50 workshop talk about active matrix, bandgap and SEU memory.

- After RD50 Workshop: follow agreed measurements of excel file.

- I-V measurement of active matrix.

- Measurement of bias voltages vs. different values programmed using ABUFF\_OUT.

- Measurements with HV applied.

- Measurements with three different chip boards (with MPW2 devices from different wafers with different resistivities).

• ...

# RD50-MPW2 active pixel matrix measurements

Ricardo Marco Hernández IFIC (CSIC-UV)

## **CR and SR pixels**

Figure 5.2. Schematic diagram of the continuous-reset pixel

Figure 5.9. Schematic diagram of the switched-reset pixel